1.本技术涉及到数据存储技术领域,尤其涉及到一种存储系统中纠错码仿真方法及装置、存储介质、计算机设备。

背景技术:

2.硬判决读是固态硬盘(nand)存储器最主要的读取方式之一,这种读取方式的特点为每两个相邻阈值电压之间只进行一次电压比较,这种读取方式较为粗糙,只能读出存储信息是比特1还是比特0,而不能给出更详细的信息,不利于后续的错误纠正,但是其带来的读延时最小,因而在整个产品寿命周期内都是优先级最高的读取方式。

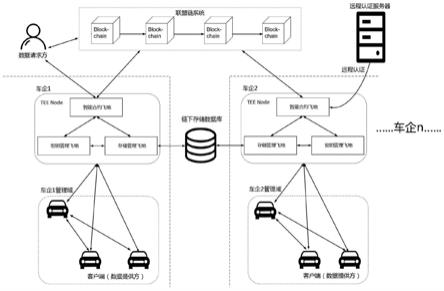

3.硬判决读会以一定的概率引入错误,并且随着存储器的使用寿命逐渐增加,错误概率会同步提升。因而固态硬盘存储控制器需要采用较为强大的纠错码(ecc,error control coding)作为应对措施,在现有技术中,参见图1,可以用模型来高度概括一个存储系统,其中,二进制对称信道(bsc,binary symmetric channel)是被广泛认可的信道模型,在0所示系统仿真中被普遍应用,bsc信道是离散无记忆信道,其输入和输出都只有0和1两种符号,并且发送0而接收到1,以及发送1而收到0(即误码)的概率相同,所以该信道是对称的。此时条件差错概率(cp,conditional probability)由p表示,二进制对称信道的转移概率如0所示。

4.现有技术在模拟bsc信道时,必须对每一个经过该信道的比特进行概率运算,以判断其是否会发生翻转,通常每次概率运算都会调用一次均匀分布随机数发生器或函数,因而计算量非常大,虽然通过采用提高运算并行度的各种措施,例如流水线、多线程、并行指令集等,可以在高速硬件平台上实现高吞吐率,但是成本很高,而且通用性受限。

技术实现要素:

5.有鉴于此,本技术提供了一种存储系统中纠错码的仿真方法及装置、存储介质、计算机设备,减少二项分布和均匀分布的运算量,减少开发成本,实现方式非常灵活,提高通用性。

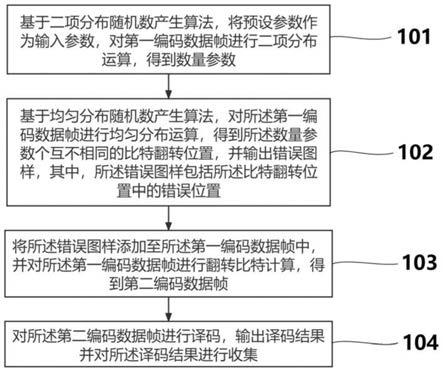

6.根据本技术的一个方面,提供了一种存储系统中纠错码的仿真方法,所述方法包括:

7.基于二项分布随机数产生算法,将预设参数作为输入参数,对第一编码数据帧进行二项分布运算,得到数量参数;

8.基于均匀分布随机数产生算法,对所述第一编码数据帧进行均匀分布运算,得到所述数量参数个互不相同的比特翻转位置,并输出错误图样,其中,所述错误图样包括所述比特翻转位置中的错误位置;

9.将所述错误图样添加至所述第一编码数据帧中,并对所述第一编码数据帧进行翻转比特计算,得到第二编码数据帧;

10.对所述第二编码数据帧进行译码,输出译码结果并对所述译码结果进行收集。

11.可选地,所述预设参数包括编码数据帧的长度值和原始比特错误概率值,其中,所述编码数据帧长度值标定为n,所述原始比特错误概率值标定为p。

12.可选地,所述二项分布运算进行至少1次,所述均匀分布运算进行至少pn次。

13.可选地,所述将所述错误图样添加至所述第一编码数据帧,并对所述第一编码数据帧进行翻转比特计算,得到第二编码数据帧,具体包括:

14.将所述错误图样添加至所述第一编码数据帧中,并根据所述错误图样将所述第一编码数据帧中翻转比特位置上的比特进行取反。

15.可选地,所述对所述第二编码数据帧进行译码,输出译码结果并收集,具体包括:

16.利用译码模块对所述第二编码数据帧进行译码,输出所述译码结果;

17.将所述译码结果写入记录文件或显示在监视器上,其中,所述译码结果包括译码完成后的编码数据帧和所述错误图样。

18.可选地,所述方法还包括:

19.基于预设的仿真中止条件,对所述译码结果进行识别,并判断仿真过程是否中止,若所述仿真过程未中止,则重复进行所述仿真过程,其中,所述预设的仿真中止条件包括译码失败的次数和完成译码的帧数。

20.可选地,所述存储系统中纠错码的仿真方法在主机端进行或在主机端和硬件平台进行或在硬件平台进行进行。

21.根据本技术的另一方面,提供了一种存储系统中纠错码的仿真装置,所述装置包括:

22.二项分布计算模块,用于基于二项分布随机数产生算法,将预设参数作为输入参数,对第一编码数据帧进行二项分布运算,得到数量参数;

23.均匀分布计算模块,用于基于均匀分布随机数产生算法,对所述第一编码数据帧进行均匀分布运算,得到所述数量参数个互不相同的比特翻转位置,并输出错误图样,其中,所述错误图样包括所述比特翻转位置中的错误位置;

24.翻转比特计算模块,用于将所述错误图样添加至所述第一编码数据帧中,并对所述第一编码数据帧进行翻转比特计算,得到第二编码数据帧;

25.解码模块,用于对所述第二编码数据帧进行译码,输出译码结果并对所述译码结果进行收集。

26.可选地,所述二项分布计算模块,具体用于:

27.所述预设参数包括编码数据帧的长度值和原始比特错误概率值,其中,所述编码数据帧长度值标定为n,所述原始比特错误概率值标定为p。

28.可选地,所述二项分布计算模块和所述均匀分布计算模块,具体用于:

29.所述二项分布运算进行至少1次,所述均匀分布运算进行至少pn次。

30.可选地,所述翻转比特计算模块,具体用于:

31.将所述错误图样添加至所述第一编码数据帧中,并根据所述错误图样将所述第一编码数据帧中翻转比特位置上的比特进行取反。

32.可选地,所述解码模块,具体用于:

33.利用译码模块对所述第二编码数据帧进行译码,输出所述译码结果;

34.将所述译码结果写入记录文件或显示在监视器上,其中,所述译码结果包括译码

完成后的编码数据帧和所述错误图样。

35.可选地,所述存储系统中纠错码的仿真装置,还包括:

36.仿真中止判断模块,用于基于预设的仿真中止条件,对所述译码结果进行识别,并判断仿真过程是否中止,若所述仿真过程未中止,则重复进行所述仿真过程,其中,所述预设的仿真中止条件包括译码失败的次数和完成译码的帧数。

37.可选地,所述存储系统中纠错码的仿真装置,具体用于:在主机端进行或在主机端和硬件平台进行或在硬件平台进行进行。

38.依据本技术又一个方面,提供了一种存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现上述一种存储系统中纠错码的仿真方法。

39.依据本技术再一个方面,提供了一种计算机设备,包括存储介质、处理器及存储在存储介质上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现上述一种存储系统中纠错码的仿真方法。

40.借由上述技术方案,本技术提供的一种存储系统中纠错码的仿真方法及装置、存储介质、计算机设备,该存储系统中纠错码的仿真方法通过二项分布计算获得每帧编码数据经过信道模拟流程后的错误个数,并通过均分布分布计算来获得互不相同的错误位置,将原本每个编码数据帧n次的随机数运算减少到1次二项分布随机运算和pn次均匀分布随机数运算,极大的减少了计算量,降低了开发成本,且实现方式灵活,通用性较高。

41.上述说明仅是本技术技术方案的概述,为了能够更清楚了解本技术的技术手段,而可依照说明书的内容予以实施,并且为了让本技术的上述和其它目的、特征和优点能够更明显易懂,以下特举本技术的具体实施方式。

附图说明

42.此处所说明的附图用来提供对本技术的进一步理解,构成本技术的一部分,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。在附图中:

43.图1为现有技术中存储系统概括模型图;

44.图2为现有技术中bsc信道模型图;

45.图3为本技术实施例提供的存储系统中纠错码的仿真方法逻辑流程图;

46.图4为本技术实施例提供的ecc仿真逻辑流程图;

47.图5为本技术实施例提供的ecc仿真系统组成示意图;

48.图6为本技术实施例提供的存储系统中纠错码的仿真装置的结构示意图。

具体实施方式

49.下文中将参考附图并结合实施例来详细说明本技术。需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。

50.在本实施例中提供了一种存储系统中纠错码的仿真方法,以该方法应用于计算机设备为例,如图3所示,该方法包括:

51.步骤101,基于二项分布随机数产生算法,将预设参数作为输入参数,对第一编码数据帧进行二项分布运算,得到数量参数;

52.具体的,通过二项分布随机数发生算法来获得每帧编码数据经过bsc信道后的错

误个数,具体来说,对于一帧含有n个比特的ecc码,经过条件差错概率为p的bsc信道后,相当于进行了n次独立重复的伯努利试验,用e表示n重伯努利试验中比特翻转发生的次数,则e的可能取值为0,1,

…

,n,且对每一个k(0≤k≤n),事件{e=k}即为“翻转比特数为k”,随机变量e的离散概率分布即为二项分布(binomial distribution),在存储器领域,通常用原始比特错误概率(raw bit error rate,rber)来表示p,在确定了以某个具体的原始比特错误概率作为仿真条件时,我们可以通过二项分布函数随机地决定每一帧错误的比特数,然后根据均匀分布函数决定比特的错误位置。

53.步骤102,基于均匀分布随机数产生算法,对所述第一编码数据帧进行均匀分布运算,得到所述数量参数个互不相同的比特翻转位置,并输出错误图样,其中,所述错误图样包括所述比特翻转位置中的错误位置;

54.具体的,根据均匀分布函数用均匀分布随机数产生算法生成e个互不相同的比特翻转位置,决定比特的错误位置,最后输出错误图样,这里的错误图样既可以同时包含e和所有的错误位置,也可以只包含错误位置。

55.步骤103,将所述错误图样添加至所述第一编码数据帧中,并对所述第一编码数据帧进行翻转比特计算,得到第二编码数据帧;

56.具体的,将bsc信道模拟输出的错误图样加到编码数据帧中,即根据错误图样将编码数据帧中对应翻转比特位置上的比特取反。

57.步骤104,对所述第二编码数据帧进行译码,输出译码结果并对所述译码结果进行收集。

58.具体的,ecc译码模块对加入了错误图样的编码数据帧进行译码,并将译码结果输出,译码结果包括译码成功与否,迭代次数,发现的错误比特数量和位置,译码成功后得到的编码数据帧等信息。

59.通过应用本实施例的技术方案,提供的一种存储系统中纠错码的仿真方法及装置、存储介质、计算机设备,该存储系统中纠错码的仿真方法通过二项分布计算获得每帧编码数据经过信道模拟流程后的错误个数,并通过均分布随机数发生器来获得互不相同的错误位置,将原本每个编码数据帧n次的随机数运算减少到1次二项分布随机运算和pn次均匀分布随机数运算,极大的减少了计算量,降低了开发成本,且实现方式灵活,通用性较高。

60.在本技术实施例中,可选地,所述预设参数包括编码数据帧的长度值和原始比特错误概率值,其中,所述编码数据帧长度值标定为n,所述原始比特错误概率值标定为p。

61.在上述实施例中,预设参数设定步骤只在初始化时执行,用于标定编码数据帧长度n和原始比特错误概率p,将n和p为输入参数,用二项分布随机数产生算法得到一个数量整数,标定为e。

62.在本技术实施例中,可选地,所述二项分布运算进行至少1次,所述均匀分布运算进行至少pn次。

63.在上述实施例中,由于nand存储器寿命周期内的rber通常小于10-2,本技术平均只需要至少1次二项分布随机运算和pn次均匀分布随机数运算,在信道模拟上的平均计算量相比现有方法减少到了1/100以下。

64.在本技术实施例中,可选地,所述将所述错误图样添加至所述第一编码数据帧,并对所述第一编码数据帧进行翻转比特计算,得到第二编码数据帧,具体包括:将所述错误图

样添加至所述第一编码数据帧中,并根据所述错误图样将所述第一编码数据帧中翻转比特位置上的比特进行取反。

65.在上述实施例中,错误图样将编码数据帧中对应翻转比特位置上的比特取反,如果ecc编码器输出的是比特映射前的数据,就是1变成0,0变成1,否则的话,就是-l变成 l, l变成-l,其中l是一个正整数。

66.在本技术实施例中,可选地,所述对所述第二编码数据帧进行译码,输出译码结果并收集,具体包括:利用译码模块对所述第二编码数据帧进行译码,输出所述译码结果;将所述译码结果写入记录文件或显示在监视器上,其中,所述译码结果包括译码完成后的编码数据帧和所述错误图样。

67.在上述实施例中,ecc译码模块对加入了错误图样的编码数据帧进行译码,并将译码结果输出,收集ecc译码模块的输出和bsc的错误图样输出,将必要的信息写入记录文件或显示在监视器上,其中,译码结果包括译码成功与否,迭代次数,发现的错误比特数量和位置,译码成功后得到的编码数据帧等信息。

68.在本技术实施例中,可选地,所述方法还包括:基于预设的仿真中止条件,对所述译码结果进行识别,并判断仿真过程是否中止,若所述仿真过程未中止,则重复进行所述仿真过程,其中,所述预设的仿真中止条件包括译码失败的次数和完成译码的帧数。

69.在上述实施例中,仿真中止条件判断步骤根据译码失败的次数、已经译码的帧数等信息决定是否中止当前仿真,若判断仿真过程中止,则不再进行仿真过程,译码结果可作为输出结果;若所述仿真过程未中止,则继续对第一编码数据帧重复进行仿真过程。

70.在本技术实施例中,可选地,所述存储系统中纠错码的仿真方法在主机端进行或在主机端和硬件平台进行或在硬件平台进行进行。

71.在上述实施例中,参见附图5,以bsc信道模拟全部在主机端仿真系统的组成为例,包括host主机和ecc模块,其中,host主机实现bsc信道模拟功能,控制多个ecc模块进行仿真,并记录仿真结果,其中host主机内部还包含以下几个功能模块:

72.控制软件:协调多个线程组同时产生相互独立的bsc模拟信道,接收各ecc模块通过接口发回的各种输出、状态参数,并将必要的结果写入记录文件;

73.线程组:包含1个或多个cpu线程,每个线程上运行bsc信道模拟软件,其产生的输出为每个待仿真的编码数据帧上需要增加的完整或部分错误图样。此外为了提高计算效率,可以采用基于并行指令集编写的二项分布和均匀分布随机数产生函数(例如intel的virngbinomial和vsrnguniform函数),相比传统方法可以将运算速率提升一个量级以上;

74.接口:通过计算机和外部硬件设备的接口及协议(包括但不限于pcie协议、nvme协议、tcp/ip协议)将各个线程组产生的错误图样发送给各个ecc模块,控制这些模块进行仿真,并接收它们的反馈信息;

75.记录文件:记录仿真过程的各种信息,包括但不限于各ecc模块的状态log,仿真结果等信息;

76.另外,ecc模块按照host主机接口下方的指令、完整或部分错误图样进行仿真,并将仿真结果和模块的状态信息上报给host主机,通过硬件搭建的ecc平台,包括但不限于fpga板卡、asic芯片板卡,这些硬件平台上必须包含ecc解码器,但ecc编码器不是必选项,从数学角度上看,用bsc信道进行ecc解码仿真时,是否在一个固定的数据编码帧上添加不

同的错误图样,对于仿真的效果是等价的。

77.如果host主机的运算速度或者接口传输速度受限,也可以将bsc信道模拟中的二项分布或者均匀分布随机数产生模块部分或全部移植到硬件平台实现。该硬件平台可以是在ecc模块上,也可也是单独的硬件平台。

78.硬件平台在ecc模块上时,每个ecc模块要将host传来的部分错误图样和本地的部分错误图样合并,才能得到完整的错误图样;硬件平台是单独的硬件平台时,host端只负责仿真的控制和结果收集,bsc信道模拟完全交由host以外的硬件实现。

79.进一步的,作为图3和图4方法的具体实现,本技术实施例提供了一种存储系统中纠错码的仿真装置,如图6所示,该装置包括:二项分布计算模块,用于基于二项分布随机数产生算法,将预设参数作为输入参数,对第一编码数据帧进行二项分布运算,得到数量参数;均匀分布计算模块,用于基于均匀分布随机数产生算法,对所述第一编码数据帧进行均匀分布运算,得到所述数量参数个互不相同的比特翻转位置,并输出错误图样,其中,所述错误图样包括所述比特翻转位置中的错误位置;翻转比特计算模块,用于将所述错误图样添加至所述第一编码数据帧中,并对所述第一编码数据帧进行翻转比特计算,得到第二编码数据帧;解码模块,用于对所述第二编码数据帧进行译码,输出译码结果并对所述译码结果进行收集。

80.其中,所述二项分布计算模块,具体用于:所述预设参数包括编码数据帧的长度值和原始比特错误概率值,其中,所述编码数据帧长度值标定为n,所述原始比特错误概率值标定为p。

81.其中,所述二项分布计算模块和所述均匀分布计算模块,具体用于所述二项分布运算进行至少1次,所述均匀分布运算进行至少pn次。

82.其中,所述翻转比特计算模块,具体用于:将所述错误图样添加至所述第一编码数据帧中,并根据所述错误图样将所述第一编码数据帧中翻转比特位置上的比特进行取反。

83.其中,所述解码模块,具体用于:利用译码模块对所述第二编码数据帧进行译码,输出所述译码结果;将所述译码结果写入记录文件或显示在监视器上,其中,所述译码结果包括译码完成后的编码数据帧和所述错误图样。

84.其中,所述存储系统中纠错码的仿真装置,还包括:仿真中止判断模块,用于基于预设的仿真中止条件,对所述译码结果进行识别,并判断仿真过程是否中止,若所述仿真过程未中止,则重复进行所述仿真过程,其中,所述预设的仿真中止条件包括译码失败的次数和完成译码的帧数。

85.其中,所述存储系统中纠错码的仿真装置,具体用于:在主机端进行或在主机端和硬件平台进行或在硬件平台进行进行。

86.需要说明的是,本技术实施例提供的一种存储系统中纠错码的仿真装置所涉及各功能单元的其他相应描述,可以参考图3至图4方法中的对应描述,在此不再赘述。

87.基于上述如图3至图4所示方法,相应的,本技术实施例还提供了一种存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现上述如图3至图4所示的存储系统中纠错码的仿真方法。

88.基于这样的理解,本技术的技术方案可以以软件产品的形式体现出来,该软件产品可以存储在一个非易失性存储介质(可以是cd-rom,u盘,移动硬盘等)中,包括若干指令

用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本技术各个实施场景所述的方法。

89.基于上述如图3至图4所示的方法,以及图6所示的虚拟装置实施例,为了实现上述目的,本技术实施例还提供了一种计算机设备,具体可以为个人计算机、服务器、网络设备等,该计算机设备包括存储介质和处理器;存储介质,用于存储计算机程序;处理器,用于执行计算机程序以实现上述如图3至图4所示的存储系统中纠错码的仿真方法。

90.可选地,该计算机设备还可以包括用户接口、网络接口、摄像头、射频(radio frequency,rf)电路,传感器、音频电路、wi-fi模块等等。用户接口可以包括显示屏(display)、输入单元比如键盘(keyboard)等,可选用户接口还可以包括usb接口、读卡器接口等。网络接口可选的可以包括标准的有线接口、无线接口(如蓝牙接口、wi-fi接口)等。

91.本领域技术人员可以理解,本实施例提供的一种计算机设备结构并不构成对该计算机设备的限定,可以包括更多或更少的部件,或者组合某些部件,或者不同的部件布置。

92.存储介质中还可以包括操作系统、网络通信模块。操作系统是管理和保存计算机设备硬件和软件资源的程序,支持信息处理程序以及其它软件和/或程序的运行。网络通信模块用于实现存储介质内部各组件之间的通信,以及与该实体设备中其它硬件和软件之间通信。

93.通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到本技术可以借助软件加必要的通用硬件平台的方式来实现,也可以通过硬件实现减少了二项分布运算和均匀分布运算的计算量,降低开发成本,且实现方式灵活,提高通用性。

94.本领域技术人员可以理解附图只是一个优选实施场景的示意图,附图中的模块或流程并不一定是实施本技术所必须的。本领域技术人员可以理解实施场景中的装置中的模块可以按照实施场景描述进行分布于实施场景的装置中,也可以进行相应变化位于不同于本实施场景的一个或多个装置中。上述实施场景的模块可以合并为一个模块,也可以进一步拆分成多个子模块。

95.上述本技术序号仅仅为了描述,不代表实施场景的优劣。以上公开的仅为本技术的几个具体实施场景,但是,本技术并非局限于此,任何本领域的技术人员能思之的变化都应落入本技术的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。