1.本公开内容涉及一种电压调制电路,特别涉及一种能够提供动态电压输出范围的电压调制电路。

背景技术:

2.在现今技术中,电子装置的电路通常会具有在低压摆幅操作的信号,前述在低压摆幅操作的信号的值域会低于适合外部电路的信号的值域,因此电压调制电路通常用于将低压摆幅信号转换为外部电路接受的高压摆幅信号,并且增加电压调制电路输出电压的范围为重要的议题。

技术实现要素:

3.本公开文件提供一种电压调制电路。电压调制电路包含缓冲电路、电平移位电器、偏压电路以及跨压限制电路。缓冲电路包含多个上拉晶体管以及多个下拉晶体管。该些上拉晶体管电性串联在该电路的输出端以及系统高电压端之间,该些下拉晶体管电性串联在电压调制电路的该输出端以及系统低电压端之间。电平移位器用以依据输入信号产生多个控制信号。偏压电路电性耦接在电平移位器以及缓冲电路之间,偏压电路用以依据该些控制信号先后致能该缓冲电路的该些上拉晶体管或该些下拉晶体管,使输出端的电位在系统高电压端的电位与系统低电压端的电位之间切换。跨压限制电路电性耦接该些上拉晶体管以及该些下拉晶体管。当输出端的电位在系统高电压端的电位与系统低电压端的电位之间切换时用以限制该些上拉晶体管或该些下拉晶体管的两端的暂态与静态跨压。

4.本公开文件提供一种方法,用于操作包含缓冲电路的电压调制电路,其中缓冲电路包含多个上拉晶体管以及多个下拉晶体管。该些上拉晶体管电性串联在系统高电压端以及该电压调制电路的输出端之间。该些下拉晶体管电性串联在电压调制电路的输出端以及系统低电压端之间。所述方法包含下列步骤。提供一输入信号。依据输入信号产生多个控制信号。依据该些控制信号先后致能缓冲电路的该些上拉晶体管或该些下拉晶体管,使输出端的电位在系统高电压端的电位与系统低电压端的电位之间切换。当输出端的电位在系统高电压端的电位与系统低电压端的电位之间切换时与切换完成时,限制该些上拉晶体管或该些下拉晶体管的两端的暂态与静态跨压。

5.本公开文件提供一种方法,用于操作包含缓冲电路的电压调制电路,其中缓冲电路包含多个上拉晶体管电性串联在系统高电压端以及电压调制电路的输出端之间以及多个下拉晶体管电性串联在电压调制电路的输出端以及系统低电压端之间。所述方法包含下列步骤。提供一输入信号;依据输入信号产生多个控制信号;依据该些控制信号分别产生多个动态偏压;该些上拉晶体管中最接近系统高电压端的一者依据该些动态偏压中的一者而致能;该些下拉晶体管中最接近该系统低电压端的一者依据该些动态偏压中的另一者而致能。

6.综上所述,本公开文件的电压调制电路利用跨压限制电路抑制输出端的电位在切

换时产生的瞬时电流,从而增加电路的可靠度以及使用时间。

附图说明

7.为使本公开的上述和其他目的、特征、优点与实施例能更明显易懂,说明书附图的说明如下:

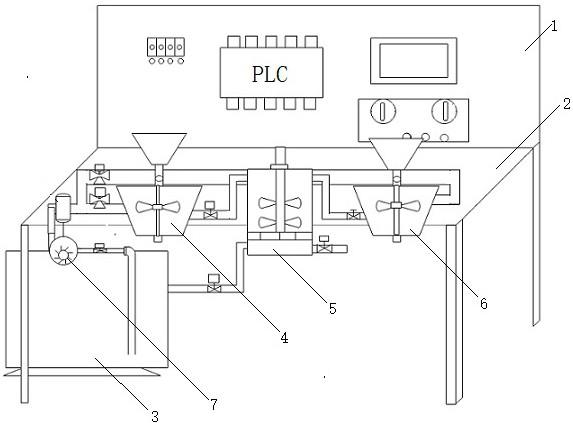

8.图1为本公开一实施例的电路的电路架构图。

9.图2为本公开一实施例的电路的电路架构图。

10.图3为图2中的电路的操作时序图。

11.图4为图2中的电路的操作时序图。

12.附图标记说明:

13.为使本公开的上述和其他目的、特征、优点与实施例能更明显易懂,所附符号的说明如下:

14.100:电压调制电路

15.110:缓冲电路

16.120:偏压电路

17.122:内部偏压电路

18.124:第一开关

19.126:第二开关

20.128:第三开关

21.130:电平移位器

22.140:跨压限制电路

23.tpu1~tpu5:上拉晶体管

24.tpd1~tpd5:下拉晶体管

25.t1~t6:晶体管

26.t7~t9:上拉限压晶体管

27.t10~t12:下拉限压晶体管

28.t13~t16:分压晶体管

29.t17~t26:晶体管

30.vin:输入信号

31.vout:输出端

32.gnd:接地端

33.n1~n3:节点

34.c1:第一电容

35.c2:第二电容

36.r1,r2,r3,r4:电阻

37.v1~v3:控制信号

38.vd1:第一动态偏压

39.vd2:第二动态偏压

40.vd3:第三动态偏压

41.vs1:第一静态偏压

42.vs2:第二静态偏压

43.vs3:第三静态偏压

44.vs4:第四静态偏压

45.vb1~vb5:内部偏压

46.na1~na4,nb1~nb4:节点

具体实施方式

47.下文是举实施例配合说明书附图作详细说明,以更好地理解本公开的实施方式,但所提供的实施例并非用以限制本公开所涵盖的范围,而结构操作的描述非用以限制其执行的顺序,任何由元件重新组合的结构,所产生具有均等技术效果的装置,皆为本公开所涵盖的范围。此外,根据业界的标准及惯常做法,附图仅以辅助说明为目的,并未依照原尺寸作图,实际上各种特征的尺寸可任意地增加或减少以便于说明。下述说明中相同元件将以相同的符号标示来进行说明以便于理解。

48.本公开说明书和附图中使用的元件编号和信号编号中的索引1~n,只是为了方便指称个别的元件和信号,并非有意将前述元件和信号的数量局限在特定数目。在本公开说明书和附图中,若使用某一元件编号或信号编号时没有指明该元件编号或信号编号的索引,则代表该元件编号或信号编号是指称所属元件群或信号群中不特定的任一元件或信号。

49.此外,在本文中所使用的用词“包含”、“包括”、“具有”、“含有”等等,均为开放性的用语,即意指“包含但不限于”。此外,本文中所使用的“及/或”,包含相关列举项目中一或多个项目的任意一个以及其所有组合。

50.于本文中,当一元件被称为“连接”或“耦接”时,可指“电性连接”或“电性耦接”。“连接”或“耦接”亦可用以表示二或多个元件间相互搭配操作或互动。此外,虽然本文中使用“第一”、“第二”、

…

等用语描述不同元件,该用语仅是用以区别以相同技术用语描述的元件或操作。

51.请参阅图1,图1为本公开一实施例的电压调制电路100的电路架构图。如图1所示,电压调制电路100包含缓冲电路110、偏压电路120、电平移位器130以及跨压限制电路140。缓冲电路110包含上拉晶体管tpu1~tpu5以及下拉晶体管tpd1~tpd5。上拉晶体管tpu1~tpu5电性串联在系统高电压端vgh以及电压调制电路100的输出端vout之间,下拉晶体管tpd1~tpd5电性串联在电压调制电路100的输出端vout以及系统低电压端vgl之间。

52.于一实施例中,电压调制电路100可以应用在显示装置(图中未示出),例如电压调制电路100可以应用在显示装置的扫描驱动器(scan driver)或栅极驱动器(gate driver)。例如,当电压调制电路100应用在扫描驱动器时,电压调制电路100用以根据输入信号vin产生相应的输出电压至输出端vout,此输出端vout可以耦接至显示装置的扫描线。电压调制电路100可以将电压变化范围较小的输入信号vin(例如在0v至3v之间震荡)转换为电压变化范围较大的输出电压(例如在-3v至12v之间震荡)至输出端vout,借此提供足够大的电压变化范围以驱动显示装置的扫描线,使显示装置达到理想的显示效果。详细如何将电压变化范围较小的输入信号vin转换为电压变化范围较大的输出电压至输出端vout将

在后续段落有进一步说明。

53.电压调制电路100具有承载高电压的系统高电压端vgh以及承载低电压的系统低电压端vgl。电压调制电路100利用偏压电路120输出的动态偏压vd1及vd2、静态偏压vs1及vs2以及内部偏压vb1~vb5来控制缓冲电路110中的上拉晶体管tpu1~tpu5以及下拉晶体管tpd1~tpd5,借此将输出端vout的电压电平切换在系统高电压端vgh的电位以及系统低电压端vgl的电位之间。

54.在本公开文件中,电压调制电路100所采用的n型晶体管可以由具有深n井的n型金属氧化物半导体实施。在电压调制电路100中的n型晶体管的深n井电性耦接至该系统高电压端vgh,使得p型基板与深n井的pn接面不会顺向导通、p型井与深n井的pn接面不会顺向导通,n型晶体管中pn接面的跨压皆会在容许范围内。如此,将电压调制电路100的系统低电压端vgl被设定在负数值,例如可将系统低电压端vgl的电位能够设定在-3伏特,n型晶体管亦能承受电压调制电路100中的跨压,从而避免n型晶体管pn接面崩溃。并且,本公开的n型晶体管各自的基极端与其源极端电性耦接,以消除本体效应(body effect)。

55.如上述实施例,在本公开文件中系统低电压端vgl的电位能够设定在-3伏特,并系统高电压端vgh的电位被设定在12伏特,借此使输出端vout的电压电平可以在-3伏特以及12伏特之间切换。

56.在一些实施例中,系统低电压端vgl的电位与系统高电压端vgh的电位的差值可以为上拉晶体管tpu1~tpu5或下拉晶体管tpd1~tpd5的数量的倍数。也就是说,系统低电压端vgl的电位以及系统高电压端vgh的电位可以被设定在其它数值,本公开文件不应以此为限。

57.在一些实施例中,电压调制电路100的输出端vout的电位可用于驱动显示面板中各个像素的驱动电路。一般而言,缓冲电路仅提供0伏特以上的电位供驱动电路使用,本公开文件的电压调制电路100当中的缓冲电路110提供-3伏特以及12伏特的输出电位,从而提高驱动电路对发光元件(例如,有机发光二极管或微型发光二极管)的电压操作范围,借此提升发光元件的亮度。

58.偏压电路120电性耦接在电平移位器130以及跨压限制电路140之间。偏压电路120用以依据控制信号v1、v2及v3先后致能缓冲电路110的上拉晶体管tpu1或下拉晶体管tpd1,使输出端vout的电位在系统高电压端vgh的电位与系统低电压端vgl的电位之间切换。偏压电路120包含第一开关124、第二开关126、第三开关128、分压晶体管t13~t16以及内部偏压电路122。分压晶体管t13~t16电性串连在系统高电压端vgh以及接地端gnd之间。分压晶体管t13~t16每一者的栅极端与漏极端电性耦接。也就是说,由于分压晶体管t13的栅极端以及第一端(漏极端)电性耦接系统高电压端,在分压晶体管t13的第二端在较低电位时,分压晶体管t13会导通以将系统高电压端的电位传送至分压晶体管t13的第二端,直到分压晶体管t13的第二端(源极端)与栅极端的电位差为分压晶体管t13的临界电压时,分压晶体管t13截止。分压晶体管t14~t16的作栋方式类似于分压晶体管t13,在此不再赘述。

59.在本公开的实施例中,分压晶体管t13~t16的临界电压可以是3伏特,并且系统高电压端vgh的电位是12伏特,接地端电位是0伏特,4颗分压晶体管t13~t16可以分别提供9伏特的第一静态偏压vs1、6伏特的第三静态偏压vs3、3伏特的第四静态偏压vs4以及0伏特的第二静态偏压vs2。

60.在架构上,分压晶体管t13的第一端电性耦接系统高电压端vgh,分压晶体管t13的第二端电性耦接分压晶体管t14的第一端。分压晶体管t14的第二端电性耦接分压晶体管t15的第一端。分压晶体管t15的第二端电性耦接分压晶体管t16的第一端。分压晶体管t16的第二端电性耦接接地端gnd。

61.电平移位器130用以接收输入信号vin,并且电平移位器130依据输入信号vin产生控制信号v1、v2及v3,并且电平移位器130分别提供控制信号v1、v2及v3至第一开关124、第二开关126以及第三开关128。

62.第一开关124、第二开关126以及第三开关128电性耦接在系统高电压端vgh以及系统低电压端vgl之间。第一开关124电性耦接在系统高电压端vgh以及分压晶体管t13的第二端(节点n1)之间。

63.第一开关124包含晶体管t1及t2。晶体管t1的第一端电性耦接系统高电压端vgh,晶体管t1的第二端电性耦接晶体管t2的第一端,晶体管t1的栅极端电性耦接晶体管t2的栅极端。晶体管t2的第二端电性耦接节点n1。晶体管t1以及晶体管t2的栅极端用以接收控制信号v1。

64.第一开关124用以依据控制信号v1导通晶体管t1及t2中的一者且关断晶体管t1及t2中的另一者以提供系统高电压端vgh的电位或第一静态偏压vs1至上拉晶体管tpu1的栅极端。换言之,第一开关124依据控制信号v1产生在系统高电电压端vgh的电位以及在第一静态偏压vs1的电位之间切换的第一动态偏压vd1,并且第一开关124提供第一动态偏压vd1至上拉晶体管tpu1的栅极端。

65.第二开关126包含晶体管t5及t6。晶体管t5的第一端电性耦接分压晶体管t16的第二端,晶体管t5的第二端电性耦接晶体管t6的第一端以及下拉晶体管tpd1的栅极端,晶体管t5的栅极端电性耦接晶体管t6的栅极端。晶体管t6的第二端电性耦接系统低电压端vgl。晶体管t5以及晶体管t6的栅极端用以接收控制信号v2。

66.第二开关126电性耦接在分压晶体管t16的第二端(节点n2)以及系统低电压端vgl之间。第二开关126用以依据控制信号v2导通晶体管t5及t6中的一者且关断晶体管t5及t6中的另一者以提供第二静态偏压vs2或系统低电压端vgl的电位至下拉晶体管tpd1的栅极端。换言之,第二开关126依据控制信号v2产生在第二静态偏压vs2的电位以及在系统低电压端vgl的电位之间切换的第二动态偏压vd2,并且第二开关126提供第二动态偏压vd2至下拉晶体管tpd1的栅极端。

67.第三开关128包含晶体管t3及t4。晶体管t3的第一端电性耦接分压晶体管t14的第二端,晶体管t3的第二端电性耦接晶体管t4的第一端以及内部偏压电路122,晶体管t3的栅极端电性耦接晶体管t4的栅极端。晶体管t4的第二端电性耦接分压晶体管t16的第一端。晶体管t3以及晶体管t4的栅极端用以接收控制信号v3。

68.第三开关128电性耦接在分压晶体管t14的第二端以及分压晶体管t16的第一端之间。第三开关128用以依据控制信号v3导通晶体管t3及t4中的一者且关断晶体管t3及t4中的另一者以提供系统第三静态偏压vs3或第四静态偏压vs4至内部偏压电路122。换言之,第三开关128依据控制信号v3产生在第三静态偏压vs3的电位以及在第四静态偏压vs4的电位之间切换的第三动态偏压vd3,并且第三开关128提供第三动态偏压vd3至内部偏压电路122。

69.偏压电路120还包含内部偏压电路122。内部偏压电路122电性耦接在节点n1以及节点n2之间。内部偏压电路122提供内部偏压vb1~vb5至缓冲电路110。在后续实施例中会详细说明内部偏压电路122架构及操作方式。

70.缓冲电路110的上拉晶体管tpu1~tpu5以及下拉晶体管tpd1~tpd5分别依据第一动态偏压vd1、第一静态偏压vs1、第二动态偏压vd2、第二静态偏压vs2以及内部偏压vb1~vb5而致能。进一步而言,上拉晶体管tpu1~tpu5中最接近系统高电压端vgh的一者(例如,上拉晶体管tpu1)依据动态偏压vd1致能,下拉晶体管tpd1~tpd5中最接近系统低电压端vgl的一者(例如,下拉晶体管tpd1)依据动态偏压vd2而致能。

71.详细而言,上拉晶体管tpu1的第一端电性耦接系统高电压端vgh,上拉晶体管tpu1的第二端电性耦接上拉晶体管tpu2的第一端,上拉晶体管tpu1的栅极端用以接收第一动态偏压vd1。上拉晶体管tpu2的第二端电性耦接上拉晶体管tpu3的第一端,上拉晶体管tpu2的栅极端用以接收第一静态偏压vs1。上拉晶体管tpu3的第二端电性耦接上拉晶体管tpu4的第一端,上拉晶体管tpu3的栅极端用以接收内部偏压vb1。上拉晶体管tpu4的第二端电性耦接上拉晶体管tpu5的第一端,上拉晶体管tpu4的栅极端用以接收内部偏压vb2。上拉晶体管tpu5的第二端电性耦接电压调制电路100的输出端vout,上拉晶体管tpu5的栅极端用以接收内部偏压vb3。并且,节点na1~na4分别是上拉晶体管tpu1~tpu4中相邻两者的连接处。

72.下拉晶体管tpd1的第一端电性耦接系统低电压端vgl,下拉晶体管tpd1的第二端电性耦接下拉晶体管tpd2的第一端,下拉晶体管tpd1的栅极端用以接收第二动态偏压vd2。下拉晶体管tpd2的第二端电性耦接下拉晶体管tpd3的第一端,下拉晶体管tpd2的栅极端用以接收第二静态偏压vs2。下拉晶体管tpd3的第二端电性耦接下拉晶体管tpd4的第一端,下拉晶体管tpd3的栅极端用以接收内部偏压vb5。下拉晶体管tpd4的第二端电性耦接下拉晶体管tpd5的第一端,下拉晶体管tpd4的栅极端用以接收内部偏压vb4。下拉晶体管tpd5的第二端电性耦接电压调制电路100的输出端vout,下拉晶体管tpd5的栅极端用以接收内部偏压vb3。并且,节点nb1~nb4分别是下拉晶体管tpd1~tpd4中相邻两者的连接处。

73.跨压限制电路140电性耦接上拉晶体管tpu1~tpu4以及下拉晶体管tpd1~tpd4。当输出端vout的电位在系统高电压端vgh的电位与系统低电压端vgl的电位之间切换时,跨压限制电路140用以限制上拉晶体管tpu1~tpu4或下拉晶体管tpd1~tpd4的两端的暂态与静态跨压。跨压限制电路140包含上拉限压晶体管t7~t9以及下拉限压晶体管t10~t12。

74.在架构上,上拉限压晶体管t7~t9电性耦接在上拉晶体管tpu2~tpu4各自的源极端以及栅极端之间。上拉限压晶体管t7~t9的栅极端电性耦接上拉晶体管tpu1~tpu3各自的栅极端。

75.上拉限压晶体管t7的漏极端耦接相邻两个上拉晶体管tpu1及tpu2其中一者(上拉晶体管tpu2)的源极端,上拉限压晶体管t7的源极端耦接相邻两个上拉晶体管tpu1及tpu2其中该者(上拉晶体管tpu2)的栅极端。上拉限压晶体管t7的栅极端耦接相邻两个上拉晶体管tpu1及tpu2中另一者(上拉晶体管tpu1)的栅极端。

76.上拉限压晶体管t8的漏极端耦接相邻两个上拉晶体管tpu2及tpu3其中一者(上拉晶体管tpu3)的源极端,上拉限压晶体管t8的源极端耦接相邻两个上拉晶体管tpu2及tpu3其中该者(上拉晶体管tpu3)的栅极端。上拉限压晶体管t8的栅极端耦接相邻两个上拉晶体管tpu2及tpu3中另一者(上拉晶体管tpu2)的栅极端。

77.上拉限压晶体管t9的漏极端耦接相邻两个上拉晶体管tpu3及tpu4其中一者(上拉晶体管tpu4)的源极端,上拉限压晶体管t9的源极端耦接相邻两个上拉晶体管tpu3及tpu4其中该者(上拉晶体管tpu4)的栅极端。上拉限压晶体管t9的栅极端耦接相邻两个上拉晶体管tpu3及tpu4中另一者(上拉晶体管tpu3)的栅极端。

78.详细而言,上拉限压晶体管t7的第一端电性耦接上拉晶体管tpu2的第一端(源极端),上拉限压晶体管t7的第二端电性耦接上拉晶体管tpu2的栅极端,上拉限压晶体管t7的栅极端电性耦接上拉晶体管tpu1的栅极端。上拉限压晶体管t7的栅极端用以接收第一动态偏压vd1,上拉限压晶体管t7的第二端(源极端)用以接收第一静态偏压vs1。换言之,上拉限压晶体管t7依据第一动态偏压vd1与第一静态偏压vs1的差异导通或关断。

79.上拉限压晶体管t8的第一端电性耦接上拉晶体管tpu3的第一端(源极端),上拉限压晶体管t8的第二端电性耦接上拉晶体管tpu3的栅极端,上拉限压晶体管t8的栅极端电性耦接上拉晶体管tpu2的栅极端。上拉限压晶体管t8的栅极端用以接收第一静态偏压vs1,上拉限压晶体管t8的第二端(源极端)用以接收内部偏压vb1。换言之,上拉限压晶体管t8依据第一静态偏压vs1与内部偏压vb1的差异导通或关断。

80.上拉限压晶体管t9的第一端电性耦接上拉晶体管tpu4的第一端(源极端),上拉限压晶体管t9的第二端电性耦接上拉晶体管tpu4的栅极端,上拉限压晶体管t9的栅极端电性耦接上拉晶体管tpu3的栅极端。上拉限压晶体管t9的栅极端用以接收内部偏压vb1,上拉限压晶体管t9的第二端(源极端)用以接收内部偏压vb2。换言之,上拉限压晶体管t9依据内部偏压vb1与内部偏压vb2的差异导通或关断。

81.在架构上,下拉限压晶体管t10~t12电性耦接在下拉晶体管tpd2~tpd4各自的源极端以及栅极端之间。下拉限压晶体管t10~t12的栅极端电性耦接下拉晶体管tpd1~tpd3各自的栅极端。

82.下拉限压晶体管t10的漏极端耦接相邻两个下拉晶体管tpd4及tpd3其中一者(下拉晶体管tpd4)的源极端,下拉限压晶体管t10的源极端耦接该相邻两个下拉晶体管tpd4及tpd3其中该者(下拉晶体管tpd4)的栅极端。下拉限压晶体管t10的栅极端耦接相邻两个下拉晶体管tpd4及tpd3中另一者(下拉晶体管tpd3)的栅极端。

83.下拉限压晶体管t11的漏极端耦接相邻两个下拉晶体管tpd3及tpd2其中一者(下拉晶体管tpd3)的源极端,下拉限压晶体管t11的源极端耦接该相邻两个下拉晶体管tpd3及tpd2其中该者(下拉晶体管tpd3)的栅极端。下拉限压晶体管t11的栅极端耦接相邻两个下拉晶体管tpd3及tpd2中另一者(下拉晶体管tpd2)的栅极端。

84.下拉限压晶体管t12的漏极端耦接相邻两个下拉晶体管tpd2及tpd1其中一者(下拉晶体管tpd2)的源极端,下拉限压晶体管t12的源极端耦接该相邻两个下拉晶体管tpd2及tpd1其中该者(下拉晶体管tpd2)的栅极端。下拉限压晶体管t12的栅极端耦接相邻两个下拉晶体管tpd2及tpd1中另一者(下拉晶体管tpd1)的栅极端。

85.详细而言,下拉限压晶体管t10的第一端电性耦接下拉晶体管tpd4的栅极端,下拉限压晶体管t10的第二端电性耦接下拉晶体管tpd4的第二端(源极端),下拉限压晶体管t10的栅极端电性耦接下拉晶体管tpd3的栅极端。下拉限压晶体管t10的第一端(源极端)用以接收内部偏压vb4,下拉限压晶体管t10的栅极端用以接收内部偏压vb5。换言之,下拉限压晶体管t10依据内部偏压vb4与内部偏压vb5的差异导通或关断。

86.下拉限压晶体管t11的第一端电性耦接下拉晶体管tpd3的栅极端,下拉限压晶体管t11的第二端电性耦接下拉晶体管tpd3的第二端(源极端),下拉限压晶体管t11的栅极端电性耦接下拉晶体管tpd2的栅极端。

87.下拉限压晶体管t11的第一端(源极端)用以接收内部偏压vb5,下拉限压晶体管t11的栅极端用以接收第二静态偏压vs2。换言之,下拉限压晶体管t11依据内部偏压vb5与第二静态偏压vs2的差异导通或关断。

88.下拉限压晶体管t12的第一端电性耦接下拉晶体管tpd2的栅极端,下拉限压晶体管t12的第二端电性耦接下拉晶体管tpd2的第二端(源极端),下拉限压晶体管t12的栅极端电性耦接下拉晶体管tpd1的栅极端。下拉限压晶体管t12的第一端(源极端)用以接收第二静态偏压vs2,下拉限压晶体管t12的栅极端用以接收第二动态偏压vd2。换言之,下拉限压晶体管t12依据第二静态偏压vs2与第二动态偏压vd2的差异导通或关断。

89.当输入信号vin在第一逻辑电平(例如,0伏特)时,电压调制电路100利用第一动态偏压vd1以及第三动态偏压vd3从系统高电压端vgh至输出端vout按序关断上拉晶体管tpu1~tpu5,并利用第二动态偏压vd2从系统低电压端vgl至输出端vout按序导通下拉晶体管tpd1~tpd5,借此将输出端vout的电位下拉至系统低电压端vgl的电位。

90.换言之,当输入信号vin在第一逻辑电平(例如,0伏特)时,上拉晶体管tpu1~tpu5依据第一动态偏压vd1、第一静态偏压vs1以及内部偏压vb1~vb5中的一部分而关断,并且下拉晶体管tpd1~tpd5依据第二动态偏压vd2、第二静态偏压vs2以及内部偏压vb1~vb5中的另一部分而导通。

91.当输入信号vin在第二逻辑电平(例如,3伏特)时,电压调制电路100利用第一动态偏压vd1从系统高电压端vgh至输出端vout按序导通上拉晶体管tpu1~tpu5,并利用第三动态偏压vd3以及第二动态偏压vd2从系统低电压端vgl至输出端vout按序关断下拉晶体管tpd1~tpd5,借此将输出端vout的电位上拉至系统高电压端vgh的电位。

92.换言之,当输入信号vin在第二逻辑电平(例如,3伏特)时,上拉晶体管tpu1~tpu5依据第一动态偏压vd1、第一静态偏压vs1以及内部偏压vb1~vb5中的一部分而导通,并且下拉晶体管tpd1~tpd5依据第二动态偏压vd2、第二静态偏压vs2以及内部偏压vb1~vb5中的另一部分而关断。

93.为了更佳的理解电压调制电路100的操作方式,在后续实施例中将进一步说明。

94.请参阅图2,图2为本公开一实施例的电压调制电路100的电路架构图。如图2所示,内部偏压电路122包含晶体管t17~t26、电阻r1~r4、第一电容c1以及第二电容c2。

95.详细而言,第一电容c1电性耦接在上拉晶体管tpu1~tpu5之中最接近输出端vout的两个上拉晶体管tpu4~tpu5的栅极端之间,用以稳定邻近输出端vout的两个上拉晶体管tpu4~tpu5的栅极端的电位。第一电容c1的第一端电性耦接上拉晶体管tpu4的栅极端,第一电容c1的第二端电性耦接上拉晶体管tpu5的栅极端。

96.电阻r1的第一端用以接收第三动态偏压vd3,电阻r1的第二端电性耦接晶体管t17的第一端。晶体管t17的第二端电性耦接上拉晶体管tpu4的栅极端,晶体管t17的栅极端电性耦接节点n3。晶体管t17用以依节点n3的电位提供内部偏压vb2至上拉晶体管tpu4的栅极端。

97.晶体管t19的第一端用以接收第三静态偏压vs3,晶体管t19的第二端电性耦接上

拉晶体管tpu3的栅极端,晶体管t19的栅极端电性耦接电容c1的第一端。晶体管t19用以依据电容c1的第一端的电位提供内部偏压vb1至上拉晶体管tpu3的栅极端。

98.电阻r3的第一端电性耦接节点n1,电阻r3的第二端电性耦接晶体管t21的第一端。晶体管t21的第二端电性耦接上拉晶体管tpu3的栅极端以及晶体管t22的第一端,晶体管t21的栅极端电性耦接上拉晶体管tpu3的第一端。晶体管t22的第二端电性耦接上拉晶体管tpu4的栅极端以及晶体管t23的第一端,晶体管t22的栅极端电性耦接上拉晶体管tpu4的第一端。晶体管t23的第二端电性耦接上拉晶体管tpu5的栅极端以及节点n3,晶体管t23的栅极端电性耦接上拉晶体管tpu5的第一端。并且,节点na4是上拉晶体管tpu4及tpu5的连接处。

99.第二电容c2电性耦接在下拉晶体管tpd1~tpd5之中最接近输出端vout的两个下拉晶体管tpd4~tpd5的栅极端之间,用以稳定邻近输出端vout的两个下拉晶体管tpd4~tpd5的栅极端的电位。第二电容c2的第一端电性耦接下拉晶体管tpd4的栅极端,第二电容c2的第二端电性耦接下拉晶体管tpd5的栅极端。

100.电阻r2的第一端用以接收第三动态偏压vd3,电阻r2的第二端电性耦接晶体管t18的第一端。晶体管t18的第二端电性耦接下拉晶体管tpd4的栅极端,晶体管t18的栅极端电性耦接节点n3。晶体管t18用以依据节点n3的电位提供内部偏压vb4至下拉晶体管tpd4的栅极端。

101.晶体管t20的第一端用以接收第四静态偏压vs4,晶体管t20的第二端电性耦接下拉晶体管tpd3的栅极端,晶体管t20的栅极端电性耦接电容c2的第二端。晶体管t20用以依据电容c2的第二端的电位提供内部偏压vb5至下拉晶体管tpd3的栅极端。

102.电阻r4的第一端电性耦接节点n2,电阻r4的第二端电性耦接晶体管t26的第二端。晶体管t26的第一端电性耦接下拉晶体管tpd3的栅极端以及晶体管t25的第二端,晶体管t26的栅极端电性耦接下拉晶体管tpd3的第二端。晶体管t25的第一端电性耦接下拉晶体管tpd4的栅极端以及晶体管t24的第二端,晶体管t25的栅极端电性耦接下拉晶体管tpd4的第二端。晶体管t24的第一端电性耦接下拉晶体管tpd5的栅极端以及节点n3,晶体管t24的栅极端电性耦接下拉晶体管tpd5的第二端。并且,节点nb4是下拉晶体管tpd4及tpd5的连接处。

103.请一并参阅图3以及图4。图3为图2中的电压调制电路100的操作时序图。图4为图2中的电压调制电路100的操作时序图。图3示出输入信号vin、第一动态偏压vd1、第二动态偏压vd2、第三动态偏压vd3、内部偏压vb1~vb5。

104.分压晶体管t13~t16电性耦接在系统高电压端vgh以及接地端gnd之间,从而提供分别为9伏特、6伏特、3伏特及0伏特的第一静态偏压vs1、第三静态偏压vs3、第四静态偏压vs4及第二静态偏压vs2。由于第一静态偏压vs1、第三静态偏压vs3、第四静态偏压vs4及第二静态偏压vs2皆在定值,因此未示出于图3及图4之中。

105.在输入信号vin由3伏特切换至0伏特时,电平移位电路130分别提供8.9伏特的控制信号v1、-3伏特的控制信号v2以及6.03伏特的控制信号v3至第一开关124、第二开关126以及第三开关128。

106.此时,控制信号v1(8.9伏特)导通晶体管t1且关断晶体管t2,以将系统高电压端vgh的电位(12伏特)作为第一动态偏压vd1传送至上拉晶体管tpu1的栅极端,使上拉晶体管

tpu1关断。并且,由于上拉限压晶体管t7的栅极端亦接收系统高电压端vgh的电位(12伏特),上拉限压晶体管t7的源极端接收第一静态偏压vs1(9伏特),使上拉限压晶体管t7导通,并将上拉限压晶体管t7的源极端的电位(9伏特)传送至上拉晶体管tpu2的源极端,借此关断上拉晶体管tpu2并抑制输出端vout的电位在下拉时的瞬时电流。

107.另一方面,控制信号v2(-3伏特)导通晶体管t5且关断晶体管t6,以将第二静态偏压vs2(0伏特)传送至下拉晶体管tpd1的栅极端,使下拉晶体管tpd1导通并关断下拉晶体管t12,以将系统低电压端vgl的电位(-3伏特)传送至下拉晶体管tpd2的源极端,使得下拉晶体管tpd2导通并将系统低电压端vgl的电位(-3伏特)传送至下拉晶体管tpd3的第二端,使晶体管t26导通并将第二静态偏压vs2(0伏特)传送至下拉晶体管tpd3的栅极端,使下拉晶体管tpd3导通并且下拉限压晶体管t11关断。下拉晶体管tpd3导通会将系统低电压端vgl的电位(-3伏特)传送至下拉晶体管tpd4的第二端以及晶体管t25的栅极端,使得晶体管t25导通。

108.晶体管t25导通会将第二静态偏压vs2(0伏特)作为内部偏压vb4传送至下拉晶体管tpd4的栅极端,使下拉晶体管tpd4导通并且下拉限压晶体管t10关断。

109.下拉晶体管tpd4导通会将系统低电压端vgl的电位(-3伏特)传送至下拉晶体管tpd4的第二端以及晶体管t24的栅极端,以导通晶体管t24。

110.晶体管t24导通会将第二静态偏压vs2(0伏特)作为内部偏压vb3传送至节点n3以及下拉晶体管tpd5的栅极端,使下拉晶体管tpd5导通,从而将系统低电压端vgl的电位(-3伏特)传送至输出端vout。如此,当输入信号vin由3伏特切换至0伏特时,输出端vout的电位得以被切换为系统低电压端vgl的电位,-3伏特。

111.晶体管t18依据节点n3的电位(0伏特)关断,并且晶体管t20依据第二电容c2的第二端的电位(0伏特)关断。

112.此时,依据控制信号v3(6.03伏特),第三开关128中的晶体管t4导通且t3关断,以将第四静态偏压vs4(3伏特)作为第三动态偏压vd3传送至晶体管t17及t18的第一端。

113.晶体管t17依据节点n3的电位(0伏特)导通,并且将第四静态偏压vs4(3伏特)作为内部偏压vb2传送至第一电容c1的第一端。晶体管t19依据第一电容c1的第一端的电位(3伏特)导通,以将第三静态偏压vs3(6伏特)作为内部偏压vb1传送至上拉晶体管tpu3的栅极端,使得上拉限压晶体管t8导通,并将上拉限压晶体管t8的源极端的电位(6伏特)传送至上拉晶体管tpu3的源极端,借此关断上拉晶体管tpu3并抑制输出端vout的电位在下拉时的瞬时电流,并且关断晶体管t21。

114.内部偏压vb2(3伏特)会导通上拉限压晶体管t9,并将上拉限压晶体管t9的源极端的电位(3伏特)传送至上拉晶体管tpu4的源极端,借此关断上拉晶体管tpu4以及晶体管t22并抑制输出端vout的电位在下拉时的瞬时电流。接着,节点na4的电位(例如,0伏特)会关断晶体管t23,并且节点n3的电位(0伏特)会关断上拉晶体管tpu5。如此,输入信号vin从3伏特切换至0伏特时,电压调制电路100依据第一动态偏压vd1从系统高电压端vgh至输出端vout按序关断上拉晶体管tpu1~tpu5,并依据第二动态偏压vd2从系统低电压端vgl至输出端vout按序导通下拉晶体管tpd1~tpd5,从而将输出端vout的电位从12伏特切换为-3伏特。

115.利用电压调制电路100的架构可从系统高电压端vgh至输出端vout按序关断上拉晶体管tpu1~tpu5,并抑制输出端vout的电位在下拉时的瞬时电流,从而增加电压调制电

路100的可靠度并延长电路的使用时间。

116.进一步而言,电压调制电路100中的各个晶体管的在操作时序中的跨压皆会小于3.1伏特,会在3.6伏特的安全范围内,亦会增加电压调制电路100的可靠度并延长电路的使用时间。因此,本公开文件中的一部分的晶体管(例如,上拉晶体管tpu1~tpu5、下拉晶体管tpd1~tpd5以及晶体管t1~t12及t17~t26)可以由低压晶体管实施,进而减少电路面积并降低制造成本。

117.如图3及图4所示,当输入信号vin从0伏特切换为3伏特时,控制信号v1、v2及v3分别是12伏特、0伏特及2.92伏特。第一动态偏压vd1、第二动态偏压vd2、第三动态偏压vd3分别是9伏特、-3伏特及6伏特。内部偏压vb1~vb5分别是9伏特、9伏特、9伏特、6伏特、3伏特。相应地,节点na1~na4的电位皆是在12伏特,节点nb1~nb4的电位分别是0伏特、3伏特、6伏特、9伏特。此时,电压调制电路100亦可从系统低电压端vgl至输出端vout按序关断下拉晶体管tpd1~tpd5,并将输出端vout的电位切换为系统高电压端vgh的电位,12伏特。

118.电压调制电路100按序关断下拉晶体管tpd1~tpd5的操作方式相似于电压调制电路100按序关断上拉晶体管tpu1~tpu5。因此,在此不再赘述。

119.综上所述,本公开文件的电压调制电路100利用上拉限压晶体管t7~t9以及下拉限压晶体管t10~t12抑制输出端vout的电位在切换时产生的瞬时电流,并且通过电压调制电路100经设计的架构使各个晶体管的跨压皆在容许范围,从而增加电压调制电路100的可靠度以及使用时间。进一步而言,电压调制电路100利用第一开关124、第二开关126以及第三开关128提供第一动态偏压vd1、第二动态偏压vd2以及第三动态偏压vd3予缓冲电路110,从而减少提供予缓冲电路110的控制信号的电路的面积。更甚者,电压调制电路100提供-3伏特及12伏特的电位供显示面板使用,借此增加显示面板的发光元件的发光亮度范围。

120.虽然本公开已以实施方式公开如上,然其并非限定本公开,任何本领域技术人员,在不脱离本公开的构思和范围内,当可作各种的变动与润饰,因此本公开的保护范围当视权利要求所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。