1.本公开涉及一种随机数生成器及随机数生成方法。

背景技术:

2.信息加密可以通过软件和硬件共同完成,硬件负责提供随机数,软件负责根据硬件提供的随机数产生更复杂的密钥,并采用密钥对信息进行加密。

3.目前,随机数生成主要是利用自然界中的物理噪声,比如器件噪声、核衰变噪声、布朗运动噪声、热噪声等,通过对这些噪声的放大、提取、后处理来生成随机数。该方案受电路制程、电压和温度影响严重,因此需要通过额外的电路去校正。

技术实现要素:

4.本公开实施例提供了一种随机数生成器及随机数生成方法。

5.本公开至少一实施例提供了一种随机数生成器,所述随机数生成器包括:

6.控制字提供电路,响应于第一规则产生多个控制字;

7.脉冲产生电路,与所述控制字提供电路连接,响应于所述多个控制字,输出多路脉冲信号,所述脉冲信号包括第一频率信号和第二频率信号,所述第一频率信号和所述第二频率信号在所述脉冲信号中出现的概率由对应的所述控制字控制;

8.随机数生成电路,与所述脉冲产生电路连接,对所述多路脉冲信号进行逻辑运算,产生随机数序列。

9.可选地,所述脉冲产生电路,包括多个脉冲子电路,所述多个脉冲子电路分别与所述控制字提供电路和所述随机数生成电路连接;

10.每个所述脉冲子电路分别根据一个所述控制字产生一路所述脉冲信号。

11.可选地,所述脉冲子电路,包括:信号发生器和频率合成器,所述频率合成器连接分别所述信号发生器、所述控制字提供电路和所述随机数生成电路连接;

12.所述信号发生器响应于初始脉冲信号产生相位均匀间隔的基准脉冲信号;

13.所述频率合成器响应于所述基准脉冲信号和所述控制字,产生所述脉冲信号;

14.其中,所述控制字包括第一系数和第二系数;

15.所述脉冲信号包括基于所述基准脉冲信号和第一系数产生的所述第一频率信号和基于所述基准脉冲信号和第一系数产生的所述第二频率信号,所述脉冲信号中的所述第一频率信号和所述第二频率信号的占比由所述第二系数控制。

16.可选地,所述频率合成器包括:第一处理单元、第二处理单元以及输出单元;

17.第一处理单元,与所述控制字提供电路连接,基于所述控制字分别产生第一控制信号和第二控制信号;

18.第二处理单元,与所述第一处理单元连接,基于所述第一控制信号从相位均匀间隔的基准脉冲信号中选出第一脉冲信号,以及基于所述第二控制信号从所述基准脉冲信号中选出第二脉冲信号,并从所述第一脉冲信号和所述第二脉冲信号中选择一个作为输出信

号;

19.输出单元,与所述第二处理单元连接,基于所述第二处理单元的输出信号产生所述脉冲信号。

20.可选地,所述随机数生成电路,包括:第一处理子电路和第二处理子电路;

21.所述第一处理子电路和所述脉冲产生电路连接,对所述多路脉冲信号进行第一处理,其中,所述第一处理包括异或、同或、与非中的至少一种;

22.所述第二处理子电路和所述第一处理子电路连接,对所述第一处理后的多路脉冲信号进行第二处理;

23.其中,第二处理包括基于时钟信号,对所述第一处理子电路输出的信号进行采样,得到所述随机数序列。

24.可选地,所述随机数生成电路,还包括:时钟子电路,与所述第二处理子电路连接,向所述第二处理子电路提供所述时钟信号。

25.可选地,所述时钟子电路用于采用所述多个脉冲子电路中的一个的输出作为所述时钟信号;

26.或者,所述时钟子电路用于采用外部时钟的输出作为所述时钟信号。

27.可选地,所述随机数生成器,还包括:

28.后处理电路,与所述随机数生成电路连接,对所述随机数生成电路输出的随机数序列进行概率偏差校正。

29.可选地,所述后处理电路,包括:

30.存储模块,存储随机序列;

31.处理模块,分别与所述随机数生成电路和所述存储模块连接,基于所述随机数生成电路输出的随机数和所述存储模块的随机序列中的一位,生成第一随机数;

32.运算模块,与所述处理模块连接,将所述处理模块输出的所述第一随机数和所述运算模块上一周期输出的第二随机数进行逻辑运算,输出第三随机数。

33.可选地,所述控制字为数值,所述多个控制字的整数部分互为质数。

34.本公开至少一实施例提供了一种随机数生成方法,所述方法包括:

35.响应于第一规则产生多个控制字;

36.响应于所述多个控制字,输出多路脉冲信号,所述脉冲信号包括第一频率信号和第二频率信号,所述第一频率信号和所述第二频率信号在所述脉冲信号中出现的概率由对应的所述控制字控制;

37.对所述多路脉冲信号进行逻辑运算,产生随机数序列。

38.可选地,所述响应于所述多个控制字,输出多路脉冲信号,包括:

39.响应于初始脉冲信号产生相位均匀间隔的基准脉冲信号;

40.响应于所述基准脉冲信号和所述控制字,产生所述脉冲信号;

41.其中,所述控制字包括第一系数和第二系数;

42.所述脉冲信号包括基于所述基准脉冲信号和第一系数产生的所述第一频率信号和基于所述基准脉冲信号和第一系数产生的所述第二频率信号,所述脉冲信号中的所述第一频率信号和所述第二频率信号的占比由所述第二系数控制。

43.可选地,所述对所述多路脉冲信号进行逻辑运算,产生随机数序列,包括:

44.对所述多路脉冲信号进行第一处理,其中,所述第一处理包括异或、同或、与非中的至少一种;

45.对所述第一处理后的多路脉冲信号进行第二处理;其中,第二处理包括基于时钟信号,对所述第一处理输出的信号进行采样,得到所述随机数序列。

46.可选地,所述方法还包括:

47.对所述随机数生成电路输出的随机数序列进行概率偏差校正。

48.可选地,所述对所述随机数生成电路输出的随机数序列进行概率偏差校正,包括:

49.基于产生的所述随机数序列和随机序列中的一位,生成第一随机数;

50.将所述第一随机数和上一周期输出的第二随机数进行逻辑运算,输出第三随机数。

附图说明

51.图1是相关技术中的随机数生成方案示意图;

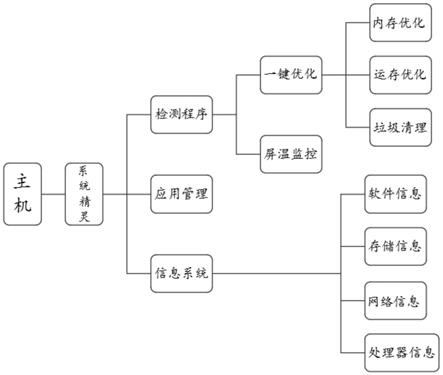

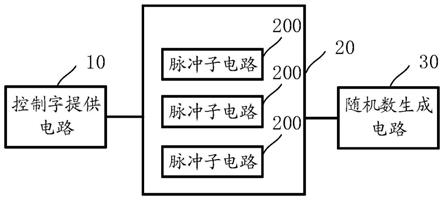

52.图2是本公开实施例提供的一种随机数生成器的结构示意图;

53.图3示出了本公开实施例提供的一种脉冲子电路的结构示意图;

54.图4为采用图3中的信号发生器产生的k路相位均匀间隔的基准脉冲信号的波形图;

55.图5为采用频率合成器进行脉冲信号合成的原理示意图;

56.图6为本公开提供的一种频率合成器的结构示意图;

57.图7为本公开提供的脉冲信号的频率fo与控制字f的关系示意图;

58.图8示出了本公开实施例提供的一种随机数生成电路的结构示意图;

59.图9示出了本公开实施例提供的一种随机数生成电路的详细示意图;

60.图10是本公开实施例提供的另一种随机数生成器的结构示意图;

61.图11示出了本公开实施例提供的一种后处理电路的结构示意图;

62.图12示出了本公开实施例提供的随机数序列示意图;

63.图13示出了本公开实施例提供的随机数序列的频谱信息示意图;

64.图14示出了本公开实施例提供的一种随机数生成方法的流程图。

具体实施方式

65.为使本公开的原理和优点更加清楚,下面将结合附图对本公开实施方式作进一步地详细描述。

66.随着5g的到来以及物联网的快速发展,大到企业服务器,小到个人心率计都会连入网络中,因此,信息安全和个人隐私问题得到人们的广泛关注,在庞大的物联网和以太网中如何保护信息成为关键。

67.相关技术中,信息加密是保障信息安全的主要手段。在信息加密技术中,硬件为加密提供不可预测性的随机数,以使得后续产生的密钥不可预测。目前,硬件随机数生成的方法主要基于亚稳态实现。

68.随机数生成主要是利用自然界中的物理噪声,比如器件噪声、核衰变噪声、布朗运动噪声、热噪声等,通过对这些噪声进行放大、提取、后处理得到不可预测的0/1序列。其中,

提取步骤通过亚稳态实现。如图1所示,用于提取的电路主要可以分为两类,一类是转换为电压域的亚稳态,最终高(high)于电压阈值(ref0)的电压是1,低(low)于电压阈值(ref0)的电压是0;另一类是转换为时间域的亚稳态,领先(early)于时间阈值(ref1)的脉冲是0,落后(late)于时间阈值(ref1)的脉冲是1。这种亚稳态的方法受制程、电压和温度(process voltage and temperature,pvt)影响严重,因此需要付出额外的电路去校正影响。

69.图2是本公开实施例提供的一种随机数生成器的结构示意图。参见图2,所述随机数生成器包括:控制字提供电路10、脉冲产生电路20和随机数生成电路30。

70.其中,控制字提供电路10,响应于第一规则产生多个控制字;

71.脉冲产生电路20,与控制字提供电路10连接,响应于所述多个控制字,输出多路脉冲信号,所述脉冲信号包括第一频率信号和第二频率信号,所述第一频率信号和所述第二频率信号在所述脉冲信号中出现的概率由对应的所述控制字控制;

72.随机数生成电路30,与脉冲产生电路20连接,对所述多路脉冲信号逻辑运算,产生随机数序列。

73.在本公开实施例中,对脉冲子电路200响应于控制字产生的多路脉冲信号进行处理,产生随机数序列。该方案没有利用自然界中的随机噪声,完全通过数字电路产生,具有全数字、低成本、低功耗、高可靠性、高编程性的优点。另外,该随机数生成器先产生第一频率信号和第二频率信号的脉冲信号,然后将这些脉冲信号进行逻辑运算,使得输出的随机数序列具有不可预测性,也即本公开提供的随机数生成器能够输出真随机数,是一种产生真随机数的真随机数生成器(true random number generator,trng)。

74.在一种可能的实现方式中,第一规则可以是指从预定的控制字集合中随机输出多个控制字,也即控制字提供电路10从预定的控制字集合中随机输出多个控制字。

75.示例性地,控制字提供电路可以采用可编程芯片实现,通过编程,限定控制字集合,从而限定随机输出的控制字的范围,例如限定控制字的整数部分只能从3、5、7、11这些互质的数中产生,从而保证可编程芯片随机输出的都是互质的数。其中,可编程芯片可以包括多个输出通道,从而可以同时输出多个控制字。

76.在其他可能的实现方式中,第一规则也可以是其他规则,例如按照顺序选择控制字等,本公开对此不做限定。

77.参见图2,所述脉冲产生电路20,包括多个脉冲子电路200,多个脉冲子电路200分别与控制字提供电路10和随机数生成电路30连接。每个所述脉冲子电路200分别根据一个控制字产生一路所述脉冲信号。每路脉冲子电路200对应一个控制字。

78.图3示出了本公开实施例提供的一种脉冲子电路的结构示意图。参见图3,脉冲子电路200包括信号发生器201和频率合成器202。

79.频率合成器202分别与信号发生器201、控制字提供电路10和随机数生成电路30连接。

80.其中,信号发生器201响应于初始脉冲信号产生相位均匀间隔的基准脉冲信号。频率合成器202响应于相位均匀间隔的基准脉冲信号和控制字,产生所述脉冲信号。

81.其中,控制字包括第一系数和第二系数;脉冲信号包括基于相位均匀间隔的基准脉冲信号和第一系数产生所述第一频率信号和基于相位均匀间隔的基准脉冲信号和第二系数产生所述第二频率信号,脉冲信号中的第一频率信号和第二频率信号的占比由第二系

数控制。

82.在该实现方式中,脉冲子电路由2个部分组成,其中,信号发生器负责产生相位均匀间隔的基准脉冲信号,而频率合成器则负责根据相位均匀间隔的基准脉冲信号和控制字产生脉冲信号。

83.示例性地,初始脉冲信号可以采用压控振荡器产生,例如采用电感电容压控振荡器(lc voltage controlled oscillator,lcvco)作为振源产生上述初始脉冲信号。也即,该脉冲子电路还可以包括压控振荡器,压控振荡器的输出端与信号发生器的输入端电连接。不同的脉冲子电路采用不同的lcvco产生初始脉冲信号,然后经过不同的信号发生器,从而使得每个脉冲子电路中的相位均匀间隔的基准脉冲信号的初始相位和噪声特性不同,从而增加最终输出的不可预测性。

84.相位均匀间隔的基准脉冲信号是指,信号发生器201产生的多路脉冲信号的相位变化情况相同,且多路脉冲信号初始相位的间隔相等。

85.示例性地,信号发生器201可以为分频器,分频器用于根据初始脉冲信号产生多路相位均匀间隔的基准脉冲信号。

86.示例性地,信号发生器201还可以为交叉耦合与非门。

87.示例性地,信号发生器201还可以采用约翰逊计数器(johnson counter),又称扭环计数器实现。可替代地,信号发生器201采用环形行波振荡器(rotary traveling-wave oscillator,rtwo)实现,这是一种基于传输线的时钟生成技术,可以很方便的产生上述k路相位均匀间隔的基准脉冲信号。除此之外,信号发生器201还可以通过差分锁存器来实现。

88.图4为采用图3中的信号发生器产生的k路相位均匀间隔的基准脉冲信号的波形图。参见图4,任意两路信号的波形相同(即周期和幅度相同),且k路信号的波形均匀排布,也即间隔相同,任意两个相邻的信号之间的相位差为基本时间单元δ,k路信号的频率均为fi,k为大于2的整数。

89.在本公开实施例的一种实现方式中,频率合成器202,被配置为按照如下公式生成脉冲信号:t

taf

=(1-r)*ta r*tb,ta=i*δ,tb=(i 1)*δ,t

taf

=(1-r)*i*δ r*(i 1)*δ=(i r)*δ,控制字f=i r。

90.其中,t

taf

为脉冲信号的周期,ta为第一频率信号(或称为第一周期信号),tb为第二频率信号(或称为第二周期信号);i为前述第一系数,用于从k路基准脉冲信号中进行选择,以进行频率信号的合成,例如控制字i为3,则在一个周期内,从k路基准脉冲信号中选择出两路相位差为3δ的基准脉冲信号,进而合成并输出ta=3δ,在下一周期内,选择出两路相位差为4δ的基准脉冲信号,进而合成并输出tb=4δ,δ为k路相位均匀间隔的基准脉冲信号中的任意两个相邻信号之间的相位差;r为前述第二系数,用于控制第一频率信号和第二频率信号出现的概率,其中r控制tb出现的概率,1-r控制ta出现的概率。

91.在本公开实施例中,控制字均可以为整数或小数,每个控制字可以拆分为整数部分和小数部分,可以采用整数部分作为前述第一系数,小数部分作为前述第二系数,实现脉率信号的合成。例如,控制字为5.4,则整数部分为5,小数部分为0.4。再例如,控制字为6,则整数部分为6,小数部分为0。

92.在这种情况下,当控制字中的小数部分为0时,脉冲信号则只由ta一个周期信号构成。另外,当控制字中小数部分的数值不同时,脉冲信号中ta和tb出现的比例也不相同。

93.在一种可能的实现方式中,所述多个控制字的整数部分互为质数。

94.如果控制字的整数部分不互质,则不同脉冲子电路中产生的ta周期是倍数关系,从而导致不同脉冲子电路中ta部分存在相同波形,从而导致在后续逻辑运算时,不同脉冲信号之间可能存在间歇性地相同波形,从而导致这些时间中的逻辑运算结果一致,无法达到随机性要求。本公开通过让控制字的整数部分互质,可以避免上述情况的出现,保证了随机数序列的随机性,进一步提高噪声源熵值。

95.在其他实现方式中,各个控制字的整数部分也可以不互质。

96.图5为采用频率合成器进行脉冲信号合成的原理示意图。参见图5,该频率合成器利用时间平均频率概念来合成输出脉冲信号。下面以第一频率信号的合成为例进行说明:频率合成器接收控制字和k路相位均匀间隔的基准脉冲信号。控制字f=i r,其中i是整数部分,r是小数部分;k路相位均匀间隔的基准脉冲信号中的任意两个相邻的信号之间的相位差为基本时间单元δ。频率合成器首先根据基本时间单元δ和控制字f中的整数部分i,构建两种不同的时钟周期ta和tb,ta=i

·

δ,tb=(i 1)

·

δ。之后,频率合成器基于控制字f中的小数部分r,控制ta和tb出现的概率,从而产生脉冲信号,脉冲信号即包括前述时钟周期ta和tb两部分。

97.图6为本公开提供的一种频率合成器的结构示意图。参见图6,频率合成器可以包括第一处理单元21、第二处理单元22以及输出单元23。

98.第一处理单元21,与控制字提供电路10连接,基于控制字分别产生第一控制信号和第二控制信号;

99.第二处理单元22,与第一处理单元21连接,基于第一控制信号从相位均匀间隔的基准脉冲信号中选出第一脉冲信号,以及基于第二控制信号从所述基准脉冲信号中选出第二脉冲信号,并从第一脉冲信号和第二脉冲信号中选择一个作为输出信号;

100.输出单元23,与第二处理单元22连接,基于第二处理单元22的输出信号产生所述脉冲信号。

101.下面结合图6对第一处理单元21、第二处理单元22以及输出单元23的详细工作过程进行说明:

102.第一处理单元21包括第一逻辑控制电路24、第二逻辑控制电路25。

103.参考图6,第一逻辑控制电路24包括第一加法器241、第一寄存器242和第二寄存器243,第一寄存器242分别与第一加法器241和第二寄存器243连接。

104.第一加法器241将控制字f和第一寄存器242存储的最高有效位(most significant bits,例如,5比特)相加,然后在第二时钟信号clk2的上升沿时将相加结果保存到第一寄存器242中;或者,第一加法器241可以将控制字f和第一寄存器242存储的所有信息相加,然后在第二时钟信号clk2的上升沿时将相加结果保存到第一寄存器242中。在第二时钟信号clk2的下一个上升沿时,第一寄存器242存储的最高有效位将被存储到第二寄存器243中,作为第一k

→

1多路复用器221的选择信号,也即前述第一控制信号,用于从k路相位均匀间隔的基准脉冲信号中选择一路信号作为第一脉冲信号。

105.在将控制字f和第一寄存器242存储的最高有效位相加时,如果控制字进位,则存入第二寄存器243的最高有效为i 1,如果相加时控制字未发生进位,则存入第二寄存器243的最高有效为i。当第二寄存器243中为i 1时,对应输出的是tb=(i 1)

·

δ,当第二寄存器

243中为i时,对应输出的是ta=i

·

δ。

106.第二逻辑控制电路25包括第二加法器251、第三寄存器252和第四寄存器222。第三寄存器252分别与第二加法器251以及第四寄存器222连接。

107.第二加法器251将控制字的一半f/2和第一寄存器242存储的最高有效位相加,然后在第二时钟信号clk2的上升沿时将相加结果保存到第三寄存器252中。在第一时钟信号clk1的下一个上升沿时,第三寄存器252存储的信息将被存储到第四寄存器222中,并作为第二k

→

1多路复用器222的选择信号,也即前述第二控制信号,用于从k个多相位输入信号中选择一路信号作为第二脉冲信号。参考图6,第二处理单元22包括第一k

→

1多路复用器221、第二k

→

1多路复用器222和2

→

1多路复用器223。第一k

→

1多路复用器221和第二k

→

1多路复用器222分别包括用于多个输入端、控制输入端和输出端。2

→

1多路复用器223包括控制输入端、输出端、第一输入端和第二输入端。第一k

→

1多路复用器221的输出端和2

→

1多路复用器223的第一输入端连接,第二k

→

1多路复用器222的输出端和2

→

1多路复用器223的第二输入端连接。

108.第一k

→

1多路复用器221的控制输入端在第一逻辑控制电路24产生的第一控制信号的控制下,从k路相位均匀间隔的基准脉冲信号中选择一路信号作为输出信号,也即第一脉冲信号;第二k

→

1多路复用器222的控制输入端在第二逻辑控制电路25产生的第二控制信号控制下,从k路相位均匀间隔的基准脉冲信号中选择一路信号作为输出信号,也即第二脉冲信号。

109.以第一k

→

1多路复用器为例,在选择输出信号时,可以根据第一控制信号的数值选择,例如,第一控制信号为3,则选择k路相位均匀间隔的基准脉冲信号中的第3路作为输出。

[0110]2→

1多路复用器223可以在第一时钟信号clk1的上升沿时,选择来自第一k

→

1多路复用器221输出的第一脉冲信号和来自第二k

→

1多路复用器222输出的第二脉冲信号中的一个,作为2

→

1多路复用器223的输出信号。

[0111]

由于2

→

1多路复用器是在2个k

→

1多路复用器的输出中进行选择的,2个k

→

1多路复用器的输出拼合形成新的周期,由于2个k

→

1多路复用器的输出的第一脉冲信号和第二脉冲信号间相差整数个δ,使得最终频率合成器输出的脉冲信号中存在ta和tb两个不同的周期。

[0112]

参考图6,输出单元23包括触发电路。触发电路用于生成脉冲串。触发电路包括d触发器231、第一反相器232和第二反相器233。d触发器231包括数据输入端、时钟输入端和输出端。第一反相器232包括输入端和输出端。第二反相器233包括输入端和输出端。d触发器231的时钟输入端与2

→

1多路复用器223连接,d触发器231的数据输入端与第一反相器232的输出端连接,d触发器231的输出端分别与第一反相器232的输入端和第二反相器233的输入端连接。d触发器231的输出端或第二反相器233的输出端可以作为频率合成器的输出端,也即产生脉冲信号的一端。

[0113]

d触发器231的时钟输入端接收来自2

→

1多路复用器223的输出端的输出,并通过输出端输出第一时钟信号clk1;第一反相器232的输入端接收第一时钟信号clk1,并将输出信号输出给d触发器231的数据输入端;第二反相器233的输入端接收第一时钟信号clk1,并通过输出端输出第二脉冲信号clk2。

[0114]

第一时钟信号clk1连接到2

→

1多路复用器223的控制输入端,第一反向器232的输出端连接到d触发器231的数据输入端。

[0115]

其输出的脉冲信号的频率fo与控制字f的关系如图7所示,二者的关系为fo=1/(f

·

δ),可以看出在相位差δ一定的情况下,频率fo与控制字f成反比,也即控制字越大频率越小。

[0116]

图8示出了本公开实施例提供的一种随机数生成电路的结构示意图。参见图8,随机数生成电路30包括第一处理子电路301和第二处理子电路302。

[0117]

第一处理子电路301和脉冲产生电路20连接,对多路脉冲信号进行第一处理,其中,所述第一处理包括异或、同或、与非中的至少一种;

[0118]

第二处理子电路302和第一处理子电路301连接,对第一处理后的多路脉冲信号进行第二处理;

[0119]

其中,第二处理包括基于时钟信号,对第一处理子电路301输出的信号进行采样,得到随机数序列。

[0120]

在该实现方式中,利用第一处理子电路对多路脉冲信号进行异或、同或等逻辑运算,然后进行采样,以提高输出信号中比特的熵值,保证信号的随机性。

[0121]

图9示出了本公开实施例提供的一种随机数生成电路的详细示意图,参见图9,第一处理子电路301可以包括异或子电路。异或子电路对所述多路脉冲信号进行异或运算。

[0122]

其中,异或子电路可以将多个脉冲信号按照如下公式计算:a

⊕b⊕c⊕…⊕

n,其中a~n表示多路脉冲信号。

[0123]

在其他实现方式中,第一处理子电路301还可以包括多个逻辑运算子电路,例如将部分脉冲信号进行异或处理,将另一部分脉冲信号进行同或处理,最后将异或处理结果和同或处理结果进行与非作为输出。

[0124]

如图9所示,在一种可能的实现方式中,第二处理子电路302可以包括采样子电路,采样子电路和前述异或子电路连接,采样子电路基于时钟信号,对所述异或子电路输出的信号进行采样,得到所述随机数序列。

[0125]

如图9所示,脉冲产生电路20具有n个频率合成器,通过控制各自的控制字f

1-fn来生成不同频率的脉冲,再通过第一处理子电路使所有波形通过逻辑运算合成在一起,生成一个具有高度不可预测性的波形。该波形的不可预测性主要来源于两点。第一,向每个频率合成器输入的k路基准脉冲信号,每个频率合成器输入的基准脉冲信号具有不同的噪声特效和初始相位,其中噪声会影响波形,例如理想状态信号的周期20ms,由于噪声存在,可能有的19ms,有的21ms,进而造成波形不同;另外,不同的频率合成器的k路输入是采用不同的电路产生的,不同的电路可以生成噪声和初始相位不同的输入波形,其中,初始相位和电路内电容残余的电量相关,不同的电路开机时电容残余的电量不同导致初始相位不同;第二,每个频率合成器的输出和初始相位不同。正是由于以上原因混频后的波形具有极高的不可预测性和异常性。

[0126]

参见图8和图9,所述随机数生成电路30还包括时钟子电路303。

[0127]

时钟子电路303与第二处理子电路302连接,向第二处理子电路302用于提供所述时钟信号。

[0128]

示例性地,所述时钟子电路303用于采用所述多个脉冲子电路中的一个的输出作

为所述时钟信号;

[0129]

或者,所述时钟子电路303用于采用外部时钟的输出作为所述时钟信号。

[0130]

在一种可能的实现方式中,该时钟子电路303可以获取外部时钟的时钟信号,然后输出给第二处理子电路302。

[0131]

在另一种可能的实现方式中,该频率合成器可以获取脉冲产生电路20中的n个频率合成器中的一个(例如频率合成器c#)的脉冲信号,然后作为时钟信号输出给第二处理子电路302,这种实现方式中,提供时钟信号的频率合成器可以具有不固定性。例如,基于n个频率合成器产生的时钟信号的频率,采用n个频率合成器产生的脉冲信号中频率最小的频率合成器提供时钟信号。

[0132]

在采用上述时钟信号时,该时钟信号的上升沿或者下降沿并非周期排布的,因此,采用该时钟信号可以增加采用的随机性。在按照上述时钟信号,对第一处理子电路的输出进行采样过程中经常发生亚稳态,又进一步增加了随机数的不可预测性。其中,采样过程中发生亚稳态是指采样点正好处于第一处理子电路的输出信号的上升沿或下降沿造成的亚稳态,此时采样子电路输出0或1具有随机性。

[0133]

示例性地,所述采样子电路包括d触发器(d-flip flop,dff)。d触发器的输入端与第一处理子电路301连接,d触发器的控制端连接时钟子电路303。

[0134]

图10是本公开实施例提供的另一种随机数生成器的结构示意图。参见图10,所述随机数生成器还包括后处理电路40。

[0135]

后处理电路40与随机数生成电路30连接,对所述随机数生成电路输出的随机数序列进行概率偏差校正。

[0136]

其中概率偏差是指随机数序列中比特0和1出现的概率与真随机情况下0和1出现的概率间的偏差,通过对随机数序列进行概率偏差校正,使得随机数生成电路输出的随机数序列中比特0和1的比例更接近1:1,并且使得比特0和1的排列顺序更符合随机分布,从而增加随机序列的混乱度和复杂度。

[0137]

为了不将随机数直接暴露给上层应用,同时又增加随机数的信息复杂度,该随机数生成器中设计有前述后处理电路,该后处理电路可以使用不同的算法,包括冯诺依曼校正算法,哈希算法,混沌算法中至少一种。其中,不直接暴露给上层应用,是指不直接将采样的结果输出给加密的应用。如果随机数直接暴露,可能存在被破解的风险。

[0138]

不同算法具有不同的针对性,比如原随机数中的0/1分布不均匀,可以使用混沌算法中的xor校正,校正后的随机数序列0/1概率趋于0.5分布。本公开后处理电路利用上述算法中的一种,提高随机数序列的随机性。

[0139]

图11示出了本公开实施例提供的一种后处理电路的结构示意图,该方案的特点是电路非常小,具有较小的面积与功耗。参见图11,所述后处理电路40,包括存储模块401、处理模块402和运算模块403。

[0140]

存储模块401,存储随机序列;

[0141]

处理模块402,分别与随机数生成电路30和存储模块401连接,基于随机数生成电路30输出的随机数和存储模块401的随机序列中的一位,生成第一随机数;

[0142]

运算模块403,与处理模块402连接,将处理模块402输出的所述第一随机数和所述运算模块403上一周期输出的第二随机数进行逻辑运算,输出第三随机数。

[0143]

通过将随机数生成电路30输出的随机数和随机序列中的一位进行运算,然后再与上一周期输出的第二随机数进行逻辑运算,由于随机序列具有随机性,使得通过上述处理后得到的随机数序列中比特0和1更具有随机性。

[0144]

示例性地,存储模块401可以包括移位寄存器,移位寄存器存储随机序列,并在每个周期将所述随机序列右移一位,所述每个周期内所述随机数生成电路输出所述随机数序列的一位。

[0145]

示例性地,处理模块402可以包括解复用器,解复用器基于所述随机数生成电路输出的随机数和所述移位寄存器的最后一位,生成第一随机数,并将生成的所述第一随机数输入到所述移位寄存器的第一位。

[0146]

示例性地,运算模块403可以包括异或器,异或器对所述解复用器输出的所述第一随机数和所述异或器在上一周期输出的第二随机数进行异或,输出第三随机数。

[0147]

如图11所示,移位寄存器中存储有序列zn-1

…

zn-k。在时钟信号ck控制下,每周期向右移动一位,新加入移位寄存器的比特由解复用器的输出zn替代zn-1。zn由移位寄存器的最后1位,zn-k与随机数生成电路的输出bn作为输出计算得到。同时,解复用器的输出zn作为异或器的一个输入,异或器的另一个输入为异或器上一个周期的输出an-1,将zn和an-1异或,得到an。为了存储an-1,该后处理电路40还可以包括一个寄存器404,寄存器404可以在时钟信号ck的作用下,每个时钟周期获取异或器的输出并存储,并在下一时钟周期将存储的比特与解复用器的输出一起输入到异或器中。

[0148]

其中,控制移位寄存器的时钟信号和控制寄存器的时钟信号,均可以由前述时钟子电路提供。当然,在其他实现方式中,控制移位寄存器的时钟信号和控制寄存器的时钟信号也可以分别由2个独立的时钟电路提供。

[0149]

在该实现方式中,解复用器通过输出电路输出的随机数和移位寄存器的最后一位确定本次输出,由于移位寄存器的初始值是随机得到的(移位寄存器上电时会在每一位随机生成比特0或1),所以将输出电路输出的随机数和移位寄存器的初始值进行运算,加强了随机数的混沌性,进一步打乱了比特0和1的顺序;异或器实现前述xor校正,通过比较解复用器的输出和自身上一周期的输出的异同进行输出,避免出现连续的0或者1,因为如果是持续的11111,则异或后会产生01010的结果,使得0和1更平均。

[0150]

通过上述两个器件的作用,尽量保证不要一直出现0或一直出现1,使得0和1的数量更平均,且顺序随机。

[0151]

可选地,所述解复用器,用于按照如下公式计算所述第一随机数:

[0152]

zn=bn*zn-k bn-1

*zn-k-1

;

[0153]

其中,zn为所述第一随机数,zn-k为所述移位寄存器的最后一位,bn为所述随机数生成电路输出的随机数。

[0154]

其中,bn-1

为bn的逆运算,zn-k-1

为zn-k的逆运算。0的逆是1,1的逆是0。例如,bn为1,zn-k为1,则zn=1;bn为1,zn-k为0,则zn=0;bn为0,zn-k为1,则zn=0;bn为0,zn-k为0,则zn=1。

[0155]

利用该方法实现的随机数生成器通过全部美国国家标准与技术研究院(national institute of standards and technology,nist)随机数测试(随机数测试国际标准),将该随机数生成器输出的随机数图形化,如图12所示。通过对图12示出的随机数序列中设定

长度的比特序列的各种组合方式进行统计,可以看出各种组合方式出现的次数相近,也即各个组合方式的比例相当,没有明显多或少的情况,该随机数序列趋近于白噪声,说明其是不可预测的真随机数序列。在统计各种组合出现的次数时,可以采用快速傅立叶变换实现,例如,对图12示出的随机数序列进行快速傅立叶变换,得到如图13所示的频谱信息示意图,其中横坐标为索引,每个索引对应设定长度的比特序列的一种组合,纵坐标为该索引对应的序列出现的次数,如图13所示,该测试数据中一共有大约5

×

106种序列,索引1对应的序列出现的次数为1.13

×

104,且其它索引值对应的序列出现的次数大多也在1

×

104到1.25

×

104之间,故从图13可以看出,各种比特序列出现的比例相当,图12提供的随机数序列为真随机数序列。

[0156]

本案提出一种全数字、低成本、低功耗、高可靠性、高编程性可重用的随机数生成器,它基于多个频率合成器实现,将多个频率合成器输出的脉冲信号通过逻辑运算混频,形成一个高熵的噪声源,再通过d触发器采样,生成一串真随机数序列,为了增强真随机数序列的复杂度,再为电路添加一个后处理电路。该架构生成的真随机数通过nist随机数测试,并且具有高熵、高不可预测性、高复杂度等特点。该随机数生成器可以集成在芯片中,通过低成本的方法提供高效可靠的真随机数。

[0157]

图14示出了本公开实施例提供的一种随机数生成方法的流程图。参见图14,该方法包括:

[0158]

步骤501:响应于第一规则产生多个控制字;

[0159]

步骤502:响应于所述多个控制字,输出多路脉冲信号,所述脉冲信号包括第一频率信号和第二频率信号,所述第一频率信号和所述第二频率信号在所述脉冲信号中出现的概率由对应的所述控制字控制;

[0160]

可选地,所述响应于所述多个控制字,输出多路脉冲信号,包括:

[0161]

响应于初始脉冲信号产生相位均匀间隔的基准脉冲信号;

[0162]

响应于所述基准脉冲信号和所述控制字,产生所述脉冲信号;

[0163]

其中,所述控制字包括第一系数和第二系数;

[0164]

所述脉冲信号包括基于所述基准脉冲信号和第一系数产生的所述第一频率信号和基于所述基准脉冲信号和第一系数产生的所述第二频率信号,所述脉冲信号中的所述第一频率信号和所述第二频率信号的占比由所述第二系数控制。

[0165]

示例性地,按照如下公式生成脉冲信号:t

taf

=(1-r)*ta r*tb,ta=i*δ,tb=(i 1)*δ,t

taf

=(1-r)*i*δ r*(i 1)*δ=(i r)*δ,控制字f=i r。

[0166]

其中,t

taf

为脉冲信号的周期,ta为第一频率信号(或称为第一周期信号),tb为第二频率信号(或称为第二周期信号);i为前述第一系数,用于从k路基准脉冲信号中进行选择,以进行频率信号的合成,例如控制字i为3,则在一个周期内,从k路基准脉冲信号中选择出两路相位差为3δ的基准脉冲信号,进而合成并输出ta=3δ,在下一周期内,选择出两路相位差为4δ的基准脉冲信号,进而合成并输出tb=4δ,δ为k路相位均匀间隔的基准脉冲信号中的任意两个相邻信号之间的相位差;r为前述第二系数,用于控制第一频率信号和第二频率信号出现的概率,其中r控制tb出现的概率,1-r控制ta出现的概率。

[0167]

步骤503:对所述多路脉冲信号进行逻辑运算,产生随机数序列。

[0168]

可选地,对所述多路脉冲信号进行逻辑运算,产生随机数序列,包括:

[0169]

对所述多路脉冲信号进行第一处理,其中,所述第一处理包括异或、同或、与非中的至少一种;

[0170]

对所述第一处理后的多路脉冲信号进行第二处理;其中,第二处理包括基于时钟信号,对所述第一处理输出的信号进行采样,得到所述随机数序列。

[0171]

可选地,所述方法还包括:

[0172]

对所述随机数生成电路输出的随机数序列进行概率偏差校正。

[0173]

示例性地,对所述随机数生成电路输出的随机数序列进行概率偏差校正,包括:

[0174]

基于产生的所述随机数序列和随机序列中的一位,生成第一随机数;

[0175]

将所述第一随机数和上一周期输出的第二随机数进行逻辑运算,输出第三随机数。

[0176]

下面提供一种对所述随机数生成电路输出的随机数序列进行概率偏差校正的示例,其过程如下:

[0177]

在移位寄存器中存储随机序列,并在每个周期将所述随机序列右移一位,所述每个周期内所述随机数生成电路输出所述随机数序列的一位;

[0178]

基于产生的所述随机数序列和所述移位寄存器的最后一位,生成第一随机数,并将生成的所述第一随机数输入到所述移位寄存器的第一位;

[0179]

对所述第一随机数和在上一周期输出的第二随机数进行异或,输出第三随机数。

[0180]

以上仅为本公开的示例性实施例,并不用以限制本公开,凡在本公开的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本公开所附权利要求书限定的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。