半导体存储装置

1.相关申请的引用

2.本技术基于2020年08月25日申请在先的日本专利申请第2020-141836号的优先权,且主张改优先权的利益,通过引用将其全部内容并入本文中。

技术领域

3.本实施方式涉及一种半导体存储装置。

背景技术:

4.已知一种半导体存储装置,其具备:衬底;多个导电层,沿与该衬底的表面交叉的方向积层;及半导体层,与这多个导电层对向。

技术实现要素:

5.一实施方式提供一种容易高集成化的半导体存储装置。

6.一实施方式的半导体存储装置具备:衬底;存储单元阵列,在与衬底的表面交叉的第1方向上与衬底分开设置;以及多个第1焊盘电极,沿与第1方向交叉的第2方向排列,设置于与第1方向及第2方向交叉的第3方向上远离存储单元阵列的位置上,且能用于输入向存储单元阵列写入的数据、及输出从存储单元阵列读出的数据。衬底具备沿第2方向交替排列的多个第1区域及多个第2区域。存储单元阵列具备:多个导电层,跨及多个第1区域及多个第2区域沿第2方向延伸,且沿第1方向排列;多个半导体层,设置于多个第1区域中,沿第1方向延伸,且与多个导电层对向;以及多个第1接点,设置于多个第2区域中,沿第1方向延伸,第1方向的一端比多个导电层更靠近衬底,且第1方向的另一端比多个导电层更远离衬底。将多个第1焊盘电极之中的一个第1焊盘电极在第2方向及第3方向上的中心位置、和最靠近该第1焊盘电极的第1接点在第2方向及第3方向上的中心位置,在第2方向及第3方向上的距离设为第1距离时,与多个第1焊盘电极对应的多个第1距离中的最大距离与最小距离之差为400nm以下。

7.一实施方式的半导体存储装置具备:衬底;存储单元阵列,在与衬底的表面交叉的第1方向上与衬底分开设置;多个第1焊盘电极,沿与第1方向交叉的第2方向排列,设置于与第1方向及第2方向交叉的第3方向上远离存储单元阵列的位置上,且能用于输入向存储单元阵列写入的数据、及输出从存储单元阵列读出的数据;多个第1驱动电路,分别与多个第1焊盘电极连接,且包含并联连接在第1焊盘电极与电压供给线之间的多个第1晶体管;以及多个第2驱动电路,分别与多个第1焊盘电极连接,且包含与第1焊盘电极连接的比较器。衬底具备:多个第1区域及多个第2区域,沿第2方向交替地排列;以及多个第3区域,设置于第3方向上远离多个第1区域及多个第2区域的位置上,且沿第2方向排列。存储单元阵列具备:多个导电层,跨及多个第1区域及多个第2区域沿第2方向延伸,且沿第1方向排列;多个半导体层,设置于多个第1区域中,沿第1方向延伸,且与多个导电层对向;以及多个第1接点,设置于多个第2区域中,沿第1方向延伸,第1方向的一端比多个导电层更靠近衬底,且第1方向

的另一端比多个导电层更远离衬底。多个第3区域分别包含构成多个第1驱动电路中的一个的多个晶体管、及构成多个第2驱动电路中的一个的多个晶体管。将多个第3区域中的一个第3区域在第2方向及第3方向上的中心位置、和最靠近该第3区域的第1接点在第2方向及第3方向上的中心位置,在第2方向及第3方向上的距离设为第1距离时,与多个第3区域对应的多个第1距离中的最大距离与最小距离之差为400nm以下。

8.根据所述构成,能够提供一种容易高集成化的半导体存储装置。

附图说明

9.图1是表示第1实施方式的存储器系统10的构成的示意性框图。

10.图2是表示第1实施方式的存储器系统10的构成例的示意性侧视图。

11.图3是表示第1实施方式的存储器系统10的构成例的示意性俯视图。

12.图4是表示第1实施方式的存储器裸片md的构成的示意性框图。

13.图5是表示第1实施方式的存储器裸片md的一部分构成的示意性电路图。

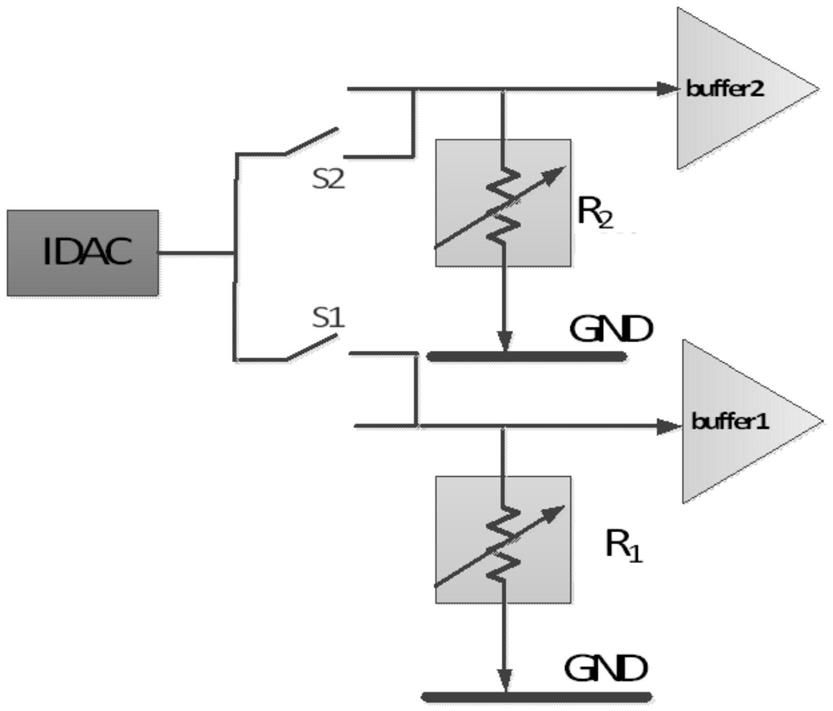

14.图6是表示第1实施方式的存储器裸片md的一部分构成的示意性电路图。

15.图7是表示第1实施方式的存储器裸片md的一部分构成的示意性电路图。

16.图8是表示第1实施方式的存储器裸片md的一部分构成的示意性电路图。

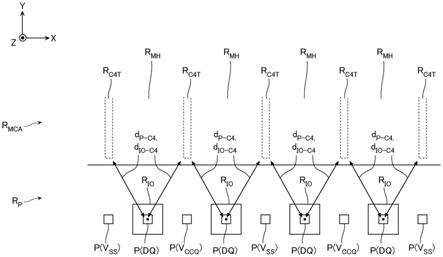

17.图9是第1实施方式的存储器裸片md的示意性俯视图。

18.图10是用a-a'线及b-b'线切断图9所示的构造,沿箭头的方向进行观察的示意性剖视图。

19.图11是放大表示图9中c所示的部分的示意性俯视图。

20.图12是放大表示图11中d所示的部分的示意性俯视图。

21.图13是用e-e'线切断图12所示的构造,沿箭头的方向进行观察的示意性剖视图。

22.图14是放大表示图13中f所示的部分的示意性俯视图。

23.图15是用g-g'线切断图11所示的构造,沿箭头的方向进行观察的示意性剖视图。

24.图16是放大表示图8的一部分的示意性俯视图。

25.图17是表示第1实施方式的存储器裸片md的一部分构成的示意性剖视图。

26.图18是表示第1实施方式的存储器裸片md的一部分构成的示意性剖视图。

27.图19是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

28.图20是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

29.图21是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

30.图22是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

31.图23是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

32.图24是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

33.图25是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

34.图26是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

35.图27是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

36.图28是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

37.图29是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

38.图30是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

39.图31是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

40.图32是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

41.图33是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

42.图34是表示第1实施方式的存储器裸片md的制造方法的示意性剖视图。

43.图35是表示另一实施方式的存储器裸片的一部分构成的示意性俯视图。

44.图36是表示另一实施方式的存储器裸片的一部分构成的示意性俯视图。

45.图37是用来对可搭载于第1实施方式的存储器裸片md及其它实施方式的存储器裸片上的晶体管的种类进行说明的示意性剖视图。

具体实施方式

46.参照附图详细说明实施方式的半导体存储装置。此外,以下实施方式仅为一例,并不带有限定本发明的意图。另外,以下附图是示意性图,为了便于说明,有时会省略一部分构成等。另外,有时对多个实施方式共通的部分标注相同的符号,并省略说明。

47.另外,在本说明书中,当采用“半导体存储装置”这种表述时,有时意指存储器裸片,有时也指存储器芯片、存储卡、ssd(solid state drive,固态驱动器)等包含控制器裸片的存储器系统。进而,有时还指智能手机、平板终端、个人计算机等包含主机的构成。

48.另外,在本说明书中,当采用“控制电路”这种表述时,有时意指设置于存储器裸片上的定序器等外围电路,有时也指与存储器裸片连接的控制器裸片或控制器芯片等,有时还指包含以上两种的构成。

49.另外,在本说明书中,当采用第1构成与第2构成“电连接”这种表述时,第1构成可与第2构成直接连接,第1构成也可经由配线、半导体部件或晶体管等与第2构成连接。例如,在将3个晶体管串联连接的情况下,即使第2个晶体管为断开(off)状态,第1个晶体管也与第3个晶体管“电连接”。

50.另外,在本说明书中,当采用第2构成与第3构成之“间连接有”第1构成这种表述时,有时意指第1构成、第2构成及第3构成串联连接,且第2构成经由第1构成与第3构成连接。

51.另外,在本说明书中,当采用电路等使2条配线等“导通”这种表述时,有时例如意指该电路等包含晶体管等,该晶体管等设置于2条配线之间的电流路径上,且该晶体管等为导通(on)状态。

52.另外,在本说明书中,将与衬底的上表面平行的指定方向称为x方向,将与衬底的上表面平行且与x方向垂直的方向称为y方向,将与衬底的上表面垂直的方向称为z方向。

53.另外,在本说明书中,有时将沿着指定面的方向称为第1方向,将沿该指定面且与第1方向交叉的方向称为第2方向,将与该指定面交叉的方向称为第3方向。所述第1方向、第2方向及第3方向可对应于x方向、y方向及z方向中的任一方向,也可不对应。

54.另外,在本说明书中,“上”或“下”等表述是以衬底为基准。例如,将沿所述z方向远离衬底的方向称为上,将沿z方向靠近衬底的方向称为下。另外,当针对某一构成采用下表面或下端这种表述时,意指该构成的衬底侧的面或端部,当采用上表面或上端这种表述时,意指该构成的与衬底相反侧的面或端部。另外,将与x方向或y方向交叉的面称为侧面等。

55.另外,在本说明书中,当针对构成、部件等采用指定方向的“宽度”、“长度”或“厚

度”、或者构成、部件间的“距离”等表述时,有时意指通过sem(scanning electron microscopy,扫描式电子显微镜)或tem(transmission electron microscopy,穿透式电子显微镜)等所观察到的剖面等上的宽度、长度或厚度、或者距离等。

56.[第1实施方式]

[0057]

[存储器系统10]

[0058]

图1是表示第1实施方式的存储器系统10的构成的示意性框图。

[0059]

存储器系统10根据由主机20发送的信号来进行用户数据的读出、写入、抹除等。存储器系统10例如为存储器芯片、存储卡、ssd或其它能够存储用户数据的系统。存储器系统10具备存储用户数据的多个存储器裸片md、以及与这多个存储器裸片md及主机20连接的控制器裸片cd。控制器裸片cd例如具备处理器、ram(random access memory,随机存取存储器)等,进行逻辑地址与物理地址的转换、比特错误检测/纠正、垃圾回收(压缩)、损耗均衡等处理。

[0060]

图2是表示本实施方式的存储器系统10的构成例的示意性侧视图。图3是表示本实施方式的存储器系统10的构成例的示意性俯视图。为了便于说明,在图2及图3中,省略一部分构成。

[0061]

如图2所示,本实施方式的存储器系统10具备安装衬底msb、积层在安装衬底msb上的多个存储器裸片md、及积层在存储器裸片md上的控制器裸片cd。在安装衬底msb的上表面中,y方向的端部区域设置有焊垫电极p,另有一部分区域经由粘接剂等粘接在存储器裸片md的下表面上。在存储器裸片md的上表面中,的y方向的端部区域设置有焊垫电极p,其它区域经由粘接剂等粘接在另一存储器裸片md或控制器裸片cd的下表面上。在控制器裸片cd的上表面中,y方向的端部区域设置有焊垫电极p。

[0062]

如图3所示,安装衬底msb、多个存储器裸片md及控制器裸片cd分别具备沿x方向排列的多个焊垫电极p。设置于安装衬底msb、多个存储器裸片md及控制器裸片cd上的多个焊垫电极p分别经由焊线b而相互连接。

[0063]

此外,图2及图3所示的构成仅为示例,具体构成可适当进行调整。例如,在图2及图3所示的例子中,多个存储器裸片md上积层有控制器裸片cd,这些构成由焊线b连接。在这种构成中,多个存储器裸片md与控制器裸片cd包含在同一个封装内。但控制器裸片cd也可与存储器裸片md包含在不同的封装内。

[0064]

[存储器裸片md的电路构成]

[0065]

图4是表示第1实施方式的存储器裸片md的构成的示意性框图。图5~图8是表示存储器裸片md的一部分构成的示意性电路图。

[0066]

此外,图4中示出了多个控制端子等。这多个控制端子有的是与高电平有效信号(正逻辑信号)对应的控制端子,有的是与低电平有效信号(负逻辑信号)对应的控制端子,有的是与高电平有效信号及低电平有效信号两者对应的控制端子。在图4中,与低电平有效信号对应的控制端子的符号包含上划线(overline)。在本说明书中,与低电平有效信号对应的控制端子的符号包含斜线(“/”)。此外,图4的记载为示例,具体形态可适当进行调整。例如,也可使一部分或全部高电平有效信号为低电平有效信号,或者使一部分或全部低电平有效信号为高电平有效信号。

[0067]

如图4所示,存储器裸片md具备存储数据的存储单元阵列mca、及与存储单元阵列

mca连接的外围电路pc。外围电路pc具备电压产生电路vg、行解码器rd、感测放大器模块sam、及定序器sqc。另外,外围电路pc具备高速缓冲存储器cm、地址寄存器adr、命令寄存器cmr、及状态寄存器str。另外,外围电路pc具备输入输出控制电路i/o、及逻辑电路ctr。

[0068]

如图5所示,存储单元阵列mca具备多个存储器区块blk。这多个存储器区块blk分别具备多个串单元su。这多个串单元su分别具备多个存储器串ms。这多个存储器串ms的一端分别经由位线bl与外围电路pc连接。另外,这多个存储器串ms的另一端分别经由共通的源极线sl与外围电路pc连接。

[0069]

存储器串ms具备串联连接在位线bl与源极线sl之间的漏极侧选择晶体管std、多个存储单元mc(存储器晶体管)、源极侧选择晶体管sts、及源极侧选择晶体管stsb。以下,有时将漏极侧选择晶体管std、源极侧选择晶体管sts、及源极侧选择晶体管stsb简称为选择晶体管(std、sts、stsb)。

[0070]

存储单元mc是具备作为通道区域发挥功能的半导体层、包含电荷蓄积膜的栅极绝缘膜、及栅极电极的场效应型晶体管。存储单元mc的阈值电压根据电荷蓄积膜中的电荷量而发生变化。存储单元mc存储1比特或多比特数据。此外,在与1个存储器串ms对应的多个存储单元mc的栅极电极上分别连接有字线wl。这些字线wl分别共通连接于1个存储器区块blk中的全部存储器串ms。

[0071]

选择晶体管(std、sts、stsb)是具备作为通道区域发挥功能的半导体层、栅极绝缘膜及栅极电极的场效应型晶体管。在选择晶体管(std、sts、stsb)的栅极电极上分别连接有选择栅极线(sgd、sgs、sgsb)。漏极侧选择栅极线sgd与串单元su对应设置,共通连接于1个串单元su中的全部存储器串ms。源极侧选择栅极线sgs共通连接于多个串单元su中的全部存储器串ms。源极侧选择栅极线sgsb共通连接于多个串单元su中的全部存储器串ms。

[0072]

电压产生电路vg(图4)例如包含调节器等降压电路及电荷泵电路等升压电路。这些降压电路及升压电路分别与被供给电源电压v

cc

及接地电压v

ss

的电压供给线连接。这些电压供给线例如与参照图2、图3所说明的焊垫电极p连接。电压产生电路vg例如按照来自定序器sqc的控制信号来产生对存储单元阵列mca进行读出动作、写入动作及抹除动作时要对位线bl、源极线sl、字线wl及选择栅极线(sgd、sgs、sgsb)施加的多种动作电压,并将它们同时输出至多条电压供给线。从电压供给线输出的动作电压可按照来自定序器sqc的控制信号适当调整。

[0073]

行解码器rd例如具备:地址解码器,对地址数据add进行解码;及开关电路,根据地址解码器的输出信号使存储单元阵列mca中的字线适当地与电压供给线导通。

[0074]

感测放大器模块sam例如具备与多条位线bl对应的多个感测放大器单元。感测放大器单元分别具备与位线bl连接的感测放大器。感测放大器具备与位线bl连接的感测电路、与位线bl连接的电压传送电路、以及与感测电路及电压传送电路连接的锁存电路。感测电路具备:感测晶体管,与位线bl的电压或电流相应地成为导通状态;及配线,与感测晶体管的导通/断开状态相应地被充电或放电。锁存电路根据该配线的电压来锁存“1”或“0”的数据。电压传送电路根据锁存在该锁存电路中的数据来使位线bl与2条电压供给线中的任一条导通。

[0075]

高速缓冲存储器cm具备经由配线dbus与感测放大器模块sam内的锁存电路连接的多个锁存电路。这多个锁存电路中包含的数据dat被依序传送至感测放大器模块sam或输入

输出控制电路i/o。另外,在高速缓冲存储器cm上连接有未图示的解码电路及开关电路。解码电路对保持在地址寄存器adr(图4)中的列地址ca进行解码。开关电路根据解码电路的输出信号使与列地址ca对应的锁存电路与总线db(图4)导通。

[0076]

定序器sqc(图4)按照保持在命令寄存器cmr中的命令数据d

cmd

将内部控制信号输出至行解码器rd、感测放大器模块sam及电压产生电路vg。另外,定序器sqc适当地将表示自身状态的状态数据d

st

输出至状态寄存器str。

[0077]

另外,定序器sqc产生就绪/忙碌信号,并将其输出至端子ry//by。在端子ry//by为“l”状态期间,基本上禁止访问存储器裸片md。另外,在端子ry//by为“h”状态期间,允许访问存储器裸片md。此外,端子ry//by例如通过参照图2、图3所说明的焊垫电极p来实现。

[0078]

输入输出控制电路i/o具备数据信号输入输出端子dq0~dq7、数据选通信号输入输出端子dqs、/dqs、及与数据信号输入输出端子dq0~dq7连接的比较器等输入电路及ocd电路等输出电路。另外,输入输出电路i/o具备与这些输入电路及输出电路连接的移位寄存器、以及缓冲电路。数据信号输入输出端子dq0~dq7及数据选通信号输入输出端子dqs、/dqs例如通过参照图2、图3所说明的焊垫电极p来实现。经由数据信号输入输出端子dq0~dq7输入的数据根据来自逻辑电路ctr的内部控制信号而从缓冲电路被输出至高速缓冲存储器cm、地址寄存器adr或命令寄存器cmr。另外,经由数据信号输入输出端子dq0~dq7输出的数据根据来自逻辑电路ctr的内部控制信号而从高速缓冲存储器cm或状态寄存器str被输入至缓冲电路。

[0079]

逻辑电路ctr经由外部控制端子/cen、cle、ale、/we、re、/re从控制器裸片cd接收外部控制信号,与其相应地将内部控制信号输出至输入输出控制电路i/o。此外,外部控制端子/cen、cle、ale、/we、re、/re例如通过参照图2、图3所说明的焊垫电极p来实现。

[0080]

图6是表示输入输出控制电路i/o的一部分构成的示意性框图。图7及图8是表示输入输出控制电路i/o的一部分构成的示意性电路图。

[0081]

例如,如图6所示,输入输出控制电路i/o具备与数据信号输入输出端子dq0~dq7连接的多个输入电路210、与数据选通信号输入输出端子dqs、/dqs连接的输入电路220、及与输入电路210、220连接的输入缓冲电路230。作为“第2驱动电路”,可包含输入电路210、输入电路220、及输入缓冲电路230。“第2驱动电路”可仅为输入电路210,也可仅为输入电路220,还可仅为输入缓冲电路230。

[0082]

例如,如图7所示,输入电路210具备与数据信号输入输出端子dq0~dq7连接的比较器211、及传输比较器211的输出信号的信号传输电路212。比较器211中,一输入端子与数据信号输入输出端子dq0~dq7中任一者连接,另一输入端子与供给参考电压vref的电压供给线连接。信号传输电路212传输比较器211的输出信号。由信号传输电路212传输的信号din是与经由数据信号输入输出端子dq0~dq7输入的数据等对应的信号。

[0083]

例如,如图7所示,输入电路220具备与数据选通信号输入输出端子dqs、/dqs连接的比较器221、及传输比较器221的输出信号的信号传输电路222、223。比较器221中,一输入端子与数据选通信号输入输出端子dqs连接,另一输入端子与数据选通信号输入输出端子/dqs连接。信号传输电路222、223传输比较器221的输出信号。由信号传输电路222、223传输的信号sig1、sig2是经由数据选通信号输入输出端子dqs、/dqs输入的数据选通信号。即,信号sig1、sig2是控制数据的获取时序的时序控制信号,也作为所谓时脉信号发挥功能。此

外,信号sig2是信号sig1的反相信号。

[0084]

例如,如图7所示,输入缓冲电路230具备锁存第偶数个数据的电路元件230e、及锁存第奇数个数据的电路元件230o。

[0085]

电路元件230e具备时控反相器231e、及锁存电路232e。时控反相器231e具备:pmos晶体管233e、234e,在供给电压v

ccq

的电压供给线与输出端子n1之间串联连接;及nmos晶体管235e、236e,在输出端子n1与供给接地电压vss的电压供给线之间串联连接。pmos晶体管233e的栅极电极与信号传输电路212的输出端子连接。pmos晶体管234e的栅极电极与信号传输电路223的输出端子连接。nmos晶体管235e的栅极电极与信号传输电路222的输出端子连接。nmos晶体管236e的栅极电极与信号传输电路212的输出端子连接。锁存电路232e具备反相器237e、238e。反相器237e的输入端子及反相器238e的输出端子与时控反相器231e的输出端子n1连接。反相器237e的输出端子及反相器238e的输入端子与未图示的fifo缓冲区等电路连接。

[0086]

电路元件230o具备时控反相器231o、及锁存电路232o。时控反相器231o具备:pmos晶体管233o、234o,在供给电压v

ccq

的电压供给线与输出端子n1之间串联连接;及nmos晶体管235o、236o,在输出端子n2与供给接地电压vss的电压供给线之间串联连接。pmos晶体管233o的栅极电极与信号传输电路212的输出端子连接。pmos晶体管234o的栅极电极与信号传输电路222的输出端子连接。nmos晶体管235o的栅极电极与信号传输电路223的输出端子连接。nmos晶体管236o的栅极电极与信号传输电路212的输出端子连接。锁存电路232o具备反相器237o、238o。反相器237o的输入端子及反相器238o的输出端子与时控反相器231o的输出端子n1连接。反相器237o的输出端子及反相器238o的输入端子与未图示的fifo缓冲区等电路连接。

[0087]

另外,例如,如图6所示,输入输出控制电路i/o具备与数据信号输入输出端子dq0~dq7连接的多个输出电路240、与数据选通信号输入输出端子dqs、/dqs连接的多个输出电路250、及与输出电路240连接的输出缓冲电路260。作为“第1驱动电路”,可包含输出电路250、及输出缓冲电路260。“第1驱动电路”可仅为输出电路250,也可仅为输出缓冲电路260。

[0088]

例如,如图8所示,输出电路240具备分别与数据信号输入输出端子dq0~dq7并联连接的7个ocd单元241、及与这7个ocd单元241连接的7个ocd单元控制电路242。

[0089]

7个ocd单元241例如分别具有240ω的阻抗。另外,7个ocd单元241分别与信号线ocd_en<6:0>连接,根据信号线ocd_en<6:0>控制被驱动的ocd单元241的数量。例如在信号0000001(按照16进制计,为01)输入至信号线ocd_en<6:0>的情况下,1个ocd单元241被驱动,输出电路240的阻抗z

drv

设定为240ω左右。另外,例如在信号0011111(按照16进制计,为1f)输入至信号线ocd_en<6:0>的情况下,5个ocd单元241被驱动,输出电路240的阻抗z

drv

设定为240ω/5=48ω左右。信号线ocd_en<6:0>的信号例如由用户来控制。

[0090]

ocd单元241分别具备上拉电路243,该上拉电路243连接在供给电压v

ccq

的电压供给线与数据信号输入输出端子dq0~dq7中任一者之间。另外,ocd单元241分别具备下拉电路244,该下拉电路244连接在数据信号输入输出端子dq0~dq7中任一者与供给接地电压vss的电压供给线之间。

[0091]

上拉电路243具备与数据信号输入输出端子dq0~dq7连接的电阻元件245、及并联连接在电阻元件245与供给电压v

ccq

的电压供给线之间的n 1(n为自然数)个晶体管246。晶

体管246是pmos晶体管。n 1个晶体管246具备互不相同的通道宽度及通道长度中至少一者,具有n 1种不同的电阻值。n 1个晶体管246的栅极电极分别与信号线up

※

<0>~up

※

<n>(

※

为0~6中任一数)连接。输入至信号线up

※

<0>~up

※

<n>的n 1比特数据会以使上拉电路243驱动时的阻抗为240ω左右的方式进行调整。

[0092]

下拉电路244具备与数据信号输入输出端子dq0~dq7连接的电阻元件247、及并联连接在电阻元件247与供给接地电压vss的电压供给线之间的m 1(m为自然数)个晶体管248。晶体管248是nmos晶体管。m 1个晶体管248分别具备不同的通道宽度及通道长度中至少一者,具有m 1种不同的电阻值。m 1个晶体管248的栅极电极分别与信号线dn

※

<0>~dn

※

<m>(

※

为0~6中任一数)连接。输入至信号线dn

※

<0>~dn

※

<m>的m 1比特的数据以下拉电路244驱动时的阻抗为240ω左右的方式进行调整。

[0093]

ocd单元控制电路242例如具备n 1个or电路251、及m 1个and电路252。

[0094]

n 1个or电路251的一输入端子与信号传输电路253的输出端子连接。信号传输电路253传输从数据信号输入输出端子dq0~dq7输出的“1”或“0”的信号。另外,与上拉电路243中所包含的n 1个晶体管246对应的n 1比特的数据pcode<n:0>中的对应的比特输入至n 1个or电路251的另一输入端子。另外,n 1个or电路251的输出端子分别与对应的晶体管246的栅极电极连接。

[0095]

m 1个and电路252的一输入端子与信号传输电路253的输出端子连接。另外,与下拉电路244中所包含的m 1个晶体管248对应的m 1比特的数据ncode<m:0>中的对应的比特输入至m 1个and电路252的另一输入端子。另外,m 1个and电路252的输出端子分别与对应的晶体管248的栅极电极连接。

[0096]

图6的输出电路250基本上与输出电路240同样地构成,具备与数据选通信号输入输出端子dqs、/dqs并联连接的7个ocd单元241、及与这7个ocd单元241连接的7个ocd单元控制电路242。但是,这些ocd单元241的输出端子与数据选通信号输入输出端子dqs或数据选通信号输入输出端子/dqs连接,而非与数据信号输入输出端子dq0~dq7中任一者连接。另外,信号传输电路253传输的是从数据选通信号输入输出端子dqs、/dqs输出的数据选通信号,而非从数据信号输入输出端子dq0~dq7输出的“1”或“0”的信号。

[0097]

[存储器裸片md的构造]

[0098]

图9是存储器裸片md的示意性俯视图。图10是用a-a'线及b-b'线切断图9所示的构造,沿箭头的方向进行观察的示意性剖视图。图11是放大表示图9中c所示的部分的示意性俯视图。图12是放大表示图11中d所示的部分的示意性俯视图。图13是用e-e'线切断图12所示的构造,沿箭头的方向进行观察的示意性剖视图。图14是放大表示图13中f所示的部分的示意性俯视图。图15是用g-g'线切断图11所示的构造,沿箭头的方向进行观察的示意性剖视图。

[0099]

例如,如图9所示,存储器裸片md具备半导体衬底100。在图示的例中,在半导体衬底100上设置有沿x方向及y方向排列的4个存储单元阵列区域r

mca

。另外,存储单元阵列区域r

mca

具备作为沿x方向排列的多个“第1区域”的存储器孔区域r

mh

、及作为设置在这些存储器孔区域r

mh

之间的多个“第2区域”的贯通接点区域r

c4t

。另外,在存储单元阵列区域r

mca

的x方向的两端部设置有接线区域r

hu

。另外,在半导体衬底100的y方向的端部设置有周边区域r

p

。另外,周边区域r

p

具备作为沿x方向排列的多个“第3区域”的输入输出电路区域r

io

。

[0100]

例如,如图10所示,存储器裸片md具备:半导体衬底100;晶体管层l

tr

,设置于半导体衬底100上;配线层d0,设置于晶体管层l

tr

的上方;配线层d1,设置于配线层d0的上方;配线层d2,设置于配线层d1的上方;存储单元阵列层l

mca

,设置于配线层d2的上方;配线层m0,设置于存储单元阵列层l

mca

的上方;配线层m1,设置于配线层m0的上方;及配线层m2,设置于配线层m1的上方。

[0101]

[半导体衬底100的构造]

[0102]

半导体衬底100例如为包含含有硼(b)等p型杂质的p型硅(si)的半导体衬底。例如,如图10所示,半导体衬底100的表面上设置有:n型阱区域100n,包含磷(p)等n型杂质;p型阱区域100p,包含硼(b)等p型杂质;半导体衬底区域100s,未设置n型阱区域100n及p型阱区域100p;以及绝缘区域100i。

[0103]

[晶体管层l

tr

的构造]

[0104]

例如,如图10所示,在半导体衬底100的上表面上,隔着未图示的绝缘层设置有配线层gc。配线层gc包含与半导体衬底100的表面对向的多个电极gc。另外,半导体衬底100的各区域及配线层gc中所包含的多个电极gc分别与接点cs连接。

[0105]

半导体衬底100的n型阱区域100n、p型阱区域100p及半导体衬底区域100s分别作为构成外围电路pc的多个晶体管tr的通道区域、及多个电容器cap的一电极等发挥功能。

[0106]

配线层gc中包含的多个电极gc分别作为构成外围电路pc的多个晶体管tr的栅极电极、及多个电容器cap的另一电极等发挥功能。

[0107]

接点cs沿z方向延伸,在下端与半导体衬底100或电极gc的上表面连接。在接点cs与半导体衬底100的连接部分设置有包含n型杂质或p型杂质的杂质区域。接点cs例如可包含氮化钛(tin)等的势垒导电膜和钨(w)等的金属膜的积层膜等。

[0108]

此外,在图示的例中,在从输入输出电路区域r

io

的z方向观察时与焊垫电极p重叠的区域中设置有电容器cap。另外,设置于输入输出电路区域r

io

中的多个晶体管tr例如作为构成参照图6~图8所说明的输入电路210、220、输入缓冲电路230、及输出电路240、250的多个晶体管发挥功能。

[0109]

[配线层d0、d1、d2的构造]

[0110]

例如,如图10所示,配线层d0、d1、d2中包含的多条配线与存储单元阵列mca中的构成及外围电路pc中的构成中至少一构成电连接。

[0111]

配线层d0、d1、d2分别包含多条配线d0、d1、d2。这多条配线d0、d1、d2例如可包含氮化钛(tin)等的势垒导电膜及钨(w)等的金属膜的积层膜等。

[0112]

此外,在图示的例中,在配线层d2的上表面上设置有氮化硅(sin)等的绝缘层104。绝缘层104跨及整个面而覆盖配线层d2中的构成。但是,绝缘层104未设置于贯通接点区域r

c4t

的至少一部分。

[0113]

[存储单元阵列层l

mca

的存储器孔区域r

mh

中的构造]

[0114]

例如,如图9所示,在存储单元阵列层l

mca

中设置有沿y方向排列的多个存储器区块blk。例如,如图11所示,存储器区块blk具备沿y方向排列的多个串单元su。在y方向上相邻的2个存储器区块blk之间设置有氧化硅(sio2)等的区块间绝缘层st。例如,如图12所示,在y方向上相邻的2个串单元su之间设置有氧化硅(sio2)等的串单元间绝缘层she。

[0115]

例如,如图13所示,存储器区块blk具备:多个导电层110,沿z方向排列;多个半导

体层120,沿z方向延伸;及多个栅极绝缘膜130,分别设置于多个导电层110与多个半导体层120之间。

[0116]

导电层110是沿x方向延伸的大致板状的导电层。导电层110可包含氮化钛(tin)等的势垒导电膜及钨(w)等的金属膜的积层膜等。另外,导电层110例如可包含含有磷(p)或硼(b)等杂质的多晶硅等。在沿z方向排列的多个导电层110之间设置有氧化硅(sio2)等的绝缘层101。

[0117]

在导电层110的下方设置有导电层111。导电层111例如可包含含有磷(p)或硼(b)等杂质的多晶硅等。另外,在导电层111与导电层110之间设置有氧化硅(sio2)等的绝缘层101。

[0118]

在导电层111的下方设置有导电层112。导电层112具备与半导体层120的下端连接的半导体层113、及与半导体层113的下表面连接的导电层114。半导体层113例如可包含含有磷(p)或硼(b)等杂质的多晶硅等。导电层114例如可包含钨(w)等金属、硅化钨等的导电层或其它导电层。另外,在导电层112与导电层111之间设置有氧化硅(sio2)等的绝缘层101。

[0119]

导电层112作为源极线sl(图5)发挥功能。例如针对存储单元阵列区域r

mca

(图9)中包含的全部存储器区块blk共通地设置有源极线sl。

[0120]

导电层111作为源极侧选择栅极线sgsb(图5)及与其连接的多个源极侧选择晶体管stsb的栅极电极发挥功能。导电层111于每个存储器区块blk中电独立。

[0121]

另外,多个导电层110中位于最下层的一个或多个导电层110作为源极侧选择栅极线sgs(图5)及与其连接的多个源极侧选择晶体管sts的栅极电极发挥功能。这多个导电层110于每个存储器区块blk中电独立。

[0122]

另外,位于比它更靠上方的多个导电层110作为字线wl(图5)及与其连接的多个存储单元mc(图5)的栅极电极发挥功能。这多个导电层110分别于每个存储器区块blk中电独立。

[0123]

另外,位于比它更靠上方的一个或多个导电层110作为漏极侧选择栅极线sgd及与其连接的多个漏极侧选择晶体管std(图5)的栅极电极发挥功能。这多个导电层110在y方向的宽度比其它导电层110小。另外,在y方向上相邻的2个导电层110之间设置有串单元间绝缘层she。这多个导电层110分别于每个串单元su中电独立。

[0124]

例如,如图12所示,半导体层120以指定图案沿x方向及y方向排列。半导体层120作为1个存储器串ms(图5)中包含的多个存储单元mc及选择晶体管(std、sts、stsb)的通道区域发挥功能。半导体层120例如为多晶硅(si)等的半导体层。例如,如图13所示,半导体层120具有大致有底圆筒状的形状,在中心部分设置有氧化硅等的绝缘层125。另外,半导体层120的外周面分别被导电层110包围,与导电层110对向。

[0125]

在半导体层120的上端部设置有包含磷(p)等n型杂质的杂质区域121。杂质区域121经由接点ch及接点vy(图12)与位线bl连接。

[0126]

在半导体层120的下端部设置有包含磷(p)等n型杂质的杂质区域122。杂质区域122与所述导电层112的半导体层113连接。半导体层120中位于杂质区域122正上方的部分作为源极侧选择晶体管stsb的通道区域发挥功能。杂质区域122的外周面被导电层111包围,与导电层111对向。

[0127]

栅极绝缘膜130具有覆盖半导体层120外周面的大致有底圆筒状形状。例如,如图14所示,栅极绝缘膜130具备积层在半导体层120与导电层110之间的隧道绝缘膜131、电荷蓄积膜132及阻挡绝缘膜133。隧道绝缘膜131及阻挡绝缘膜133例如为氧化硅(sio2)等的绝缘膜。电荷蓄积膜132例如为氮化硅(si3n4)等的能够蓄积电荷的膜。隧道绝缘膜131、电荷蓄积膜132、及阻挡绝缘膜133具有大致圆筒状的形状,沿着半导体层120的外周面沿z方向延伸。

[0128]

此外,图14示出了栅极绝缘膜130具备氮化硅等的电荷蓄积膜132的例子。然而,栅极绝缘膜130例如也可具备包含n型或p型杂质的多晶硅等的浮动栅极。

[0129]

[存储单元阵列层l

mca

的贯通接点区域r

c4t

中的构造]

[0130]

例如,如图11所示,在贯通接点区域r

c4t

中,在沿y方向排列的2个区块间绝缘层st之间设置有沿y方向排列的2个绝缘层sto。另外,在这2个绝缘层sto之间设置有接点连接小区域r

c4t

。另外,在区块间绝缘层st与绝缘层sto之间设置有导电层连接小区域r

110

。这些区域沿着区块间绝缘层st沿x方向延伸。

[0131]

例如,如图15所示,绝缘层sto沿z方向延伸,在下端与导电层112连接。绝缘层sto例如包含氧化硅(sio2)。

[0132]

接点连接小区域r

c4t

具备沿z方向排列的多个绝缘层110a、及作为沿z方向延伸的多个“第1接点”的接点c4。

[0133]

绝缘层110a是沿x方向延伸的大致板状的绝缘层。绝缘层110a可包含氮化硅(sin)等的绝缘层。在沿z方向排列的多个绝缘层110a之间设置有氧化硅(sio2)等的绝缘层101。

[0134]

例如,如图10所示,接点c4沿x方向排列有多个。接点c4可包含氮化钛(tin)等的势垒导电膜及钨(w)等的金属膜的积层膜等。接点c4的外周面分别被绝缘层110a及绝缘层101包围,与这些绝缘层110a及绝缘层101连接。此外,接点c4沿z方向延伸,在上端与配线层m0中的配线m0连接,在下端与配线层d2中的配线d2连接。

[0135]

例如,如图11所示,导电层连接小区域r

110

具备沿z方向排列的多个导电层110的窄宽部110

c4t

。x方向上相邻的2个存储器孔区域r

mh

中包含的多个导电层110经由该窄宽部110

c4t

而相互导通。

[0136]

[存储单元阵列层l

mca

的输入输出电路区域r

io

中的构造]

[0137]

例如,如图10所示,输入输出电路区域r

io

具备氧化硅(sio2)等的绝缘层103、及沿z方向延伸的多个接点c3。

[0138]

接点c3可包含氮化钛(tin)等的势垒导电膜及钨(w)等的金属膜的积层膜等。接点c3的外周面分别被绝缘层103包围,与这些绝缘层103连接。此外,接点c3沿z方向延伸,在上端与配线层m0中的配线m0连接,在下端与配线层d2中的配线d2连接。

[0139]

[配线层m0、m1、m2的构造]

[0140]

例如,如图10所示,配线层m0、m1、m2中包含的多条配线例如与存储单元阵列层l

mca

中的构成及晶体管层l

tr

中的构成中至少一构成电连接。

[0141]

配线层m0包含多条配线m0。这多条配线m0例如可包含氮化钛(tin)等的势垒导电膜及铜(cu)等的金属膜的积层膜等。此外,多条配线m0中的一部分配线m0作为位线bl(图5)发挥功能。例如,如图12所示,位线bl沿x方向及y方向延伸。另外,这多条位线bl分别与各串单元su中包含的1个半导体层120连接。

[0142]

配线层m1包含多条配线m1。这多条配线m1例如可包含氮化钛(tin)等的势垒导电膜及铜(cu)等的金属膜的积层膜等。

[0143]

配线层m2包含多条配线m2。这多条配线m2例如可包含氮化钛(tin)等的势垒导电膜及铝(al)等的金属膜的积层膜等。此外,多条配线m2中设置于周边区域r

p

的一部分配线m2作为焊垫电极p(图2、图3)发挥功能。

[0144]

[输入输出电路区域r

io

的配置]

[0145]

图16是放大表示图9的一部分的示意性俯视图。在周边区域r

p

中设置有沿x方向排列的多个焊垫电极p。另外,这多个焊垫电极p中作为数据信号输入输出端子dq0~dq7、或数据选通信号输入输出端子dqs、/dqs发挥功能的焊垫电极p(以下,有时称为“输入输出焊垫电极p(dq)”)设置于输入输出电路区域r

io

中。

[0146]

在图16的例中,多个焊垫电极p在y方向上的位置全部对齐。另外,多个输入输出焊垫电极p(dq)的x方向上的中心位置分别与x方向上相邻的2个贯通接点区域r

c4t

的x方向上的中间位置一致。即,在图16的例中,将从输入输出焊垫电极p(dq)的xy平面上的中心位置到最靠近该输入输出焊垫电极p(dq)的贯通接点区域r

c4t

中最靠近该输入输出焊垫电极p(dq)的接点c4的xy平面上的中心位置的距离设为距离d

p-c4

时,距离d

p-c4

在所有输入输出焊垫电极p(dq)中皆相同。

[0147]

此外,较理想为与所有输入输出焊垫电极p(dq)对应的所有距离d

p-c4

皆相同。然而,距离d

p-c4

有时会因为设计上的原因或制造误差等关系而不完全一致。在这种情况下,例如较理想为距离d

p-c4

的最大值与最小值之差为400nm以下。

[0148]

另外,在图16的例中,多个输入输出电路区域r

io

在y方向上的位置全部对齐。另外,多个输入输出电路区域r

io

的x方向上的中心位置分别与x方向上相邻的2个贯通接点区域r

c4t

的x方向上的中间位置一致。即,在图16的例中,将从输入输出电路区域r

io

的xy平面上的中心位置到最靠近该输入输出电路区域r

io

的贯通接点区域r

c4t

中最靠近该输入输出电路区域r

io

的接点c4的xy平面上的中心位置的距离设为距离d

io-c4

时,距离d

io-c4

在所有输入输出电路区域r

io

中皆相同。另外,例如沿y方向观察时,贯通接点区域r

c4t

与输入输出电路区域r

io

(输入输出焊垫电极p(dq))不重叠。即,沿y方向观察时,最靠近输入输出电路区域r

io

(输入输出焊垫电极p(dq))的接点c4与输入输出电路区域r

io

(输入输出焊垫电极p(dq))不重叠。此时,所有输入输出电路区域r

io

(输入输出焊垫电极p(dq))可配置为不与贯通接点区域r

c4t

沿y方向重叠。例如沿y方向观察时,贯通接点区域r

c4t

可与电源焊垫电极p(v

ss

)、p(v

ccq

)重叠。沿y方向观察时,贯通接点区域r

c4t

可配置为不与电源焊垫电极p(v

ss

)、p(v

ccq

)重叠。

[0149]

另外,例如,在图16中,可将电源焊垫电极p(v

ss

)、p(v

ccq

)与输入输出电路区域r

io

(输入输出焊垫电极p(dq))互换。即使如此,也可使距离d

io-c4

在所有输入输出电路区域r

io

中皆相同。

[0150]

此外,较理想为与所有输入输出电路区域r

io

对应的所有距离d

io-c4

皆相同。然而,距离d

io-c4

有时会因为设计上的原因或制造误差等关系而不完全一致。在这种情况下,例如较理想为距离d

io-c4

的最大值与最小值之差为400nm以下。

[0151]

[设置于输入输出电路区域r

io

中的晶体管tr]

[0152]

如上所述,在存储器裸片md的晶体管层l

tr

中设置有构成外围电路pc的多个晶体管tr。这多个晶体管tr包含被供给相对较大电压的高电压晶体管、及被供给相对较小电压的

低电压晶体管。低电压晶体管能够比高电压晶体管更高速地动作。

[0153]

另外,如上所述,在输入输出电路区域r

io

中设置有构成参照图6~图8所说明的输入电路210、220、输入缓冲电路230、及输出电路240、250的多个晶体管。作为这多个晶体管,采用如上所述的低电压晶体管。以下,有时将这种低电压晶体管中的n型晶体管称为晶体管tr

nl

,将p型晶体管称为晶体管tr

pl

。

[0154]

例如,如图17所示,n型晶体管tr

nl

设置于半导体衬底100的p型阱区域100p。晶体管tr

nl

具备:p型阱区域100p的一部分;氧化硅(sio2)等的栅极绝缘层141,设置于半导体衬底100的表面上;包含磷(p)或砷(as)等n型杂质的多晶硅(si)等的栅极电极部件142,设置于栅极绝缘层141的上表面上;包含钨(w)或硅化钨(wsi)等的栅极电极部件143,设置于栅极电极部件142的上表面上;氮化硅(si3n4)等的顶盖绝缘层144,设置于栅极电极部件143的上表面上;及氮化硅(si3n4)等的侧壁绝缘层145,设置于栅极电极部件142、栅极电极部件143及顶盖绝缘层144的x方向或y方向上的侧面上。此外,栅极电极部件142、143构成所述电极gc。

[0155]

另外,n型晶体管tr

nl

具备积层在半导体衬底100的表面、栅极绝缘层141的x方向或y方向上的侧面、侧壁绝缘层145的x方向或y方向上的侧面、及顶盖绝缘层144的上表面上的氧化硅(sio2)等的衬垫绝缘层146及氮化硅(si3n4)等的衬垫绝缘层147。

[0156]

另外,在n型晶体管tr

nl

上连接有沿z方向延伸的3个接点cs

nl

。接点cs

nl

例如可包含氮化钛(tin)等的势垒导电膜及钨(w)等的金属膜的积层膜等。3个接点cs

nl

中的一个接点cs

nl

贯通衬垫绝缘层147、衬垫绝缘层146及顶盖绝缘层144而与栅极电极部件143的上表面连接,作为晶体管tr

nl

的栅极电极的一部分发挥功能。3个接点cs

nl

中的两个接点cs

nl

贯通衬垫绝缘层147及衬垫绝缘层146而与半导体衬底200的表面连接,作为晶体管tr

nl

的源极电极或漏极电极发挥功能。

[0157]

另外,n型晶体管tr

nl

将半导体衬底100的表面上的与栅极电极部件142的对向面作为通道区域。另外,在半导体衬底100的表面上的与接点cs

nl

的连接部分中设置有杂质区域148。杂质区域148例如包含磷(p)或砷(as)等n型杂质。

[0158]

例如,如图18所示,p型晶体管tr

pl

基本上与n型晶体管tr

nl

同样地构成。

[0159]

但是,p型晶体管tr

pl

设置于n型阱区域100n中而非p型阱区域100p中。

[0160]

另外,p型晶体管tr

pl

具备设置于栅极绝缘层141与栅极电极部件142之间的氮化硅(sin)等的绝缘层151。

[0161]

另外,p型晶体管tr

pl

具备栅极电极部件152来代替栅极电极部件142。栅极电极部件152例如包含含有硼(b)等p型杂质的多晶硅等。

[0162]

另外,在p型晶体管tr

pl

上连接有3个接点cs

pl

来代替3个接点cs

nl

。这3个接点cs

pl

中与晶体管tr

pl

的漏极区域或源极区域连接的接点cs

pl

具备与半导体衬底100连接的半导体层153、与半导体层153连接的半导体层154、及与半导体层154连接的导电层155。半导体层153及半导体层154例如为由外延生长等方法形成的单晶硅(si)等的半导体层。半导体层154包含硼(b)等p型杂质。半导体层153可包含硼(b)等p型杂质,也可不包含硼(b)等p型杂质。在半导体层153中包含p型杂质的情况下,半导体层153中包含的p型杂质的杂质浓度小于半导体层154中包含的p型杂质的杂质浓度。导电层155例如可包含氮化钛(tin)等的势垒导电膜及钨(w)等的金属膜的积层膜等。

[0163]

另外,p型晶体管tr

pl

具备杂质区域158来代替杂质区域148。杂质区域158例如包含硼(b)等p型杂质。

[0164]

[制造方法]

[0165]

接着,参照图19~图34,对存储器裸片md的制造方法进行说明。图19~图21、图23、图25~图29、图31及图33是用来说明存储器裸片md的制造方法的示意性剖视图,表示与图13对应的剖面。图22、图24、图30、图32及图34是用来说明存储器裸片md的制造方法的示意性剖视图,表示与图15对应的剖面。

[0166]

制造本实施方式的存储器裸片md时,首先,在半导体衬底100上形成晶体管层l

tr

、配线层d0、配线层d1及配线层d2(图10)。另外,在配线层d2的上表面上形成绝缘层104及绝缘层101。

[0167]

接着,例如,如图19所示,在绝缘层101上形成导电层114、硅等的半导体层113a、氧化硅等的牺牲层113b、硅等的牺牲层113c、氧化硅等的牺牲层113d、硅等的半导体层113e、绝缘层101及导电层111。另外,交替地形成多个绝缘层101及多个绝缘层110a。该步骤例如通过cvd(chemical vapor deposition,化学气相沉积)等方法来进行。

[0168]

接着,例如,如图20所示,在与半导体层120对应的位置上形成多个存储器孔mh。存储器孔mh是沿z方向延伸,贯通绝缘层101及绝缘层110a、导电层111、半导体层113e、牺牲层113d、牺牲层113c及牺牲层113b,使半导体层113a的上表面露出的贯通孔。该步骤例如通过rie(reactive ion etching,反应性离子蚀刻)等方法来进行。

[0169]

接着,例如,如图21所示,在存储器孔mh的内周面形成栅极绝缘膜130、半导体层120及绝缘层125。在该步骤中,例如通过cvd等进行成膜,在存储器孔mh的内部形成非晶硅膜。另外,例如,通过退火处理等使该非晶硅膜的晶体结构改质。

[0170]

接着,例如,如图22所示,形成绝缘层sto。在该步骤中,例如,通过rie等方法在与绝缘层sto对应的位置上形成槽。另外,通过cvd等方法在该槽的内部形成绝缘层sto。

[0171]

接着,例如,如图23及图24所示,形成槽sta。槽sta是沿z方向及x方向延伸,在y方向上分割绝缘层101及绝缘层110a、导电层111、半导体层113e及牺牲层113d,且使牺牲层113c的上表面露出的槽。该步骤例如通过rie等方法来进行。

[0172]

接着,例如,如图25所示,在槽sta的y方向上的侧面上形成氮化硅等的保护膜stsw。在该步骤中,例如通过cvd等方法在槽sta的y方向上的侧面及底面上形成氮化硅等的绝缘膜。另外,通过rie等方法去除该绝缘膜中的覆盖槽sta底面的部分。

[0173]

接着,例如,如图26所示,去除牺牲层113b、113c、113d及栅极绝缘膜130的一部分,使半导体层120的一部分露出。该步骤例如通过湿式蚀刻等方法来进行。

[0174]

接着,例如,如图27所示,形成半导体层113。该步骤例如通过外延生长等方法来进行。

[0175]

接着,例如,如图28所示,去除保护膜stsw。该步骤例如通过湿式蚀刻等方法来进行。

[0176]

接着,例如,如图29及图30所示,经由槽sta而去除绝缘层110a。由此形成配设在z方向上的多个绝缘层101、及支持该绝缘层101的包含存储器孔mh内的构造(半导体层120、栅极绝缘膜130及绝缘层125)的中空构造。该步骤例如通过湿式蚀刻等方法来进行。此外,如图30所示,在该步骤中,接点连接小区域r

c4t

中也可残留绝缘层110a。

[0177]

接着,例如,如图31及图32所示,形成导电层110。该步骤例如通过cvd等方法来进行。

[0178]

接着,例如,如图33及图34所示,在槽sta内形成区块间绝缘层st。该步骤例如通过cvd及rie等方法来进行。

[0179]

其后,形成配线等,藉由切晶分割晶圆,由此形成存储器裸片md。

[0180]

[效果]

[0181]

如上所述,本实施方式的存储器裸片md具备多个输入输出焊垫电极p(dq)。此处,在时脉信号中的一定时序范围内将数据输入至存储器裸片md,将数据从存储器裸片md输出。因此,较理想为与多个输入输出焊垫电极p(dq)连接的多个电路(例如,参照图6~图8所说明的输入电路210、220、输入缓冲电路230、及输出电路240、250)全部以相同速度动作。

[0182]

此处,如参照图9所说明的那样,在本实施方式中,通过cvd等方法形成多个绝缘层110a及多个绝缘层101。以此方式形成的绝缘层110a有时含有氢。另外,进行参照图21所说明的热处理等时,这种氢有时会扩散。

[0183]

此处,参照图18所说明的晶体管tr

pl

的栅极电极部件152中包含硼(b)等p型杂质。当所述氢到达栅极电极部件152时,存在氢与硼发生反应,栅极电极部件152中的硅(si)与硼(b)的键断开的情况。另外,存在该硼(b)扩散至半导体衬底100,晶体管tr

pl

的阈值电压等特性发生变动的情况。

[0184]

为了抑制这种晶体管tr

pl

的特性变动,在第1实施方式的半导体存储装置中,在配线层d2的上表面上设置包含氮化硅(sin)等的绝缘层104(图10)。由此,能够大幅抑制存储单元阵列层l

mca

中的氢扩散至晶体管层l

tr

。

[0185]

然而,如上所述,有时贯通接点区域r

c4t

中存在未设置有绝缘层104的区域。在这种情况下,有时氢会从这种区域渗透至晶体管层l

tr

。另外,有时设置于晶体管层l

tr

的多个晶体管tr

pl

中与贯通接点区域r

c4t

的距离越小者,氢所导致的特性变动越大,与贯通接点区域r

c4t

的距离越大者,氢所导致的特性变动越小。在这种情况下,当氢产生的影响在多个输入输出电路区域r

io

之间有所差异时,在与多个输入输出焊垫电极p(dq)连接的多个电路之间,有动作速度不均的危险。

[0186]

因此,在第1实施方式的半导体存储装置中,例如,如参照图16等所说明的那样,使从输入输出电路区域r

io

的xy平面上的中心位置到最靠近该输入输出电路区域r

io

的贯通接点区域r

c4t

中最靠近该输入输出电路区域r

io

的接点c4的xy平面上的中心位置的距离d

io-c4

在所有输入输出电路区域r

io

中皆相同。根据这种构成,能够使如上所述的氢的影响在与多个输入输出焊垫电极p(dq)连接的多个电路之间统一为相同程度。由此,能够抑制在这多个电路之间动作速度发生不均。

[0187]

[其它实施方式]

[0188]

以上,参照图1~图34对第1实施方式的半导体存储装置进行说明。然而,这种构成仅为示例,具体构成等可适当进行调整。

[0189]

例如,如参照图16所说明的那样,在第1实施方式中,在x方向上相邻的2个贯通接点区域r

c4t

之间对应的位置上设置有1个输入输出焊垫电极p(dq)及与其对应的输入输出电路区域r

io

。然而,这种构成仅为示例,具体构成等可适当进行调整。例如,如图35所示,也可在x方向上相邻的2个贯通接点区域r

c4t

之间设置沿x方向排列的2个输入输出焊垫电极p

(dq)。

[0190]

此外,在图35的例中,将从输入输出焊垫电极p(dq)的xy平面上的中心位置到最靠近该输入输出焊垫电极p(dq)的贯通接点区域r

c4t

中最靠近该输入输出焊垫电极p(dq)的接点c4的xy平面上的中心位置的距离设为距离d

p-c4-35-1

时,距离d

p-c4-35-1

在所有输入输出焊垫电极p(dq)中皆相同。另外,在图35的例中,将从输入输出焊垫电极p(dq)的xy平面上的中心位置到第二靠近该输入输出焊垫电极p(dq)的贯通接点区域r

c4t

中最靠近该输入输出焊垫电极p(dq)的接点c4的xy平面上的中心位置的距离设为距离d

p-c4-35-2

时,距离d

p-c4-35-2

在所有输入输出焊垫电极p(dq)皆相同。

[0191]

此外,较理想为与所有输入输出焊垫电极p(dq)对应的所有距离d

p-c4-35-1

、d

p-c4-35-2

皆相同。然而,距离d

p-c4-35-1

、d

p-c4-35-2

有时会因为设计上的原因或制造误差等关系而不完全一致。在这种情况下,例如较理想为距离d

p-c4-35-1

、d

p-c4-35-2

的最大值与最小值之差为400nm以下。

[0192]

另外,在图35的例中,将从输入输出电路区域r

io

的xy平面上的中心位置到最靠近该输入输出电路区域r

io

的贯通接点区域r

c4t

中最靠近该输入输出电路区域r

io

的接点c4的xy平面上的中心位置的最短距离设为距离d

io-c4-35-1

时,距离d

io-c4-35-1

在所有输入输出电路区域r

io

中皆相同。另外,在图35的例中,将从输入输出电路区域r

io

的xy平面上的中心位置到第二靠近该输入输出电路区域r

io

的贯通接点区域r

c4t

中最靠近该输入输出电路区域r

io

的接点c4的xy平面上的中心位置的最短距离设为距离d

io-c4-35-2

时,距离d

io-c4-35-2

在所有输入输出电路区域r

io

中皆相同。

[0193]

此外,较理想为与所有输入输出电路区域r

io

对应的所有距离d

io-c4-35-1

、d

io-c4-35-2

皆相同。然而,距离d

io-c4-35-1

、d

io-c4-35-2

有时会因为设计上的原因或制造误差等关系而不完全一致。在这种情况下,例如较理想为距离d

io-c4-35-1

、d

io-c4-35-2

的最大值与最小值之差为400nm以下。

[0194]

此外,当采用图35这种配置时,关于从x方向开始数第偶数个输入输出电路区域r

io

中的晶体管tr等的配置、及从x方向开始数第奇数个输入输出电路区域r

io

中的晶体管tr等的配置,能够以将y方向作为轴的对称图案(在图35的例子中,为左右对称的图案)来配置。根据这种配置,即使在输入输出电路区域r

io

内氢的浓度有不均的情况下,也能够将如上所述的氢的影响在与多个输入输出焊垫电极p(dq)连接的多个电路之间统一为相同程度。

[0195]

另外,例如,如参照图16所说明的那样,在第1实施方式中,多个输入输出焊垫电极p(dq)及与其对应的输入输出电路区域r

io

的x方向上的中心位置分别与x方向上相邻的2个贯通接点区域r

c4t

的x方向上的中间位置一致。然而,这种构成仅为示例,具体构成等可适当进行调整。例如,如图36所示,多个输入输出焊垫电极p(dq)及与其对应的输入输出电路区域r

io

的x方向上的中心位置也可分别与x方向上相邻的2个贯通接点区域r

c4t

的x方向上的中间位置不一致。

[0196]

此外,在图36的例中,将从输入输出焊垫电极p(dq)的xy平面上的中心位置到最接近该输入输出焊垫电极p(dq)的贯通接点区域r

c4t

中最靠近该输入输出焊垫电极p(dq)的接点c4的xy平面上的中心位置的距离设为距离d

p-c4-36-1

时,距离d

p-c4-36-1

在所有输入输出焊垫电极p(dq)中皆相同。另外,在图36的例中,将从输入输出焊垫电极p(dq)的xy平面上的中心位置到第二靠近该输入输出焊垫电极p(dq)的贯通接点区域r

c4t

中最靠近该输入输出焊垫

电极p(dq)的接点c4的xy平面上的中心位置的距离设为距离d

p-c4-36-2

时,距离d

p-c4-36-2

在所有输入输出焊垫电极p(dq)中皆相同。

[0197]

此外,较理想为与所有输入输出焊垫电极p(dq)对应的所有距离d

p-c4-36-1

、d

p-c4-36-2

皆相同。然而,距离d

p-c4-36-1

、d

p-c4-36-2

有时会因为设计上的原因或制造误差等关系而不完全一致。在这种情况下,例如较理想为距离d

p-c4-36-1

、d

p-c4-36-2

的最大值与最小值之差为400nm以下。

[0198]

另外,在图36的例中,将从输入输出电路区域r

io

的xy平面上的中心位置到最靠近该输入输出电路区域r

io

的贯通接点区域r

c4t

中最靠近该输入输出电路区域r

io

的接点c4的xy平面上的中心位置的距离设为距离d

io-c4-36-1

时,距离d

io-c4-36-1

在所有输入输出电路区域r

io

中皆相同。另外,在图36的例中,将从输入输出电路区域r

io

的xy平面上的中心位置到第二靠近该输入输出电路区域r

io

的贯通接点区域r

c4t

中最靠近该输入输出电路区域r

io

的接点c4的xy平面上的中心位置的距离设为距离d

io-c4-36-2

时,距离d

io-c4-36-2

在所有输入输出电路区域r

io

中皆相同。

[0199]

此外,较理想为与所有输入输出电路区域r

io

对应的所有距离d

io-c4-36-1

、d

io-c4-36-2

皆相同。然而,距离d

io-c4-36-1

、d

io-c4-36-2

有时会因为设计上的原因或制造误差等关系而不完全一致。在这种情况下,例如较理想为距离d

io-c4-36-1

、d

io-c4-36-2

的最大值与最小值之差为400nm以下。

[0200]

此外,当采用图36这种配置时,在所有输入输出电路区域r

io

中,能够以相同图案配置晶体管tr等。根据这种配置,即使在输入输出电路区域r

io

内氢的浓度有不均的情况下,也能够将如上所述的氢的影响在与多个输入输出焊垫电极p(dq)连接的多个电路之间统一为相同程度。

[0201]

另外,在图16、图35及图36中,输入输出焊垫电极p(dq)的xy平面上的中心位置与输入输出电路区域r

io

的xy平面上的中心位置一致。然而,这种构成仅为示例,具体构成等可适当进行调整。例如,输入输出焊垫电极p(dq)的xy平面上的中心位置与输入输出电路区域r

io

的xy平面上的中心位置也可不一致。

[0202]

[晶体管tr]

[0203]

如上所述,在存储器裸片md的晶体管层l

tr

中设置有高电压晶体管、及低电压晶体管。以下,参照图37,对该方面更详细地进行说明。图37是用来对可搭载于第1实施方式的存储器裸片md及其它实施方式的存储器裸片上的晶体管的种类进行说明的示意性剖视图。

[0204]

图37中示出了所述晶体管tr

nl

及晶体管tr

nl

'作为n型低电压晶体管。另外,示出了所述晶体管tr

pl

及晶体管tr

pl

'作为p型低电压晶体管。另外,示出了晶体管tr

nh

作为n型高电压晶体管。另外,示出了晶体管tr

ph

作为p型高电压晶体管。

[0205]

晶体管tr

nl

、tr

pl

比晶体管tr

nl

'、tr

pl

'、tr

nh

、tr

ph

更高速地动作。因此,晶体管tr

nl

、tr

pl

用于外围电路pc中被要求最高速动作的部分。例如,如上所述,晶体管tr

nl

、tr

pl

包含在输入输出控制电路i/o(图4)中。

[0206]

晶体管tr

nl

'、tr

pl

'的耐受电压比晶体管tr

nl

、tr

pl

大。另外,晶体管tr

nl

'、tr

pl

'比晶体管tr

nh

、tr

ph

更高速地动作。晶体管tr

nl

、tr

pl

用于外围电路pc中进行信号传送、运算、解码等的部分。例如,晶体管tr

nl

'、tr

pl

'包含在感测放大器模块sam、定序器sqc、高速缓冲存储器cm、地址寄存器adr、命令寄存器cmr、状态寄存器str(图4)等中。

[0207]

晶体管tr

nh

、tr

ph

的耐受电压比晶体管tr

nl

、tr

pl

、tr

nl

'、tr

pl

'大。晶体管tr

nl

、tr

pl

用于外围电路pc中进行电压产生、电压传送等的部分。例如,晶体管tr

nh

、tr

ph

包含在电压产生电路vg、行解码器rd(图4)等中。

[0208]

如上所述,晶体管tr

nl

例如将半导体衬底100的p型阱区域100p作为通道区域。如上所述,晶体管tr

pl

例如将半导体衬底100的n型阱区域100n作为通道区域。晶体管tr

nl

'例如将半导体衬底100的p型阱区域100p作为通道区域。晶体管tr

pl

'例如将半导体衬底100的n型阱区域100n作为通道区域。晶体管tr

nh

例如将半导体衬底100的半导体衬底区域100s作为通道区域。晶体管tr

ph

例如将半导体衬底100的n型阱区域100n作为通道区域。

[0209]

另外,如上所述,晶体管tr

nl

的栅极电极包含含有n型杂质的多晶硅(si)等的栅极电极部件142。另外,如上所述,晶体管tr

pl

的栅极电极包含含有p型杂质的多晶硅(si)等的栅极电极部件152。晶体管tr

nl

'、tr

pl

'、tr

nh

、tr

ph

的栅极电极与晶体管tr

nl

的栅极电极同样地包含含有n型杂质的多晶硅(si)等的栅极电极部件142'。

[0210]

另外,图37中将晶体管tr

nl

、tr

pl

的栅极绝缘膜在z方向上的厚度表示为t

l

。另外,将晶体管tr

nl

'、tr

pl

'的栅极绝缘膜在z方向上的厚度表示为t

l

'。另外,将晶体管tr

nh

、tr

ph

的栅极绝缘膜在z方向上的厚度表示为th。另外,t

l

小于t

l

'。另外,t

l

'小于th。

[0211]

[其它]

[0212]

已对本发明的若干实施方式进行了说明,但这些实施方式仅作为示例提出,并未意图限定发明的范围。实际上,所述新颖的方法和系统能以其它各种方式来实现,此外,在不脱离本发明主旨范围内,可对所述方法和系统的实施方式进行各种省略、替换和变更。这些实施方式及其变化包含在所附权利要求书及与其同等的范围内,并且包含在发明的范围和主旨中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。