1.本发明涉及一种逆流检测电路以及直流-直流(direct current-direct current,dc-dc)转换器。

背景技术:

2.dc-dc转换器是具有从dc输入电压转换为不同的dc输出电压的功能的装置。dc-dc转换器中的同步整流型转换器例如在待机时等轻负载时,通过使作为同步整流器的同步整流晶体管断开,由此,能够提高电力转换的效率(参照日本专利特开2019-103199号公报)。

3.关于使同步整流晶体管断开的时机,线圈电流越接近0(零)安培,则从获得高效率的观点出发越有利。因此,在同步整流型转换器中,由逆流检测电路来检测同步整流晶体管两端的电压,在线圈电流成为0安培的时机使同步整流晶体管断开。

4.[现有技术文献]

[0005]

[专利文献]

[0006]

专利文献1:日本专利特开2019-103199号公报

技术实现要素:

[0007]

[发明所要解决的问题]

[0008]

但是,同步整流晶体管的导通电阻的电阻值会因所谓的过程-电压-温度(process-voltage-temperature,pvt)偏差而变动。同步整流晶体管的导通电阻的电阻值的变动会使所检测的线圈电流值发生变动。例如,若同步整流晶体管的导通电阻相对于设计值而变动为大的值,则同步整流晶体管断开时机会发生延迟。使同步整流晶体管断开的时机的延迟会导致输出电容器的电荷放电,而造成电力转换的效率下降。

[0009]

本发明考虑到所述的情况,目的在于提供一种逆流检测电路以及dc-dc转换器,即使在同步整流晶体管的导通电阻的电阻值发生了变动的情况下,也能抑制电力转换的效率下降。

[0010]

[解决问题的技术手段]

[0011]

本发明的实施方式的逆流检测电路耦接至同步整流晶体管,且基于被耦接的所述同步整流晶体管两端的电压来检测逆电流,所述逆流检测电路包括:第一级差动输入电路,具有包含与第一输入端连接的栅极的第一晶体管、与所述第一晶体管串联连接的第一电阻、包含与第二输入端连接的栅极的第二晶体管、以及与所述第二晶体管串联连接的第二电阻;以及第二级差动输入电路,具有包含与所述第一晶体管和所述第一电阻的节点连接的栅极的第三晶体管、以及包含与所述第二晶体管和所述第二电阻的节点连接的栅极的第四晶体管,所述第一级差动输入电路还具有第五晶体管,所述第五晶体管包含与所述第一电阻的相对于跟所述第一晶体管连接的一端的另一端连接的漏极,且与所述同步整流晶体管为相同的导电型。

[0012]

根据本发明的另一实施方式的逆流检测电路,所述第五晶体管包含与供给规定的

偏压电压的偏压电路连接的栅极。

[0013]

根据本发明的另一实施方式的逆流检测电路,所述第五晶体管包含与供给电源电压的电源供给端子连接的栅极。

[0014]

根据本发明的另一实施方式的逆流检测电路,所述第五晶体管是包含与电源端子连接的栅极的n沟道金属氧化物半导体晶体管,所述电源端子供给比接地电压高的电压来作为所述电源电压。

[0015]

根据本发明的另一实施方式的逆流检测电路,所述第五晶体管是包含与接地端子连接的栅极的p沟道金属氧化物半导体晶体管,所述接地端子供给接地电压来作为所述电源电压。

[0016]

本发明的实施方式的直流-直流转换器包括同步整流晶体管,逆流检测电路基于所述同步整流晶体管两端的电压来检测逆电流。

[0017]

[发明的效果]

[0018]

根据本发明,即使在同步整流晶体管的导通电阻的电阻值发生了变动的情况下,也能够抑制电力转换的效率下降。

附图说明

[0019]

图1是本发明的第一实施方式的dc-dc转换器的电路图。

[0020]

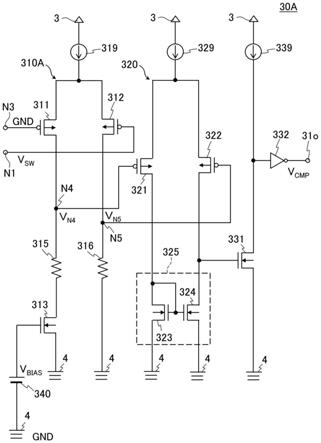

图2是表示第一实施方式的dc-dc转换器中的逆流检测电路的结构例(第一结构例)的电路图。

[0021]

图3是概略地表示第一实施方式的dc-dc转换器的动作波形的说明图。

[0022]

图4是说明在逆流检测电路内产生的偏移电压的说明图。

[0023]

图5是说明检测电压、偏移电压以及非反转输入端的电压、逆流检测电路内的第二级差动输入电路的第一输入端的电压及第二输入端的电压、与输出端的电压相对于时间的关系的说明图。

[0024]

图6的(a)是表示同步整流晶体管的导通电阻以及第一结构例的逆流检测电路中的偏移电压相对于温度的关系的关系图。图6的(b)是表示同步整流晶体管的导通电阻以及第一结构例的逆流检测电路中的偏移电压相对于输入电压的关系的关系图。

[0025]

图7是表示第二实施方式的dc-dc转换器中的逆流检测电路的结构例(第二结构例)的电路图。

[0026]

图8的(a)是表示同步整流晶体管的导通电阻以及第二结构例的逆流检测电路中的偏移电压相对于温度的关系的关系图。图8的(b)是表示同步整流晶体管的导通电阻以及第二结构例的逆流检测电路中的偏移电压相对于输入电压的关系的关系图。

[0027]

图9是本发明的第三实施方式的dc-dc转换器的电路图。

[0028]

图10是表示第三实施方式的dc-dc转换器中的逆流检测电路的结构例(第三结构例)的电路图。

[0029]

图11是表示第四实施方式的dc-dc转换器中的逆流检测电路的结构例(第四结构例)的电路图。

[0030]

[符号的说明]

[0031]

1a~1d:dc-dc转换器

[0032]

3:电源端子(电源供给端子)

[0033]

4:接地端子(电源供给端子)

[0034]

12:nmos晶体管(同步整流晶体管)

[0035]

30a~30d:逆流检测电路

[0036]

310a、310b、410c、410d:1段目差动输入电路

[0037]

311:pmos晶体管(第一晶体管)

[0038]

312:pmos晶体管(第二晶体管)

[0039]

313、314:nmos晶体管(第五晶体管)

[0040]

411:nmos晶体管(第一晶体管)

[0041]

412:nmos晶体管(第二晶体管)

[0042]

413、414:pmos晶体管(第五晶体管)

[0043]

320、420:第二级差动输入电路

[0044]

321:pmos晶体管(第三晶体管)

[0045]

322:pmos晶体管(第四晶体管)

[0046]

421:nmos晶体管(第三晶体管)

[0047]

422:nmos晶体管(第四晶体管)

[0048]

340、440:偏压电路

[0049]

62:pmos晶体管(同步整流晶体管)

[0050]

vdd:电压(电源电压)

[0051]

gnd:接地电压(电源电压)

[0052]vbias

:偏压电压

[0053]

n1、n11:节点(第一输入端)

[0054]

n3、n13:节点(第二输入端)

[0055]

n4、n5、n14、n15:节点

具体实施方式

[0056]

以下,参照附图来说明本发明的实施方式的逆流检测电路以及dc-dc转换器。

[0057]

[第一实施方式]

[0058]

图1是作为第一实施方式的dc-dc转换器的一例的dc-dc转换器1a的电路图。

[0059]

dc-dc转换器1a是所谓的同步整流型的降压dc-dc转换器。dc-dc转换器1a包括:p沟道金属氧化物半导体(p channel metal oxide semiconductor,pmos)晶体管11、nmos晶体管12、电感器21、输出电容器22、逆流检测电路30a、及构成控制电路的反相器41以及与非(not and,nand)电路42。逆流检测电路30a包含具备偏移电压的比较器31。

[0060]

pmos晶体管11包含:栅极,连接于控制端子tc;源极,连接于输入端子ti;以及漏极,与nmos晶体管12的漏极和电感器21的第一端的节点n1相连接。

[0061]

作为同步整流晶体管的nmos晶体管12包含:栅极,与nand电路42的输出端连接;漏极,与节点n1连接;以及源极,连接于接地端子4。

[0062]

电感器21包含:第一端,与nmos晶体管12的漏极连接;以及第二端,与输出端子to连接。输出电容器22连接于电感器21的第二端和输出端子to的节点n2与接地端子4之间。从

输出端子to向连接于输出端子to的外部电路(省略图示)输出输出电压vout。

[0063]

逆流检测电路30a等效地具有比较器31、以及产生偏移电压值vos的偏移电压的偏移电压源32。比较器31包含:非反转输入端( ),与节点n1连接;以及反转输入端(-),经由偏移电压源32而连接于nmos晶体管12的源极和接地端子4的节点n3。偏移电压源32包含连接于节点n3的正极、及连接于反转输入端(-)的负极。

[0064]

比较器31的正侧电源端连接于电源端子3,负侧电源端连接于接地端子4。作为电源供给端子的电源端子3供给作为电源电压的电压vdd。作为电源供给端子的接地端子4供给作为电源电压的接地电压gnd。电压vdd为比接地电压gnd高的电压。

[0065]

图2是表示作为第一实施方式的dc-dc转换器中的逆流检测电路的第一结构例的逆流检测电路30a的电路图。

[0066]

逆流检测电路30a包括:例如构成两级等多级差动输入电路的第一级差动输入电路310a及第二级差动输入电路320、nmos晶体管331、反相器332、以及向nmos晶体管331供给恒电流的恒电流源339。

[0067]

第一级差动输入电路310a具有:作为第一晶体管的pmos晶体管311、作为第二晶体管的pmos晶体管312、作为第一电阻的电阻315、以及作为第二电阻的电阻316。在pmos晶体管311、pmos晶体管312的各源极与电源端子3之间,连接有向各pmos晶体管311、pmos晶体管312供给恒电流的恒电流源319。而且,第一级差动输入电路310a还具有与nmos晶体管12为相同的导电型的n型的作为第五晶体管的nmos晶体管313。

[0068]

pmos晶体管311包含与作为第一输入端的节点n3连接的栅极。pmos晶体管312包含与作为第二输入端的节点n1连接的栅极。

[0069]

电阻315、电阻316是第一级差动输入电路310a中的负载电阻。电阻315、电阻316各自与pmos晶体管311、pmos晶体管312分别串联连接。此处,将电阻315和pmos晶体管311的漏极的连接点称作节点n4,将电阻316和pmos晶体管312的漏极的连接点称作节点n5。

[0070]

电阻315包含:作为一端的第一端,与pmos晶体管311的漏极连接;以及第二端,为相对于所述一端的另一端且与nmos晶体管313的漏极连接。电阻316包含与pmos晶体管312的漏极连接的第一端、及与接地端子4连接的第二端。关于电阻315、电阻316的电阻值,既可为相同的值,也可为不同的值。

[0071]

nmos晶体管313包含:栅极,与供给偏压电压v

bias

的偏压电路340连接;漏极,连接于电阻315的第二端;以及源极,与接地端子4连接。

[0072]

第二级差动输入电路320具有作为第三晶体管的pmos晶体管321、及作为第四晶体管的pmos晶体管322。在pmos晶体管321的漏极,连接有nmos晶体管323的漏极。在pmos晶体管322的漏极,连接有nmos晶体管324的漏极。在pmos晶体管321、pmos晶体管322的各源极与电源端子3之间,连接有向各pmos晶体管321、pmos晶体管322供给恒电流的恒电流源329。

[0073]

pmos晶体管321包含与节点n4连接的栅极。pmos晶体管322包含与节点n5连接的栅极。

[0074]

nmos晶体管323包含:与pmos晶体管321的漏极连接的漏极、与自身的漏极连接(短路)的栅极、及连接于接地端子4的源极。nmos晶体管324包含:与nmos晶体管323的栅极及漏极连接的栅极、与pmos晶体管322的漏极连接的漏极、及连接于接地端子4的源极。nmos晶体管323、nmos晶体管324构成电流镜电路325。

[0075]

作为输出晶体管的nmos晶体管331包含:与pmos晶体管322及nmos晶体管324的节点连接的栅极、经由恒电流源339而连接于电源端子3的漏极、及连接于接地端子4的源极。反相器332包含:连接于恒电流源339和nmos晶体管331的节点的输入端、及与输出端31o连接的输出端。

[0076]

继而,对dc-dc转换器1a的作用进行说明。

[0077]

图3是作为dc-dc转换器1a的动作波形,而概略地表示控制端子tc的电压vc、输出端31o的电压v

cmp

、节点n1的电压vsw以及流经电感器21的线圈电流i

l

的说明图。另外,图3中,基于简化图的观点,省略了pmos晶体管11与nmos晶体管12同时断开的死时间(dead time)期间。而且,图3所示的带上划线的pwm表示了电压vc使pmos晶体管11导通的时机为低(l)电平。

[0078]

电压vc、电压v

cmp

、电压vsw以及线圈电流i

l

均以周期t而周期性地变化。电压vc在时刻0以后且直至时刻t1前为止维持l电平,在时刻t1迁移至高(h)电平,在时刻t1以后且直至时刻t3前为止维持h电平,在时刻t3迁移至l电平。因而,pmos晶体管11在时刻0以后且直至时刻t1前为止为导通状态,在时刻t1断开,在时刻t1以后且直至时刻t3前为止维持断开状态,在时刻t3导通。

[0079]

电压v

cmp

在时刻0以后且直至时刻t1前为止维持h电平,在时刻t1迁移至l电平,在时刻t1以后且时刻t2前维持l电平,在时刻t2迁移至h电平,在时刻t2以后且时刻t3维持h电平。因而,nmos晶体管12在时刻0以后且直至时刻t1前为止为断开状态,在时刻t1导通,维持了导通状态后,在时刻t3断开。

[0080]

线圈电流i

l

在时刻0以后且直至时刻t1为止以固定比例增加。当到达时刻t1时,伴随pmos晶体管11的断开与nmos晶体管12的导通,线圈电流i

l

以固定比例减少。当到达时刻t2时,线圈电流i

l

成为0安培,直至时刻t3前为止维持0安培(i

l

=0)。

[0081]

电压vsw在时刻0以后且直至时刻t1前为止,从输入电压vin以固定比例减少,在时刻t1,伴随pmos晶体管11的断开与nmos晶体管12的导通,掉落至负电压,随后,朝向0伏特以固定比例增加。在时刻t2,线圈电流i

l

成为0安培,线圈电流i

l

的变化停止。因而,电感器21的两端间的电压差成为0伏特,节点n1与节点n2的电压平衡,上升至比输入电压vin低的规定的正电压。在时刻t2以后且时刻t3前维持所述正电压,在时刻t3,伴随pmos晶体管11的导通以及nmos晶体管12的断开,电压vsw上升至与输入电压vin相等的电压。

[0082]

图4是说明在逆流检测电路30a内产生的偏移电压的说明图。实线l1表示节点n1处产生的电压vsw的特性,虚线l2表示因某些原因而nmos晶体管12的导通电阻值ron12变大后的电压vsw的特性。

[0083]

逆流检测电路30a使检测电压vd具备偏移电压。即,对于逆流检测电路30a,设定考虑到比较器31的响应的延迟时间td1的偏移电压值vos。偏移电压值vos能够以导通电阻值ron12与电感器21的线圈电流i

l

之积来表示。即,偏移电压值vos(=ron12

·il

)与检测电压vd的电压值相等。偏移电压值vos被设定为,检测电压vd的电压值为负(vd<0)(点p1)。

[0084]

节点n1处产生的电压vsw以实线l1来表示。实线l1是通过点p1、点p0的直线,且利用导通电阻值ron12与电感器21的线圈电流i

l

之积来求出。因而,电压vsw的电压值与偏移电压值vos以及检测电压vd的电压值相等。逆流检测电路30a检测电压的时机是实线l1与检测电压vd的交点即点p1。当逆流检测电路30a检测电压时,在延迟了比较器31的响应的延迟

时间td1的时机即作为与0伏特的交点的点p0处,电压v

cmp

反转,使nmos晶体管12断开而防止线圈电流i

l

的逆流。

[0085]

继而,对因某些原因而导通电阻值ron12变大的情况(虚线l2)进行说明。此处,假设伴随导通电阻值ron12的变化,偏移电压值vos以及延迟时间td2无变化。即,关于比较器31的响应的延迟时间,假设延迟时间td2与延迟时间td1相等。

[0086]

导通电阻值ron12变大时的电压vsw以虚线l2来表示。虚线l2是通过点p3、点p0的直线。尽管线圈电流i

l

相同,但因nmos晶体管12的导通电阻以及线圈电流i

l

产生的电压vsw的绝对值|vsw|变大,因此,若偏移电压值vos相同,则所检测的线圈电流i

l

的电流值变小。线圈电流i

l

的电流值减少时的斜率以输出电压vout与电感器21的电感l的倒数之积即vout/l来表示。即使在导通电阻值ron12f发生了变化的情况下,线圈电流i

l

的斜率即vout/l也大致无变化,但电压vsw的绝对值|vsw|变大。

[0087]

此处,在偏移电压值vos无变化的情况下,即使检测电压vd相同,但由于电压vsw的变化陡峭,因此在从检测电压的点p3经过了延迟时间td2后的点p4处,以δi

l

产生线圈电流i

l

的逆流,即从节点n2朝向节点n1的方向的电流即逆电流。δi

l

是来自输出电容器22的放电动作,因此电力转换的效率下降。相反,当导通电阻值ron12变小时,在电压vsw到达0伏特之前,电压v

cmp

反转,因此容易偏离理想的动作,电力转换的效率容易下降。

[0088]

因此,在逆流检测电路30a中,利用与作为同步整流晶体管的nmos晶体管12(图1参照)为相同导电型的nmos晶体管313的导通电阻来产生比较器31(参照图1)的偏移电压。

[0089]

由于nmos晶体管12与nmos晶体管313为相同的导电型,因此即使导通电阻值ron12因温度、输入电压或制造偏差(小批量过程验证测试(pilot-run verification test,pvt)偏差)而发生变化,nmos晶体管313的导通电阻值ron313也会同样地变化。这意味着,若使用图4所示的示例来概念性地进行说明,则在导通电阻值ron12发生了变化的情况下,偏移电压值vos从点p1向点p2自动移动。因而,偏移电压值vos对应于导通电阻值ron12的变化,朝电力转换的效率不易下降的方向自动变化,因此能够使电力转换的效率不易下降。

[0090]

图5是说明检测电压vd、偏移电压值vos及非反转输入端( )的电压vsw、第二级差动输入电路320的第一输入电压及第二输入电压即电压v

n4

及电压v

n5

、与输出端31o的电压v

cmp

相对于时间的关系的说明图。

[0091]

电压vsw为导通电阻值ron12与电感器21的线圈电流i

l

之积。检测电压vd、偏移电压值vos、点p0、点p1以及延迟时间与图3相同。随着电压vsw从点p1向点p0接近,即从负电压(vsw<0)向0伏特接近,第二级差动输入电路320的第一输入电压即电压v

n4

逐渐上升,第二级差动输入电路320的第二输入电压即电压v

n5

逐渐下降。

[0092]

逆流检测电路30a中,将电阻315加上nmos晶体管313的导通电阻值ron313,因此电压v

n4

增加,产生偏移电压值vos。所产生的偏移电压值vos除了基于导通电阻值ron313以外,还基于pmos晶体管311、pmos晶体管312的各栅极-源极间电压以及各阈值电压与电阻315、电阻316的电阻值来决定。输出端31o的电压v

cmp

在从电压vsw到达0伏特之前的电压v

n4

=电压v

n5

的时机经过了延迟时间td1后,从l电平反转为h电平。

[0093]

图6的(a)是表示nmos晶体管12(参照图1)的导通电阻以及逆流检测电路30a中的偏移电压相对于温度的关系的关系图。此处,实线l3表示导通电阻值ron12。虚线l4表示比较器31(参照图1)的偏移电压值vos。

[0094]

实线l3以及虚线l4均为具有相同斜率的向右上斜的直线。这表示:导通电阻值ron12以及偏移电压值vos均相对于温度成正比。具体而言,若温度上升,则偏移电压值vos的电压与导通电阻值ron12一同上升。即,偏移电压值vos相对于导通电阻值ron12的温度变化而朝效率不易下降的方向自动调整,在经过了延迟时间td1后,可检测到线圈电流i

l

=0安培附近。

[0095]

图6的(b)是表示nmos晶体管12(参照图1)的导通电阻以及逆流检测电路30a中的偏移电压相对于输入电压vin的关系的关系图。此处,实线l5表示导通电阻值ron12。虚线l6表示比较器31(参照图1)的偏移电压值vos。

[0096]

实线l5与虚线l6均为相对于输入电压vin而固定(斜率为零)的直线。这表示:导通电阻值ron12以及偏移电压值vos均相对于输入电压vin无变动,即,均维持固定值。这是因为,对nmos晶体管313的栅极施加的电压被固定为偏压电压v

bias

。

[0097]

根据像这样构成的dc-dc转换器1a,相对于温度或电源电压等的环境变化,偏移电压值vos朝效率不易下降的方向自动调整。而且,相对于制造工艺的偏差,偏移电压值vos也会朝效率不易下降的方向自动调整。因而,在dc-dc转换器1a中,对于使nmos晶体管12断开的时机,例如只要将线圈电流i

l

设定在可获得高效率的线圈电流i

l

=0安培附近,便能够抑制伴随导通电阻值ron12的变化引起的dc-dc转换器1a的效率下降。

[0098]

而且,根据dc-dc转换器1a,消耗电流不会增加,因此不会使电力消耗增加,而能够相对于导通电阻值ron12的变化来使电力转换的效率稳定化。

[0099]

进而,根据dc-dc转换器1a,对产生偏移电压的nmos晶体管313的栅极施加的电压被固定为偏压电压v

bias

,因此不依存于输入电压vin。

[0100]

[第二实施方式]

[0101]

图7是作为第二实施方式的dc-dc转换器的一例的dc-dc转换器1b中的逆流检测电路30b的结构例(第二结构例)的电路图。

[0102]

dc-dc转换器1b相对于dc-dc转换器1a,不同之处在于,取代逆流检测电路30a而包括逆流检测电路30b,其他方面实质上并无不同。因此,本实施方式中,以逆流检测电路30b为中心来进行说明,并且省略与第一实施方式重复的说明。

[0103]

逆流检测电路30b相对于逆流检测电路30a,不同之处在于,包括取代第一级差动输入电路310a的nmos晶体管313而具有nmos晶体管314的第一级差动输入电路310b,其他方面实质上并无不同。

[0104]

作为第五晶体管的nmos晶体管314相对于nmos晶体管313,栅极的连接目标不同,其他方面实质上并无不同。nmos晶体管314包含与作为电源供给端子的电源端子3连接的栅极,所述电源端子3供给电压vdd。

[0105]

图8的(a)是表示nmos晶体管12(参照图1)的导通电阻以及逆流检测电路30b中的偏移电压相对于温度的关系的关系图。此处,实线l7表示导通电阻值ron12。虚线l8表示比较器31(参照图1)的偏移电压值vos。

[0106]

实线l7以及虚线l8均为具有相同斜率的向右上斜的直线。这表示:导通电阻值ron12以及偏移电压值vos均相对于温度成正比。具体而言,若温度上升,则偏移电压值vos与导通电阻值ron12一同上升。即,偏移电压值vos相对于导通电阻值ron12的温度变化而朝效率不易下降的方向自动调整,在经过了延迟时间td1后可检测到线圈电流i

l

=0安培附

近。

[0107]

图8的(b)是表示nmos晶体管12(参照图1)的导通电阻值ron12以及逆流检测电路30b中的偏移电压相对于输入电压vin的关系的关系图。此处,实线c1表示导通电阻值ron12。虚线c2表示比较器31(参照图1)的偏移电压值vos。

[0108]

实线c1与虚线c2是呈反比的曲线。对nmos晶体管314的栅极施加的电压为电压vdd。偏移电压值vos与电压vdd成反比,当输入电压vin为电压vdd时,相对于输入电压vin的变化,与导通电阻值ron12同步地变化。即,偏移电压值vos相对于输入电压vin的变化,而与导通电阻值ron12的变化同步地自动调整。

[0109]

根据像这样构成的dc-dc转换器1b,能够获得与dc-dc转换器1a同样的作用以及效果。即,根据dc-dc转换器1b,相对于温度或电源电压等的环境变化,偏移电压值vos朝效率不易下降的方向自动调整。而且,相对于制造工艺的偏差,偏移电压值vos也会朝效率不易下降的方向自动调整。

[0110]

因而,在dc-dc转换器1b中,对于使nmos晶体管12断开的时机,例如只要将线圈电流i

l

设定在可获得高效率的线圈电流i

l

=0安培附近,便能够抑制伴随导通电阻值ron12的变化引起的电力转换的效率下降。

[0111]

而且,根据dc-dc转换器1b,消耗电流不会增加,因此不会使电力消耗增加,而能够相对于导通电阻值ron12的变化来使电力转换的效率稳定化。

[0112]

进而,根据dc-dc转换器1b,对产生偏移电压值vos的nmos晶体管314的栅极施加的电压为电压vdd,因此偏移电压值vos相对于输入电压vin的变化而与导通电阻值ron12同步地变化。因而,dc-dc转换器1b具有下述优点,即,相对于输入电压vin的变化,比dc-dc转换器1a更不易受到影响。

[0113]

[第三实施方式]

[0114]

图9是作为第三实施方式的dc-dc转换器的一例的dc-dc转换器1c的电路图。

[0115]

dc-dc转换器1c相对于dc-dc转换器1a,不同之处在于,取代pmos晶体管11、nmos晶体管12、逆流检测电路30a与反相器41及nand电路42而分别包括nmos晶体管61、pmos晶体管62、逆流检测电路30c及or电路81与电感器21的配置,其他方面实质上并无不同。因此,本实施方式中,省略与第一实施方式、第二实施方式重复的说明。

[0116]

dc-dc转换器1c是所谓的同步整流型的升压dc-dc转换器。dc-dc转换器1c包括nmos晶体管61、pmos晶体管62、电感器21、输出电容器22、逆流检测电路30c以及构成控制电路的or电路81。逆流检测电路30c包含具备偏移电压的比较器31。

[0117]

在dc-dc转换器1c中,电感器21包含连接于输入端子ti的第一端、nmos晶体管61、pmos晶体管62、以及连接于与逆流检测电路30c的节点n11的第二端。

[0118]

nmos晶体管61包含:连接于控制端子tc的栅极、连接于节点n11的漏极、以及连接于接地端子4的源极。

[0119]

作为同步整流晶体管的pmos晶体管62包含:与or电路81的输出端连接的栅极、与节点n11连接的漏极、以及连接于输出端子to的源极。

[0120]

or电路81连接于:与控制端子tc及nmos晶体管61的栅极连接的第一输入端、与输出端31o连接的第二输入端、以及pmos晶体管62的栅极。

[0121]

逆流检测电路30c等效地具有:比较器31、及产生偏移电压值vos的偏移电压的偏

移电压源32。比较器31包含:与节点n11连接的反转输入端(-)、以及经由偏移电压源32而与节点n13连接的非反转输入端( )。偏移电压源32包含:连接于非反转输入端( )的正极、及连接于节点n13的负极。

[0122]

比较器31的正侧电源端连接于电源端子3,负侧电源端连接于接地端子4。作为电源供给端子的电源端子3供给作为电源电压的电压vdd。作为电源供给端子的接地端子4供给作为电源电压的接地电压gnd。电压vdd是比接地电压gnd高的电压。

[0123]

图10是表示作为第三实施方式的dc-dc转换器中的逆流检测电路的第三结构例的逆流检测电路30c的电路图。

[0124]

逆流检测电路30c包括:例如构成两级等多级的差动输入电路的第一级差动输入电路410c及第二级差动输入电路420、pmos晶体管431、反相器432、以及从pmos晶体管431将恒电流灌(sink)至接地端子4的恒电流源439。

[0125]

第一级差动输入电路410c具有:作为第一晶体管的nmos晶体管411、作为第二晶体管的nmos晶体管412、作为第一电阻的电阻415、以及作为第二电阻的电阻416。在nmos晶体管411、nmos晶体管412的各源极与接地端子4之间,连接有将恒电流灌至接地端子4的恒电流源419。而且,第一级差动输入电路410c还具有与pmos晶体管62为相同导电型的p型的作为第五晶体管的pmos晶体管413。

[0126]

nmos晶体管411包含与作为第一输入端的节点n11连接的栅极。nmos晶体管412包含与作为第二输入端的节点n13连接的栅极。

[0127]

电阻415、电阻416是第一级差动输入电路410c中的负载电阻。电阻415、电阻416各自与nmos晶体管411、nmos晶体管412分别串联连接。此处,将电阻415与nmos晶体管411的漏极的连接点称作节点n14,将电阻416与nmos晶体管412的漏极的连接点称作节点n15。

[0128]

电阻415包含:与nmos晶体管411的漏极连接的第一端、以及与电源端子3连接的第二端。电阻416包含:作为一端的第一端,与nmos晶体管412的漏极连接;以及第二端,为相对于所述一端的另一端且与pmos晶体管413的漏极连接。另外,关于电阻415、电阻416的电阻值,既可为相同的值,也可为不同的值。

[0129]

pmos晶体管413包含:与供给偏压电压v

bias

的偏压电路440连接的栅极、连接于电阻416的第二端的漏极、以及与电源端子3连接的源极。

[0130]

第二级差动输入电路420具有:作为第三晶体管的nmos晶体管421、以及作为第四晶体管的nmos晶体管422。在nmos晶体管421、nmos晶体管422的各源极与接地端子4之间,连接有将恒电流灌至接地端子4的恒电流源429。

[0131]

在nmos晶体管421的漏极,连接有pmos晶体管423的漏极。在nmos晶体管422的漏极,连接有pmos晶体管424的漏极。在nmos晶体管421、nmos晶体管422的各源极与接地端子4之间,连接有将恒电流灌至接地端子4的恒电流源429。

[0132]

nmos晶体管421包含与节点n14连接的栅极。nmos晶体管422包含与节点n15连接的栅极。

[0133]

pmos晶体管423包含:与nmos晶体管421的漏极连接的漏极、与自身的漏极连接(短路)的栅极、以及连接于电源端子3的源极。pmos晶体管424包含:与pmos晶体管423的栅极及漏极连接的栅极、与nmos晶体管422的漏极连接的漏极、以及连接于电源端子3的源极。pmos晶体管423、pmos晶体管424构成电流镜电路425。

[0134]

作为输出晶体管的pmos晶体管431包含:与nmos晶体管422以及pmos晶体管424的节点连接的栅极、连接于电源端子3的源极、以及经由恒电流源439而连接于接地端子4的漏极。反相器432包含:连接于恒电流源439和pmos晶体管431的节点的输入端、以及与输出端31o连接的输出端。

[0135]

根据像这样构成的dc-dc转换器1c,能够获得与dc-dc转换器1a同样的作用以及效果。即,利用与作为同步整流晶体管的pmos晶体管62为相同导电型的pmos晶体管413的导通电阻来产生偏移电压。由于pmos晶体管62与pmos晶体管413为相同的导电型,因此即使pmos晶体管62的导通电阻值ron62因温度、输入电压或制造偏差(pvt偏差)发生变化,pmos晶体管413的导通电阻值ron413也会同样地变化。因而,偏移电压值vos对应于导通电阻值ron62的变化而朝电力转换的效率不易下降的方向自动变化,因此能够使电力转换的效率不易下降。

[0136]

如上所述,根据dc-dc转换器1c,对于升压dc-dc转换器,相对于温度或电源电压等的环境变化,偏移电压值vos也会朝效率不易下降的方向自动调整。而且,相对于制造工艺的偏差,偏移电压值vos也会朝电力转换的效率不易下降的方向自动调整。因而,在dc-dc转换器1c中,对于使pmos晶体管62断开的时机,例如只要将线圈电流i

l

设定在可获得高效率的线圈电流i

l

=0安培附近,便能够抑制伴随pmos晶体管62的导通电阻的变化引起的dc-dc转换器1c的效率下降。

[0137]

而且,根据dc-dc转换器1c,消耗电流不会增加,因此不会使电力消耗增加,而能够相对于导通电阻值ron62的变化来使电力转换的效率稳定化。

[0138]

进而,根据dc-dc转换器1c,对产生偏移电压的pmos晶体管413的栅极施加的电压被固定为偏压电压v

bias

,因此不依存于输入电压vin。

[0139]

[第四实施方式]

[0140]

图11是表示作为第四实施方式的dc-dc转换器的一例的dc-dc转换器1d中的逆流检测电路30d的结构例(第四结构例)的电路图。

[0141]

dc-dc转换器1d相对于dc-dc转换器1c,不同之处在于,取代逆流检测电路30c而包括逆流检测电路30d,其他方面实质上并无不同。因此,本实施方式中,以逆流检测电路30d为中心来进行说明,并且省略与第一实施方式至第三实施方式重复的说明。

[0142]

逆流检测电路30d相对于逆流检测电路30c,不同之处在于,包括取代第一级差动输入电路410c的pmos晶体管413而具有pmos晶体管414的第一级差动输入电路410d,其他方面实质上并无不同。

[0143]

作为第五晶体管的pmos晶体管414相对于pmos晶体管413,栅极的连接目标不同,其他方面实质上并无不同。pmos晶体管414包含与作为电源供给端子的接地端子4连接的栅极,所述接地端子4供给接地电压gnd。

[0144]

根据像这样构成的dc-dc转换器1d,能够获得与dc-dc转换器1b同样的作用以及效果。因而,对于使pmos晶体管62断开的时机,例如只要将线圈电流i

l

设定在可获得高效率的线圈电流i

l

=0安培附近,便能够抑制伴随pmos晶体管62的导通电阻的变化引起的dc-dc转换器1d的电力转换的效率下降。

[0145]

而且,根据dc-dc转换器1d,消耗电流不会增加,因此不会使电力消耗增加,而能够相对于pmos晶体管62的导通电阻的变化来使电力转换的效率稳定化。进而,根据dc-dc转换

器1d,对产生偏移电压的pmos晶体管414的栅极施加的电压为接地电压gnd,因此偏移电压值vos相对于输入电压vin而与导通电阻值ron62同步地变化。因而,dc-dc转换器1d具有下述优点,即,相对于所输入的电压的变动,比dc-dc转换器1c更不易受到影响。

[0146]

如上所述,根据本实施方式的任一个,即使在同步整流晶体管的导通电阻的电阻值发生了变动的情况下,也不会使消耗电流增加而能够抑制电力转换的效率下降。

[0147]

另外,本发明并不就此限定于所述实施方式,在实施阶段,除了所述示例以外,还能够以各种方式来实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式或其变形包含在发明的范围或主旨中,并且包含在权利要求所记载的发明及其均等的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。