1.本技术实施例涉及光数据存储的技术领域,尤其涉及一种三维堆叠式光接口存储器和一种光数据处理装置。

背景技术:

2.相关技术中,在存储或者读取光数据时,需要通过处理器对光数据进行处理。

3.具体地,在存储光数据时,需要将光数据发送至处理器,处理器对光数据进行处理之后,再写入存储器中存储。在读取存储器中存储的光数据时,同样需要通过处理器对光数据进行处理之后,才能够向外发送。

4.存储器与处理器往往相互独立设置,光数据在存储器与处理器之间进行传输,实现存储或读取功能,延长了光数据的传输路径,增加了光数据的传输时间,从而降低了存储或读取光数据的效率。

技术实现要素:

5.为了解决上述技术问题中至少之一,本技术实施例提供了一种三维堆叠式光接口存储器和一种光数据处理装置。

6.第一方面,本技术实施例提供了一种三维堆叠式光接口存储器,包括存储芯片,存储芯片用于存储数据,存储芯片包括第一键合面;接口芯片,接口芯片包括第二键合面,第一键合面与第二键合面形成三维异质集成结构,以将接口芯片与存储芯片三维堆叠连接,形成三维堆叠式光接口存储器;其中,接口芯片包括光数据通信电路,光数据通信电路用于处理写入存储芯片的数据和从存储芯片读取的数据。

7.在一种可行的实施方式中,光数据通信电路包括光数据协议电路,光数据协议电路用于存储光数据协议。

8.在一种可行的实施方式中,光数据协议包括xgmii协议、pmd协议、pma协议和pcs协议中至少一者。

9.在一种可行的实施方式中,光数据通信电路还包括存储控制电路,存储控制电路与光数据协议电路连接,存储控制电路用于将光数据协议电路处理后的数据写入存储芯片;和存储控制电路用于读取存储芯片内存储的数据并传输给光数据协议电路。

10.在一种可行的实施方式中,光数据通信电路还包括缓存电路,存储控制电路通过缓存电路与光数据协议电路连接,缓存电路用于缓存数据。

11.在一种可行的实施方式中,光数据通信电路包括电压转化电路,电压转化电路与存储芯片和接口芯片连接,电压转化电路用于升高或降低接口芯片的电压值和/或存储芯片的电压值,以使接口芯片和存储芯片之间能够传输数据。

12.在一种可行的实施方式中,存储芯片的数量为至少两个。

13.在一种可行的实施方式中,至少两个存储芯片分别与接口芯片三维堆叠连接;和/或至少两个存储芯片之间三维堆叠连接。

14.第二方面,本技术实施例提供了一种光数据处理装置,包括光数据接收单元,光数据接收单元用于接收光数据;如上述第一方面的三维堆叠式光接口存储器,三维堆叠式光接口存储器与光数据接收单元连接;处理器,处理器与三维堆叠式光接口存储器连接。

15.在一种可行的实施方式中,三维堆叠式光接口存储器通过三维异质集成结构与处理器连接。

16.本技术实施例有益效果如下:

17.本技术实施例设置光数据通信电路,通过光数据通信电路处理写入存储芯片的光数据和从存储芯片读取的光数据,从而无需经过其他元件即可实现光数据的存储和读取,缩短了光数据的传输路径,减少光数据的传输时间,提高光数据的传输效率,从而提高光数据存储和读取的效率。

18.此外,设置存储芯片包括第一键合面,接口芯片包括第二键合面,第一键合面与第二键合面形成三维异质集成结构,以将接口芯片与存储芯片三维堆叠连接,从而增大三维堆叠式光接口存储器处理光数据的带宽,降低三维堆叠式光接口存储器的功耗,同时减小了三维堆叠式光接口存储器的面积,进一步提高了三维堆叠式光接口存储器的使用灵活性。

附图说明

19.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本技术的限制。而且在整个附图中,用相同的参考符号表示相同的部件。在附图中:

20.图1为相关技术中光数据传输示意图;

21.图2为本技术提供的一种实施例的三维堆叠式光接口存储器结构示意图之一;

22.图3为本技术提供的一种实施例的光数据通信电路结构示意框图;

23.图4为本技术提供的一种实施例的电压转化电路结构示意图;

24.图5为本技术提供的一种实施例的三维堆叠式光接口存储器结构示意图之二;

25.图6为本技术提供的一种实施例的三维堆叠式光接口存储器结构示意图之三;

26.图7为本技术提供的一种实施例的三维堆叠式光接口存储器结构示意图之四;

27.图8为本技术提供的一种实施例的光数据处理装置结构示意框图;

28.图9为本技术提供的一种实施例的三维堆叠式光接口存储器与处理器的连接示意图。

29.其中,图1中附图标记与部件名称之间的对应关系为:

30.110’:存储器,112’:存储器光数据接口,120’:处理器,122’:处理器光数据接口。

31.其中,图2至图9中附图标记与部件名称之间的对应关系为:

32.100:三维堆叠式光接口存储器,110:存储芯片,120:接口芯片,130:光数据通信电路,132:光数据协议电路,134:存储控制电路,136:缓存电路,138:电压转化电路,141:电压逻辑电路,142:电压输入接口,143:电压输出接口,210:基板,212:引脚,300:光数据处理装置,310:光数据接收单元,320:处理器。

具体实施方式

33.为了能够更清楚地理解本实用新型的上述目的、特征和优点,下面结合附图和具体实施方式对本实用新型进行进一步的详细描述。需要说明的是,在不冲突的情况下,本技术的实施例及实施例中的特征可以相互组合。

34.在下面的描述中阐述了很多具体细节以便于充分理解本实用新型,但是,本实用新型还可以采用其他不同于在此描述的其他方式来实施,因此,本实用新型的保护范围并不受下面公开的具体实施例的限制。

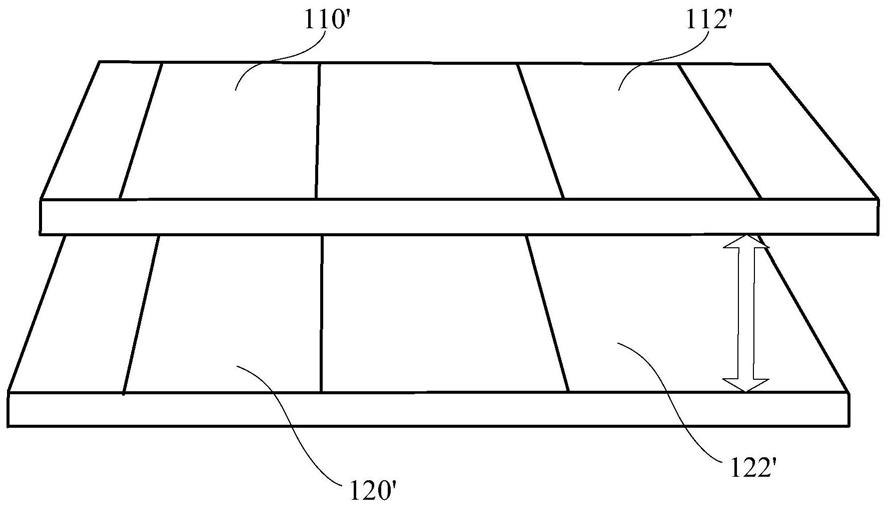

35.在一些示例中,光数据可以为通过光波进行传输的数据。如图1所示,相关技术中,在存储或读取光数据时,需要通过光数据协议对光数据进行处理。光数据协议通常存储在处理器120’上,从而在存储或读取光数据时,光数据需要在存储器110’和处理器120’之间进行传输。

36.具体地,在存储光数据时,需要将光数据发送至处理器120’,处理器120’上的光数据协议对光数据进行处理之后,再通过处理器光数据接口122’和存储器光数据接口112’,将光数据传输至存储器110’中进行存储。同样地,在读取光数据时,需要通过存储器光数据接口112’和处理器光数据接口122’,将存储器110’内存储的光数据传输至处理器120’,通过处理器120’上存储的光数据协议对光数据进行处理之后,再向外传输。

37.处理器120’与存储器110’相互独立设置,光数据在处理器120’和存储器110’之间的传输需要经过处理器120’、处理器光数据接口122’、存储器光数据接口112’、存储器110’,才能够实现存储和读取,光数据的传输路径长,延长了光数据的传输时间,降低了光数据的传输效率,从而降低了光数据的存储和读取效率。

38.为了解决上述技术问题中至少之一,第一方面,如图2所示,本技术实施例提供了一种三维堆叠式光接口存储器100,包括存储芯片110和接口芯片120。存储芯片110用于存储数据,存储芯片110包括第一键合面。接口芯片120包括第二键合面。第一键合面与第二键合面形成三维异质集成结构,以将接口芯片120与存储芯片110三维堆叠连接,形成三维堆叠式光接口存储器100。其中,如图3所示,接口芯片120包括光数据通信电路130,光数据通信电路130用于处理写入存储芯片110的数据和从存储芯片110读取的数据。

39.可以理解地,存储芯片110的材质可以为硅。在一些示例中,存储芯片110包括硅晶圆和半导体元件,半导体元件集成在硅晶圆上。

40.在一些示例中,存储芯片110的数量可以为一个或多个,从而增大三维堆叠式光接口存储器100的存储容量,提高三维堆叠式光接口存储器100的使用性能。

41.可以理解地,接口芯片120的材质可以为硅。在一些示例中,接口芯片120包括硅晶圆和半导体元件,半导体元件集成在硅晶圆上。

42.存储芯片110包括第一键合面,接口芯片120包括第二键合面。第一键合面与第二键合面形成三维异质集成结构。在一些示例中,接口芯片120可以通过混合键合的方式,与存储芯片110形成三维异质集成结构。

43.具体地,三维异质集成是将两个芯片(存储芯片110和接口芯片120)内部的金属层直接跨芯片互连,物理及电气参数遵循半导体制程工艺特征。与相关技术中相比,三维异质集成的互连密度无限接近于芯片内部金属层的互连密度。

44.存储芯片110和接口芯片120之间通过三维异质集成互连,逐层建立芯片内高密度

金属层互连,无需通过相关技术中的io接口或者io电路互连,而是直接建立跨芯片的高密度金属层互连,缩短了数据的传输距离,降低了存储芯片110和接口芯片120之间的通讯功耗,突破了访问带宽和访问功耗的瓶颈,避免了访问冲突,增大三维堆叠式光接口存储器100处理数据的带宽,降低三维堆叠式光接口存储器100的功耗。

45.接口芯片120包括光数据通信电路130。可以理解地,在进行数据存储时,光数据通信电路130能够对光数据进行处理,并将处理后的光数据写入存储芯片110。在进行数据读取时,光数据通信电路130能够对存储芯片110内的数据进行读取,对读取后的数据进行处理后向外界传输。

46.在一些示例中,光数据通信电路130的数量可以为一个或多个,进一步提高了数据的存储和读取效率。

47.通过在接口芯片120上设置光数据通信电路130,通过光数据通信电路130处理写入存储芯片110的数据和从存储芯片110读取的数据,从而无需通过其他元件,即可实现数据的存储和读取,缩短了数据的传输路径,减小了数据的传输时间,提高了光数据的存储和读取效率。

48.此外,设置存储芯片110与接口芯片120三维堆叠连接,一方面能够减小存储芯片110与接口芯片120的互连距离,进而缩短光数据的传输路径,减少光数据的传输时间,提高光数据的存储和读取效率。另一方面,三维异质集成是将两个芯片内部金属层直接跨芯片互连,物理及电气参数遵循半导体制程工艺特征,与通过输入输出(i/o)接口或者i/o电路实现的互连相比,三维异质集成的互连密度和速度有着极大提高,因此能够增大三维堆叠式光接口存储器100处理光数据的带宽,降低三维堆叠式光接口存储器100的功耗。同时由于三维异质集成的方式可以直接将芯片堆叠进行集成,不需要额外的线路板作为支撑,从而能够减小三维堆叠式光接口存储器100的面积,进一步提高了三维堆叠式光接口存储器100的使用灵活性。

49.在一些示例中,光数据通信电路130可以通过蚀刻或者集成等方式设置在接口芯片120上。

50.在一些示例中,如图2和图3所示,光数据通信电路130包括光数据协议电路132。光数据协议电路132用于存储光数据协议。

51.光数据通信电路130包括光数据协议电路132,可以理解地,光数据协议电路132的数量可以为一个或多个。不同光数据协议电路132上存储的光数据协议可以相同,也可以不同。

52.光数据协议电路132能够存储光数据协议,从而在处理写入存储芯片110的数据和从存储芯片110中读取的数据时,能够按照存储的光数据协议对数据进行处理。可以理解地,数据在经过光数据协议处理之后,无需经过其他元件进行处理,即可被存储芯片110识别并存储。相同地,存储芯片110内存储的光数据经过光数据协议处理之后,无需经过其他元件进行处理,即可向外发送。通过设置光数据协议电路132,缩短了光数据的传输路径,减少了光数据的传输时间,提高了光数据的传输效率,从而提高了三维堆叠式光接口存储器100对光数据的处理效率。

53.在一些示例中,光数据协议的数量可以为多个,满足对于不同类型光数据的处理需求,提高了三维堆叠式光接口存储器100的适用性。

54.在一些示例中,光数据协议包括xgmii协议、pmd协议、pma协议和pcs协议中至少一者。

55.具体地,光数据协议包括xgmii协议(gigabit medium independent interface,以太网接口协议)、pmd协议(physical media dependent,物理介质关联层接口协议)、pma(physical medium attachment,物理介质连接子层协议)和pcs(physical coding sublayer,物理编码子层协议)中的至少一者,从而使得三维堆叠式光接口存储器100能够满足不同光类型光数据的存储和读取需求,提高了三维堆叠式光接口存储器100的适用性和使用灵活性。

56.在一些示例中,如图3所示,光数据通信电路130还包括存储控制电路134。存储控制电路134与光数据协议电路132连接,存储控制电路134用于将光数据协议电路132处理后的数据写入存储芯片110;和存储控制电路134用于读取存储芯片110内存储的数据并传输给光数据协议电路132。

57.存储控制电路134与光数据协议电路132连接,可以理解地,存储控制电路134的数量可以为一个或多个。存储控制电路134与光数据协议电路132的数量可以相同,也可以不同。

58.在一些示例中,存储控制电路134可以通过铜线与光数据协议电路132连接。

59.具体地,在存储数据时,数据在经过光数据协议电路132处理之后,被存储控制电路134写入存储芯片110。在读取数据时,存储控制电路134读取存储芯片110内存储的数据,并将数据传输给光数据协议电路132,数据经过光数据协议电路132处理之后向外传输。

60.通过设置存储控制电路134,使得光数据协议电路132处理后的数据能够被写入存储芯片110,同时使得光数据协议电路132能够获取到存储芯片110内存储的数据,也即是实现了数据在光数据协议电路132和存储芯片110之间的传输,进一步确保了三维堆叠式光接口存储器100的使用可靠性。

61.在一些示例中,存储控制电路134可以为mc(memory controller,内存控制器)。

62.在一些示例中,如图3所示,光数据通信电路130还包括缓存电路136。存储控制电路134通过缓存电路136与光数据协议电路132连接,缓存电路136用于缓存数据。

63.可以理解地,缓存电路136的数量可以为一个或多个。缓存电路136与光数据协议电路132和存储控制电路134的数量可以相同,也可以不同。

64.在一些示例中,存储控制电路134通过铜线与缓存电路136连接,缓存电路136通过铜线与光数据协议电路132连接。

65.缓存电路136用于缓存数据,可以理解地,在存储数据时,数据被光数据协议电路132处理之后,传输至缓存电路136。数据在缓存电路136之内缓存之后,传输至存储控制电路134,并被存储控制电路134写入存储芯片110。在读取数据时,存储控制电路134读取存储芯片110内的数据,并将数据传输至缓存电路136,数据在缓存电路136中缓存之后,传输至光数据协议电路132。

66.通过在存储控制电路134和光数据协议电路132之间设置缓存电路136,使得数据在存储控制电路134和光数据协议电路132之间传递时,能够在缓存电路136中进行缓存,避免过多的数据同时传输至存储控制电路134或者光数据协议电路132,造成存储控制电路134或者光数据协议电路132中数据堆积,或者过少的数据传输至存储控制电路134或者光

数据协议电路132,降低光数据通信电路130对于数据的处理效率。

67.通过设置缓存电路136,使得数据在存储控制电路134和光数据协议电路132之间传递时能够进行缓存,避免传输过程中的数据量过大或者过小,进一步提高了数据的存储和读取效率,并且确保了数据在传输过程的可靠性。

68.在一些示例中,如图3和图4所示,光数据通信电路130包括电压转化电路138。电压转化电路138与存储芯片110和接口芯片120连接。电压转化电路138用于升高或降低接口芯片120的电压值和/或存储芯片110的电压值,以使接口芯片120和存储芯片110之间能够传输数据。

69.光数据通信电路130包括电压转化电路138,可以理解地,电压转化电路用于升高或降低电压。在一些示例中,电压转化电路138的数量可以为一个或多个。

70.具体地,如图4所示,电压转化电路138可以包括电压逻辑电路141、电压输入接口142和电压输出接口143。可以理解地,电压输入接口142通过电压逻辑电路141与电压输出接口143连接,从而使得电压逻辑电路141能够对输入电压进行转化并输出。

71.在一些示例中,电压逻辑电路141可以包括二极管、三极管、场效应管或者放大器等元器件,通过不同元器件之间的连接关系,实现电压转化的功能。

72.在一些示例中,电压输入接口142的数量为两个,分别用于获取存储芯片110和接口芯片120的电压。电压输出接口143的数量为两个,分别用于向存储芯片110和接口芯片120输出电压。

73.电压转化电路138与存储芯片110和接口芯片120连接,从而能够升高或者降低存储芯片110的电压值和/或接口芯片120中的电压值,使得存储芯片110和接口芯片120之间能够进行数据传输,提高了三维堆叠式光接口存储器100对于数据传输的稳定性和可靠性。

74.在一些示例中,电压转化电路138能够使得存储芯片110与接口芯片120的电压相等,提高了数据在存储芯片110和接口芯片120之间传输的可靠性。

75.在一些示例中,如图5和图6所示,存储芯片110的数量为至少两个。

76.可以理解地,存储芯片110的数量为至少两个,增大了三维堆叠式光接口存储器100的存储容量,进一步提高三维堆叠式光接口存储器100的使用性能,满足不同的存储需求。

77.在一些示例中,如图5和图6所示,至少两个存储芯片110分别与接口芯片120三维堆叠连接;和/或至少两个存储芯片110之间三维堆叠连接。

78.可以理解地,至少两个存储芯片110可以通过三维异质集成结构,分别与接口芯片120三维堆叠连接,和/或至少两个存储芯片110也可以通过三维异质集成结构相互堆叠连接。

79.在一些示例中,三维堆叠连接的方式包括wow(wafer on wafer,晶圆-晶圆)堆叠连接和cow(chip on wafer,晶圆-芯片)堆叠连接中至少一者,从而能够根据使用需求,设置不同的三维堆叠连接方式,提高了三维堆叠式光接口存储器100的适用性。

80.至少两个存储芯片110分别与接口芯片120三维堆叠连接,和/或至少两个存储芯片110之间三维堆叠连接之后,再与接口芯片120三维堆叠连接,增大了三维堆叠式光接口存储器100处理数据的带宽,提高三维堆叠式光接口存储器100对于数据的传输效率,降低三维堆叠式光接口存储器100的功耗,进一步提高三维堆叠式光接口存储器100的使用性

能。此外,通过三维异质集成结构实现三维堆叠连接,还能够进一步减小存三维堆叠式光接口存储器100的面积,提高三维堆叠式光接口存储器100的使用灵活性。

81.同时,至少两个存储芯片110能够通过不同的方式,与接口芯片120进行三维堆叠连接,使得三维堆叠式光接口存储器100能够满足不同的使用需求,提高三维堆叠式光接口存储器100的适用性。

82.在一些示例中,如图6所示,至少两个存储芯片110的面积之和小于接口芯片120的面积,从而使得至少两个存储芯片110能够分别与接口芯片120三维堆叠连接。

83.在一些示例中,如图7所示,至少两个存储芯片110中的任一个存储芯片110与接口芯片120三维堆叠连接,其余的存储芯片110通过tsv(through silicon via,硅通孔技术)与接口芯片120三维堆叠连接,满足不同的使用需求。

84.在一些示例中,如图6和图7所示,三维堆叠式光接口存储器100包括基板210。基板210与三维堆叠式光接口存储器100连接,基板210用于封装三维堆叠式光接口存储器100。在一些示例中,基板210上包括引脚212,通过引脚212与其他元件连接,使得三维堆叠式光接口存储器100能够与其他元件之间进行数据传输。在一些示例中,引脚212的数量可以为一个或多个。

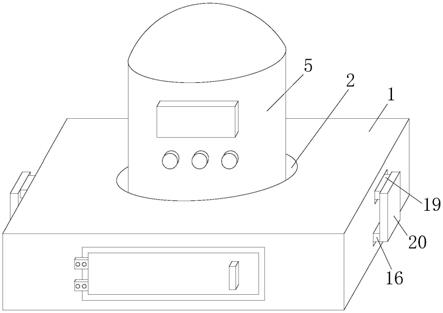

85.第二方面,如图8所示,本技术实施例提供了一种光数据处理装置300,包括光数据接收单元310、如上述第一方面的三维堆叠式光接口存储器100和处理器320。光数据接收单元310用于接收光数据。三维堆叠式光接口存储器100与光数据接收单元310连接,处理器320与三维堆叠式光接口存储器100连接。

86.本技术实施例的光数据处理装置300包括上述第一方面的三维堆叠式光接口存储器100,因此具有上述第一方面的全部有益效果,在此不再赘述。

87.在一些示例中,光数据接收单元310可以为光模块,光模块通过光接头与三维堆叠式光接口存储器100连接。具体地,光接头可以为rj45光接头。

88.在一些示例中,如图9所示,三维堆叠式光接口存储器100通过三维异质集成结构与处理器320连接。

89.三维堆叠式光接口存储器100通过三维异质集成结构与处理器320连接,从而能够增大光数据处理装置300处理光数据的带宽,降低光数据处理装置300的功耗,同时减小光数据处理装置300的面积,提高光数据处理装置300的使用灵活性。

90.在一个具体实施例中,如图6和图7所示,提供了一种三维堆叠式光接口存储器100。三维堆叠式光接口存储器100包括多个存储芯片110、接口芯片120和基板210。至少两个存储芯片110通过3d-ic(三维芯片)技术分别与接口芯片120三维堆叠连接,其余存储芯片110通过tsv(through silicon via,硅通孔技术)与接口芯片120三维堆叠连接,从而在增大三维堆叠式光接口存储器100的存储容量的基础上,进一步扩大了三维堆叠式光接口存储器100的带宽,缩短了光数据在三维堆叠式光接口存储器100内传输的路径,降低三维堆叠式光接口存储器100的功耗,提高了三维堆叠式光接口存储器100对于光数据的传输效率。此外,通过3d-ic(三维芯片)技术堆叠连接,还能够减三维堆叠式光接口存储器100的面积,提高三维堆叠式光接口存储器100的使用灵活性。

91.具体地,可以通过wow(wafer on wafer,晶圆-晶圆)连接或者cow(chip on wafer,晶圆-芯片)连接的方式,将接口芯片120和至少两个存储芯片110进行三维集成。

92.具体地,接口芯片120上集成有光数据通信电路130,光数据通信电路包括光数据协议电路132、存储控制电路134、缓存电路136和电压转化电路138。

93.光数据协议电路132上存储有光数据协议,具体地,在存储光数据时,光数据协议电路132按照存储的光数据协议对数据进行处理,并将处理后的数据传输至缓存电路136。数据在缓存电路136内进行缓存之后,通过存储控制电路134将输出写入存储芯片110。

94.在读取光数据时,存储控制电路134从存储芯片110上读取光数据,并将光数据传输至缓存电路136。光数据在缓存电路136中进行缓存之后,传输至光数据协议电路132,通过光数据协议电路132处理后向外界传输。

95.在一些示例中,存储控制电路134为内存控制器。

96.在一些示例中,光数据协议包括xgmii协议(gigabit medium independent interface,以太网接口协议)、pmd协议(physical media dependent,物理介质关联层接口协议)、pma(physical medium attachment,物理介质连接子层协议)和pcs(physical coding sublayer,物理编码子层协议)。

97.电压转化电路138与存储芯片110和接口芯片120连接。可以理解地,当存储芯片110与接口芯片120的电压不相等时,光数据无法在存储芯片110和接口芯片120之前进行传输。故而设置电压转化电路138,通过电压转化电路138升高或降低存储芯片110和接口芯片120中至少之一的电压值,使得二者的电压能够满足光数据的传输需求,实现光数据在存储芯片110和接口芯片120之间进行传递,提高了三维堆叠式光接口存储器100的使用可靠性。

98.通过设置光数据通信电路130,使得数据能够直接被存储或读取,无需经过其他元件,缩短了数据的传输路径,减少了数据的传输时间,提高了数据的传输效率。

99.在本实用新型中,术语“第一”、“第二”、“第三”仅用于描述的目的,而不能理解为指示或暗示相对重要性;术语“多个”则指两个或两个以上,除非另有明确的限定。术语“安装”、“相连”、“连接”、“固定”等术语均应做广义理解,例如,“连接”可以是固定连接,也可以是可拆卸连接,或一体地连接;“相连”可以是直接相连,也可以通过中间媒介间接相连。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本实用新型中的具体含义。

100.本实用新型的描述中,需要理解的是,术语“上”、“下”、“左”、“右”、“前”、“后”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或单元必须具有特定的方向、以特定的方位构造和操作,因此,不能理解为对本实用新型的限制。

101.在本说明书的描述中,术语“一个实施例”、“一些实施例”、“具体实施例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或特点包含于本实用新型的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或实例。而且,描述的具体特征、结构、材料或特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

102.以上仅为本实用新型的优选实施例而已,并不用于限制本实用新型,对于本领域的技术人员来说,本实用新型可以有各种更改和变化。凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。