技术特征:

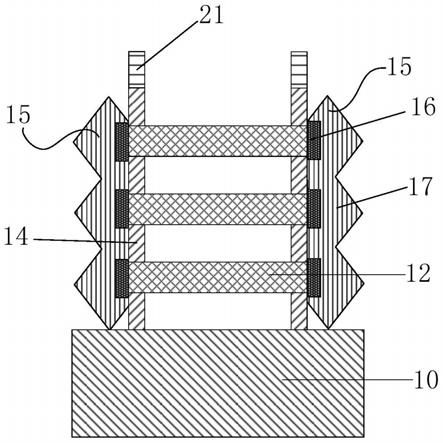

1.一种半导体器件,其特征在于,包括:半导体衬底;位于所述半导体衬底上的有源区,所述有源区包括沟道区、以及位于所述沟道区两侧的源/漏区;至少位于所述沟道区的侧壁的栅堆叠,以及位于所述栅堆叠两侧的侧墙;其中,沿着远离所述沟道区中心的方向,所述源/漏区的材料与所述沟道区的材料之间的刻蚀选择比逐渐增大。2.根据权利要求1所述的半导体器件,其特征在于,所述沟道区的材料包括si;所述源/漏区的材料包括sige;沿着远离所述沟道区中心的方向,所述源/漏区中ge的浓度逐渐增加。3.根据权利要求1所述半导体器件,其特征在于,所述栅堆叠位于所述沟道区的顶部和侧壁。4.根据权利要求1所述半导体器件,其特征在于,所述沟道区包括至少两个纳米线,所述源/漏区分别位于所述纳米线的两端;所述栅堆叠环绕每一个所述纳米线。5.根据权利要求1至4任一项所述的半导体器件,其特征在于,所述源/漏区均至少包括第一外延层和第二外延层;在水平方向上,沿着靠近所述沟道区中心的方向,所述第一外延层形成在所述沟道区的外侧,所述第二外延层形成在所述第一外延层远离所述沟道区的一侧,所述第一外延层与所述沟道区的刻蚀选择比为1。6.根据权利要求5所述的半导体器件,其特征在于,所述第一外延层的厚度大于或等于5埃。7.根据权利要求5所述的半导体器件,其特征在于,当所述源/漏区的材料包括sige时,所述第二外延层中ge的初始浓度大于1%。8.一种半导体器件的制造方法,其特征在于,包括:提供一半导体衬底;在所述半导体衬底上形成沟道区;在所述沟道区的两端外延形成源/漏区,其中,沿着远离所述沟道区中心的方向,所述源/漏区的材料与所述沟道区的材料之间的刻蚀选择比逐渐增大;至少在所述沟道区的侧壁形成栅堆叠。9.根据权利要求8所述的半导体器件的制造方法,其特征在于,所述沟道区的材料包括si,所述源/漏区的材料包括sige;沿着远离所述沟道区的中心的方向,所述源/漏区中ge的浓度逐渐增加。10.根据权利要求8所述的半导体器件的制造方法,其特征在于,所述在所述半导体衬底上形成沟道区,在所述沟道区的两端外延形成源/漏区包括:在所述半导体衬底上形成鳍片;所述鳍片具有源/漏区形成区、以及位于所述源/漏区形成区之间的沟道形成区;在所述沟道形成区的侧壁和顶壁形成牺牲栅和栅极侧墙;刻蚀所述鳍片的端部,保留鳍片端部的底部作为种子层;剩余的所述鳍片形成沟道区;以所述鳍片端部的底部作为种子层外延生长所述源/漏区;所述至少在所述沟道区的侧壁形成栅堆叠包括:

去除所述牺牲栅,至少在所述沟道区的侧壁形成所述栅堆叠。11.根据权利要求8所述的半导体器件的制造方法,其特征在于,所述在所述半导体衬底上形成沟道区包括:在所述半导体衬底上从下至上形成至少两组由牺牲层和半导体层构成的叠层;上述叠层具有源/漏区形成区、以及位于所述源/漏区形成区之间的沟道形成区;在所述沟道形成区的侧壁和顶壁形成牺牲栅和栅极侧墙;刻蚀所述叠层使得所述半导体层成为纳米线;至少两个所述纳米线构成所述沟道区;所述在所述沟道区的两端外延形成源/漏区包括:在所述纳米线的两端外延形成si层,并沿着远离所述纳米线中心的方向,增加ge的浓度。12.根据权利要求11所述的半导体器件的制造方法,其特征在于,所述在所述半导体衬底上形成沟道区后,在所述沟道区的两端外延形成源/漏区前,所述半导体器件的制造方法包括:在刻蚀后的所述牺牲层的两侧形成内侧墙;所述内侧墙和所述栅极侧墙构成侧墙;所述至少在所述沟道区的侧壁形成栅堆叠包括:去除所述牺牲栅,以及去除剩余所述牺牲层,环绕所述纳米线形成所述栅堆叠。

技术总结

本发明公开一种半导体器件及其制造方法,涉及半导体制造技术领域,以解决在去除位于沟道区之间、以及沟道区与半导体衬底之间的牺牲层的过程中,损伤到源/漏区,降低半导体器件性能的技术问题。所述半导体器件包括:半导体衬底、有源区、栅堆叠和侧墙。有源区位于半导体衬底上,有源区包括沟道区、以及位于沟道区两侧的源/漏区。至少位于沟道区的侧壁的栅堆叠,以及位于栅堆叠两侧的侧墙。其中,沿着远离沟道区中心的方向,源/漏区的材料与沟道区的材料之间的刻蚀选择比逐渐增大。本发明还提供了一种半导体器件的制造方法。种半导体器件的制造方法。种半导体器件的制造方法。

技术研发人员:吕寅准 高建峰 李俊杰 刘卫兵 卢一泓

受保护的技术使用者:真芯(北京)半导体有限责任公司

技术研发日:2020.08.24

技术公布日:2022/2/24

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。