被配置为进行电源门控操作的器件

1.相关申请的交叉引用

2.本技术要求2020年8月10日提交的申请号为10-2020-0099606的韩国专利申请的优先权,其全部内容通过引用合并于此。

技术领域

3.本公开的实施例涉及被配置为进行电源门控操作的器件。

背景技术:

4.在便携式电子器件中采用的半导体器件已经被设计为执行电源门控操作,以防止不必要的电能被消耗。电源门控操作可以包括用于禁止提供不必要的电力的操作和用于将电源电压的电平转换为各种不同的电压电平的操作。

技术实现要素:

5.根据一个实施例,一种器件可以包括开关控制信号生成电路和电源门控电路。开关控制信号生成电路可以被配置为控制基于第一电源电压与第二电源电压的比较结果来从模式信号生成第一开关控制信号和第二开关控制信号的操作,直到在加电时段结束之后执行模式寄存器设置操作为止。电源门控电路可以被配置为基于所述第一开关控制信号和所述第二开关控制信号来将电源电压驱动至所述第一电源电压或所述第二电源电压。

6.根据另一实施例,一种器件可以包括模式控制信号生成电路、开关控制信号驱动电路和电源门控电路。模式控制信号生成电路可以被配置为基于第一电源电压与第二电源电压的比较结果来生成模式控制信号,直到在加电时段结束之后执行模式寄存器设置操作为止。开关控制信号驱动电路可以被配置为基于所述模式控制信号和模式信号来生成第一开关控制信号和第二开关控制信号。电源门控电路可以被配置为当所述第一开关控制信号被激活时,根据所述电源电压的电平来将电源电压驱动至所述第一电源电压,并且被配置为当所述第二开关控制信号被激活时,将所述电源电压驱动至所述第二电源。

附图说明

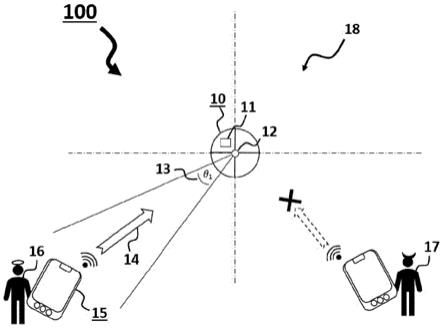

7.图1是示出根据本公开的一个实施例的器件的配置的框图。

8.图2是示出包括在图1中所示的器件中的开关控制信号生成电路的配置的框图。

9.图3是示出包括在图2中所示的开关控制信号生成电路中的模式控制信号生成电路的电路图。

10.图4示出了包括在图2中所示的开关控制信号生成电路中的开关控制信号驱动电路。

11.图5是示出包括在图1中所示的器件中的电源门控电路的电路图。

12.图6、图7、图8、图9、图10、图11、图12和图13示出了图1至图5中所示的器件的操作。

具体实施方式

13.在下面的实施例的描述中,当参数被称为“预定的”时,其可能旨在表示当在过程或算法中使用该参数时预先确定该参数的值。参数的值可以在过程或算法开始时被设定,或者可以在过程或算法执行的时段期间被设定。

14.将理解的是,尽管本文中使用术语“第一”、“第二”、“第三”等来描述各种元件,但是这些元件不应受这些术语的限制。这些术语仅用于将一个元件与另一个元件区分开。因此,在不脱离本公开的教导的情况下,在一些实施例中的第一元件可以在其它实施例中被称为第二元件,反之亦然。

15.此外,将理解的是,当一个元件被称为“连接”或“耦接”到另一元件时,它可以直接连接或耦接到另一元件,或者可以存在中间元件。相反,当一个元件被称为“直接连接”或“直接耦接”至另一元件时,则不存在中间元件。

16.逻辑“高”电平和逻辑“低”电平可以用于描述电信号的逻辑电平。具有逻辑“高”电平的信号可以与具有逻辑“低”电平的信号区分开。例如,当具有第一电压的信号对应于具有逻辑“高”电平的信号时,具有第二电压的信号对应于具有逻辑“低”电平的信号。在一个实施例中,逻辑“高”电平可以被设定为比逻辑“低”电平的电压电平高的电压电平。此外,根据实施例,信号的逻辑电平可以被设定为不同或相反。例如,在一个实施例中具有逻辑“高”电平的某个信号可以被设定为在另一实施例中具有逻辑“低”电平。

17.在下文中将参照附图来描述本公开的各种实施例。然而,本文中描述的实施例仅用于说明性目的,并非旨在限制本公开的范围。

18.如图1中所示,根据实施例的器件100可以包括命令解码器(com_dec)101、模式寄存器103、加电信号生成电路(pwr_gen)105、开关控制信号生成电路(sw_cnt_gen)107、电源门控电路109和控制电路110。在一个实施例中,器件100可以是半导体器件。

19.命令解码器101可以基于设置信号ca来生成模式寄存器设置信号mrs。设置信号ca可以包括由外部设备(未示出)提供的命令和地址。外部设备可以位于与器件100分开的位置,并且外部设备可以包括主机和控制器。命令解码器101可以对包括在设置信号ca中的命令进行解码,以生成被激活以执行模式寄存器设置操作的模式寄存器设置信号mrs。可以通过模式寄存器设置操作将关于器件100的各种内部操作的信息储存在模式寄存器103中。关于各种内部操作的信息可以包括关于突发长度的信息、关于等待时间的信息、用于电源门控操作的模式信息等。

20.模式寄存器103可以从命令解码器101接收模式寄存器设置信号mrs。当执行模式寄存器设置操作时,模式寄存器103可以提取并储存包括在设置信号ca中的模式信息(用于电源门控操作),并且可以将储存的模式信息作为模式信号dvfs_mrs输出。模式信号dvfs_mrs的逻辑电平可以被设定,从而根据频率调节供应给控制电路110的电源电压vdds的电平。模式信号dvfs_mrs可以被设定具有用于动态电压频率缩放(dynamic voltage frequency scaling,dvfs)的第一逻辑电平或第二逻辑电平。模式信号dvfs_mrs可以被设定为具有第一逻辑电平,以将供应给控制电路110的电源电压vdds以高频驱动至第一电源电压vdd1,并且可以被设定为具有第二逻辑电平,以将供应给控制电路110的电源电压vdds以低频驱动至第二电源电压vdd2。第一电源电压vdd1和第二电源电压vdd2可以是由外部设备提供的电源电压,并且第一电源电压vdd1可以被设定为比第二电源电压vdd2高。高频是

指比预定频率高的频率,而低频是指比预定频率低的频率。尽管结合第一逻辑电平是逻辑“低”电平并且第二逻辑电平是逻辑“高”电平的情况描述了本实施例,但是本实施例仅是本公开的示例。因此,本公开不限于第一逻辑电平是逻辑“低”电平并且第二逻辑电平是逻辑“高”电平的情况。

21.加电信号生成电路105可以从外部设备接收第一电源电压vdd1和第二电源电压vdd2。加电信号生成电路105可以基于第一电源电压vdd1和第二电源电压vdd2来生成加电信号pwrb。加电信号生成电路105可以在加电时段期间生成具有第一逻辑电平的加电信号pwrb,并且可以在加电时段结束时生成具有从第一逻辑电平改变为第二逻辑电平的电平的加电信号pwrb。在一个实施例中,尽管加电时段被设定为从第一电源电压vdd1和第二电源电压vdd2被施加到加电信号生成电路105的时间点一直到在第一电源电压vdd1和第二电源电压vdd2都被升高到高于预定目标电平时的时间点为止,但本公开不限于此。例如,在一些其它实施例中,加电时段可以被设定为从第一电源电压vdd1或第二电源电压vdd2被施加到加电信号生成电路105的时间点一直到第一电源电压vdd1或第二电源电压vdd2升高到高于预定目标电平时的时间点为止。

22.开关控制信号生成电路107可以从命令解码器101接收模式寄存器设置信号mrs,可以从模式寄存器103接收模式信号dvfs_mrs,并且可以从加电信号生成电路105接收加电信号pwrb。开关控制信号生成电路107还可以从外部设备接收第一电源电压vdd1和第二电源电压vdd2。在将加电信号pwrb设定为具有第一逻辑电平的加电时段期间,开关控制信号生成电路107可以基于加电信号pwrb来执行初始化操作。初始化操作可以被执行以将内部节点初始化为预定的逻辑电平。开关控制信号生成电路107可以控制将第一电源电压vdd1的逻辑电平与第二电源电压vdd2的逻辑电平彼此进行比较,以从模式信号dvfs_mrs生成第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2的操作,直到在加电时段终止之后执行模式寄存器设置操作为止。在一个实施例中,如果在第一电源电压vdd1高于第二电源电压vdd2的情况下执行模式寄存器设置操作,则开关控制信号生成电路107可以生成其中一个根据模式信号dvfs_mrs的逻辑电平而被选择性地激活的第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2。即,当模式信号dvfs_mrs具有第一逻辑电平时,开关控制信号生成电路107可以生成被激活的第一开关控制信号sw_cnt1和被去激活的第二开关控制信号sw_cnt2。另外,当模式信号dvfs_mrs具有第二逻辑电平时,开关控制信号生成电路107可以生成被去激活的第一开关控制信号sw_cnt1和被激活的第二开关控制信号sw_cnt2。根据实施例,被激活的第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2的逻辑电平可以被设定为不同。在一些其它实施例中,如果在第一电源电压vdd1低于第二电源电压vdd2的情况下执行模式寄存器设置操作,则开关控制信号生成电路107可以生成被激活的第一开关控制信号sw_cnt1和被去激活的第二开关控制信号sw_cnt2,而与模式信号dvfs_mrs的逻辑电平无关。

23.电源门控电路109可以从开关控制信号生成电路107接收第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2,并且可以从外部设备接收第一电源电压vdd1和第二电源电压vdd2。当第一开关控制信号sw_cnt1被激活时,电源门控电路109可以将供应给控制电路110的电源电压vdds驱动至第一电源电压vdd1。当第二开关控制信号sw_cnt2被激活时,电源门控电路109可以将供应给控制电路110的电源电压vdds驱动至第二电源电压

vdd2。当第一开关控制信号sw_cnt1被激活时,电源门控电路109可以检测电源电压vdds的电平,以将电源电压vdds驱动至第一电源电压vdd1。在一个实施例中,当第一开关控制信号sw_cnt1被激活时,仅当电源电压vdds的电平变得低于预定电平时,电源门控电路109才可以将电源电压vdds驱动至第一电源电压vdd1以降低器件100的功耗。

24.控制电路110可以从电源门控电路109接收电源电压vdds。控制电路110可以控制各种内部操作。例如,可以利用用于控制接收和输出数据的操作的电路来实现控制电路110。控制电路110可以接收电源电压vdds以控制器件100的内部操作,所述电源电压vdds的电平根据频率来调整。提供给控制电路110的电源电压vdds可以通过动态电压频率缩放(dvfs)被设定为在高频下具有高电平,并且可以通过动态电压频率缩放(dvfs)被设定为在低频下具有低电平。当第一电源电压vdd1和第二电源电压vdd2具有相同的电平时,可以将供应给控制电路110的电源电压vdds驱动至第一电源电压vdd1,而与频率无关。

25.如图2中所示,开关控制信号生成电路107可以包括模式控制信号生成电路121和开关控制信号驱动电路123。

26.模式控制信号生成电路121可以从加电信号生成电路(图1中的105)接收加电信号pwrb,可以从外部设备接收第一电源电压vdd1和第二电源电压vdd2,并且可以从命令解码器(图1中的101)接收模式寄存器设置信号mrs。模式控制信号生成电路121可以基于加电信号pwrb、第一电源电压vdd1、第二电源电压vdd2和模式寄存器设置信号mrs来生成模式控制信号mcs。模式控制信号生成电路121可以生成在加电时段期间被去激活的模式控制信号mcs。模式控制信号生成电路121可以检测第一电源电压vdd1和第二电源电压vdd2的电平,以生成模式控制信号mcs,直到在加电时段结束之后执行模式寄存器设置操作为止。例如,模式控制信号生成电路121可以在第一电源电压vdd1高于第二电源电压vdd2时生成被去激活的模式控制信号mcs,并且可以在第一电源电压vdd1等于或低于第二电源电压vdd2时生成被激活的模式控制信号mcs。在执行模式寄存器设置操作之后,模式控制信号生成电路121可以生成保持去激活状态的模式控制信号mcs,而与第一电源电压vdd1和第二电源电压vdd2的电平无关。

27.开关控制信号驱动电路123可以从加电信号生成电路(图1中的105)接收加电信号pwrb,可以从模式控制信号生成电路121接收模式控制信号mcs,并且可以从模式寄存器(图1中的103)接收模式信号dvfs_mrs。开关控制信号驱动电路123可以基于加电信号pwrb、模式控制信号mcs和模式信号dvfs_mrs来生成第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2。开关控制信号驱动电路123可以在加电时段期间基于加电信号pwrb来执行初始化操作。在加电时段结束之后执行模式寄存器设置操作为止,开关控制信号驱动电路123可以接收模式控制信号mcs,以判断在模式寄存器设置操作之后是否根据模式信号dvfs_mrs还是与模式信号dvfs_mrs无关来生成第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2。在一个实施例中,当在模式控制信号mcs被去激活的情况下执行模式寄存器设置操作时,开关控制信号驱动电路123可以生成其中一个根据模式信号dvfs_mrs而被选择性地激活的第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2。可替代地,当在模式控制信号mcs被激活的情况下执行模式寄存器设置操作时,开关控制信号驱动电路123可以生成被激活的第一开关控制信号sw_cnt1和被去激活的第二开关控制信号sw_cnt2,而与模式信号dvfs_mrs无关。

28.如图3中所示,模式控制信号生成电路121可以包括电压检测信号生成电路125、操作检测信号生成电路127和模式控制信号输出电路129。

29.电压检测信号生成电路125可以包括第一分压生成电路131、第二分压生成电路133、电压比较器135和反相缓冲器137。第一分压生成电路131可以包括串联耦接在第一电源电压vdd1的供应端子与接地电压vss的供应端子之间的电阻元件r131和r133,并且可以基于电阻元件r131和r133的电阻值来对第一电源电压vdd1进行分压,以经由电阻元件r131和r133之间的节点nd131生成并输出第一分压vdiv1。第二分压生成电路133可以包括串联耦接在第二电源电压vdd2的供应端子与接地电压vss的供应端子之间的电阻元件r135和r137,并且可以基于电阻元件r135和r137的电阻值来对第二电源电压vdd2进行分压,以经由电阻元件r135与r137之间的节点nd133来生成并输出第二分压vdiv2。在本实施例中,电阻元件r131、r133、r135和r137可以具有相同的电阻值。因此,第一分压vdiv1与第一电源电压vdd1之比可以被设定为等于第二分压vdiv2与第二电源电压vdd2之比。电压比较器135可以将第一分压vdiv1与第二分压vdiv2进行比较。在一个实施例中,电压比较器135可以在第一分压vdiv1高于第二分压vdiv2时输出具有逻辑“高”电平的信号,并且可以在第一分压vdiv1等于或小于第二分压vdiv2时输出具有逻辑“低”电平的信号。反相缓冲器137可以反相缓冲电压比较器135的输出信号,以生成并输出电压检测信号det。电压检测信号生成电路125可以将第一分压vdiv1与第二分压vdiv2进行比较,以生成电压检测信号det。电压检测信号生成电路125可以在第一分压vdiv1高于第二分压vdiv2时生成具有逻辑“低”电平的电压检测信号det,并且可以在第一分压vdiv1等于或低于第二分压vdiv2时生成具有逻辑“高”电平的电压检测信号det。

30.操作检测信号生成电路127可以包括上拉驱动器141、下拉驱动器143和操作检测信号锁存电路145。上拉驱动器141可以耦接在第一电源电压vdd1的供应端子与节点nd141之间,并且下拉驱动器143可以耦接在节点nd141与接地电压vss的供应端子之间。操作检测信号锁存电路145可以耦接到节点nd141。上拉驱动器141可以基于加电信号pwrb来上拉节点nd141的电平。上拉驱动器141可以利用pmos晶体管来实现。在这种情况下,pmos晶体管可以在加电时段期间通过具有逻辑“低”电平的加电信号pwrb而被导通,以将节点nd141上拉到第一电源电压vdd1。下拉驱动器143可以基于模式寄存器设置信号mrs来下拉节点nd141的电平。下拉驱动器143可以利用nmos晶体管来实现。在这种情况下,nmos晶体管可以通过经由模式寄存器设置操作而具有逻辑“高”电平的模式寄存器设置信号mrs而被导通,以将节点nd141下拉至接地电压vss。操作检测信号锁存电路145可以锁存并缓冲节点nd141的信号,以生成操作检测信号mrsd。操作检测信号生成电路127可以在加电时段期间将操作检测信号mrsd初始化为逻辑“高”电平。在执行模式寄存器设置操作之后,操作检测信号生成电路127可以生成保持逻辑“低”电平的操作检测信号mrsd。

31.模式控制信号输出电路129可以从电压检测信号生成电路125接收电压检测信号det,可以从加电信号生成电路(图1中的105)接收加电信号pwrb,并且可以从操作检测信号生成电路127接收操作检测信号mrsd。模式控制信号输出电路129可以基于电压检测信号det、加电信号pwrb和操作检测信号mrsd来生成模式控制信号mcs。模式控制信号输出电路129可以在加电时段期间根据具有逻辑“低”电平的加电信号pwrb来生成被去激活为具有逻辑“低”电平的模式控制信号mcs。模式控制信号输出电路129可以基于通过检测第一电源电

压vdd1和第二电源电压vdd2的电平而生成的电压检测信号det来生成模式控制信号mcs,直到在加电时段终止之后执行模式寄存器设置操作为止。例如,当第一电源电压vdd1高于第二电源电压vdd2时,模式控制信号输出电路129可以通过具有逻辑“低”电平的电压检测信号det来生成被去激活为具有逻辑“低”电平的模式控制信号mcs。另外,当第一电源电压vdd1小于或等于第二电源电压vdd2时,模式控制信号输出电路129可以通过具有逻辑“高”电平的电压检测信号det来生成被激活为具有逻辑“高”电平的模式控制信号mcs。在执行模式寄存器设置操作之后,模式控制信号输出电路129可以通过具有逻辑“低”电平的操作检测信号mrsd来生成保持去激活状态(即,逻辑“低”电平)的模式控制信号mcs。

32.如图4中所示,开关控制信号驱动电路123可以包括:第一驱动器151、第二驱动器153、传输控制信号生成电路155和开关控制信号输出电路157。第一驱动器151可以耦接在第一电源电压vdd1的供应端子与节点nd151之间,并且第二驱动器153可以耦接在节点nd151与接地电压vss的供应端子之间。传输控制信号生成电路155可以耦接到节点nd151。

33.第一驱动器151可以基于加电信号pwrb来上拉节点nd151的电平。可以利用pmos晶体管来实现第一驱动器151。在这种情况下,pmos晶体管可以在加电时段期间通过具有逻辑“低”电平的加电信号pwrb而被导通,以将节点nd151上拉到第一电源电压vdd1。第二驱动器153可以基于模式控制信号mcs来下拉节点nd151的电平。第二驱动器153可以利用nmos晶体管来实现。在这种情况下,nmos晶体管可以通过被激活为具有逻辑“高”电平的模式控制信号mcs而被导通,以将节点nd151下拉至接地电压vss。

34.传输控制信号生成电路155可以锁存并缓冲节点nd151的信号,以生成传输控制信号tcnt。在加电时段期间,当通过具有逻辑“低”电平的加电信号pwrb将节点nd151上拉为具有第一电源电压vdd1时,传输控制信号生成电路155可以将传输控制信号tcnt初始化为逻辑“高”电平。当通过被激活为具有逻辑“高”电平的模式控制信号mcs来将节点nd151下拉至具有接地电压vss,直到在加电时段结束之后执行模式寄存器设置操作为止时,传输控制信号生成电路155可以生成具有逻辑“低”电平的传输控制信号tcnt。当模式控制信号mcs被去激活为具有逻辑“低”电平时,传输控制信号生成电路155可以保持具有逻辑“高”电平的传输控制信号tcnt。

35.开关控制信号输出电路157可以包括:传输元件159_1、电平移位器159_3、第一反相缓冲器159_5和第二反相缓冲器159_7。传输元件159_1可以利用对传输控制信号tcnt和模式信号dvfs_mrs执行逻辑与非运算的与非门来实现。当传输控制信号tcnt具有逻辑“高”电平时,传输元件159_1可以将模式信号dvfs_mrs反相缓冲以输出模式信号dvfs_mrs的反相缓冲信号。当传输控制信号tcnt具有逻辑“低”电平时,传输元件159_1可以输出具有逻辑“高”电平的信号,而与模式信号dvfs_mrs无关。电平移位器159_3可以将传输元件159_1的输出信号的电平移位,以输出传输元件159_1的输出信号的移位电平。包括电平移位器159_3的开关控制信号输出电路157的配置可以仅仅是本公开的示例。因此,开关控制信号输出电路157不限于图4中所示的示例。第一反相缓冲器159_5可以将电平移位器159_3的输出信号反相缓冲,以生成并输出第二开关控制信号sw_cnt2。第二反相缓冲器159_7可以将第一反相缓冲器159_5的输出信号反相缓冲,以生成并输出第一开关控制信号sw_cnt1。

36.在加电时段期间,开关控制信号驱动电路123可以基于具有逻辑“低”电平的加电信号pwrb而执行用于将传输控制信号tcnt初始化为逻辑“高”电平的初始化操作。基于被输

入到开关控制信号驱动电路123直到在加电时段结束之后执行模式寄存器设置操作为止的模式控制信号mcs,开关控制信号驱动电路123可以在模式寄存器设置操作之后生成第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2。例如,在模式控制信号mcs被去激活为具有逻辑“低”电平的情况下,当执行模式寄存器设置操作时,开关控制信号驱动电路123可以生成其中一个根据模式信号dvfs_mrs而被选择性地激活的第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2。例如,当模式信号dvfs_mrs具有逻辑“低”电平时,开关控制信号驱动电路123可以生成被激活为具有逻辑“高”电平的第一开关控制信号sw_cnt1和被去激活为具有逻辑“低”电平的第二开关控制信号sw_cnt2。可替代地,当模式信号dvfs_mrs具有逻辑“高”电平时,开关控制信号驱动电路123可以生成被去激活为具有逻辑“低”电平的第一开关控制信号sw_cnt1和被激活为具有逻辑“高”电平的第二开关控制信号sw_cnt2。在模式控制信号mcs被激活为具有逻辑“高”电平的情况下,当执行模式寄存器设置操作时,开关控制信号驱动电路123可以生成被激活为具有逻辑“高”电平的第一开关控制信号sw_cnt1和被去激活为具有逻辑“低”电平的第二开关控制信号sw_cnt2,而与模式信号dvfs_mrs的逻辑电平无关。

37.如图5中所示,电源门控电路109可以包括开关驱动信号生成电路161、第一电源电压驱动电路163、电源分压电路165和第二电源电压驱动电路167。

38.开关驱动信号生成电路161可以从开关控制信号生成电路107接收第一开关控制信号sw_cnt1,并且可以从电源分压电路165接收分压电源电压dvdds。开关驱动信号生成电路161可以基于第一开关控制信号sw_cnt1、参考电压vref和分压电源电压dvdds来生成开关驱动信号sw_drv。参考电压vref可以设定为具有恒定电平。当第一开关控制信号sw_cnt1被去激活为具有逻辑“低”电平时,开关驱动信号生成电路161可以生成被去激活为具有逻辑“低”电平的开关驱动信号sw_drv。当第一开关控制信号sw_cnt1被激活为具有逻辑“高”电平时,开关驱动信号生成电路161可以将分压电源电压dvdds的电平与参考电压vref的电平进行比较,以生成开关驱动信号sw_drv。在一个实施例中,在第一开关控制信号sw_cnt1被激活为具有逻辑“高”电平的情况下,当分压电源电压dvdds低于参考电压vref时,开关驱动信号生成电路161可以生成被激活为具有逻辑“高”电平的开关驱动信号sw_drv。可替代地,在第一开关控制信号sw_cnt1被激活为具有逻辑“高”电平的情况下,当分压电源电压dvdds等于或高于参考电压vref时,开关驱动信号生成电路161可以生成被去激活为具有逻辑“低”电平的开关驱动信号sw_drv。

39.第一电源电压驱动电路163可以从开关驱动信号生成电路161接收开关驱动信号sw_drv。在一个实施例中,第一电源电压驱动电路163可以利用耦接在第一电源电压vdd1的供应端子与节点nd161之间的nmos晶体管163_1来实现。当开关驱动信号sw_drv被激活为具有逻辑“高”电平时,第一电源电压驱动电路163可以将经由节点nd161输出的电源电压vdds驱动至第一电源电压vdd1。在第一电源电压vdd1高于第二电源电压vdd2的情况下,当通过模式寄存器设置操作将模式信号dvfs_mrs设定为具有逻辑“低”电平并且分压电源电压dvdds低于参考电压vref时,第一电源电压驱动电路163可以接收被激活为具有逻辑“高”电平的开关驱动信号sw_drv,以将电源电压vdds驱动至第一电源电压vdd1。在第一电源电压vdd1高于第二电源电压vdd2的情况下,当通过模式寄存器设置操作将模式信号dvfs_mrs设定为具有逻辑“低”电平并且分压电源电压dvdds等于或高于参考电压vref时,第一电源电

压驱动电路163可以接收被去激活为具有逻辑“低”电平的开关驱动信号sw_drv,以禁止电源电压vdds被驱动。在第一电源电压vdd1和第二电源电压vdd2具有相同的电平的情况下,仅当分压电源电压dvdds低于参考电压vref时,第一电源电压驱动电路163才可以将电源电压vdds驱动至第一电源电压vdd1,而与模式信号dvfs_mrs的电平无关。

40.电源分压电路165可以包括串联耦接的第一电源分压元件165_1和第二电源分压元件165_3。第一电源分压元件165_1可以利用耦接在节点nd161与节点nd163之间以用作电阻元件的nmos晶体管来实现。在这种情况下,用作第一电源分压元件165_1的nmos晶体管可以具有彼此电耦接的栅极和漏极。第二电源分压元件165_3可以利用耦接在节点nd163与接地电压vss的供应端子之间以用作电阻元件的nmos晶体管来实现。在这种情况下,用作第二电源分压元件165_3的nmos晶体管可以具有彼此电耦接的栅极和漏极。电源分压电路165可以根据第一电源分压元件165_1的电阻值与第二电源分压元件165_3的电阻值之比来对电源电压vdds进行分压,以生成经由节点nd163输出的分压电源电压dvdds。当第一电源分压元件165_1和第二电源分压元件165_3具有相同的电阻值时,电源分压电路165可以生成具有电源电压vdds的一半电平的分压电源电压dvdds。

41.第二电源电压驱动电路167可以从开关控制信号生成电路(图1中的107)接收第二开关控制信号sw_cnt2。在一个实施例中,第二电源电压驱动电路167可以利用耦接在第二电源电压vdd2的供应端子与节点nd161之间的nmos晶体管167_1来实现。当第二开关控制信号sw_cnt2被激活为具有逻辑“高”电平时,第二电源电压驱动电路167可以将经由节点nd161输出的电源电压vdds驱动至第二电源电压vdd2。在第一电源电压vdd1高于第二电源电压vdd2的情况下,当通过模式寄存器设置操作将模式信号dvfs_mrs设定为具有逻辑“高”电平时,第二电源电压驱动电路167可以接收被激活为具有逻辑“高”电平的第二开关控制信号sw_cnt2,以将电源电压vdds驱动至第二电源电压vdd2。

42.在下文中将参照图6至图13来描述具有前述配置的器件100的操作。

43.首先,在下文中将参照图6和图7来描述在加电时段期间执行的器件100的操作。

44.如图6中所示,可以将第一电源电压vdd1和第二电源电压vdd2施加到器件100(参见步骤s101),并且可以验证第一电源电压vdd1和第二电源电压vdd2是否升高到高于预定目标电平,即,是否保持加电时段(参见步骤s103)。在保持加电时段的情况下,可以执行初始化操作(参见步骤s105)。

45.参考图7和图8,示出了在加电时段期间执行的初始化操作。首先,如图7中所示,在模式控制信号生成电路121中,在加电时段期间,可以通过具有逻辑“低(l)”电平的加电信号pwrb来将操作检测信号mrsd初始化为具有逻辑“高(h)”电平,并且可以将模式控制信号mcs初始化为具有逻辑“低(l)”电平。在这种情况下,模式寄存器设置信号mrs可以被去激活为具有逻辑“低”电平。接下来,如图8中所示,在开关控制信号驱动电路123中,在加电时段期间,通过具有逻辑“低(l)”电平的加电信号pwrb可以将传输控制信号tcnt初始化为逻辑“高(h)”电平。

46.如图6中所示,可以根据第一电源电压vdd1与第二电源电压vdd2的比较结果来生成电压检测信号det,直到在加电时段结束之后执行模式寄存器设置操作为止(参见步骤s107),并且可以通过电压检测信号det来生成模式控制信号mcs(参见步骤s109)。随后,可以通过模式控制信号mcs来生成传输控制信号tcnt(参见步骤s111)。可以判断是否执行了

模式寄存器设置操作(参见步骤s113)。当在步骤s113验证出没有执行模式寄存器设置操作时,可以生成电压检测信号det、模式控制信号mcs和传输控制信号tcnt(参见步骤s107、s109和s111)。当在步骤s113验证出执行了模式寄存器设置操作时,模式控制信号mcs可以被去激活(参见步骤s115,mcs被去激活)。可以基于在执行模式寄存器设置操作之前生成的传输控制信号tcnt来生成第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2(参见步骤s117)。例如,在传输控制信号tcnt被激活时,生成其中一个根据模式信号dvfs_mrs而被选择性地激活的第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2,并且在传输控制信号tcnt被去激活时,可以生成被激活的第一开关控制信号sw_cnt1和被去激活的第二开关控制信号sw_cnt2,而与模式信号dvfs_mrs无关。电源电压vdds可以通过第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2来驱动(参见步骤s119),并且电源电压vdds可以被供应给控制电路110(参见步骤s121)。

47.图9至图11示出了在第一电源电压vdd1高于第二电源电压vdd2的情况下,执行器件100的操作,直到在加电时段结束之后执行模式寄存器设置操作为止。首先,如图9中所示,在模式控制信号生成电路121中,操作检测信号mrsd可以通过具有逻辑“高(h)”电平的加电信号pwrb和具有逻辑“低(l)”电平的模式寄存器设置信号mrs来维持与逻辑“高(h)”电平相对应的初始化状态,直到在加电时段结束之后执行模式寄存器设置操作为止。因为第一分压vdiv1被生成为高于第二分压vdiv2以生成具有逻辑“低(l)”电平的电压检测信号det,所以从模式控制信号输出电路129输出的模式控制信号mcs可以被去激活为具有逻辑“低(l)”电平。随后,如图10中所示,如果在模式控制信号生成电路121中执行模式寄存器设置操作,则可以通过具有逻辑“高(h)”电平的模式寄存器设置信号mrs来将操作检测信号mrsd生成为具有逻辑“低(l)”电平。因此,模式控制信号mcs可以维持与逻辑“低(l)”电平相对应的去激活状态。接下来,如图11中所示,当基于保持去激活状态的模式控制信号mcs而使传输控制信号tcnt保持与逻辑“高(h)”电平相对应的初始化状态时,可以根据模式信号dvfs_mrs来选择性地激活第一开关控制信号sw_cnt1和第二开关控制信号sw_cnt2中的一个。例如,当模式信号dvfs_mrs具有逻辑“低(l)”电平时,第一开关控制信号sw_cnt1可以被激活为具有逻辑“高(h)”电平,使得电源电压vdds被驱动至第一电源电压vdd1。另外,当模式信号dvfs_mrs具有逻辑“高(h)”电平时,第二开关控制信号sw_cnt2可以被激活为具有逻辑“高(h)”电平,使得电源电压vdds被驱动至第二电源电压vdd2。

48.图12和图13示出了在具有相同电平的第一电源电压vdd1和第二电源电压vdd2被施加到器件100的情况下,执行器件100的操作,直到在加电时段结束之后执行模式寄存器设置操作为止。首先,如图12中所示,在模式控制信号生成电路121中,操作检测信号mrsd可以通过具有逻辑“高(h)”电平的加电信号pwrb和具有逻辑“低”电平的模式寄存器设置信号mrs来维持与逻辑“高(h)”电平相对应的初始化状态,直到在加电时段结束之后执行模式寄存器设置操作为止。因为第一分压vdiv1和第二分压vdiv2被生成为具有相同的电平以生成具有逻辑“高(h)”电平的电压检测信号det,所以从模式控制信号输出电路129输出的模式控制信号mcs可以被激活为具有逻辑“高(h)”电平。随后,如图13中所示,在开关控制信号驱动电路123中,可以通过被激活为具有逻辑“高(h)”电平的模式控制信号mcs来使传输控制信号tcnt去激活为具有逻辑“低(l)”电平。因此,与模式信号dvfs_mrs无关,第一开关控制信号sw_cnt1可以被激活为具有逻辑“高(h)”电平,而第二开关控制信号sw_cnt2可以被去

激活为具有逻辑“低(l)”电平。

49.如上所述,根据本公开的实施例的器件100可以在具有相同电平的第一电源电压vdd1和第二电源电压vdd2被施加到器件100时激活第一开关控制信号sw_cnt1,而与模式信号dvfs_mrs无关,并且可以根据供应给控制电路110的电源电压vdds的电平来控制电源电压vdds的驱动。因此,可以减少器件100的功耗。另外,在第一电源电压vdd1高于第二电源电压vdd2时,器件100可以根据模式信号dvfs_mrs和工作频率来将电源电压vdds的电平驱动至第一电源电压vdd1或第二电源电压vdd2。

50.已经结合如上所述的一些实施例公开了这些构思。本领域技术人员将理解的是,在不脱离本公开的范围和精神的情况下,可以进行各种修改、添加和替换。因此,不应从限制性的观点而是从说明性的观点来考虑本说明书中公开的实施例。构思的范围不限于以上描述,而是由所附权利要求限定,并且等同范围内的所有独特特征均应解释为包括在构思中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。