技术特征:

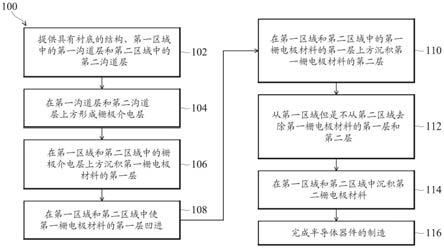

1.一种形成半导体器件的方法,包括:提供结构,所述结构具有衬底和位于所述衬底的表面上方并且邻近介电部件的半导体层的堆叠件,所述半导体层的每个在所述相应堆叠件内彼此垂直间隔开;形成包裹所述半导体层和所述介电部件的每个的栅极介电层;在所述栅极介电层上方和所述介电部件上方沉积所述第一栅电极材料的第一层;使所述介电部件上的所述第一栅电极材料的所述第一层凹进至所述介电部件的顶面下方第一高度;在所述第一栅电极材料的所述第一层上方沉积所述第一栅电极材料的第二层;去除所述衬底的第一区域中的所述第一栅电极材料以暴露所述栅极介电层的位于所述第一区域中的部分而不去除所述衬底的第二区域中的所述第一栅电极材料;以及在所述栅极介电层的暴露部分上方和所述第一栅电极材料的剩余部分上沉积第二栅电极材料。2.根据权利要求1所述的方法,其中,所述第一区域是n型器件区域,所述第二区域是p型器件区域。3.根据权利要求1所述的方法,还包括:在所述第二栅电极材料上方形成覆盖层,其中,所述覆盖层的形成封闭所述介电部件和所述半导体层之间的气隙。4.根据权利要求1所述的方法,其中,沉积所述第一层包括在相邻半导体层上形成所述第一层的相对表面,所述相对表面彼此间隔开第一距离,以及其中,沉积所述第二层包括沉积具有等于或大于所述第一距离的厚度的第二层。5.根据权利要求1所述的方法,其中,沉积所述第一层包括在所述介电部件上形成所述第一层的第一侧面以及在所述半导体层中的一个的侧壁上形成所述第一层的第二侧面,所述第二侧面面向所述第一侧面,以及其中,沉积所述第二层包括形成在所述第一侧面和所述第二侧面之间合并的所述第二层。6.根据权利要求1所述的方法,其中,沉积所述第二层包括在所述介电部件上方进行沉积,所述方法还包括在沉积所述第二层之后,使所述第二层凹进以暴露所述介电部件的侧壁表面。7.根据权利要求1所述的方法,其中,沉积所述第二栅电极材料包括在所述第一区域中沉积所述第二栅电极材料的包裹所述半导体层的第一部分以及在所述第二区域中的所述半导体层的顶面上方沉积所述第二栅电极材料的第二部分。8.一种形成半导体器件的方法,包括:在第一对介电部件之间的第一区域中的衬底上方形成第一纳米结构;在第二对介电部件之间的第二区域中的衬底上方形成第二纳米结构;形成包裹所述第一纳米结构和所述第二纳米结构的栅极介电层;在所述第一对介电部件和所述第二对介电部件上形成第一栅电极材料的包裹所述栅极介电层的第一层;使所述第一层凹进以暴露所述第一对介电部件和所述第二对介电部件的顶部;在所述第一对介电部件和所述第二对介电部件的暴露顶部上以及所述第一层上形成所述第一栅电极材料的第二层;

去除所述第一对介电部件之间的所述第一栅电极材料以暴露所述栅极介电层的部分;以及在所述栅极介电层的位于所述第一对介电部件之间的所述暴露部分上以及在第一栅电极材料的位于所述第二对介电部件之间的剩余部分上沉积第二栅电极材料。9.根据权利要求8所述的方法,其中,所述第一区域是n型器件区域,并且所述第二区域是p型器件区域。10.一种半导体器件,包括:半导体衬底,具有衬底表面;半导体层,位于所述半导体衬底上方并且沿垂直于所述衬底表面的第一方向与所述半导体衬底分隔开;介电部件,邻近所述半导体层,从所述衬底表面沿所述第一方向延伸,所述介电部件具有面向所述半导体层的第一侧面和与所述第一侧面相对的第二侧面;栅极介电层,具有包裹所述半导体层的第一部分和位于所述介电部件的所述第一侧面上的第二部分;第一栅电极层,其中,所述第一栅电极层包括包裹所述栅极介电层的所述第一部分的第一段,以及从所述第一段延伸至所述栅极介电层的所述第二部分的侧壁表面的第二段,所述第二段具有高于所述第一栅电极层的所述第一段的顶面并且低于所述介电部件的顶面的顶面;以及第二栅电极层,位于所述第一栅电极层的所述第一段的顶面上、位于所述第一栅电极层的所述第二段的顶面和侧壁表面上以及位于所述介电部件的所述第一侧面上。

技术总结

结构具有位于衬底上方并且邻近介电部件的半导体层的堆叠件。形成包裹每层和介电部件的栅极电介质。在栅极电介质和介电部件上方沉积第一栅电极材料的第一层。介电部件上的第一层凹进至介电部件的顶面下方第一高度。在第一层上方沉积第一栅电极材料的第二层。去除衬底的第一区域中的第一栅电极材料以暴露栅极电介质的位于第一区域中的部分,而保留衬底的第二区域中的第一栅电极材料。在栅极电介质的暴露部分上方和第一栅电极材料的剩余部分上方沉积第二栅电极材料。本申请的实施例还涉及半导体器件及其形成方法。导体器件及其形成方法。导体器件及其形成方法。

技术研发人员:徐崇威 江国诚 黄懋霖 朱龙琨 余佳霓 程冠伦 王志豪

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:2021.08.02

技术公布日:2022/2/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。