技术特征:

1.一种装置,包括:存储器控制器电路;以及存储器控制器接口,所述存储器控制器接口耦合到所述存储器控制器电路,并且适于将所述存储器控制器电路耦合到存储器阵列的解码器电路,所述存储器阵列包括地址线,所述地址线包括字线(wl)和位线(bl),并且所述解码器电路包括分别耦合到所述wl或者分别耦合到所述bl的多个开关;其中,所述存储器控制器电路用于通过使所述多个开关中的选定开关将耦合到所述选定开关的对应选定地址线的偏置从所述解码器电路的空闲状态下的浮置偏置改变为正偏置或负偏置,而不将与所述多个开关中的取消选定开关对应的取消选定地址线处的偏置从所述空闲状态下的所述浮置偏置改变,来控制所述解码器电路。2.根据权利要求1所述的装置,其中,所述存储器控制器电路用于通过引起所述地址线处的所述浮置偏置来引起所述解码器电路的所述空闲状态。3.根据权利要求2所述的装置,其中,所述浮置偏置对应于浮置参考地电压(flvss)。4.根据权利要求1所述的装置,其中,所述多个开关均包括一对互补晶体管,所述一对互补晶体管包括正型(p型)金属氧化物半导体晶体管(pmos)和负型(n型)mos晶体管(nmos)。5.根据权利要求4所述的装置,其中,所述存储器控制器电路用于通过关断所述多个开关中的每一个的所述pmos和所述nmos来在所述空闲状态下引起所述地址线处的所述浮置偏置。6.根据权利要求5所述的装置,其中,所述存储器控制器电路用于通过以下操作在所述空闲状态下引起所述地址线处的所述浮置偏置:将对应于正选择偏置电压(vpps)的栅极偏置施加到所述多个开关中的每一个的所述pmos;将对应于负选择偏置电压(vnns)的栅极偏置施加到所述多个开关中的每一个的所述nmos;将等于参考地电压(vss)或vpps的源极电压施加到所述多个开关中的每一个的所述pmos(gp);以及将等于vss或vnns的源极电压施加到所述多个开关中的每一个的所述nmos(gn)。7.根据权利要求4所述的装置,其中,所述存储器控制器电路用于通过将对应于参考地电压(vss)的栅极偏置施加到所述选定开关的所述pmos和所述nmos两者,同时与所述空闲状态相比,保持所述取消选定开关中的每一个的所述pmos和所述nmos两者的栅极偏置不变,来使所述选定开关将耦合到所述选定开关的所述对应选定地址线的所述偏置从所述空闲状态下的浮置偏置改变为所述正偏置或所述负偏置。8.根据权利要求4所述的装置,其中,所述存储器控制器电路用于在多个存储器操作之后,使所述解码器电路从所述空闲状态改变为刷新状态并且返回到所述空闲状态,每个存储器操作涉及将选定地址线偏置到正电压值或负电压值,随后使地址线返回到所述空闲状态,其中,所述刷新状态对应于所述解码器电路的其中所述地址线被偏置在不是浮置电压的已知电压的状态。9.根据权利要求8所述的装置,其中,所述已知电压对应于参考地电压(vss)。

10.根据权利要求8所述的装置,其中,所述刷新状态包括正刷新状态或负刷新状态中的至少一种,在所述正刷新状态中,所述多个开关中的每一个的所述pmos关断并且所述多个开关中的每一个的所述nmos导通,在所述负刷新状态中,所述多个开关中的每一个的所述nmos关断并且所述多个开关中的每一个的所述pmos导通。11.一种系统,包括:存储器阵列,所述存储器阵列包括存储器单元和地址线,所述地址线包括字线(wl)和位线(bl);存储器控制器电路;wl解码器电路,所述wl解码器电路耦合到所述存储器控制器电路,并且包括分别耦合到所述wl的多个wl开关;以及bl解码器电路,所述bl解码器电路耦合到所述存储器控制器电路,并且包括分别耦合到所述bl的多个bl开关;其中,所述存储器控制器电路用于:通过使所述多个wl开关中的选定wl开关将耦合到所述选定wl开关的对应选定wl的偏置从所述wl解码器电路的空闲状态下的浮置wl偏置改变为正wl偏置或负wl偏置,而不将与所述多个wl开关中的取消选定wl开关对应的取消选定wl处的wl偏置从所述wl解码器电路的所述空闲状态下的所述浮置wl偏置改变,来控制所述wl解码器电路;并且通过使所述多个bl开关中的选定bl开关将耦合到所述选定bl开关的对应选定bl的偏置从所述bl解码器电路的空闲状态下的浮置bl偏置改变为正bl偏置或负bl偏置,而不将与所述多个bl开关中的取消选定bl开关对应的取消选定bl处的bl偏置从所述bl解码器电路的所述空闲状态下的所述浮置bl偏置改变,来控制所述bl解码器电路。12.根据权利要求11所述的系统,其中,所述存储器控制器电路用于执行以下操作中的至少一个:通过引起所述wl处的所述浮置wl偏置来引起所述wl解码器电路的所述空闲状态,或者通过引起所述bl处的所述浮置bl偏置来引起所述bl解码器电路的所述空闲状态。13.根据权利要求12所述的系统,其中,所述浮置wl偏置或所述浮置bl偏置中的至少一个对应于浮置参考地电压(flvss)。14.根据权利要求11所述的系统,其中,所述多个wl开关和所述多个bl开关均包括一对互补晶体管,所述一对互补晶体管包括正型(p型)金属氧化物半导体晶体管(pmos)和负型(n型)mos晶体管(nmos)。15.根据权利要求14所述的系统,其中,所述存储器控制器电路用于通过关断所述多个wl开关和所述多个bl开关中的每一个的所述pmos和所述nmos来在所述空闲状态下引起所述浮置wl偏置和所述浮置bl偏置。16.根据权利要求15所述的系统,其中,所述存储器控制器电路用于通过以下操作引起所述wl解码器电路的所述空闲状态下的所述浮置wl偏置和所述bl解码器电路的所述空闲状态下的所述浮置bl偏置:将对应于正选择偏置电压(vpps)的栅极偏置施加到所述多个wl开关和所述多个bl开关中的每一个的所述pmos;将对应于负选择偏置电压(vnns)的栅极偏置施加到所述多个wl开关和所述多个bl开

关中的每一个的所述nmos;将等于参考地电压(vss)或vpps的源极电压施加到所述多个wl开关和所述多个bl开关中的每一个的所述pmos(gp);以及将等于vss或vnns的源极电压施加到所述多个wl开关和所述多个bl开关中的每一个的所述nmos(gn)。17.根据权利要求14所述的系统,其中,所述存储器控制器电路用于执行以下操作中的至少一个:通过将对应于参考地电压(vss)的栅极偏置施加到所述选定wl开关的所述pmos和所述nmos两者,同时与所述wl解码器电路的所述空闲状态相比,保持所述取消选定wl开关中的每一个的所述pmos和所述nmos两者的栅极偏置不变,来使所述wl开关将耦合到所述wl开关的所述对应选定wl的所述偏置从所述wl解码器电路的所述空闲状态下的浮置wl偏置改变为所述正wl偏置或所述负wl偏置;或通过将对应于参考地电压(vss)的栅极偏置施加到所述选定bl开关的所述pmos和所述nmos两者,同时与所述bl解码器电路的所述空闲状态相比,保持所述取消选定bl开关中的每一个的所述pmos和所述nmos两者的栅极偏置不变,来使所述bl开关将耦合到所述bl开关的所述对应选定bl的所述偏置从所述bl解码器电路的所述空闲状态下的浮置bl偏置改变为所述正bl偏置或所述负bl偏置。18.一种对存储器阵列中的存储器单元进行寻址的方法,所述存储器阵列包括地址线,所述地址线包括字线(wl)和位线(bl),所述方法包括:控制存储器阵列的解码器电路,所述解码器电路包括分别耦合到所述wl或者分别耦合到所述bl的多个开关;以及使所述多个开关中的选定开关将耦合到所述选定开关的对应选定地址线的偏置从所述解码器电路的空闲状态下的浮置偏置改变为正偏置或负偏置,而不将与所述多个开关中的取消选定开关对应的取消选定地址线处的偏置从所述空闲状态下的所述浮置偏置改变。19.根据权利要求18所述的方法,还包括通过引起所述地址线处的所述浮置偏置来引起所述解码器电路的所述空闲状态。20.根据权利要求19所述的方法,其中,所述浮置偏置对应于浮置参考地电压(flvss)。21.根据权利要求18所述的方法,其中,所述多个开关均包括一对互补晶体管,所述一对互补晶体管包括正型(p型)金属氧化物半导体晶体管(pmos)和负型(n型)mos晶体管(nmos)。22.根据权利要求21所述的方法,还包括通过关断所述多个开关中的每一个的所述pmos和所述nmos来在所述空闲状态下引起所述地址线处的所述浮置偏置。23.根据权利要求22所述的方法,还包括通过以下操作在所述空闲状态下引起所述地址线处的所述浮置偏置:将对应于正选择偏置电压(vpps)的栅极偏置施加到所述多个开关中的每一个的所述pmos;将对应于负选择偏置电压(vnns)的栅极偏置施加到所述多个开关中的每一个的所述nmos;将等于参考地电压(vss)或vpps的源极电压施加到所述多个开关中的每一个的所述

pmos(gp);以及将等于vss或vnns的源极电压施加到所述多个开关中的每一个的所述nmos(gn)。24.一种或多种计算机可读介质,所述一种或多种计算机可读介质包括指令,所述指令在由一个或多个处理器执行时,使所述一个或多个处理器执行根据以上权利要求18-23中任一项所述的方法。

技术总结

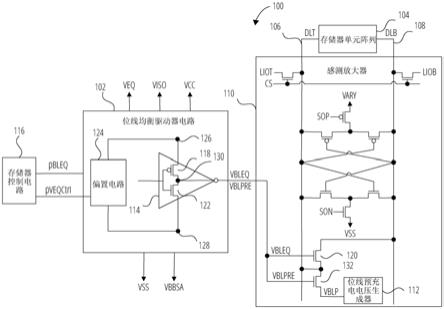

一种对存储器阵列中的存储器单元进行寻址的方法、装置和系统,存储器阵列包括地址线,地址线包括字线(WL)和位线(BL)。该方法包括:控制存储器阵列的解码器电路,存储器阵列包括多条WL和多条BL,解码器电路包括分别耦合到WL或者分别耦合到BL的多个开关;以及使多个开关中的选定开关将耦合到选定开关的对应选定地址线的偏置从解码器电路的空闲状态下的浮置偏置改变为正偏置或负偏置,而不将与多个开关中的取消选定开关对应的取消选定地址线处的偏置从空闲状态下的浮置偏置改变。偏置从空闲状态下的浮置偏置改变。偏置从空闲状态下的浮置偏置改变。

技术研发人员:B

受保护的技术使用者:英特尔公司

技术研发日:2021.07.21

技术公布日:2022/2/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。