1.本案是有关于一种网络通讯装置,且特别是有关于一种提供时间同步的网络装置。

背景技术:

2.网络时间协定(network time protocol,ntp)是运用在网络装置之间的时间同步标准协定。随着电子元件的精密度提升,也发展出更高精确度的时间同步标准,ieee 1588的精确时间协定(precision time protocol,ptp)因应而生。举例而言,在布署许多网络装置的环境中,做为主要装置(master device)的网络交换器可以提供时钟信息,透过在封包中携带时钟信息来提供给做为从属装置(slave device)的网络装置,使得从属装置可以使用该时钟信息来校正本地时钟,达到与主要装置的时钟同步。

3.一般来说,网络装置搭载的网络晶片内建有计数器,而计数器的位元数则影响计数值的数值范围。举例而言,若计数器为32个位元数,则表示计数器在计数4294967296(即2

32

)次之后,会因为溢位(overflow)而从0开始重新计数。换言之,在精度为1纳秒(nanosecond,ns)的时候,计数器只能提供0秒~4.294967295秒此区间内的计数值范围。由于超过此区间后计数器会重新计数,因此该数值范围并无法提供充足的日历时间tod(time of day)。

4.另一方面,目前的网络装置,例如网络交换器,是透过诸如媒体存取控制晶片(media access control chip,mac chip)之类的网络晶片来负责封包的接收及传送,因此需仰赖媒体存取控制晶片内的时间戳章计数器(timestamp counter)提供的数值,来记录接收及传送封包的时间。由于媒体存取控制晶片的时间戳章计数器的位元数有限,无法提供充足的日历时间,使得在基于精确时间协定下,搭载这样媒体存取控制晶片的网络交换器并无法作为主要装置(master device)。

5.除此之外,网络交换器若欲做为主要装置并执行一步骤同步模式(1-step synchronization),则网络交换器中搭载的实体层电路必须具备将发送时间填入封包中的能力,因此实体层电路将有较高的规格要求,而使得网络交换器的成本提高。

6.依照ieee1588协定,一步骤同步模式是指主要装置只透过同步封包传送时间t1给从属装置,无需再发出跟随封包(follow-up),请参照图1,其绘示主要装置100与从属装置200操作于一步骤同步模式的示意图。主要装置100只需传送具备时间t1信息的同步封包(sync)至从属装置200,而此时间t1为主要装置100传送同步讯息的传送时间。从属装置200于时间t2收到此同步讯息后,于时间t3传送延迟请求封包(delay request)至主要装置100。主要装置100于时间t4时收到此延迟请求封包。回应此延迟请求封包,主要装置100会再次发送具备时间(t4)信息的延迟回应封包(delay response)至从属装置200。透过这4个时间信息,从属装置200可以计算延迟时间,并使用此时间信息来更新本地时钟。一步骤同步模式可以提升时间更新效率,然而,需要特定硬件规格才能实现。

7.据此,有必要对于如何在不增加晶片成本下让网络交换器具有提供一步骤同步模

式的能力。

技术实现要素:

8.发明内容旨在提供本揭示内容的简化摘要,以使阅读者对本案内容具备基本的理解。此发明内容并非本揭示内容的完整概述,且其用意并非在指出本案实施例的重要/关键元件或界定本案的范围。以下将说明本案的网络装置及同步方法可使主要装置不需额外的硬件成本,即可达成对从属装置之间的一步骤同步。

9.根据本案的一实施例,揭示一种网络装置经配置以发送一同步封包至一从属装置,其中该同步封包至少包括一时间戳记栏位及一校正栏位。网络装置包括计数电路、通讯晶片及处理器。计数电路用以提供一日历时间tod。通讯晶片包括一第一端口以及一第二端口以及具有一位元数n的一时间戳电路。处理器耦接于该通讯晶片的该第一端口。其中处理器经配置以:根据该日历时间tod及该位元数n取得一余数r;以及根据该日历时间tod及该余数r填入该同步封包。

10.根据一实施例,其中该处理器对该日历时间tod与该位元数n进行mod函数运算以取得该余数r。

11.根据一实施例,其中该处理器对该日历时间tod与该位元数n进行相除运算以取得该余数r及一商数q。

12.根据一实施例,其中还包括该第一端口是设定为一般模式;该第二端口是设定为透通模式;其中,该处理器将该日历时间tod填入该时间戳记栏位以及将该余数r的补数-r填入该校正栏位。

13.根据一实施例,其中还包括该第一端口是设定为一般模式;该第二端口是设定为透通模式;其中,该处理器将该日历时间tod与该第一余数r1相减后的结果填入该时间戳记栏位以及将该校正栏位填入0值或空值。

14.根据一实施例,其中还包括:该通讯晶片于接收一延迟请求封包时,记录一延迟请求封包输入时间ti

req

;该计数电路提供一延迟请求封包接收日历时间tod

req

;以及该处理器经配置以:依据该延迟请求封包接收日历时间tod

req

与该位元数n以取得一对应的商数q

req

以及一对应的余数r

req

;以及依据该对应的商数q

req

、该位元数n以及该延迟请求封包输入时间ti

req

以产生一延迟回应封包。

15.根据一实施例,其中该处理器依该延迟请求封包输入时间ti

req

小于该对应的余数r

req

时,将该对应的商数q

req

加1。

16.根据另一实施例,揭示一种网络装置经配置以发送一同步封包至一从属装置,该网络装置于一第一同步封包的周期中取得一第一日历时间tod1、一第一余数r1以及一第一晶片接收时间ti1。其中该同步封包至少包括一时间戳记栏位及一校正栏位。网络装置包括计数电路、通讯晶片及处理器。通讯晶片包括一第一端口、一第二端口以及具有一位元数n的一时间戳电路。其中该第一端口与该第二端口是设定为透通模式,且对应接收该第一同步封包时取得该第一晶片接收时间ti1及对应接收该第二同步封包时取得一第二晶片接收时间ti2。处理器耦接于该通讯晶片的该第一端口。其中处理器经配置以根据该第二日历时间tod2、该第一余数r1以及该第一晶片接收时间ti1以填入该第二同步封包。

17.根据一实施例,其中该处理器更经配置以:根据该第二日历时间tod2及该位元数n

取得一第二余数r2;以及将该第二余数r2填入该第二同步封包。

18.根据一实施例,其中该处理器对该第二日历时间tod2与该位元数n进行mod函数运算以取得该第二余数r2。

19.根据一实施例,其中该处理器对该第二日历时间tod2与该位元数n进行相除运算以取得该第二余数r2。

20.根据一实施例,其中该处理器以该第二日历时间tod2、该第二余数r2以及该第一晶片接收时间ti1减去该第一余数r1的差值进行加总后的结果填入该第二同步封包的该时间戳记栏位,并且将该第二余数r2的一补数-r2填入该第二同步封包的该校正栏位。

21.根据一实施例,其中该处理器将该第二日历时间tod2与该第一晶片接收时间ti1减掉该第一余数r1的差值进行加总后的结果填入该第二同步封包的该时间戳记栏位,并且将该第二同步封包的该校正栏位填入0值或空值。

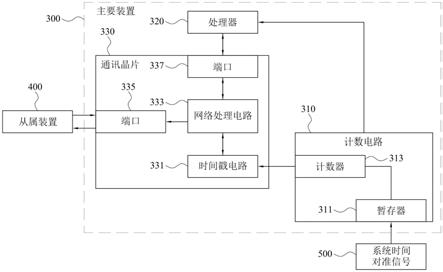

22.根据一实施例,其中更包括:该通讯晶片于接收一延迟请求封包时,记录一延迟请求封包输入时间ti

req

;该计数电路提供一延迟请求封包接收日历时间tod

req

;以及该处理器配置以:依据该延迟请求封包接收日历时间tod

req

与该位元数n取得一对应的商数q

req

以及一对应的余数r

req

;以及依据该对应的商数q

req

、该位元数n以及该延迟请求封包输入时间ti

req

以产生一延迟回应封包。

23.根据一实施例,其中该处理器依该延迟请求封包输入时间ti

req

小于该对应的余数r

req

时,将该对应的商数q

req

加1。

附图说明

24.以下详细描述结合随附附图阅读时,将有利于较佳地理解本揭示文件的态样。应注意,根据说明上实务的需求,附图中各特征并不一定按比例绘制。实际上,出于论述清晰的目的,可能任意增加或减小各特征的尺寸。

25.图1绘示主要装置与从属装置操作于一步骤同步的示意图。

26.图2绘示根据本案一些实施例中的一种网络装置的功能方块示意图。

27.图3绘示根据本案一些实施例中的一种操作于主从架构的同步方法的流程图。

28.图4绘示根据本案一些实施例中的一种操作于主从架构的同步方法的流程图。

29.图5绘示根据本案一些实施例中的一种操作于主从架构的同步方法的流程图。

30.【符号说明】

31.100,300:主要装置

32.200,400:从属装置

33.310:计数电路

34.311:暂存器

35.313:计数器

36.320:处理器

37.330:通讯晶片

38.331:时间戳电路

39.333:网络处理电路

40.335:端口

41.337:端口

42.500:系统时间对准信号

43.s310~s330,s405~s425:步骤

44.s505~s530:步骤

具体实施方式

45.以下揭示内容提供许多不同实施例,以便揭示实施本案的不同特征。当然,该些实例仅为示例性且并不欲为限制性。举例而言,本案中使用“第一”、“第二”等用语描述元件,仅是用以区别以相同或相似的元件或操作,该用语并非用以限定本案的技术元件,亦非用以限定操作的次序或顺位。另外,本案可在各实例中重复元件符号及/或字母,并且相同的技术用语可使用相同及/或不同的元件符号于各实施例。此重复是出于简明性及清晰的目的,且本身并不指示所论述的各实施例及/或配置之间的关系。

46.于本案中,以下所述的网络通讯装置包括第二层装置(例如交换器)、第三层装置(例如路由器),以及第二层装置与第三层装置的混和型网络装置等。本案的装置与方法并不限于是特定哪一些厂牌或者开放式系统互联模型(open system interconnection model,osi)的哪一个特定堆叠。所有支援osi模型底层(例如第一层至第四层)的堆叠功能的网络装置以及支援这些堆叠功能的程序码及其虚拟机器,均属本案的范畴。为便于表达,以下使用网络装置此一技术用语来说明。

47.请参照图2,其绘示本发明实施例主要装置300的硬件方块示意图。于本实施例中,主要装置300会接收系统时间对准信号(systemtime alignment signal)500,来校准计数电路310的日历时间tod(time of day,tod)。主要装置300根据日历时间tod传送携带时间信息的同步封包,从属装置400可依该同步封包中的时间信息更新其本身的时钟,借以达成与主要装置300之间的时钟同步。

48.如图2所示,主要装置300包括计数电路310、处理器320以及通讯晶片330。计数电路310耦接于处理器320以及通讯晶片330。计数电路310配置以提供日历时间tod。另外,计数电路310依据时间提供装置(未绘示)提供的日历时间及每秒脉冲信号(1pulse per second,1pps),将自身的时间计数值与计数频率与标准时间同步。其中,时间提供装置例如是全球卫星定位系统或可提供标准日历时间及脉冲的装置。其中,标准时间例如是世界协调时间(coordinated universal time,简称utc)。

49.于本实施例中,计数电路310更包括暂存器311以及计数器313。暂存器311用以暂存由时间提供装置提供的信号。计数器313用以计数及提供日历时间,且依暂存于暂存器311中的信号来校正日历时间与计数频率。于本实施例中,计数器313是80位元长度的计数器,可提供0~2

80-1的计数值,据以提供日历时间tod。于本实施例中,计数电路310可以是场域可程序化逻辑门阵列(field programmable gate array,fpga)来实现。

50.通讯晶片330包括时间戳电路331、网络处理电路333、端口335以及端口337。时间戳电路311用以提供计数值。于本实施例中,时间戳电路311是一n位元数的计数器,可于0~2

n-1之间循环计数,于本实施例中,n为32,因此时间戳电路311可由0计数至4294967295后溢位,重新由0开始计数。也就是说,计数值单位为1纳秒(nano second,ns)时,时间戳电路331将于0~4.294967295秒之间循环计数。需特别说明的是,时间戳电路311的位元数愈多,

能提供的时间信息愈充足,但其电路所需的成本愈高。

51.于一些实施例中,端口335、337是用以接收、传送封包的接口。网络处理电路333配置以将封包转发至指定的端口,并依据接收、传送的端口为透通模式或一般模式,决定是否对封包的特定栏位进行接收与传送时间的计算。于本实施例中,端口被设定为透通模式时,于该端口所接收的封包,其封包中特定栏位值将减除该封包的接收时间;或者,于该端口传送的封包,其封包中特定栏位值将与传送时间相加。于本实施例中,封包的特定栏位为校正栏位(correction field)。

52.于一些实施例中,通讯晶片330可以是媒体存取控制(mac)晶片或layer2/layer3网络晶片。

53.依据ieee 1588精确时间协定,于一步骤同步模式中,主要装置300传送给从属装置400的同步封包中携带同步封包的传送时间t1。从属装置400于时间t2收到此同步封包,并透过解析此同步封包取得该同步封包的传送时间t1。接着,从属装置400于时间t3传送延迟请求封包。主要装置300于接收此延迟请求封包时记录接收时间t4,再透过延迟回应封包将此时间t4发送给从属装置400。如此一来,从属装置400可使用时间t1~t4来计算并补偿时间误差,完成时间同步。

54.一般来说,主要装置若欲以一步骤同步模式进行同步,实体层硬件需能够于传送同步封包的同时将传送时间t1填入同步封包的时间戳记栏位(timestamp)。如此一来,做为主要装置的网络装置欲具备实施一步骤同步模式的能力时,不论是实体层电路或内建实体层电路的媒体存取控制晶片皆需具备较高的硬件规格,如此将提高网络装置的建置成本。

55.以下实施例将说明本案实施例的网络装置在其做为主要装置时,在搭载有限位元数的时间戳电路331的通讯晶片下如何产生及发送同步封包,以执行一步骤同步模式,提供时间t1及时间t4供从属装置同步。于本实施例中,有限位元位数是指其位元数并不足以提供充足日历时间信息的位元数。于此补充说明,于实施上,计数电路310计数的日历时间tod与时间戳电路331的计数值是时常地进行同步,以维持计数频率的相同,而于本实施例中,对日历时间tod与时间戳电路331的位元数n运算得到的余数值是相等于时间戳电路331的计数值,意即余数值可以等同处理器320取得日历时间tod当下,时间戳电路331当时的计数值。

56.请参照图3,其绘示根据本发明实施例的同步封包的产生及发送流程图。以下说明请一并参照图2及图3,以说明本发明实施例的主要装置300产生并传送同步封包(sync packet)的流程。此外,需特别说明的是,于本实施例中,主要装置300的端口335需设定为透通模式,而端口337则需设定为一般模式。

57.于步骤s310,处理器320读取计数电路310中的日历时间tod。于本步骤中,处理器320欲产生同步封包时,会先读取计数电路310的计数值,以取得日历时间tod。

58.于步骤s315,处理器320将日历时间tod与时间戳电路331的位元数n进行运算以取得余数r。

59.于本步骤中,根据时间戳电路331的位元数n,处理器310将日历时间tod与位元数n进行运算后得到余数r。举例来说,处理器310将日历时间tod与位元数n进行mod函数运算即可得到余数r。于另一实施例中,处理器310是将日历时间tod除以位元数n后得到商数q及余数r。需提醒的是,取得余数r的方式,只要使日历时间tod满足以下公式(1)即可:

r) te,意即t1=q

×2n

te

77.根据另一实施例,从属装置400收到的同步封包的时间信息如表2-1所示。

78.表2-1:封包中的栏位对应

[0079][0080][0081]

因此,t1=q

×2n

te,上述二个实施例皆可得到相同的时间t1。

[0082]

接着,依据ieee1588协定,主要装置300将接收由从属装置400传送的延迟请求封包,并依据该封包的接收时间,将该接收时间透过延迟回应封包传送给从属装置400。请参照图4,其绘示本实施例的主要装置300产生及发送延迟回应封包的流程。以下说明请一并参照图2及图4。

[0083]

于步骤s405,通讯晶片330透过端口335接收从属装置400的延迟请求封包,并记录一延迟请求封包输入时间ti

req

。于本步骤中,端口335接收延迟请求封包时,通讯晶片330将会读取时间戳电路331的计数值,以取得延迟请求封包输入时间ti

req

。

[0084]

于步骤s410,处理器320依据计数电路310的计数值取得商数及余数,以计算延迟请求封包的接收时间t4。

[0085]

于本步骤中,对应端口335收到延迟请求封包,处理器320读取计数电路310的计数值以取得延迟请求封包接收日历时间tod

req

,并将该延迟请求封包接收日历时间tod

req

除以时间戳电路331的位元数n以得到商数q

req

及余数r

req

。接着,处理器320以商数值q

req

及位元数n相乘后的乘积值以及延迟请求封包输入时间ti

req

二者的加总值取得接收时间t4,为利了解,接收时间t4的计算可以如下公式(3)表示:

[0086]

t4=q

req

×2n

ti

req

……

公式(3)

[0087]

处理器320依公式(3)计算出接收时间t4。

[0088]

于其他实施例中,步骤s410还进一步判断是否对商数值q

req

加1。具体来说,处理器320会比对延迟请求封包输入时间ti

req

和余数r

req

。若处理器320判断延迟请求封包输入时间ti

req

等于或小于余数r

req

,代表通讯晶片330收到延迟请求封包的时间点到处理器320取得日历时间tod

req

的过程中,计数电路310的计数器313没有发生溢位;反之,代表于该过程中,计数电路310的计数器313已发生过一次溢位,在这样的情况下,处理器320必需先将商数q

req

加1,因此,接收时间t4可以如下公式(4)表示。

[0089]

t4=(q

req

1)

×2n

ti

req

……

公式(4)

[0090]

于步骤s415,处理器320产生一延迟回应封包。于一些实施例中,延迟回应封包的时间信息包括时间戳记ts以及校正栏位cf。

[0091]

于步骤s420,处理器320根据接收时间t4来修改延迟回应封包的时间戳记栏位ts。

[0092]

于一些实施例中,处理器320是依公式(3)计算的时间t4写入回应封包的时间戳记ts。

[0093]

于步骤s425,通讯晶片330透过端口335传送延迟回应封包至从属装置400。

[0094]

于上述步骤之后,从属装置400可于收到延迟回应封包后,经过解析延迟回应封包的时间戳记栏位以得到接收时间t4。

[0095]

上述步骤是说明本发明实施例的主要装置如何产生及传送同步封包及延迟回应封包。

[0096]

接着,请参照图5,其绘示根据本发明第二实施例的主要装置产生及发送同步封包的流程图。以下说明请一并参照图2及图5以说明本案第二实施例中主要装置300产生及发送同步封包的流程。

[0097]

于本实施例中,端口335和端口337都被设为透通模式。另补充说明的是,以下实施例所使用的参数或名词,是透过冠以第一、第二来代表在不同的同步封包产生周期中所产生或取得,例如第一日历时间tod1与第二日历时间tod2是代表在不同的同步封包产生周期中所取得的日历时间;第一余数r1与第二余数r2是为在不同的同步封包产生周期所取得的余数,并且,第一日历时间tod1与第一余数r1是指在相同的封包产生周期所取得的数值。

[0098]

于步骤s505,处理器320将第一日历时间tod1与时间戳电路331的位元数n进行运算以取得第一余数r1。本步骤与前一实施例的步骤s310~s315相同,于此不再赘述。

[0099]

于步骤s510,处理器320取得一第一晶片接收时间ti1。于本步骤中,对应端口337是透通模式,于本实施例中,端口337收到来自处理器320的第一同步封包时,通讯晶片330会读取时间戳电路331中的计数值,以取得该第一晶片接收时间ti1。于另一实施例中,处理器320于送出第一同步封包时,透过计数电路310的计数值来获得该第一晶片接收时间ti1。

[0100]

于步骤s515,当欲产生第二同步封包时,处理器320读取计数电路310中的第二日历时间tod2。本步骤与步骤s310相同,于此不再赘述。

[0101]

于步骤s520,处理器320将第二日历时间tod2与时间戳电路331的位元数n进行运算以取得第二余数r2。本步骤与步骤s315相同,于此不再赘述。

[0102]

于步骤s525,处理器320根据第一余数r1、第一晶片接收时间ti1及第二余数r2产生第二同步封包。于本步骤中,处理器320产生具有时间戳记栏位及校正栏位的第二同步封包。接着,处理器320将第一晶片接收时间ti1与第一余数r1相减的差值与第二余数r2进行加总后,再与第二日历时间tod2进行加总计算,亦即满足如下公式(5):

[0103]

tod2=q2

×2n

r2 r2 (ti1-r1)

……

公式(5)

[0104]

将满足公式(5)的数值填入时间戳记栏位ts。而校正栏位cf则填入第二余数r2的补数,即-r2,完成后各栏位值可参考表3所示。

[0105]

表3:封包中的栏位对应

[0106]

时间戳记ts校正栏位cfq2

×2n

r2 r2 (ti1-r1)-r2

[0107]

因此,于本步骤中,时间戳记ts的值是将第二日历时间tod2加上r2 (ti1-r1)的数值。

[0108]

于另一实施例中,处理器320将第一晶片接收时间ti1与第一余数r1相减的差值与与第二日历时间tod2进行加总计算,亦即满足如下公式(5-1):

[0109]

tod2=q2

×2n

r2 (ti1-r1)

……

公式(5-1)

[0110]

将满足公式(5-1)的数值填入时间戳记栏位ts,而校正栏位cf则填入0或空值,完成后封包各栏位值可参考表3-1所示。

[0111]

表3-1:封包中的栏位对应

[0112]

时间戳记ts校正栏位cf

q2

×2n

r2 (ti1-r1)0

[0113]

于步骤s530,通讯晶片330于接收第二同步封包时,根据第二晶片接收时间ti2修改第二同步封包的校正栏位cf,并于之后传送第二同步封包时,依据第二晶片传送时间te2修改第二同步封包的校正栏位cf后,将第二同步封包传送出去。于本步骤中,通讯晶片330透过端口337接收由处理器320传来的第二同步封包,且对应端口337被设为透通模式,通讯晶片330会于接收第二同步封包时读取时间戳电路331的计数值而获得第二晶片接收时间ti2,并且将校正栏位cf的值减去该第二晶片接收时间ti2。此时,第二同步封包的相关栏位对应的值将如表4所示。

[0114]

表4:封包中的栏位对应

[0115]

时间戳记ts校正栏位cfq2

×2n

r2 r2 (ti1-r1)-r2-ti2

[0116]

于另一实施例中,第二同步封包的相关栏位对应的值将如表4-1所示。

[0117]

表4-1:封包中的栏位对应

[0118]

时间戳记ts校正栏位cfq2

×2n

r2 (ti1-r1)0-ti2

[0119]

接着,当通讯晶片330欲透过端口335传送第二同步封包时,对应端口335被设定为透通模式,通讯晶片330会读取时间戳电路331而获得第二晶片传送时间te2,并且将校正栏位的值加上该第二晶片传送时间te2,因此校正栏位cf的值可如表5所示。最后第二同步封包各栏位值将如表5所示,并依此传送同步封包。

[0120]

表5:封包中的栏位对应

[0121]

时间戳记ts校正栏位cfq2

×2n

r2 r2 (ti1-r1)-r2-ti2 te2

[0122]

于另一实施例中,第二同步封包的相关栏位对应的值将如表5-1所示。

[0123]

表5-1:封包中的栏位对应

[0124]

时间戳记ts校正栏位cfq2

×2n

r2 (ti1-r1)0-ti2 te2

[0125]

需特别说明,因时间戳电路331与计数电路310的计数频率同步,所以在秒的计数值是相同的,而数值(ti1-r1)可视为处理器320取得日历时间到通讯晶片330收到同步封包的经过时间,通常来说,每个产生同步封包的周期中,取得日历时间至通讯晶片330收到同步封包的经过时间是相同的,并如前所述,余数可以等同处理器320取得日历时间tod当下,时间戳电路331当时的计数值,因此,第二余数值r2加上经过时间(ti1-r1)即会等于通讯晶片330收到第二同步封包的晶片接收时间ti2,即ti2=r2 ti1-r1。因此,表5中的各栏位对应的值也可被表示为如表6所示。

[0126]

表6:封包中的栏位对应

[0127]

时间戳记ts校正栏位cfq2

×2n

r2 r2 (ti1-r1)-r2-(r2 ti1-r1) te2

[0128]

经由上述步骤传送的同步封包,当从属装置400接收该第二同步封包后,可由时间戳记ts加上校正栏位cf的加总结果取得第二同步封包的发送时间t1,意即

[0129]

t1=q2

×2n

r2 r2 (ti1-r1) (-r2-(r2 ti1-r1) te2),经化简后可如公式(6)所示。

[0130]

t1=q2

×2n

te2

……

公式(6)

[0131]

于另一实施例中,表5-1中的各栏位对应的值也可被表示为如表6-1所示

[0132]

时间戳记ts校正栏位cfq2

×2n

r2 (ti1-r1)0-(r2 ti1-r1) te2

[0133]

t1=q2

×2n

r2 ti1-r1 0-r2-ti1 r1 te2,经化简后可如公式(6-1)所示

[0134]

t1=q2

×2n

te2

……

公式(6-1)

[0135]

因此,由公式(6)或公式(6-1)可知,不论是由第二实施例所产生的同步封包,或是由第一实施例所产生的同步封包,二者在从属装置400所计算得到的时间t1将会是相同的。

[0136]

需特别说明的是,在端口337被设定为透通模式时,若未经过上述步骤s525所进行步骤,也就是对时间戳记加上时间补偿以及在校正栏位填入对应的数值,则依通讯晶片330在收到及传送第二同步封包时对校正栏位cf修改后的第二同步封包,从属装置所计算的t1时间,例如会是t1=q2

×2n

r2-ti2 te2,而使得第二同步封包无法提供正确的时间信息。

[0137]

综上所述,即使网络装置的硬件位元数有限,例如网络装置没有搭载足够位元数的晶片,本案仍可计算出完整的日历时间,大幅降低通讯晶片的制造成本。此外,本案可使用一般通讯晶片搭载的透通模式功能,让网络装置能以一步骤同步模式发出同步封包,而不受限于通讯晶片的硬件规格。

[0138]

上述内容概述若干实施例的特征,使得熟悉此项技术者可更好地理解本案的态样。熟悉此项技术者应了解,在不脱离本案的精神和范围的情况下,可轻易使用上述内容作为设计或修改为其他变化的基础,以便实施本文所介绍的实施例的相同目的及/或实现相同优势。上述内容应当被理解为本案的举例,其保护范围应以权利要求书所界定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。