1.本发明涉及通信技术领域,特别是涉及一种数据映射和解映射方法、系统、介质及装置。

背景技术:

2.在物联网相关iot(internet of things)感知项目中,需要处理数以万计节点的传感器数据,节点和传感器数据之间数值匹配是一种常见的编程场景,假设有两个相关的整数集合{a}和{b},并且{a}和{b}之间有1对1或者1对多的关系,这会定义出一个数据匹配表,如下表所示:

3.{a}{b}10001388731000212546100033775310003345341000443256

…………

4.一个常见的编程场景,根据{a}中的一个值a,在{b}查找a对就的1个或者多个值b,如下表所示:

5.a对应的b10001388731000337753,34534

6.这个操作就是数据映射。

7.业内对这个操作的主流解决方案是利用multimap数据结构在内存中构建数值匹配表,假设有如下的数据结构m:

8.m:multimap《key,value》

9.上述结构中key为{a}中的值,value为{b}中的值。然后将数值匹配表中条条目添加进使用的编程语言的相应数据结构中,比如c 语言中的std::multimap。

10.数据匹配表全部添加进内存multimap数据结构后,可执行相应的匹配操作。

11.业内还有利用磁盘的解决方案,即将数值对照表存入磁盘文件,或者存入基于磁盘文件的数据库系统中,例如mysql数据库系统。

12.在multimap方案中,当数值匹配表有大量条目时,以c 为例,依照本文假设场景,应选用std::multimap《uint64_t,uint16_t》数据结构,以100,000,000个条目规模的数据匹配表为例,在内存中把数值匹配表构建完成后内存占用为6714mb。可见内存占用较大,对于内存不富裕的计算机工作站来说并不友好。

13.在使用磁盘的解决方案中,由于计算机磁盘系统本身的特性使然,磁盘系统和基于磁盘的数据库系统的匹配效率与计算机内存相比存在数个数量级的差距,并不适合频繁

匹配的场景。本文后续不再关注此类方案。本文后续全部基于内存中的方案。

14.因此,希望能够解决如何减少数据映射所占用的内存的问题。

技术实现要素:

15.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种数据映射和解映射方法、系统、介质及装置,用于解决现有技术中如何减少数据映射所占用的内存的问题。

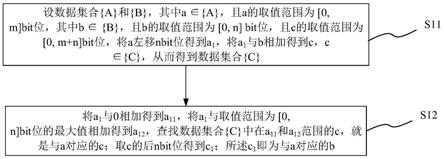

16.为实现上述目的及其他相关目的,本发明提供一种数据映射和解映射方法,包括以下步骤:设数据集合{a}和{b},其中a∈{a},且a的取值范围为[0,m]bit位,其中b∈{b},且b的取值范围为[0,n]bit位,且c的取值范围为[0,m n]bit位,将a左移nbit位得到a1,将a1与b相加得到c,c∈{c},从而得到数据集合{c};将a1与0相加得到a

11

,将a1与取值范围为[0,n]bit位的最大值相加得到a

12

,查找数据集合{c}中在a

11

和a

12

范围的c,就是与a对应的c;取c的后nbit位得到c1;所述c1即为与a对应的b。

[0017]

于本发明的一实施例中,还包括预先将a、b、c转为二进制数。

[0018]

于本发明的一实施例中,所述m为48,n为16。

[0019]

于本发明的一实施例中,所述a为传感器编号,b为传感器数据。

[0020]

为实现上述目的,本发明还提供一种数据映射和解映射系统,包括:映射模块和解映射模块;所述映射模块用于设数据集合{a}和{b},其中a∈{a},且a的取值范围为[0,m]bit位,其中b∈{b},且b的取值范围为[0,n]bit位,且c的取值范围为[0,m n]bit位,将a左移nbit位得到a1,将a1与b相加得到c,c∈{c},从而得到数据集合{c};所述解映射模块用于将a1与0相加得到a

11

,将a1与取值范围为[0,n]bit位的最大值相加得到a

12

,查找数据集合{c}中在a

11

和a

12

范围的c,就是与a对应的c;取c的后nbit位得到c1;所述c1即为与a对应的b。

[0021]

于本发明的一实施例中,还包括预先将a、b、c转为二进制数。

[0022]

于本发明的一实施例中,所述m为48,n为16。

[0023]

于本发明的一实施例中,所述a为传感器编号,b为传感器数据。

[0024]

为实现上述目的,本发明还提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现任一上述数据映射和解映射方法。

[0025]

为实现上述目的,本发明还提供一种数据映射和解映射装置,包括:处理器和存储器;所述存储器用于存储计算机程序;所述处理器与所述存储器相连,用于执行所述存储器存储的计算机程序,以使所述数据映射和解映射装置执行任一上述的数据映射和解映射方法。

[0026]

如上所述,本发明的一种数据映射和解映射方法、系统、介质及装置,具有以下有益效果:用于减少数据映射所占用的内存。

附图说明

[0027]

图1显示为本发明的数据映射和解映射方法于一实施例中的流程图;

[0028]

图2显示为本发明的数据映射和解映射系统于一实施例中的结构示意图;

[0029]

图3显示为本发明的数据映射和解映射装置于一实施例中的结构示意图。

[0030]

元件标号说明

[0031]

21

ꢀꢀꢀꢀ

映射模块

[0032]

22

ꢀꢀꢀꢀ

解映射模块

[0033]

31

ꢀꢀꢀꢀ

处理器

[0034]

32

ꢀꢀꢀꢀ

存储器

具体实施方式

[0035]

以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

[0036]

需要说明的是,以下实施例中所提供的图示仅以示意方式说明本发明的基本构想,故图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

[0037]

本发明的数据映射和解映射方法、系统、介质及装置,用于减少数据映射所占用的内存。

[0038]

如图1所示,于一实施例中,本发明的数据映射和解映射方法,包括以下步骤:

[0039]

步骤s11、设数据集合{a}和{b},其中a∈{a},且a的取值范围为[0,m]bit位,其中b∈{b},且b的取值范围为[0,n]bit位,且c的取值范围为[0,m n]bit位,将a左移nbit位得到a1,将a1与b相加得到c,c∈{c},从而得到数据集合{c}。

[0040]

具体地,还包括预先将a、b、c转为二进制数。

[0041]

具体地,所述m为48,n为16。设数据集合{a}和{b},其中a∈{a},且a的取值范围为[0,48]bit位,其中b∈{b},且b的取值范围为[0,16]bit位,且c的取值范围为[0,64]bit位,将a左移16bit位得到a1,将a1与b相加得到c,c∈{c},从而得到数据集合{c}。具体地,a的取值范围为[0,48]bit位是指在a为二进制数时,a的取值范围为0bit到48bit,即a的取值范围为二进制数0到二进制数111111111111111111111111111111111111111111111111之间。b的取值范围为[0,16]bit位是指b为二进制数时,b的取值范围为0bit到16bit,即a的取值范围为二进制数0到二进制数1111111111111111之间。c的取值范围为[0,64]bit位,是指c为二进制数时,c的取值范围为0bit到64bit,即c的取值范围为二进制数0到二进制数1111111111111111111111111111111111111111111111111111111111111111之间。所述将a左移16bit位得到a1是指,例如a为101,那么将101左移16bit位得到a1为1010000000000000000。将a1与b相加得到c是指,例如b为10001,那么将a1与b相加得到c为1010000000000010001。

[0042]

具体地,对数据集{a}和{b}中的数据基于数据集{a}和{b}原先的映射关系,进行计算得到数据集合{c}。例如,所述a为传感器编号,b为传感器数据。那么,数据集{a}和{b}原先的映射关系为数据集{a}中数据a代表的传感器编号与所述传感器编号对应的传感器产生的传感器数据对应关系,即为数据集{a}和{b}原先的映射关系。

[0043]

具体地,例如数值a为314159265359,数值b为8848。对数据集{a}中的每条目中的a在二进制的表现形式中左移16位,然后把b的2进制数据复制到a左移16位后空出的16位低位上。这样就得到了编码后的数据c。

[0044][0045][0046]

步骤s12、将a1与0相加得到a

11

,将a1与取值范围为[0,m n]bit位的最大值相加得到a

12

,查找数据集合{c}中在a

11

和a

12

范围的c,就是与a对应的c;取c的后nbit位得到c1;所述c1即为与a对应的b。

[0047]

具体地,所述将a1与0相加得到a

11

,将a1与取值范围为[0,16]bit位的最大值相加得到a

12

,查找数据集合{c}中在a

11

和a

12

范围的c,就是与a对应的c;取c的后16bit位得到c1;所述c1即为与a对应的b。具体地,所述例如a的十进制数为314159265359,则将a转换为二进制数为100100100100101010110011111011001001111,则a1为将a左移16bit位得到a1,a1为1001001001001010101100111110110010011110000000000000000,所述将a1与0相加得到a

11

,则a

11

为1001001001001010101100111110110010011110000000000000000。取值范围为[0,16]bit位的最大值为1111111111111111。将a1与取值范围为[0,16]bit位的最大值相加得到a

12

为1001001001001010101100111110110010011111111111111111111,则查找数据集合{c}中在1001001001001010101100111110110010011110000000000000000和1001001001001010101100111110110010011111111111111111111范围的c。通常排序数据结构会提供根

据从一个数值范围内查询元素的方法,以c 的std::set为例,就提供了lower_bound和upper_bound两个函数,可以从c可能的最大值和最小值,获取在这个数值范围内的所有的c。如果只查找到1个c,则表示数值匹配表中a只对应了一个b。如果有查找到多个c,则表示数值匹配表中a对应了多个b。

[0048]

具体地,取c的后16bit位得到c1;所述c1即为与a对应的b。例如,c的十进制为20588741614576270,那么转换为二进制为1001001001001010101100111110110010011110010001010010000。那么取c的后16bit位得到c1为0010001010010000,即0010001010010000为与a对应的b。将b转换为十进制为8848。本文以节省内存占用为目的,以提供数据密度为手段,让内存受限的计算机工作站可以处理更大规模的数值匹配场景.

[0049]

至此,本发明适用的数值匹配场景,从数据集合{a}和{b}的映射,内存数据结构,数值a匹配的查询方式,以及最后c解码得到b都作了说明。

[0050]

在上述说明过程中,以100,000,000个条目规模的数据匹配表为例,在内存中把数值匹配表构建完成,在应用本方法前内存占用为6714mb,应用本方法后内存占用为4578mb,内存占用仅为之前的68%:4578/6714=68.19%。可充分体现本方法减少内存占用的有效性。

[0051]

如图2所示,于一实施例中,本发明的数据映射和解映射系统,包括:映射模块21和解映射模块22;所述映射模块21用于设数据集合{a}和{b},其中a∈{a},且a的取值范围为[0,m]bit位,其中b∈{b},且b的取值范围为[0,n]bit位,且c的取值范围为[0,m n]bit位,将a左移nbit位得到a1,将a1与b相加得到c,c∈{c},从而得到数据集合{c};所述解映射模块22用于将a1与0相加得到a

11

,将a1与取值范围为[0,n]bit位的最大值相加得到a

12

,查找数据集合{c}中在a

11

和a

12

范围的c,就是与a对应的c;取c的后nbit位得到c1;所述c1即为与a对应的b。

[0052]

于本发明的一实施例中,还包括预先将a、b、c转为二进制数。

[0053]

于本发明的一实施例中,所述m为48,n为16。

[0054]

于本发明的一实施例中,所述a为传感器编号,b为传感器数据。

[0055]

需要说明的是,映射模块21和解映射模块22的结构和原理与上述数据映射和解映射方法中的步骤一一对应,故在此不再赘述。

[0056]

需要说明的是,应理解以上系统的各个模块的划分仅仅是一种逻辑功能的划分,实际实现时可以全部或部分集成到一个物理实体上,也可以物理上分开。且这些模块可以全部以软件通过处理元件调用的形式实现;也可以全部以硬件的形式实现;还可以部分模块通过处理元件调用软件的形式实现,部分模块通过硬件的形式实现。例如,x模块可以为单独设立的处理元件,也可以集成在上述装置的某一个芯片中实现,此外,也可以以程序代码的形式存储于上述装置的存储器中,由上述装置的某一个处理元件调用并执行以上x模块的功能。其它模块的实现与之类似。此外这些模块全部或部分可以集成在一起,也可以独立实现。这里所述的处理元件可以是一种集成电路,具有信号的处理能力。在实现过程中,上述方法的各步骤或以上各个模块可以通过处理器元件中的硬件的集成逻辑电路或者软件形式的指令完成。

[0057]

例如,以上这些模块可以是被配置成实施以上方法的一个或多个集成电路,例如:一个或多个特定集成电路(application specific integrated circuit,简称asic),或,

一个或多个微处理器(micro processor uint,简称mpu),或,一个或者多个现场可编程门阵列(field programmable gate array,简称fpga)等。再如,当以上某个模块通过处理元件调度程序代码的形式实现时,该处理元件可以是通用处理器,例如中央处理器(central processing unit,简称cpu)或其它可以调用程序代码的处理器。再如,这些模块可以集成在一起,以片上系统(system-on-a-chip,简称soc)的形式实现。

[0058]

于本发明一实施例中,本发明还包括一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现上述任一所述数据映射和解映射方法。

[0059]

本领域普通技术人员可以理解:实现上述各方法实施例的全部或部分步骤可以通过计算机程序相关的硬件来完成。前述的计算机程序可以存储于一计算机可读存储介质中。该程序在执行时,执行包括上述各方法实施例的步骤;而前述的存储介质包括:rom、ram、磁碟或者光盘等各种可以存储程序代码的介质。

[0060]

如图3所示,于一实施例中,本发明的数据映射和解映射装置包括:处理器31和存储器32;所述存储器32用于存储计算机程序;所述处理器31与所述存储器32相连,用于执行所述存储器32存储的计算机程序,以使所述数据映射和解映射装置执行任一所述的数据映射和解映射方法。

[0061]

具体地,所述存储器32包括:rom、ram、磁碟、u盘、存储卡或者光盘等各种可以存储程序代码的介质。

[0062]

优选地,所述处理器31可以是通用处理器,包括中央处理器(central processing unit,简称cpu)、网络处理器(network processor,简称np)等;还可以是数字信号处理器(digital signal processor,简称dsp)、专用集成电路(application specific integrated circuit,简称asic)、现场可编程门阵列(field programmable gate array,简称fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件。

[0063]

综上所述,本发明数据映射和解映射方法、系统、介质及装置,用于减少数据映射所占用的内存。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

[0064]

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。