用于可调谐光子延迟的装置和方法

1.相关申请案交叉引用

2.本技术要求于2019年7月11日提交的发明名称为“用于可调谐光子延迟的装置和方法(apparatus and method for tunable photonic delay)”、序列号为16/508,652的美国专利申请优先权的权益,该在先申请的内容通过引用并入本文中。

技术领域

3.本发明属于光通信系统领域,具体涉及用于配置光通信系统的系统和方法。

背景技术:

4.对于基于光子和光技术的下一代分组交换机的发展,光缓存仍然是实现全光分组交换的一个主要挑战。

5.由于光不能停止或直接存储在任何介质中,一种方法是光缓存器可以暂时存储光信号。光缓存器在光子交换和信号处理中有多种应用。在过去30年里,许多研究人员提出在交换时使用光缓存器来存储数据。光缓存的能力相当有限,因为与电子随机存取存储器等效的光随机存取存储器仍不存在。当前的光缓存器是用光延迟线构建的,这些光延迟线可以使数据包延迟,而不是存储数据包。再循环回路通常用于构建光缓存器。

6.慢光技术在光信号处理方面表现出一定前景,但它是否可以用于构建大型光缓存器尚未可知。如今,没有光缓存器可以容纳不同长度的数据包。光移动很快,因此缓存器中的光路长度是一个关键参数。虽然有解决系统级问题或模拟非常短期缓存器的变通办法,但在实际中尚未实现长期光缓存器。

7.如今,没有大型光缓存器可以容纳不同长度的数据包,也没有一个方案为缓存和安全应用提供有意义的可编程光延迟。现有技术的方案提供了最大1.2纳秒的可编程延迟,而许多实际应用需要数十纳秒的延迟,例如0-30纳秒。本发明提供了一种实现数十纳秒光延迟的光缓存器的系统和方法。

8.提供该背景信息是为了揭示申请人认为可能与本发明相关的信息。没有必要承认也不应解释任何前述信息构成与本发明相对的现有技术。

技术实现要素:

9.本发明的实施例的目标为提供克服现有技术的至少一些上述限制的技术。

10.因此,本发明的一个方面提供了一种可调谐光延迟线。所述可调谐光延迟线包括:提供粗略延迟量的粗略延迟部分,所述粗略延迟部分包括相结合的粗略延迟选择元件与粗略延迟元件,所述粗略延迟选择元件片上合入到光子集成电路(integrated circuit,ic)组件中,所述粗略延迟元件设置在所述光子ic组件片外并与所述粗略延迟选择元件互连;提供精细延迟量的精细延迟元件,所述精细延迟元件与所述粗略延迟选择元件串联互连;所述光延迟线可通过聚集所述粗略延迟量和所述精细延迟量调谐到目标延迟量。

11.在一个方面中,所述粗略延迟元件包括一组1

×

n和n

×

1光交换元件,所述1

×

n和n

×

1光交换元件可供选择以提供所述粗略延迟量。

12.在另一方面,所述粗略延迟元件包括一组小型化光纤线轴组件。

13.在一个实施例中,所述一组1

×

n光交换元件的n个输出和所述一组n

×

1光交换元件的n个输入通过所述一组小型化光纤线轴组件互连。

14.在可调谐光延迟的另一个实施例中,所述一组1

×

n光交换元件的所述n个输出和所述一组n

×

1光交换元件的所述n个输入可以基于提供2n 2个元件的总输入/输出配置的以下中的至少一个:马赫-曾德尔、微环和分光器/耦合器装置。

15.在一个变型方式中,所述粗略延迟量的范围在1纳秒至100纳秒之间。

16.在另一个变型方式中,所述精细延迟量小于1纳秒。

17.在可调谐光延迟线的另一个实施例中,所述精细延迟元件包括合入到所述光子ic组件中的基于波导的精细延迟元件。

18.在另一个实施例中,所述粗略延迟元件和所述精细延迟元件可在临时控制时间内调谐,以实现所述目标延迟量,所述临时控制时间与分组交换、安全混淆和应用中的至少一个相关。

19.在另一个广泛的方面中,提供了一种将光延迟线调谐到目标延迟量的方法。所述方法包括:选择粗略延迟量,所述粗略延迟量是使用片上合入到光子集成电路(integrated circuit,ic)组件中的粗略延迟选择元件与粗略延迟元件结合提供的,所述粗略延迟元件设置在所述光子ic组件片外并与所述粗略延迟选择元件互连;使用与所述粗略延迟元件串联互连的精细延迟元件选择精细延迟量;聚集所述粗略延迟量和所述精细延迟量以将所述光延迟线调谐到所述目标延迟量。

20.在另一个广泛的方面中,还提供了一种光网络控制器。所述控制器包括:处理器;非瞬时存储器,存储指令,所述指令可在所述处理器中执行以:选择粗略延迟量,所述粗略延迟量是使用粗略延迟选择元件与粗略延迟元件结合提供的,所述粗略延迟选择元件片上合入到光子集成电路(integrated circuit,ic)组件中,所述粗略延迟元件设置在所述光子ic组件片外并与所述粗略延迟选择元件互连;使用与所述粗略延迟元件串联互连的精细延迟元件选择精细延迟量;通过聚集所述粗略延迟量和所述精细延迟量将所述光延迟线调谐到目标延迟量。

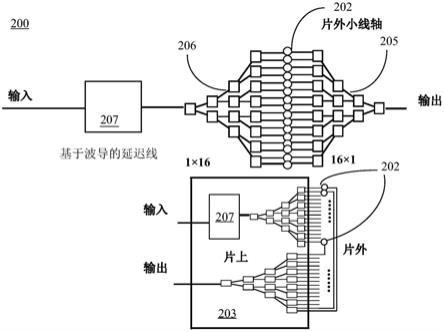

附图说明

21.进一步地,通过阅读以下结合附图所作的详细描述将容易了解本发明的特征和优势,其中:

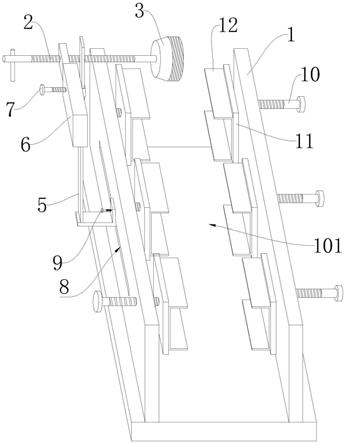

22.图1a示出了在一个示例性实施例中光延迟线的设计;

23.图1b示出了光延迟线的另一个示例性实施例;

24.图2示出了在一个示例性实施例中使用硅光交换机实现光延迟线;

25.图3示出了光延迟线在偏振复用信号的光信号混淆中的示例性实施例应用;

26.图4示出了光延迟线在光分组缓存中的示例性实施例应用;

27.图5示出了在一个示例性实施例中配置光延迟线的方法;

28.图6示出了在一个示例性实施例中包括配置光延迟线的控制器的架构。

29.需要说明的是,在所有附图中,相同的特征由相同的附图标记标识。

具体实施方式

30.除了其它优点和益处中,与现有方法相比,本发明还有以下优点和益处:

31.延迟更高,可编程性从0纳秒到数十纳秒。

32.与易受可变损耗影响的现有方法相比,通过使用片外粗略延迟元件与片上粗略延迟选择元件,在可选择的整个延迟范围内,损耗均匀。在一个实施例中,片上粗略延迟选择元件由1

×

n和n

×

1光子交换元件(或n

×

1耦合器代替n

×

1交换机)提供,而片外粗略延迟元件可以是多个小型化光纤线轴,连接到使1

×

n和n

×

1交换元件互连的芯片的外围区域。1

×

n的输出i连接到第i个光纤线轴的一端,第i个光纤线轴的另一端连接到n

×

1的输入i。1

×

n和n

×

1都是单芯片,光纤线轴位于片外。

33.下文论述的可调谐延迟实施例应用,这些应用需要高达30纳秒的延迟,具有1至数十纳秒的粗粒度以及可选的亚纳秒的更细粒度。

34.可选的基于波导的精细延迟,可以串联添加,以便进一步调谐光延迟线。精细延迟可以是基于波导的延迟,该延迟与1

×

n和n

×

1粗略延迟选择元件一起片上合入到光子集成电路(integrated circuit,ic)组件中。

35.图1a示出了在一个示例性实施例100中光延迟线的设计。为了增加光学光的延迟,并能够应用于应用案例,提出了一种具有两个串联配置的延迟元件的片上和片外混合系统。图1a示出了一个延迟元件101,该延迟元件101提供了小于1纳秒的相对较小的延迟,在此称为精细延迟。图1a还示出了另一个延迟元件102,该延迟元件102提供更大的延迟,在此称为粗略延迟,延迟分辨率为1纳秒到数十纳秒。精细延迟元件101在延迟调整中可以具有皮秒分辨率,而粗略延迟元件102用于例如以纳秒为单位的大延迟。

36.图1a示出了控制器103,该控制器103设置小(精细)延迟和大(粗略)延迟以实现目标延迟t。对于光缓存应用案例,交换是预先(例如,在传输的数据包之间的间隔或在控制时间期间)执行的,因此交换时间(通常是几纳秒)不是延迟的一部分。在一个实施例中,本发明使用片上1

×

n和n

×

1光交换元件,其中,精细延迟元件101和粗略延迟元件102使用片外小光纤线轴连接。

37.在一个示例性实施例中,控制器可以通过将使用精细延迟元件101实现的350皮秒与使用粗略元件102实现的5纳秒组合来配置5.35纳秒(nanosecond,nsec)的目标延迟。包括精细延迟元件的小型化光纤线轴基本上是封装光子集成电路(integrated circuit,ic)芯片的光纤长度。当n=8且延迟为0至7纳秒时,在图1a的使用1

×

n交换机和n

×

1耦合器的设计实施例中,相应选择的光纤线轴的长度为0cm、20cm、40cm、60cm、80cm、100cm、120cm、140cm。

38.图1b示出了光延迟线的另一个示例性实施例150。具体地,图1b示出了具有1

×

n和n

×

1交换元件的替代设计,该替代设计具有紧凑设计的小光纤线轴151,串联地间插在输入交换元件152与输出交换元件153之间。

39.如图1a和图1b的实施例所示,粗略延迟元件包括1

×

n/n

×

1交换元件以及一组使1

×

n和n

×

1交换元件互连的n个小型化光纤线轴。例如,每个线轴可以表示2纳秒延迟量,当n=16时,粗略延迟设置为0纳秒(对于n=1)到30纳秒(对于n=16),单位为2纳秒。精细延迟元件与1

×

n或n

×

1串联互连,可以设置为覆盖0至2纳秒的范围。

40.图2示出了在一个示例性实施例200中使用硅光交换机实现光延迟线。具体地,图2

示出了使用硅光交换机实现图1b。形成光子片上ic组件202的粗略延迟部分102的1

×

n和n

×

1交换机的1

×

2和2

×

1交换的交换构建块可以是在硅光子中使用载流子注入设计的快速马赫-曾德尔(mach-zender,mzi)交换机。小型化光纤线轴组件202设置在光子片上ic组件202片外,并与粗略延迟部分102的1

×

n交换机的n个输出和n

×

1交换机的n个输入串联连接,n个输出和n个输入分别在图2的项目206、205中示出。可选的基于波导的精细延迟元件207可以与粗略延迟元件102串联连接,提供额外的调谐能力。在一个实施例中,可选的基于波导的精细延迟元件207可以合入到包括粗略延迟元件102的光子ic组件202中。

41.在可调谐光延迟的另一个实施例中,所述一组1

×

n光交换元件的n个输出和所述一组n

×

1光交换元件的n个输入可以基于提供2n 2个元件的总输入/输出配置的以下中的任何一个:马赫-曾德尔、微环和分光器/耦合器装置。

42.图3示出了光延迟线在偏振复用信号的光信号混淆中的示例性实施例应用300。具体地,图3所示的应用案例需要1到30纳秒的延迟,粗粒度为1纳秒,可选地为亚纳秒粒度。图3中描述的特定应用实施例示出了本发明应用于延迟设置,该延迟设置用于混淆光信道301中偏振复用信号的光信号,所述光信道301包括光发送器302和光接收器303。所描述的实施例可以在光发送器301处在一个偏振上安全混淆光信号时实现时间可变延迟304,并通过在光接收器303处使该时间可变延迟304延迟而在相反的偏振上进行补偿,因此两个偏振具有相同的延迟。显然,窃听信号的入侵者不知道延迟的存在、选择延迟的过程,也不知道恢复被混淆的伴随光信号所需的延迟量。

43.所选择的目标延迟量t应远远大于数字信号处理器(digital signal processor,dsp)的校正能力,该校正能力迄今通常在100皮秒左右实现。延迟应在随机时间段内随机设置为1纳秒到数十纳秒之间的值,并更改为另一个值。变化的时间可以是随机但同步的,变化的值也可以是随机的。

44.图4示出了光延迟线在光分组缓存中的示例性实施例应用400。具体地,图4所示的应用案例需要1到30纳秒的延迟,粗粒度为1纳秒,可选地为亚纳秒粒度。图4中描述的应用示出了本发明可应用于光分组缓存中。当输入源402尝试将数据包发送到输出端时,它可能因为输出端可能正在从另一个输入端接收数据包而无法发送。由于这种争用,输入端可能会延迟传输。由于数据包大小从64字节到1518字节不等,延迟t 403的量取决于线速。在数据包大小在64b与1500b之间的实施例中,延迟量t 403可以在1.2纳秒至30纳秒的范围内,使用1纳秒和n=32的粗略调谐。在本示例中,细粒度是可选的,因为粗略延迟可能足以用于类似的实际应用。延迟量403可以设置在交换结构401的输入端。

45.图5示出了在一个示例性实施例中配置光延迟线的方法500。

46.在步骤510中,选择粗略延迟量,所述粗略延迟量是使用粗略延迟选择元件与粗略延迟元件结合提供的,所述粗略延迟选择元件片上合入到光子集成电路(integrated circuit,ic)组件中,所述粗略延迟元件设置在所述光子ic组件片外并与所述粗略延迟选择元件互连。

47.在步骤520中,使用与所述粗略延迟选择元件串联互连的精细延迟元件选择精细延迟量。

48.在步骤530中,通过聚集所述粗略延迟量和所述精细延迟量将所述光延迟线调谐到目标延迟量。

49.图6示出了在一个示例性实施例中包括控制器601的架构600,所述控制器601在光信号602的传输路径中配置精细延迟元件610a和粗略延迟元件610b。控制器601可以包括处理器603和存储可在处理器603中执行的指令的非瞬时存储器604。

50.在一个实施例中,非瞬时存储器604存储指令,所述指令可在处理器603中执行以:选择粗略延迟量,所述粗略延迟量是使用片上合入到光子集成电路(integrated circuit,ic)组件中的粗略延迟元件提供的;使用独立于所述光子ic组件设置并与所述粗略延迟元件串联互连的精细延迟元件选择精细延迟量;通过聚集所述粗略延迟量和所述精细延迟量将所述光延迟线调谐到目标延迟量。

51.在一个实施例中,控制器601可以包括实现网络监控和管理软件层的软件定义网络(software defined network,sdn)控制器。控制器801的功能还可以部分或全部驻留在与光通信网络的光部分相关联的节点上。

52.尽管已经参考本发明的特定特征和实施例描述了本发明,但是明显可以在不脱离本发明的情况下制定本发明的各种修改和组合。因此,说明书和附图仅被视为所附权利要求书限定的对本发明的说明,并且预期覆盖落入本发明的范围内的任何和所有修改、变化、组合或等同物。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。