技术特征:

1.一种三维(3d)半导体存储器结构,包括:存储器芯片,其包括存储器和硅通孔(tsv);硬件加速器,其被布置在所述芯片上并且被耦接至所述芯片;以及衬底,所述衬底被布置在所述(3d)半导体存储器结构和所述硬件加速器之下并且附接到所述tsv以及所述存储器芯片和所述硬件加速器的外部输入和输出。2.根据权利要求1所述的结构,其中,所述硬件加速器面对面地耦接至所述存储器芯片。3.根据权利要求2所述的结构,其中,所述tsv被布置在所述存储器芯片的外围。4.根据权利要求2所述的结构,其中,所述存储器芯片和所述硬件加速器耦接以形成中间结构,所述衬底附接至所述中间结构。5.根据权利要求2所述的结构,其中,所述衬底是包括预焊接的层压物的封装衬底。6.根据权利要求2所述的结构,其中,所述存储器芯片包括静态随机存取存储器。7.根据权利要求2所述的结构,还包括补充高带宽存储器(hbm),所述补充高带宽存储器耦接到所述衬底并且被配置为执行存储器操作。8.根据权利要求7所述的结构,其中,所述补充的hbm使用预焊接的层压物耦接至所述衬底。9.根据权利要求8所述的结构,其中,所述存储器芯片进一步包括用于控制所述存储器操作的存储器控制器。10.根据权利要求8所述的结构,其中,所述存储器芯片进一步包括hbm phy和hbm存储器控制器,所述hbmphy和hbm存储器控制器支持所述补充的hbm并且使用线后段(beol)金属线直接电耦接至所述补充的hbm。11.根据权利要求10所述的结构,其中,所述hbm phy和所述hbm存储器控制器被设置在所述晶片的beol的层间电介质层中。12.根据权利要求2所述的结构,其中,所述tsv穿过所述存储器芯片的外围区域。13.根据权利要求1所述的结构,包括模拟芯片,所述模拟芯片布置在所述存储器芯片与所述硬件加速器之间并且面对面地耦接至所述硬件加速器,所述衬底位于所述结构、所述硬件加速器以及所述模拟芯片的下方。14.根据权利要求13所述的结构,其中,所述模拟芯片使用cu柱和焊盖耦接至所述硬件加速器。15.根据权利要求13所述的结构,其中,所述模拟芯片没有tsv。16.根据权利要求13所述的结构,其中,所述模拟芯片包括一个或多个tsv。17.根据权利要求13所述的结构,其中,所述硬件加速器通过在所述铜到铜接合中使用的铜柱耦接至所述存储器芯片。18.一种用于形成三维(3d)半导体存储器结构的方法,所述方法包括:接收包括存储器和硅通孔(tsv)的存储器芯片;将硬件加速器布置在所述存储器芯片上并且耦接至所述存储器芯片;以及将衬底布置在所述(3d)半导体存储器结构和所述硬件加速器下方并附接至所述tsv和所述存储器芯片和所述硬件加速器的外部输入和输出。19.根据权利要求18所述的方法,其中,所述硬件加速器面对面地耦接至所述存储器芯

片。20.根据权利要求19所述的方法,其中,所述tsv布置在所述存储器芯片的外围。21.根据权利要求19所述的方法,其中,所述芯片和所述硬件加速器耦接以形成所述衬底所附接的中间结构。22.根据权利要求19所述的方法,进一步包括将被配置为与所述芯片执行存储操作的补充的高带宽存储器(hbm)耦接至所述衬底。23.根据权利要求18所述的方法,所述方法包括:将模拟芯片布置在所述存储器芯片与所述硬件加速器之间并且面对面耦接至所述硬件加速器;所述衬底布置在所述结构、所述硬件加速器和所述模拟芯片的下方。24.根据权利要求23所述的方法,进一步包括在所述布置步骤之前将所述模拟芯片变薄。

技术总结

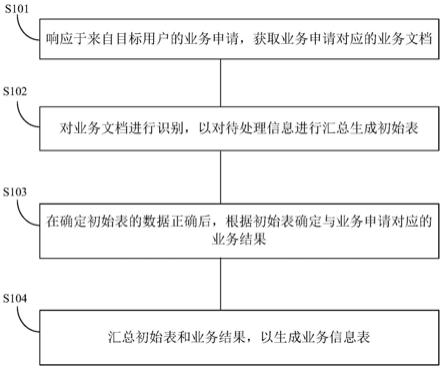

提供了三维(3D)半导体存储器结构以及形成3D半导体存储器结构的方法。3D半导体存储器结构包括芯片,该芯片包括存储器和硅通孔(TSV)。3D半导体存储器结构还包括布置在上述芯片上并面对面耦接到上述芯片的硬件加速器。该3D半导体存储器结构还包括衬底,该衬底被布置在该(3D)半导体存储器结构和该硬件加速器之下并且附接至该TSV和该存储器芯片和该硬件加速器的外部输入和输出。加速器的外部输入和输出。加速器的外部输入和输出。

技术研发人员:M.法鲁克 A.库马尔

受保护的技术使用者:国际商业机器公司

技术研发日:2020.06.16

技术公布日:2022/2/18

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。