1.本发明涉及信号采集领域,更具体涉及一种跳合闸回路采集器。

背景技术:

2.跳合闸回路信号采集是在传统断路器跳合闸回路监测方法的基础上,实时监测跳合闸线圈回路电流值的变化情况,分析断路器跳合闸回路的运行状态,消除二次设备因电缆问题存在的安全隐患,减少电网跳闸几率,提高二次设备运行管控能力,实现跳合闸回路的全工况监视和保护,能广泛服务于各类变电站高压断路器跳合闸场景需求。但是目前市场上缺乏跳合闸回路采集器,中国专利授权公告号cn201527441u,公开一种断路器控制回路跳合闸信号检测装置,涉及一种涉及电力系统中检测断路器控制回路跳合闸信号的装置,特别是断路器控制回路跳合闸信号检测装置。技术方案是:包含信号采集器(1)、霍尔运算器(2)、精密检波器(3)、单片机控制器(4)、数据存储电路(5)及数据传输电路(6),信号采集器的输出连接霍尔运算器,霍尔运算器的输出连接精密检波器,精密检波器的输出连接单片机控制器,数据存储电路及数据传输电路也分别连接单片机控制器。该实用新型的有益效果是:利用高性能微处理器,以及采用霍尔直流采集技术,可靠地记录控制回路向断路器发出的动作命令,为电力系统事故分析提供了新的判断数据;系统结构紧凑,整体性能好,可靠性高。但是该信号检测装置的结构简单,电路功能不完善,不适用于变电站二次回路中跳合闸回路信号采集。

技术实现要素:

3.本发明所要解决的技术问题在于现有技术跳合闸信号检测装置结构简单,电路功能不完善,不适用于变电站二次回路中跳合闸回路信号采集。

4.本发明通过以下技术手段实现解决上述技术问题的:一种跳合闸回路采集器,包括fpga以及分别与fpga连接的以太网电路、开关量输入电路、rs485通信电路、ad采样电路、光串口接收和发送电路及uart串口电路,还包括若干路差分放大电路、系统电源电路及设置于跳合闸回路上的若干个电流传感器,系统电源电路为采集器供电,每个电流传感器分别连接一路差分运放电路,每路差分放大电路均与ad采样电路连接。

5.本发明提供一种跳合闸回路采集器,每个电流传感器的信号通过差分放大电路放大以后经ad采样电路进行模数转换以后送入fpga,经过以太网电路、rs485通信电路、光串口接收和发送电路或者uart串口电路将信号传输出去,信号传输方式多,功能齐全,满足变电站所有场合使用,适用于变电站二次回路中跳合闸回路信号采集。

6.进一步地,所述以太网电路包括芯片u29、顺序编号的电阻r107至电阻r112、电阻r127、电阻r153至电阻r155、电阻r139、电阻r133、磁珠fb44、电容c240、电容c238以及电容c232,所述电阻r107至电阻r112的一端分别与芯片u29的第四十六引脚、第四十五引脚、第四十四引脚、第四十三引脚、第四十一引脚以及第三十九引脚连接,电阻r107至电阻r112的另一端均接地;电阻r127的一端以及电阻r154的一端均与电源v3p3_vdd连接,电阻r127的

另一端与芯片u29的第七引脚连接,电阻r154的另一端与芯片u29的第二十一引脚连接;电阻r155的一端接地,电阻r155的另一端与芯片u29的第二十四引脚连接;芯片u29的第二十引脚通过电阻r153接地;芯片u29的第十九引脚分别与磁珠fb44的一端以及电容c240的一端连接,磁珠fb44的另一端与电容c238的一端连接并接电源v3p3_vdd,电容c240的另一端与电容c238的另一端连接并接地;芯片u29的第四十八引脚、第三十二引脚以及电容c232的一端与电源v3p3_vdd连接,电容c232的另一端与电阻r133的一端连接并接地,电阻r133的另一端、芯片u29的第二十七引脚以及电阻r139的一端连接,电阻r139的另一端与电源v3p3_vdd连接。

7.更进一步地,所述以太网电路还包括电阻r145、电阻r146、电容c78、电容c77、电阻r149、电阻r150、电阻r159、电阻r160、电容c82、电容c81、连接器j5a及顺序编号的电阻r264至电阻r268,所述芯片u29的第十六引脚、电阻r145的一端以及电容c77的一端连接,芯片u29的第十七引脚、电阻r146的一端以及电容c78的一端连接,电阻r145的另一端以及电阻r146的另一端与电源v3p3_vdd连接,电容c77的另一端与连接器j5a的第十九引脚连接,电容c78的另一端与连接器j5a的第十八引脚连接,连接器j5a的第八引脚、第四引脚、第五引脚以及第六引脚分别一一对应的通过电阻r264、电阻r267、电阻r266以及电阻r265接电源v3p3_vdd;连接器j5a的第三引脚通过电阻r268接地;芯片u29的第十四引脚、电容c82的一端、电阻160的一端以及电阻r150的一端连接,芯片u29的第十三引脚、电容c81的一端电阻r159的一端以及电阻r149的一端连接,电阻r149的另一端及电阻r150的另一端与电源v3p3_vdd连接,电阻r159的另一端及电阻r160的另一端接地,电容c82的另一端与连接器j5a的第十三引脚连接,电容c81的另一端与连接器j5a的第十二引脚连接;芯片u29的第一引脚至第六引脚、第三十八引脚、第三十九引脚、第四十三引脚至第四十六引脚、第三十引脚、第三十一引脚分别与fpga的一个io端口连接。

8.进一步地,所述开关量输入电路包括共模电感l-com9、整流桥br4、二极管d21、稳压二极管d9、稳压二极管d25、电阻r119、电容c60、电阻r94、芯片u18、电容c196、电阻r56、电阻r167、电阻r129、电阻r120、电容c61、电阻r95、芯片u19、电容c195、电阻r57、电阻r247、芯片u8、电容c154、电阻r45以及电容c46,所述共模电感l-com9的第一端以及第四端接收开关量输入信号,共模电感l-com9的第三端、整流桥br4的第一交流输入端以及二极管d21的阴极连接,二极管d21的阳极接电源v24p_1,共模电感l-com9的第二端、整流桥br4的第二交流输入端以及稳压二极管d25的阴极连接,整流桥br4的输出正端与稳压二极管d9的阴极连接,整流桥br4的输出负端接地;稳压二极管d9的阳极与电阻r119的一端连接,电阻r119的另一端、电容c60的一端、电阻r94的一端以及芯片u18的第一引脚连接,电容c60的另一端、电阻r94的另一端及芯片u18的第三引脚连接并接地;

9.芯片u18的第六引脚、电阻r56的一端以及电容c196的一端连接并接电源v3p3_vdd,电容c196的另一端接地,电阻r56的另一端、芯片u18的第五引脚以及芯片u8的第六引脚连接;电阻r167的一端与稳压二极管d25的阳极连接,电阻r167、电阻r129及电阻r120依次串联,电阻r120的非串联端、电容c61的一端、电阻r95的一端及芯片u19的第一引脚连接,电容c61的另一端、电阻r95的另一端及芯片u19的第三引脚连接并接地,芯片u19的第六引脚、电容c195的一端及电阻r57的一端连接并接电源v3p3_vdd,电容c195的另一端接地,电阻r57的另一端、芯片u19的第五引脚及芯片u8的第三引脚连接;芯片u8的第一引脚通过电

阻r247与电源v3p3_vdd连接,芯片u8的第五引脚与电容c154的一端连接并接电源v3p3_vdd,电容c154的另一端与芯片u8的第二引脚连接并接地,芯片u8的第四引脚与电阻r45的一端连接,电阻r45的另一端分别与fpga的一个io端口以及电容c46的一端连接,电容c46的另一端接地。

10.进一步地,所述差分放大电路包括磁珠fb27、磁珠fb28、瞬态二极管tvs14、瞬态二极管tvs15、电阻r191、电阻r193、电阻r192、二极管d19、二极管d15、电容c256、芯片u36、电阻r165、电阻r173、电容c242、电阻r137、电容c75及电阻r143,所述磁珠fb27的一端以及磁珠fb28的一端接收电流传感器的信号,磁珠fb27的另一端、瞬态二极管tvs14的一端以及电阻r191的一端连接,磁珠fb28的另一端、瞬态二极管tvs15的一端以及电阻r193的一端连接,瞬态二极管tvs14的另一端以及瞬态二极管tvs15的另一端接地;

11.电阻r191的另一端、二极管d19的阴极、二极管d15的阳极、芯片u36的第二引脚、电阻r137的一端及电阻r143的一端连接,二极管d19的阳极、电阻r193的另一端及电阻r192的一端、二极管d15的阴极及芯片u36的第三引脚连接,电阻r192的另一端接地;芯片u36的第四引脚与电容c256的一端连接并接电源vn8p_av,电容c256的另一端接地;电阻r143的另一端与电容c75的一端连接,电容c75的另一端、电阻r137的另一端及芯片u36的第六引脚连接并作为信号输出端口,电容c242的一端、电阻r173的一端、电阻r165的一端及芯片u36的第七引脚连接并接电源v8p_av,电阻r165的另一端与芯片u36的第八引脚连接,电阻r173的另一端与芯片u36的第一引脚连接。

12.更进一步地,跳合闸回路采集器还包括电流传感器电源电路,所述电流传感器电源电路包括磁珠fb21、电容c88至电容c93、电阻r258、电容c275、芯片u38、电感l5、二极管d29、电阻r197、电阻r198、磁珠fb22、电容c96及电容c278,所述磁珠fb21的一端及电容c90的一端连接并接电源v5p_vdd,磁珠fb21的另一端、电容c88的一端、电容c89的一端、芯片u38的第六引脚、芯片u38的第五引脚及电感l5的一端连接,电容c90的另一端、电容c88的另一端及电容c89的另一端接地;电阻r258的一端与芯片u38的第二引脚连接,电阻r258的另一端通过电容c275接地;电感l5的另一端、二极管d29的阳极及芯片u38的第四引脚连接,二极管d29的阴极、电阻r198的一端、电容c92的一端、电容c91的一端及磁珠fb22的一端连接,电阻r198的另一端、芯片u38的第一引脚及电阻r197的一端连接,电阻r197的另一端、电容c92的另一端及电容c91的另一端连接并接地,磁珠fb22的另一端、电容c96的一端、电容c278的一端及电容c93的一端连接并作为电源输出接口ct_vdd,电容c96的另一端、电容c278的另一端及电容c93的另一端连接并接地。

13.更进一步地,所述ad采样电路包括芯片u4及其外围电路,所述芯片u4的第四十九引脚、第五十一引脚、第五十三引脚、第五十五引脚、第五十七引脚、第五十九引脚、第六十一引脚及第六十三引脚分别通过一个电阻连接一路差分放大电路的信号输出端口,芯片u4的第九引脚、第十引脚、第十一引脚、第十二引脚、第十三引脚、第十四引脚、第二十四引脚及第二十五引脚分别与fpga的一个ad采样端口连接。

14.更进一步地,所述ad采样电路还包括第一电源单元和第二电源单元,所述第一电源单元包括芯片u2、电容c105、电容c106、电容c118、电容c117、电容c114、电容c113、电阻r239及电阻r237,电容c105的一端、电容c106的一端及芯片u2的第一引脚连接并接电源v5p_vdd,电容c105的另一端、电容c106的另一端及芯片u2的第二引脚连接并接地,芯片u2

的第七引脚、电容c118的一端、电容c117的一端及电阻r239的一端连接并作为电源vp9_av的输出端口,电容c118的另一端、电容c117的另一端、电阻r239的另一端、电容c114的一端、电容c113的一端、电阻r237的一端及芯片u2的第六引脚连接并接地,电容c114的另一端、电容c113的另一端及电阻r237的另一端连接并作为电源vn9p_av的输出接口;

15.第二电源单元包括芯片u43、电容c120、电容c123、电容c132、电阻r242、电阻r243、电容c127、电容c119及电容c122,电容c120的一端、电容c123的一端、芯片u43的第八引脚及芯片u43的第五引脚连接并接电源v9p_av,电容c132的一端与芯片u43的第六引脚连接,电容c120的另一端、电容c123的另一端及电容c132的另一端连接并接地;电阻r242的一端、芯片u43的第一引脚、电容c127的一端、电容c119的一端及电容c122的一端连接并作为电源v8p_av的输出接口,芯片u43的第二引脚、电阻r242的另一端、电容c127的另一端及电阻r243的一端连接,芯片u43的第四引脚、芯片u43的第九引脚、电阻r243的另一端、电容c119的另一端及电容c122的另一端连接并接地。

16.进一步地,所述光串口接收和发送电路包括接收单元和发送单元,所述接收单元包括电阻r200、与非门u41a、非门u41b、非门u41c、非门u41d、电阻r269、电容c279、电阻r271、电阻r215、电阻r208、电容c103及光电转换模块j12,所述与非门u41a的第一引脚与fpga的uart接收端口连接,与非门u41a的第二引脚、电阻r200的一端、与非门u41d的第十三引脚、与非门u41b的第四引脚及与非门u41c的第九引脚连接,电阻r200的另一端以及与非门u41a的第十四引脚均与电源v5p_vdd连接,与非门u41a的第七引脚接地,与非门u41a的第三引脚、与非门u41d的第十二引脚、与非门u41b的第五引脚及与非门u41c的第十引脚连接,与非门u41d的第十一引脚、与非门u41b的第六引脚、非门u41c的第八引脚、电阻r269的一端及电容c279的一端连接,电阻r269的另一端及电容c279的另一端均与电阻r271的一端连接,电阻r271的另一端与光电转换模块j12的第三引脚连接;电阻r215的一端、电阻r208的一端及电容c103的一端连接并接fpga的uart接收端口连接,电阻r215的另一端与光电转换模块j12的第二引脚连接,电阻r208的另一端与光电转换模块j12的第六引脚连接,电容c103的另一端接地;

17.所述发送单元包括电阻r199、与非门u40a、与非门u40b、与非门u40c、与非门u40d、电阻r270、电容c280、电阻r272、电阻r211、电阻r206、电容c102及芯片j11,所述与非门u40a的第一引脚与fpga的uart发送端口连接,与非门u40a的第二引脚、电阻r199的一端、与与非门u40d的第十三引脚、与与非门u40b的第四引脚及与与非门u40c的第九引脚连接,电阻r199的另一端以及与非门u40a的第十四引脚均与电源v5p_vdd连接,与非门u40a的第七引脚接地,与非门u40a的第三引脚、与与非门u40d的第十二引脚、与与非门u40b的第五引脚及与与非门u40c的第十引脚连接,与与非门u40d的第十一引脚、与与非门u40b的第六引脚、与非门u40c的第八引脚、电阻r270的一端及电容c280的一端连接,电阻r270的另一端及电容c280的另一端均与电阻r272的一端连接,电阻r272的另一端与芯片j11的第三引脚连接;电阻r211的一端、电阻r206的一端及电容c102的一端连接并接fpga的uart发送端口连接,电阻r211的另一端与芯片j11的第二引脚连接,电阻r206的另一端与芯片j11的第六引脚连接,电容c102的另一端接地。

18.进一步地,所述系统电源电路包括第一降压单元和第二降压单元,所述第一降压单元包括开关sw2、共模电感u39、保险丝f2、电源模块u28、保险丝f1、瞬态二极管tvs1、极性

电容ct1至极性电容ct4、电容c59、电感l4、电容c16、电容c22、电容c11及电容c4,所述开关sw2的第三引脚及第四引脚与dc220v电源连接,开关sw2的第一引脚与共模电感u39的第二引脚连接,开关sw2的第二引脚与共模电感u39的第三引脚连接,共模电感u39的第一引脚接地,共模电感u39的第五引脚与电源模块u28的第一引脚连接,共模电感u39的第四引脚通过保险丝f2与电源模块u28的第二引脚连接;电源模块u28的第四引脚与保险丝f1的一端连接,保险丝f1的另一端、瞬态二极管tvs1的一端、极性电容ct4的正极、电容c59的一端、极性电容ct3的正极及电感l4的一端连接,极性电容ct2的正极、极性电容ct1的正极、电容c16的一端、电容c22的一端、电容c11的一端及电容c4的一端连接并作为电源v5p_vdd的输出接口;电源模块u28的第三引脚、瞬态二极管tvs1的另一端、极性电容ct4的负极、电容c59的负极、极性电容ct3的负极、极性电容ct2的负极、极性电容ct1的负极、电容c16的另一端、电容c22的另一端、电容c11的另一端及电容c4的另一端连接并接地;

19.所述第二降压单元包括电容c9、磁珠fb2、电容c3、电容c2、电容c1、电阻r1、电容c10、芯片u1、电感l1、电阻r2、电阻r4、电阻r3、电容c19、电容c20、磁珠fb3、磁珠fb1、电容c17及电容c18,所述磁珠fb2的一端及电容c9的一端与电源v5p_vdd连接,磁珠fb2的另一端、电容c3的一端、电容c2的一端、电容c1的一端、电阻r1的一端、芯片u1的第十二引脚、芯片u1的第十一引脚及芯片u1的第十引脚连接,电容c9的另一端、电容c3的另一端、电容c2的另一端及电容c1的另一端连接并接地,电阻r1的另一端与芯片u1的第十三引脚连接,电容c10的一端与芯片u1的第九引脚连接,电容c10的另一端与芯片u1的第八引脚连接并接地;电感l1的一端、芯片u1的第一引脚、芯片u1的第二引脚及芯片u1的第三引脚连接,电阻r2的一端与芯片u1的第四引脚连接,电阻r2的另一端、芯片u1的第十四引脚、电感l1的另一端、电阻r4的一端、电容c19的一端、电容c20的一端、磁珠fb1的一端及磁珠fb3的一端连接,磁珠fb1的另一端、磁珠fb3的另一端、电容c17的一端及电容c18的一端连接并接作为电源v3p3_vdd的接口,电阻r4的另一端、芯片u1的第五引脚及电阻r3的一端连接,芯片u1的第七引脚、第六引脚、第十六引脚、第十五引脚及第十七引脚接地,电阻r3的另一端、电容c19的另一端、电容c20的另一端、电容c17的另一端及电容c18的另一端接地。

20.本发明的优点在于:本发明提供一种跳合闸回路采集器,每个电流传感器的信号通过差分放大电路放大以后经ad采样电路进行模数转换以后送入fpga,经过以太网电路、rs485通信电路、光串口接收和发送电路或者uart串口电路将信号传输出去,信号传输方式多,功能齐全,满足变电站所有场合使用,适用于变电站二次回路中跳合闸回路信号采集。

附图说明

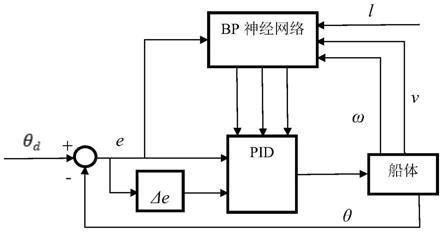

21.图1为本发明实施例所公开的一种跳合闸回路采集器的电路原理框图;

22.图2为本发明实施例所公开的一种跳合闸回路采集器中以太网电路的第一部分原理图;

23.图3为本发明实施例所公开的一种跳合闸回路采集器中以太网电路的第二部分原理图;

24.图4为本发明实施例所公开的一种跳合闸回路采集器中以太网电路的第三部分原理图;

25.图5为本发明实施例所公开的一种跳合闸回路采集器中开关量输入电路的原理

图;

26.图6为本发明实施例所公开的一种跳合闸回路采集器中rs485通信电路的原理图;

27.图7为本发明实施例所公开的一种跳合闸回路采集器中差分放大电路的原理图;

28.图8为本发明实施例所公开的一种跳合闸回路采集器中电流传感器电源电路的原理图;

29.图9为本发明实施例所公开的一种跳合闸回路采集器中ad采样电路的原理图;

30.图10为本发明实施例所公开的一种跳合闸回路采集器中ad采样电路的第一电源单元的原理图;

31.图11为本发明实施例所公开的一种跳合闸回路采集器中ad采样电路的第二电源单元的原理图;

32.图12为本发明实施例所公开的一种跳合闸回路采集器中光串口接收和发送电路的接收单元的第一部分原理图;

33.图13为本发明实施例所公开的一种跳合闸回路采集器中光串口接收和发送电路的接收单元的第二部分原理图;

34.图14为本发明实施例所公开的一种跳合闸回路采集器中光串口接收和发送电路的接收单元的第三部分原理图;

35.图15为本发明实施例所公开的一种跳合闸回路采集器中光串口接收和发送电路的发送单元的第一部分原理图;

36.图16为本发明实施例所公开的一种跳合闸回路采集器中光串口接收和发送电路的发送单元的第二部分原理图;

37.图17为本发明实施例所公开的一种跳合闸回路采集器中光串口接收和发送电路的发送单元的第三部分原理图;

38.图18为本发明实施例所公开的一种跳合闸回路采集器中uart串口电路的第一部分原理图;

39.图19为本发明实施例所公开的一种跳合闸回路采集器中uart串口电路的第二部分原理图;

40.图20为本发明实施例所公开的一种跳合闸回路采集器中时钟扇出电路的原理图;

41.图21为本发明实施例所公开的一种跳合闸回路采集器中系统电源电路的第一降压单元的原理图;

42.图22为本发明实施例所公开的一种跳合闸回路采集器中系统电源电路的第二降压单元的原理图。

具体实施方式

43.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

44.如图1所示,一种跳合闸回路采集器,包括fpga1以及分别与fpga 1连接的以太网电路2、开关量输入电路3、rs485通信电路4、ad采样电路5、光串口接收和发送电路6及uart

串口电路7,还包括若干路差分放大电路8、系统电源电路9及设置于跳合闸回路上的若干个电流传感器10,系统电源电路9为采集器供电,每个电流传感器10分别连接一路差分运放电路,每路差分放大电路8均与ad采样电路5连接。每个电流传感器10采集的跳合闸回路上的信号,通过差分放大电路8放大以后经过ad采样电路5经模拟量信号转换成数字量信号给fpga 1,fpga 1接收到ad采样电路5发送的信号以后通过以太网电路2、rs485通信电路4、光串口接收和发送电路6或者uart串口电路7将信号传输出去,开关量输入电路3主要采集的开关量信号并且将信号传输给fpga 1,fpga 1同样同样通过以太网电路2、rs485通信电路4、光串口接收和发送电路6或者uart串口电路7将信号传输出去。以下通过结合附图详细介绍每个电路的结构。

45.如图2至图4所示,所述以太网电路2包括芯片u29、顺序编号的电阻r107至电阻r112、电阻r127、电阻r153至电阻r155、电阻r139、电阻r133、磁珠fb44、电容c240、电容c238以及电容c232,所述芯片u29的型号为dp83620sq,所述电阻r107至电阻r112的一端分别与芯片u29的第四十六引脚、第四十五引脚、第四十四引脚、第四十三引脚、第四十一引脚以及第三十九引脚连接,电阻r107至电阻r112的另一端均接地;电阻r127的一端以及电阻r154的一端均与电源v3p3_vdd连接,电阻r127的另一端与芯片u29的第七引脚连接,电阻r154的另一端与芯片u29的第二十一引脚连接;电阻r155的一端接地,电阻r155的另一端与芯片u29的第二十四引脚连接;芯片u29的第二十引脚通过电阻r153接地;芯片u29的第十九引脚分别与磁珠fb44的一端以及电容c240的一端连接,磁珠fb44的另一端与电容c238的一端连接并接电源v3p3_vdd,电容c240的另一端与电容c238的另一端连接并接地;芯片u29的第四十八引脚、第三十二引脚以及电容c232的一端与电源v3p3_vdd连接,电容c232的另一端与电阻r133的一端连接并接地,电阻r133的另一端、芯片u29的第二十七引脚以及电阻r139的一端连接,电阻r139的另一端与电源v3p3_vdd连接;

46.以太网电路2还包括电阻r145、电阻r146、电容c78、电容c77、电阻r149、电阻r150、电阻r159、电阻r160、电容c82、电容c81、连接器j5a及顺序编号的电阻r264至电阻r268,所述连接器j5a的型号为z-8281100000000,所述芯片u29的第十六引脚、电阻r145的一端以及电容c77的一端连接,芯片u29的第十七引脚、电阻r146的一端以及电容c78的一端连接,电阻r145的另一端以及电阻r146的另一端与电源v3p3_vdd连接,电容c77的另一端与连接器j5a的第十九引脚连接,电容c78的另一端与连接器j5a的第十八引脚连接,连接器j5a的第八引脚、第四引脚、第五引脚以及第六引脚分别一一对应的通过电阻r264、电阻r267、电阻r266以及电阻r265接电源v3p3_vdd;连接器j5a的第三引脚通过电阻r268接地;芯片u29的第十四引脚、电容c82的一端、电阻160的一端以及电阻r150的一端连接,芯片u29的第十三引脚、电容c81的一端电阻r159的一端以及电阻r149的一端连接,电阻r149的另一端及电阻r150的另一端与电源v3p3_vdd连接,电阻r159的另一端及电阻r160的另一端接地,电容c82的另一端与连接器j5a的第十三引脚连接,电容c81的另一端与连接器j5a的第十二引脚连接;芯片u29的第一引脚至第六引脚、第三十八引脚、第三十九引脚、第四十三引脚至第四十六引脚、第三十引脚、第三十一引脚分别与fpga1的一个io端口连接。

47.如图5所示,所述开关量输入电路3包括共模电感l-com9、整流桥br4、二极管d21、稳压二极管d9、稳压二极管d25、电阻r119、电容c60、电阻r94、芯片u18、电容c196、电阻r56、电阻r167、电阻r129、电阻r120、电容c61、电阻r95、芯片u19、电容c195、电阻r57、电阻r247、

芯片u8、电容c154、电阻r45以及电容c46,所述共模电感l-com9的型号为dlw5bsm501tq2,所述芯片u18及芯片u19的型号为acpl-m50l,芯片u8的型号为sn74lvc1g97dbv,所述共模电感l-com9的第一端以及第四端接收开关量输入信号,共模电感l-com9的第三端、整流桥br4的第一交流输入端以及二极管d21的阴极连接,二极管d21的阳极接电源v24p_1,共模电感l-com9的第二端、整流桥br4的第二交流输入端以及稳压二极管d25的阴极连接,整流桥br4的输出正端与稳压二极管d9的阴极连接,整流桥br4的输出负端接地;稳压二极管d9的阳极与电阻r119的一端连接,电阻r119的另一端、电容c60的一端、电阻r94的一端以及芯片u18的第一引脚连接,电容c60的另一端、电阻r94的另一端及芯片u18的第三引脚连接并接地;芯片u18的第六引脚、电阻r56的一端以及电容c196的一端连接并接电源v3p3_vdd,电容c196的另一端接地,电阻r56的另一端、芯片u18的第五引脚以及芯片u8的第六引脚连接;电阻r167的一端与稳压二极管d25的阳极连接,电阻r167、电阻r129及电阻r120依次串联,电阻r120的非串联端、电容c61的一端、电阻r95的一端及芯片u19的第一引脚连接,电容c61的另一端、电阻r95的另一端及芯片u19的第三引脚连接并接地,芯片u19的第六引脚、电容c195的一端及电阻r57的一端连接并接电源v3p3_vdd,电容c195的另一端接地,电阻r57的另一端、芯片u19的第五引脚及芯片u8的第三引脚连接;芯片u8的第一引脚通过电阻r247与电源v3p3_vdd连接,芯片u8的第五引脚与电容c154的一端连接并接电源v3p3_vdd,电容c154的另一端与芯片u8的第二引脚连接并接地,芯片u8的第四引脚与电阻r45的一端连接,电阻r45的另一端分别与fpga 1的一个io端口以及电容c46的一端连接,电容c46的另一端接地。

48.所述开关量输入电路能自适应有源、无源、极性及不同电压等级的开入量的检测,并且将外部检测电压与内部工作电压隔离开来,既避免了外部电压对设备正常工作造成干扰,又避免了对人员造成的可能是损伤。所述直流隔离电源v24p_1为开入量电路提供电源,u18光电耦合器电路用于将位于强电侧的开入量的实时状态传递到弱电侧,起到强弱电隔离的作用;整流桥br4用于将有源输入量的电压转换成极性固定的电压,以实现有源输入量的极性自适应;芯片u8逻辑门电路能将u18和u19光电耦合器输出的状态进行判断,并供弱电侧的主控器监视。

49.如图6所示,为rs485通信电路4的原理图,其电路结构及原理在此不做赘述,具体参阅图6的接线图。

50.如图7所示,所述差分放大电路8包括磁珠fb27、磁珠fb28、瞬态二极管tvs14、瞬态二极管tvs15、电阻r191、电阻r193、电阻r192、二极管d19、二极管d15、电容c256、芯片u36、电阻r165、电阻r173、电容c242、电阻r137、电容c75及电阻r143,所述磁珠fb27的一端以及磁珠fb28的一端接收电流传感器的信号,磁珠fb27的另一端、瞬态二极管tvs14的一端以及电阻r191的一端连接,磁珠fb28的另一端、瞬态二极管tvs15的一端以及电阻r193的一端连接,瞬态二极管tvs14的另一端以及瞬态二极管tvs15的另一端接地;电阻r191的另一端、二极管d19的阴极、二极管d15的阳极、芯片u36的第二引脚、电阻r137的一端及电阻r143的一端连接,二极管d19的阳极、电阻r193的另一端及电阻r192的一端、二极管d15的阴极及芯片u36的第三引脚连接,电阻r192的另一端接地;芯片u36的第四引脚与电容c256的一端连接并接电源vn8p_av,电容c256的另一端接地;电阻r143的另一端与电容c75的一端连接,电容c75的另一端、电阻r137的另一端及芯片u36的第六引脚连接并作为信号输出端口,电容c242的一端、电阻r173的一端、电阻r165的一端及芯片u36的第七引脚连接并接电源v8p_

av,电阻r165的另一端与芯片u36的第八引脚连接,电阻r173的另一端与芯片u36的第一引脚连接。

51.如图8所示,所述跳合闸回路采集器还包括电流传感器电源电路10,所述电流传感器电源电路10包括磁珠fb21、电容c88至电容c93、电阻r258、电容c275、芯片u38、电感l5、二极管d29、电阻r197、电阻r198、磁珠fb22、电容c96及电容c278,芯片u38的型号为tps61170drv,所述磁珠fb21的一端及电容c90的一端连接并接电源v5p_vdd,磁珠fb21的另一端、电容c88的一端、电容c89的一端、芯片u38的第六引脚、芯片u38的第五引脚及电感l5的一端连接,电容c90的另一端、电容c88的另一端及电容c89的另一端接地;电阻r258的一端与芯片u38的第二引脚连接,电阻r258的另一端通过电容c275接地;电感l5的另一端、二极管d29的阳极及芯片u38的第四引脚连接,二极管d29的阴极、电阻r198的一端、电容c92的一端、电容c91的一端及磁珠fb22的一端连接,电阻r198的另一端、芯片u38的第一引脚及电阻r197的一端连接,电阻r197的另一端、电容c92的另一端及电容c91的另一端连接并接地,磁珠fb22的另一端、电容c96的一端、电容c278的一端及电容c93的一端连接并作为电源输出接口ct_vdd,电容c96的另一端、电容c278的另一端及电容c93的另一端连接并接地。

52.如图9所示,所述ad采样电路5包括芯片u4及其外围电路,芯片u4的型号为ad7606bstz,所述芯片u4的第四十九引脚、第五十一引脚、第五十三引脚、第五十五引脚、第五十七引脚、第五十九引脚、第六十一引脚及第六十三引脚分别通过一个电阻连接一路差分放大电路8的信号输出端口,芯片u4的第九引脚、第十引脚、第十一引脚、第十二引脚、第十三引脚、第十四引脚、第二十四引脚及第二十五引脚分别与fpga1的一个ad采样端口连接;所述外围电路包括电容c36、电容c112、电容c121、电容c124、电容c116、电容c21、电阻r16、电阻r18、电阻r19、电阻r11、电阻r12、电阻r14、电阻r9、电容c30、电容c27、电容c23及电容c31,芯片u4的第一引脚、第三十七引脚、第三十八引脚、第四十八引脚、电容c36的一端、电容c112的一端、电容c121的一端、电容c124的一端及电容c116的一端连接并接电源v5p_av,电容c36的另一端、电容c112的另一端、电容c121的另一端、电容c124的另一端及电容c116的另一端连接并接地;电容c21的一端与芯片u4的第二十三引脚连接,电容c21的另一端接地;电阻r19的一端、电阻r18的一端及电阻r16的一端分别与芯片u4的第三引脚、第四引脚及第五引脚一一对应的连接,电阻r19的另一端、电阻r18的另一端及电阻r16的另一端连接并接地;电阻r14的一端、电阻r12的一端及电阻r11的一端分别与芯片u4的第六引脚、第七引脚及第八引脚一一对应的连接,电阻r14的另一端及电阻r12的另一端与电源v3p3_vd连接,电阻r11的另一端接地;电容c30的一端与芯片u4的第四十二引脚连接,电容c30的另一端接地,电容c27的一端与芯片u4的第三十九引脚连接,电容c23的一端与芯片u4的第三十六引脚连接,电容c27的另一端及电容c23的另一端接地;电容c31的一端、芯片u4的第四十四引脚及芯片u4的第四十五引脚连接,电容c31的另一端接地。

53.所述ad采样电路5还包括第一电源单元和第二电源单元,如图10所示,所述第一电源单元包括芯片u2、电容c105、电容c106、电容c118、电容c117、电容c114、电容c113、电阻r239及电阻r237,芯片u2的型号为12d-05d09n2,电容c105的一端、电容c106的一端及芯片u2的第一引脚连接并接电源v5p_vdd,电容c105的另一端、电容c106的另一端及芯片u2的第二引脚连接并接地,芯片u2的第七引脚、电容c118的一端、电容c117的一端及电阻r239的一端连接并作为电源vp9_av的输出端口,电容c118的另一端、电容c117的另一端、电阻r239的

另一端、电容c114的一端、电容c113的一端、电阻r237的一端及芯片u2的第六引脚连接并接地,电容c114的另一端、电容c113的另一端及电阻r237的另一端连接并作为电源vn9p_av的输出接口。

54.所述ad采样电路以ad7606bstz芯片核心,其是16位电荷再分配逐次逼近型模数转换器,具有8通道同步采样能力、极低的功耗和高分辨率。采用5v单电源供电,集成片上2.5v精密基准电压源和基准电压缓冲器,具有片内滤波和高输入阻抗,可处理

±

5v和

±

10v真双极性模拟输入信号,同时所有通道均能以高达200ksps的吞吐速率采样。输入钳位保护电路可以耐受高达

±

16.5v的电压。无论以何种采样频率工作,其模拟输入阻抗均为1mω。二阶模拟抗混叠滤波器的3db截止频率为22khz;当采样速率为200ksps时,其具有40db抗混叠抑制特性。灵活的数字滤波器采用引脚驱动,可以改善信噪比,并降低3db带宽。并行和串行spi输出接口,可与主控fpga直接连接。

55.如图11所示,第二电源单元包括芯片u43、电容c120、电容c123、电容c132、电阻r242、电阻r243、电容c127、电容c119及电容c122,芯片u43的型号为tps7a4901dgnt,电容c120的一端、电容c123的一端、芯片u43的第八引脚及芯片u43的第五引脚连接并接电源v9p_av,电容c132的一端与芯片u43的第六引脚连接,电容c120的另一端、电容c123的另一端及电容c132的另一端连接并接地;电阻r242的一端、芯片u43的第一引脚、电容c127的一端、电容c119的一端及电容c122的一端连接并作为电源v8p_av的输出接口,芯片u43的第二引脚、电阻r242的另一端、电容c127的另一端及电阻r243的一端连接,芯片u43的第四引脚、芯片u43的第九引脚、电阻r243的另一端、电容c119的另一端及电容c122的另一端连接并接地。

56.所述光串口接收和发送电路6包括接收单元和发送单元,如图12至图14所示,所述接收单元包括电阻r200、与非门u41a、非门u41b、非门u41c、非门u41d、电阻r269、电容c279、电阻r271、电阻r215、电阻r208、电容c103及光电转换模块j12,所述光电转换模块j12的型号为afbr-2418tz,与非门u41a的第一引脚与fpga 1的uart接收端口连接,与非门u41a的第二引脚、电阻r200的一端、与非门u41d的第十三引脚、与非门u41b的第四引脚及与非门u41c的第九引脚连接,电阻r200的另一端以及与非门u41a的第十四引脚均与电源v5p_vdd连接,与非门u41a的第七引脚接地,与非门u41a的第三引脚、与非门u41d的第十二引脚、与非门u41b的第五引脚及与非门u41c的第十引脚连接,与非门u41d的第十一引脚、与非门u41b的第六引脚、非门u41c的第八引脚、电阻r269的一端及电容c279的一端连接,电阻r269的另一端及电容c279的另一端均与电阻r271的一端连接,电阻r271的另一端与光电转换模块j12的第三引脚连接;电阻r215的一端、电阻r208的一端及电容c103的一端连接并接fpga 1的uart接收端口连接,电阻r215的另一端与光电转换模块j12的第二引脚连接,电阻r208的另一端与光电转换模块j12的第六引脚连接,电容c103的另一端接地;接收单元中图12所示的电路为兼容设计,实际应用中使用图13和图14所示的电路。

57.如图15至图17所示,所述发送单元包括电阻r199、与非门u40a、与非门u40b、与非门u40c、与非门u40d、电阻r270、电容c280、电阻r272、电阻r211、电阻r206、电容c102及芯片j11,所述芯片j11的型号为hfbr-1414tz,与非门u40a的第一引脚与fpga 1的uart发送端口连接,与非门u40a的第二引脚、电阻r199的一端、与与非门u40d的第十三引脚、与与非门u40b的第四引脚及与与非门u40c的第九引脚连接,电阻r199的另一端以及与非门u40a的第

十四引脚均与电源v5p_vdd连接,与非门u40a的第七引脚接地,与非门u40a的第三引脚、与与非门u40d的第十二引脚、与与非门u40b的第五引脚及与与非门u40c的第十引脚连接,与与非门u40d的第十一引脚、与与非门u40b的第六引脚、与非门u40c的第八引脚、电阻r270的一端及电容c280的一端连接,电阻r270的另一端及电容c280的另一端均与电阻r272的一端连接,电阻r272的另一端与芯片j11的第三引脚连接;电阻r211的一端、电阻r206的一端及电容c102的一端连接并接fpga 1的uart发送端口连接,电阻r211的另一端与芯片j11的第二引脚连接,电阻r206的另一端与芯片j11的第六引脚连接,电容c102的另一端接地。对发送单元来说,图16所示的电路为兼容设计,实际应用中采用图15和图17所示的电路。

58.如图18和图19所示为uart串口电路7的原理图,其连接关系和工作原理在此不做赘述,本领域技术人员根据图18和图19记载的连接关系能够直接毫无疑义的推导出该电路的原理。

59.如图20所示,本发明的采集器还包括时钟扇出电路,时钟扇出电路与fpga 1的时钟信号端口连接,所述时钟扇出电路的连接关系和工作原理在此不做赘述,本领域技术人员根据图20记载的连接关系能够直接毫无疑义的推导出该电路的原理。

60.所述系统电源电路9包括第一降压单元和第二降压单元,如图21所示,所述第一降压单元包括开关sw2、共模电感u39、保险丝f2、电源模块u28、保险丝f1、瞬态二极管tvs1、极性电容ct1至极性电容ct4、电容c59、电感l4、电容c16、电容c22、电容c11及电容c4,开关sw2的型号为kcd1-104b,共模电感u39的型号为fc-lx1d,电源模块u28的型号为lde10-23b05,所述开关sw2的第三引脚及第四引脚与dc220v电源连接,开关sw2的第一引脚与共模电感u39的第二引脚连接,开关sw2的第二引脚与共模电感u39的第三引脚连接,共模电感u39的第一引脚接地,共模电感u39的第五引脚与电源模块u28的第一引脚连接,共模电感u39的第四引脚通过保险丝f2与电源模块u28的第二引脚连接;电源模块u28的第四引脚与保险丝f1的一端连接,保险丝f1的另一端、瞬态二极管tvs1的一端、极性电容ct4的正极、电容c59的一端、极性电容ct3的正极及电感l4的一端连接,极性电容ct2的正极、极性电容ct1的正极、电容c16的一端、电容c22的一端、电容c11的一端及电容c4的一端连接并作为电源v5p_vdd的输出接口;电源模块u28的第三引脚、瞬态二极管tvs1的另一端、极性电容ct4的负极、电容c59的负极、极性电容ct3的负极、极性电容ct2的负极、极性电容ct1的负极、电容c16的另一端、电容c22的另一端、电容c11的另一端及电容c4的另一端连接并接地;

61.如图22所示,所述第二降压单元包括电容c9、磁珠fb2、电容c3、电容c2、电容c1、电阻r1、电容c10、芯片u1、电感l1、电阻r2、电阻r4、电阻r3、电容c19、电容c20、磁珠fb3、磁珠fb1、电容c17及电容c18,所述芯片u1的型号为tps62130rgtr,所述磁珠fb2的一端及电容c9的一端与电源v5p_vdd连接,磁珠fb2的另一端、电容c3的一端、电容c2的一端、电容c1的一端、电阻r1的一端、芯片u1的第十二引脚、芯片u1的第十一引脚及芯片u1的第十引脚连接,电容c9的另一端、电容c3的另一端、电容c2的另一端及电容c1的另一端连接并接地,电阻r1的另一端与芯片u1的第十三引脚连接,电容c10的一端与芯片u1的第九引脚连接,电容c10的另一端与芯片u1的第八引脚连接并接地;电感l1的一端、芯片u1的第一引脚、芯片u1的第二引脚及芯片u1的第三引脚连接,电阻r2的一端与芯片u1的第四引脚连接,电阻r2的另一端、芯片u1的第十四引脚、电感l1的另一端、电阻r4的一端、电容c19的一端、电容c20的一端、磁珠fb1的一端及磁珠fb3的一端连接,磁珠fb1的另一端、磁珠fb3的另一端、电容c17的

一端及电容c18的一端连接并接作为电源v3p3_vdd的接口,电阻r4的另一端、芯片u1的第五引脚及电阻r3的一端连接,芯片u1的第七引脚、第六引脚、第十六引脚、第十五引脚及第十七引脚接地,电阻r3的另一端、电容c19的另一端、电容c20的另一端、电容c17的另一端及电容c18的另一端接地。

62.通过以上技术方案,本发明提供一种跳合闸回路采集器,每个电流传感器的信号通过差分放大电路放大以后经ad采样电路进行模数转换以后送入fpga,经过以太网电路、rs485通信电路、光串口接收和发送电路或者uart串口电路将信号传输出去,信号传输方式多,功能齐全,满足变电站所有场合使用,适用于变电站二次回路中跳合闸回路信号采集。

63.以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。