技术特征:

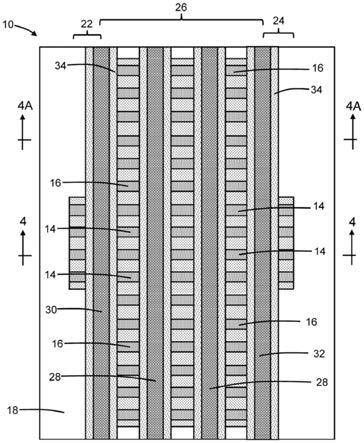

1.一种半导体存储器件,包括:第一堆叠结构,在衬底上,所述第一堆叠结构包括在第一方向上堆叠的第一栅电极;第一支撑层,在所述第一堆叠结构上,所述第一支撑层由第一切割图案划分;第二堆叠结构,在所述第一支撑层上,所述第二堆叠结构包括在所述第一方向上堆叠的第二栅电极;块切割结构,在与所述第一方向交叉的第二方向上延伸,并且切割所述第二堆叠结构或所述第一堆叠结构中的至少一个;第二支撑层,在所述第二堆叠结构上并且由第二切割图案划分;以及沟道结构,包括穿透所述第一堆叠结构的下沟道结构、以及穿透所述第一支撑层和所述第二堆叠结构的上沟道结构,其中,所述沟道结构在与所述第二方向交叉的第三方向上的上表面的宽度大于所述沟道结构在所述第三方向上的下表面的宽度,所述下沟道结构在所述第二方向上的最上表面的宽度大于所述上沟道结构在所述第二方向上的最下表面的宽度,所述第一堆叠结构包括由所述块切割结构至少部分地划分的第一堆叠和第二堆叠,所述第二堆叠结构包括所述第一堆叠上的第三堆叠、以及所述第二堆叠上的第四堆叠,所述第三堆叠和所述第四堆叠由所述块切割结构分开,所述第一支撑层在所述第一堆叠和所述第二堆叠上,所述第二支撑层在所述第三堆叠和所述第四堆叠上,所述第一支撑层的所述第一切割图案包括所述块切割结构上的第一连接,所述第一连接将所述第一堆叠上的所述第一支撑层与所述第二堆叠相连接,并且所述第二支撑层的所述第二切割图案包括所述块切割结构上的第二连接,所述第二连接将所述第三堆叠上的所述第二支撑层与所述第四堆叠相连接。2.根据权利要求1所述的半导体存储器件,其中,所述第一连接包括在所述第二方向上彼此间隔开的n个第一子连接,所述第二连接包括在所述第二方向上彼此间隔开的m个第二子连接,并且n和m是大于或等于1的整数,并且n大于m。3.根据权利要求1所述的半导体存储器件,其中,所述第一连接包括在所述第二方向上彼此间隔开的n个第一子连接,所述第二连接包括在所述第二方向上彼此间隔开的m个第二子连接,n和m是大于或等于1的整数,并且n小于m。4.根据权利要求1所述的半导体存储器件,其中,所述块切割结构包括:第一子切割结构,所述第一子切割结构切割所述第一堆叠结构、所述第一切割图案和所述第二堆叠结构;以及第二子切割结构,所述第二子切割结构切割所述第二堆叠结构,并且所述第二子切割结构在所述第一连接上。5.根据权利要求4所述的半导体存储器件,其中,所述第一子切割结构和所述第二子切割结构在所述第二方向上交替。6.根据权利要求4所述的半导体存储器件,其中,所述第一堆叠结构还包括:连接所述第一堆叠和所述第二堆叠的第一连接堆叠,并且所述第一连接在所述第一连接堆叠上。

7.根据权利要求4所述的半导体存储器件,其中,所述块切割结构在所述第三方向上的上表面的宽度大于所述块切割结构在所述第三方向上的下表面的宽度。8.根据权利要求1所述的半导体存储器件,其中,所述块切割结构包括:(a)第一子切割结构,切割所述第一堆叠结构、所述第一切割图案和所述第二堆叠结构;(b)第二子切割结构,切割所述第二堆叠结构;以及(c)第三子切割结构,切割所述第一堆叠结构,其中所述第一子切割结构和所述第三子切割结构在所述第一方向上由所述第一支撑层彼此间隔开。9.根据权利要求8所述的半导体存储器件,其中,所述第三子切割结构在所述第三方向上的上表面的宽度大于所述第二子切割结构在所述第三方向上的下表面的宽度。10.根据权利要求8所述的半导体存储器件,其中,所述第一子切割结构包括:(a)下切割结构,切割所述第一切割图案和所述第一堆叠结构;以及(b)上切割结构,切割所述第二堆叠结构,其中所述下切割结构在所述第三方向上的最上表面的宽度大于所述上切割结构在所述第三方向上的最下表面的宽度。11.根据权利要求8所述的半导体存储器件,其中,所述下沟道结构包括:(a)第一沟道图案,穿透所述第一堆叠结构;(b)第一信息存储膜,介于所述第一沟道图案与所述第一栅电极中的至少一个第一栅电极之间;以及(c)第一沟道焊盘,设置在所述第一沟道图案上,并且所述上沟道结构包括:(d)第二沟道图案,在所述第一沟道焊盘上并且穿透所述第一支撑层和所述第二堆叠结构;(e)第二信息存储膜,介于所述第二沟道图案与所述第二栅电极中的至少一个第二栅电极之间;以及(f)第二沟道焊盘,在所述第二沟道图案上。12.根据权利要求1所述的半导体存储器件,其中,所述第二连接的至少一部分在所述第一方向上与所述第一连接重叠。13.根据权利要求1所述的半导体存储器件,其中,所述第一支撑层包括第一材料,并且所述第二支撑层包括与所述第一材料不同的第二材料。14.一种半导体存储器件,包括:第一堆叠结构,在衬底上,所述第一堆叠结构包括在第一方向上堆叠的第一栅电极;第一支撑层,在所述第一堆叠结构上;第二堆叠结构,在所述第一堆叠结构上,所述第二堆叠结构包括在所述第一方向上堆叠的第二栅电极;多个第一子切割结构,切割所述第一堆叠结构和所述第二堆叠结构,并且布置在与所述第一方向交叉的第二方向上;第二子切割结构,在所述多个第一子切割结构内的在所述第二方向上彼此间隔开的第

一子切割结构之间,所述第二子切割结构切割所述第二堆叠结构;沟道结构,所述沟道结构包括穿透所述第一堆叠结构的下沟道结构、以及穿透所述第一支撑层和所述第二堆叠结构的上沟道结构,其中,所述沟道结构的侧壁具有阶梯;以及第二支撑层,在所述第二堆叠结构上,其中,所述第一支撑层包括第一切割图案,所述多个第一子切割结构穿透所述第一切割图案,所述第二支撑层包括第二切割图案,所述第二切割图案显露所述多个第一子切割结构的上表面的至少一部分并且显露所述第二子切割结构,并且所述第一切割图案的面积不同于所述第二切割图案的面积。15.根据权利要求14所述的半导体存储器件,其中,所述第一切割图案的面积小于所述第二切割图案的面积。16.根据权利要求14所述的半导体存储器件,其中,所述多个第一子切割结构的侧壁和所述第二子切割结构的侧壁没有阶梯。17.根据权利要求14所述的半导体存储器件,其中,所述多个第一子切割结构的侧壁具有阶梯,并且所述第二子切割结构的侧壁没有阶梯。18.根据权利要求17所述的半导体存储器件,其中,所述多个第一子切割结构的侧壁具有第一水平处的阶梯,并且所述沟道结构具有低于所述第一水平的第二水平处的阶梯。19.一种半导体存储器件,包括:公共源极板,在衬底上;第一堆叠结构,在所述公共源极板上,所述第一堆叠结构包括在第一方向上堆叠的第一栅电极;第一支撑层,在所述第一堆叠结构上并且在与所述第一方向交叉的第二方向上分开,所述第一支撑层由第一切割图案分开;第二堆叠结构,在所述第一堆叠结构上,所述第二堆叠结构包括在所述第一方向上堆叠的第二栅电极;多个第一子切割结构,切割所述第一堆叠结构和所述第二堆叠结构,并且布置在所述第二方向上;第二子切割结构,在所述多个第一子切割结构内的在所述第二方向上彼此间隔开的第一子切割结构之间,所述第二子切割结构切割所述第二堆叠结构;沟道结构,包括(a)穿透所述第一堆叠结构的下沟道结构、以及(b)穿透所述第一支撑层和所述第二堆叠结构的上沟道结构,所述沟道结构的侧壁具有阶梯;第二支撑层,在所述第二堆叠结构上并且在所述第二方向上由第二切割图案分开;以及位线,在所述第二支撑层上,所述位线在所述第一方向上延伸,所述位线连接到所述沟道结构,其中,所述第一堆叠结构包括由所述多个第一子切割结构彼此分开的第一堆叠和第二堆叠、以及所述第二子切割结构下方的第一连接堆叠,所述第一堆叠结构连接所述第一堆叠和所述第二堆叠,所述第二堆叠结构包括由所述多个第一子切割结构和所述第二子切割结构彼此分开

并且设置在所述第一堆叠上的第三堆叠、以及所述第二堆叠上的第四堆叠,所述第一切割图案包括多个第一连接,所述多个第一连接与所述多个第一子切割结构和所述第二子切割结构在所述第一方向上重叠,所述第一切割图案在所述第二方向上位于所述第一连接堆叠上,所述第二切割图案包括多个第二连接,所述多个第二连接在所述第一方向上与所述多个第一子切割结构和所述第二子切割结构重叠,所述第二切割图案在所述第二方向上,并且所述多个第一连接的数量大于所述多个第二连接的数量。20.根据权利要求19所述的半导体存储器件,还包括:第三子切割结构,由所述第一支撑层在所述第一方向上与所述第二子切割结构间隔开,并且切割所述第一堆叠结构。

技术总结

一种半导体存储器件,包括:第一堆叠结构、第一支撑层、第二堆叠结构、块切割结构、以及在所述第二堆叠结构上并且由第二切割图案分开的第二支撑层。所述第一堆叠结构包括第一堆叠和第二堆叠,所述第二堆叠结构包括由所述块切割结构分开的第三堆叠和第四堆叠,所述第一支撑层在所述第一堆叠和所述第二堆叠上,所述第二支撑层在所述第三堆叠和所述第四堆叠上,第一切割图案包括所述块切割结构上并且连接所述第一支撑层和所述第二堆叠的第一连接,并且所述第二支撑层的所述第二切割图案包括所述块切割结构上并且连接设置在所述第三堆叠和所述第四堆叠上的所述第二支撑层的第二连接。所述第四堆叠上的所述第二支撑层的第二连接。所述第四堆叠上的所述第二支撑层的第二连接。

技术研发人员:金志荣 梁宇成 黄盛珉 成锡江 任峻成

受保护的技术使用者:三星电子株式会社

技术研发日:2021.07.21

技术公布日:2022/1/25

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。