condition)被满足,利用该修整控制电路在该暂存器电路中产生并储存多个处理结果,以供被发送回该处理电路,以完成该锁相环的该参数调整,从而实现该存储装置的该系统上锁相环管理。6.除了上述方法以外,本发明还提供一种存储装置,而该存储装置包含一非挥发性存储器和一控制器。该非挥发性存储器被配置成储存信息,其中该非挥发性存储器可以包含至少一非挥发性存储器元件(例如一或多个非挥发性存储器元件)。该控制器耦接至该非挥发性存储器,并且该控制器被配置成控制该存储装置的操作。另外,控制器包含一处理电路,而该处理电路被配置成根据来自一主机装置的多个主机命令来控制该控制器,以容许该主机装置透过该控制器存取该非挥发性存储器。该控制器另包含耦接至该处理电路的一传输接口电路,并且该传输接口电路被配置成与该主机装置进行通信,其中该传输接口电路包含一物理层(phy)电路。该物理层电路包含一锁相环(pll)、一修整控制电路和一暂存器电路,其中该物理层电路中的一压控振荡器(vco)是用一压控晶体振荡器(vcxo)实现,且该修整控制电路被配置为对该锁相环进行修整控制,以支持使用该压控晶体振荡器的该锁相环的优化,其中该锁相环的该优化包含该锁相环的参数调整。该暂存器电路被配置成储存该锁相环的多个参数,并储存该锁相环的该参数调整的多个处理结果,其中该多个参数包含多个控制参数。例如,该控制器利用该处理电路设定该多个控制参数,以控制该锁相环的该参数调整;该控制器利用该修整控制电路根据该多个控制参数进行该锁相环的该参数调整,以调整该多个参数中的一组电压参数,以优化该压控振荡器的一控制电压,其中该控制电压对应于该组电压参数,且该压控振荡器的振荡频率对应于该控制电压;以及在该锁相环的该参数调整的期间,因应该锁相环的该参数调整的至少一预定条件被满足,该控制器利用该修整控制电路在该暂存器电路中产生并储存该多个处理结果,以供被发送回该处理电路,以完成该锁相环的该参数调整,从而实现该存储装置的系统上锁相环管理。7.根据某些实施例,本发明还提供了相关的电子装置。该电子装置可以包含上述存储装置,并且可以进一步包含一主机装置,并且该主机装置可以耦接至该存储装置。该主机装置可以包含:至少一处理器,被配置成控制该主机装置的操作;以及一电源供应电路,耦接至该至少一处理器,用以提供电源至该至少一处理器及该存储装置。另外,存储装置可以为该主机装置提供储存空间。8.除了上述方法以外,本发明还提供了一种存储装置的控制器,其中该存储装置包含该控制器和一非挥发性存储器。该非挥发性存储器可包含至少一非挥发性存储器元件(例如一或多个非挥发性存储器元件)。另外,控制器包含一处理电路,而该处理电路被配置成根据来自一主机装置的多个主机命令来控制该控制器,以容许该主机装置透过该控制器存取该非挥发性存储器。该控制器另包含耦接至该处理电路的一传输接口电路,并且该传输接口电路被配置成与该主机装置进行通信,其中该传输接口电路包含一物理层(phy)电路。该物理层电路包含一锁相环(pll)、一修整控制电路和一暂存器电路,其中该物理层电路中的一压控振荡器(vco)是用一压控晶体振荡器(vcxo)实现,且该修整控制电路被配置为对该锁相环进行修整控制,以支持使用该压控晶体振荡器的该锁相环的优化,其中该锁相环的该优化包含该锁相环的参数调整。该暂存器电路被配置成储存该锁相环的多个参数,并储存该锁相环的该参数调整的多个处理结果,其中该多个参数包含多个控制参数。例如,该控制器利用该处理电路设定该多个控制参数,以控制该锁相环的该参数调整;该控制器利用修整控制电路根据该多个控制参数进行该锁相环的该参数调整,以调整该多个参数中的一组电压参数,以优化该压控振荡器的一控制电压,其中该控制电压对应于该组电压参数,且该压控振荡器的振荡频率对应于该控制电压;以及在该锁相环的该参数调整的期间,因应该锁相环的该参数调整的至少一预定条件被满足,该控制器利用该修整控制电路在该暂存器电路中产生并储存该多个处理结果,以供被发送回该处理电路,以完成该锁相环的该参数调整,从而实现该存储装置的系统上锁相环管理。9.根据某些实施例,该设备可以包含该电子装置的至少一部分(例如:一部分或全部)。举例来说,该设备可以包含该存储装置内的该存储器控制器。在另一个示例中,该设备可以包含该存储装置。在某些示例中,该设备可以包含该电子装置的整体。另外,该存储装置的该存储器控制器可以根据该方法控制该存储装置的操作。举例来说,因应来自该主机装置的一主机命令诸如一写入命令,该存储装置可以为该主机装置储存数据。该存储装置可以因应来自该主机装置的另一主机命令诸如一读取命令来读取所储存的数据,并且向该主机装置提供从该非挥发性存储器读取的数据。此外,该非挥发性存储器可以包含一或多个非挥发性存储器元件(例如,一或多个快闪存储器(flashmemory)裸晶(die),或一或多个快闪存储器晶片)。10.本发明的方法及相关设备能确保该存储装置能在各种情况下妥善地运作。正当高稳定性和低相位噪声可以藉由使用该压控晶体振荡器实现该锁相环中的该压控振荡器来达成之际,本发明的方法及相关设备可以优化一控制电压以供控制该压控振荡器,例如,藉助于针对该压控振荡器的该控制电压的一优化工作流程,以确保一极短的安顿(settling)时间和该锁相环的一准确频率。另外,本发明的方法及相关设备可以在没有副作用或较不会带来副作用的情况下解决相关技术的现有问题。【附图说明】11.图1为依据本发明一实施例的一电子装置的示意图。12.图2是依据本发明一实施例所绘示的一种用于在一存储装置诸如图1所示的存储装置中进行系统上(on-system)锁相环(phase-lockedloop,简称pll)管理的方法的一控制方案的示意图。13.图3是依据本发明一实施例所绘示的用于在该存储装置中进行该系统上pll管理的方法的一工作流程。14.图4是依据本发明一实施例所绘示的针对图4所示的工作流程中的某些操作的某些实施细节的示意图。15.图5绘示了该方法所涉及的一pll的示例。16.符号说明17.10:电子装置18.50:主机装置19.52:处理器20.54:电源供应电路21.100:存储装置22.110:存储器控制器23.112:微处理器24.112c:程序码25.112m:只读存储器26.114:控制逻辑电路27.116:缓冲存储器28.118:传输接口电路29.118app:应用层电路30.118mac:媒体存取控制层电路31.118phy:物理层(phy)电路32.118l:锁相环(pll)33.118t:修整控制(tc)电路34.118r:暂存器(reg)电路35.120:非挥发性存储器36.122-1,122-2~122-n:非挥发性存储器元件37.120sys:系统信息38.118v:压控振荡器(vco)39.rcnt:参考时钟计数器40.tcnt:传输(tx)位元时钟计数器41.refclk:参考时钟42.vp:电源电压43.trim_enable:修整启用参数44.count_limit:计数极限45.vref[trim],vctrl[trim]:暂时值[0046]vref[result],vctrl[result]:结果值[0047]s11~s15,s16a,s16b,s17:步骤[0048]refclk_sel:参考时钟选择参数[0049]gear_speed:齿轮速度[0050]vstep[ref,ctrl],vstep:电压步长[0051]th_diff:计数差阈值[0052]timeout_count:超时计数[0053]count_diff_max:最大计数差[0054]tcount:循环计数[0055]count_diff:计数差[0056]adjust:调整步长[0057]vref_cur,vctrl_cur:当前值[0058]vref_next,vctrl_next:下一个值[0059]118f:低通滤波器(lpf)[0060]118d:分频器(div)[0061]pd:相位检测器[0062]vref:电压参考参数[0063]vctrl:电压控制参数【具体实施方式】[0064]图1为依据本发明一实施例的一种电子装置10的示意图,其中电子装置10包含一主机装置(hostdevice)50与一存储装置100。主机装置50可以包含:至少一处理器52(例如一或多个处理器),用来控制主机装置50的操作;以及一电源供应电路54,耦接至上述至少一处理器52,用来提供电源给上述至少一处理器52与存储装置100,以及输出一或多个驱动电压至存储装置100,其中存储装置100可以用来提供储存空间给主机装置50,并且从主机装置50取得该一或多个驱动电压,作为存储装置100的电源。主机装置50的例子可以包含(但不限于):多功能行动电话(multifunctionalmobilephone)、平板电脑(tablet)、以及个人电脑(personalcomputer)诸如桌上型电脑与膝上型电脑。存储装置100的例子可以包含(但不限于):固态硬碟(solidstatedrive,ssd)以及各种嵌入式(embedded)存储装置(诸如符合ufs或emmc规格的嵌入式存储装置)。依据本实施例,存储装置100可以包含一控制器诸如存储器控制器110,且可以另包含一非挥发性存储器(non-volatilememory,nvmemory)120,其中该控制器诸如存储器控制器110是用来为主机装置50存取(access)非挥发性存储器120,且非挥发性存储器120系用来储存信息。非挥发性存储器120可以包含至少一非挥发性存储器元件(nvmemoryelement)(例如一或多个非挥发性存储器元件),诸如多个非挥发性存储器元件122-1、122-2、…与122-n,其中符号“n”可以代表大于一的正整数。举例来说,非挥发性存储器120可以是一快闪存储器(flashmemory),而非挥发性存储器元件122-1、122-2、…与122-n可以分别是多个快闪存储器晶片(flashmemorychip;可以简称为快闪晶片)或多个快闪存储器裸晶(flashmemorydie;可以简称为快闪裸晶),但是本发明不限于此。[0065]如图1所示,存储器控制器110可以包含一处理电路诸如一微处理器112、一储存单元诸如一只读存储器(readonlymemory,rom)112m、一控制逻辑电路114、一缓冲存储器116与一传输接口电路118,其中这些元件中之至少一部分(例如一部分或全部)可透过总线彼此耦接。缓冲存储器116是用一随机存取存储器(randomaccessmemory,ram)来实施,例如可以是一静态随机存取存储器(staticram,sram),其中该随机存取存储器可以用来提供内部储存空间给存储器控制器110,例如可以暂时地储存信息,但是本发明不限于此。另外,本实施例的只读存储器112m是用来储存一程序码112c,而微处理器112则是用来执行程序码112c以控制对非挥发性存储器120的存取。请注意,程序码112c也可以被储存在缓冲存储器116或任何形式的存储器内。此外,控制逻辑电路114可以用来控制非挥发性存储器120。控制逻辑电路114可以包含一错误更正码电路(errorcorrectioncodecircuit,可简称为“ecc电路”;未显示于图1),其可以进行错误更正码编码(eccencoding,可简称为“ecc编码”)与错误更正码解码(eccdecoding,可简称为“ecc解码”),以保护数据、及/或进行错误更正,并且传输接口电路118可以符合一特定通信标准(例如,串列高级技术附件(serialadvancedtechnologyattachment,sata)标准、通用序列总线(universalserialbus,usb)标准、快捷外设互联(peripheralcomponentinterconnectexpress,pcie)标准、嵌入式多媒体记忆卡(embeddedmultimediacard,emmc)标准、或通用快闪存储器储存(universalflashstorage,ufs)标准),且可以依据该特定通信标准,与主机装置50进行通信。[0066]为了更好的理解,传输接口电路118可以包含分别对应于多个层的多个子电路,诸如一物理层(physicallayer,简称phy)电路118phy、一媒体存取控制层(mediaaccesscontrollayer,简称mac层)电路118mac和一应用层(applicationlayer)电路118app,并且,该多个子电路诸如phy电路118phy、mac层电路118mac和应用层电路118app等可以藉由控制逻辑等方式来实现。phy电路118phy可以包含一锁相环(phase-lockedloop,简称pll)118l、一修整控制(trimmingcontrol,tc)电路118t和一暂存器(register,reg)电路118r(于图1中可以分别标示为“pll”、“tc”和“reg”以求简明)。另外,暂存器电路118r可以包含多个暂存器,并且这些暂存器的至少一部分(例如,一部分或全部)可以被配置成储存phy电路118phy的多个参数,诸如pll118l的某些参数。举例来说,pll118l中的一压控振荡器(voltagecontrolledoscillator,简称vco;未显示于图1中)可以藉由一压控晶体振荡器(voltagecontrolledcrystaloscillator,简称vcxo)来实现,而不是藉由一非晶体振荡器(non-crystaloscillator)来实现。使用该vcxo有助于达到高数据速率要求,并且可以具有某些优点诸如高稳定性、低相位噪声等、以及某些缺点诸如窄频率范围、电压灵敏度等。修整控制电路118t可以支持pll118l的优化(例如,参数调整),以减少或消除由于该vcxo引起的不想要的效应。在微处理器112的控制下,存储装置100可以进行pll118l的该优化以更新在暂存器电路118r中的一或多个参数(例如,phy电路118phy的该多个参数中的一或多个参数、及/或pll118l的这些参数中的一或多个参数)。于是,传输接口电路118可以很容易地在一高数据速率诸如10gbps或更高的数据速率中操作,以增强电子装置10的整体效能。[0067]于本实施例中,主机装置50可以向存储器控制器110发送多个主机命令(hostcommand)诸如主机装置命令(hostdevicecommand)以及对应的逻辑地址,以间接地存取存储装置100内的非挥发性存储器120。存储器控制器110接收该多个主机命令与逻辑地址,并且将该多个主机命令分别转译成存储器操作命令(可以称为操作命令,以求简明),且进一步以操作命令控制非挥发性存储器120读取、写入(write)/编程(program)非挥发性存储器120内的特定物理地址的存储单元(memoryunit)或数据页面(page),其中物理地址关联于逻辑地址。例如,存储器控制器110可以产生或更新至少一逻辑对物理地址映射表(logical-to-physicaladdressmappingtable,简称l2p地址映射表)诸如一或多个l2p地址映射表,以管理物理地址与逻辑地址之间的关系。非挥发性存储器120可以储存系统信息120sys,以供存储器控制器110控制存储装置100的操作。系统信息120sys的例子可包含(但不限于):该一或多个l2p地址映射表的一或多个储存位置(例如一或多个物理地址)、phy电路118phy的一或多个参数、以及pll118l的一或多个参数。当需要时,存储器控制器110可以将系统信息120sys的至少一部分(例如,一部分或全部)加载到缓冲器存储器116或其它存储器中。系统信息120sys可以位于非挥发性存储器元件122-1内的一预定区域中,诸如一系统区域(systemregion),但是本发明不限于此。在某些实施例中,系统信息120sys可以位于非挥发性存储器元件122-1、122-2,...和122-n中的任何一个非挥发性存储器元件内的一预定区域中,诸如一系统区域。[0068]另外,前述的至少一非挥发性存储器元件(例如,该一或多个非挥发性存储器元件诸如{122-1,122-2,…,122-n})可包含多个区块,其中存储器控制器110对非挥发性存储器120进行抹除数据的操作的最小单位可以是区块,并且存储器控制器110对非挥发性存储器120进行写入数据的操作的最小单位可以是页面,但是本发明不限于此。例如,非挥发性存储器元件122-1、122-2、…与122-n中的任一非挥发性存储器元件122-n(符号“n”可代表区间[1,n]中的任一整数)可以包含一群区块,且这一群区块中的一区块可以包含并且记录特定数量的页面,其中,存储器控制器110可以依据一区块地址与一页面地址来存取这一群区块中的某一区块中的某一页面。对于另一个示例,非挥发性存储器元件122-n可以包含多个平面(plane),且该多个平面中的任一平面可以包含一组区块诸如这一群区块,其中存储器控制器110可以依据一平面编号(planenumber)、一区块地址与一页面地址来存取该多个平面中的某一平面中的某一区块中的某一页面。随着区块的总数的增加,非挥发性存储器120的储存空间可以变得更大。关于制造非挥发性存储器120,可以利用许多技术,例如:二维(twodimensional,简称2d)/平面nand快闪存储器技术,其可以将存储器单元排列成单层;以及三维(threedimensional,简称3d)nand快闪存储器技术,其可以将存储器单元排列成多层的垂直堆栈。根据某些实施例,非挥发性存储器120可以被实现为具有被排列在单层中的存储器单元的2d/平面nand快闪存储器结构。根据某些实施例,非挥发性存储器120可以被实现为具有被垂直地堆迭的多层存储器单元的3dnand快闪存储器结构。在这种情况下,非挥发性存储器120的储存空间可以变得非常大。由于传输接口电路118可以很容易地在一高数据速率诸如10gbps或更高的数据速率中操作,所以当需要在存储装置100(例如,非挥发性存储器120)中存取大量数据时,存储器控制器110可以保证电子装置10的整体效能。[0069]图2是依据本发明一实施例所绘示的一种用于在一存储装置诸如图1所示的存储装置100中进行系统上(on-system)锁相环(pll)管理的方法的一控制方案的示意图。存储器控制器110可以被配置为对pll118l进行该系统上pll管理,尤其,在存储装置100的一上电(power-up)阶段和一适应均衡(adaptequalization)阶段的任何阶段(例如,每个阶段)进行图2所示的控制方案的相关操作。举例来说,微处理器112可以利用其控制逻辑,诸如在微处理器112内的固件(firmware,简称fw)/晶片上系统(system-on-chip,简称soc)暂存器,来设定某些控制参数以供控制修整控制电路118t。例如,这些控制参数可以包含:一修整启用参数trim_enable,用于指出pll修整(例如,pll参数调整)是否被启用(enable);以及一计数极限count_limit,用于指出该pll修整的目标(例如,在该pll修整的期间,被预期要达到的一目标计数值)。另外,phy电路118phy可以利用暂存器电路118r来为修整控制电路118t接收这些控制参数,诸如修整启用参数trim_enable、计数极限count_limit等,但是本发明不限于此。例如,phy电路118phy可以利用暂存器电路118r来储存该pll修整的处理结果,以供透过上述fw/soc暂存器被发送回微处理器112。[0070]如图2所示,位于phy电路118phy中并且耦接至修整控制电路118t的一时钟分频器模组(标示为“时钟分频器”以求简明)包含pll118l。pll118l中的前述vco可以被绘示为vco118v,并且可以藉由该vcxo来实现。修整控制电路118t和pll118l都可以接收一参考时钟refclk,并且参考时钟refclk可以从存储装置100的一印刷电路板(printedcircuitboard,简称pcb)取得,尤其,透过主机装置50和存储装置100之间的连接,从主机装置50取得,其中存储器控制器110和非挥发性存储器120可以藉由安装在该pcb上的一或多个晶片来实现。例如,参考时钟refclk可以具有多个预定频率的其中之一,诸如19.2百万赫兹(megahertz,简称mhz)、26mhz、38.4mhz或54mhz(标示为“refclk=19.2/26/38.4/54mhz”,以便有更好的理解)。另外,该时钟分频器模组可以进一步包含一分频器(frequencydivider;未显示于图2),并且利用该分频器对pll118l的一pll输出的频率进行分频以产生一传输位元时钟(transmissionbitclock,简称“tx位元时钟”)。于是,该tx位元时钟载有(carry)该pll输出的该频率的一分频频率(dividedfrequency),并且该分频频率是与该pll输出的该频率成正比。[0071]pll118l可以被配置为尝试锁定到参考时钟refclk的一当前频率(例如,该多个预定频率的其中之一)上。不论pll118l是否进入一稳定状态,该tx位元时钟都载有与该pll输出的该频率成正比的该分频频率。当修整启用参数trim_enable指出微处理器112启用该pll修整(例如,该pll参数调整)时,修整控制电路118t可以被配置成根据参考时钟refclk和该tx位元时钟,为微处理器112对pll118l(例如,vco118v)进行修整控制。如图2所示,修整控制电路118t包含分别对应于参考时钟refclk和该tx位元时钟的一参考时钟计数器rcnt和一tx位元时钟计数器tcnt。修整控制电路118t可以利用参考时钟计数器rcnt和tx位元时钟计数器tcnt来分别监控参考时钟refclk和该tx位元时钟,例如,藉由分别对参考时钟refclk和该tx位元时钟的各自的循环计数(cyclecount;也可以称为周期计数)rcount和tcount(诸如参考时钟refclk和该tx位元时钟分别经历了多少个周期的循环,分别以其各自的周期为单位来度量)进行计数。[0072]请注意,vco118v的一振荡频率,诸如vco118v的振荡器输出(例如vco118v的输出)的频率,典型地对应于vco118v的一控制电压,这表示vco118v的该振荡频率可以藉由调整vco118v的该控制电压来调整。例如,vco118v的该振荡器输出可以用来作为pll118l的该pll输出。另外,phy电路118phy的该多个参数可以包含一电压参考参数vref和一电压控制参数vctrl,用于微调(fine-tune)vco118v的该控制电压。举例来说,vco118v可以被配置为从存储装置100内(例如,微处理器112内)的一电源管理电路取得一电源电压vp,并且根据电压参考参数vref和电压控制参数vctrl将电源电压vp转换为vco118v的该控制电压,例如,藉由使用对应于电压参考参数vref的一主要(primary)调整电压vref(例如,一偏移(offset)电压)来调整(例如增加或减少)电源电压vp、及/或藉由使用对应于电压控制参数vctrl的一次要(secondary)调整电压vctrl(例如,一微小电压)来调整(例如增加或减少)电源电压vp,其中次要调整电压vctrl的绝对值典型地小于主要调整电压vref的绝对值(例如:|vctrl|《|vref|),并且主要调整电压vref的绝对值典型地小于电源电压vp(例如:|vref|<vp),但是本发明不限于此。[0073]在对pll118l(例如,vco118v)进行该修整控制的期间,修整控制电路118t可以分别将电压参考参数vref和电压控制参数vctrl暂时地设定为其暂时值vref[trim]和vctrl[trim]。例如,暂时值vref[trim]可以代表电压参考参数vref的多个候选值{vref[0],vref[1],...}的其中之一,而暂时值vctrl[trim]可以代表电压控制参数vctrl的多个候选值{vctrl[0],vctrl[1],...}的其中之一。当pll118l的该优化(例如,该参数调整)完成时,修整控制电路118t可以从多个候选值{vref[0],vref[1],...}中选择一优化的候选值vref[]作为电压参考参数vref的一结果值vref[result],并且从多个候选值{vctrl[0],vctrl[1],...}中选择一优化的候选值vctrl[]作为电压控制参数vctrl的一结果值vctrl[result[1]。[0074]根据某些实施例,参考时钟refclk可以从存储装置100的一内部时钟源取得。例如,该内部时钟源可以位于存储器控制器110中,尤其,可以位于phy电路118phy外部或位于传输接口电路118的外部。对于另一示例,该内部时钟源可以接收vco118v的该振荡器输出,并且藉由使用该内部时钟源内的一或多个分频器将该振荡器输出转换为参考时钟refclk。[0075]图3是依据本发明一实施例所绘示的用于在该存储装置中进行该系统上pll管理的方法的一工作流程。该方法(例如该工作流程)可以被应用于(appliedto)图1所示的存储装置100,尤其,可以被应用于存储器控制器110及其内部元件。例如,该系统上pll管理可以包含该pll修整和相关联的控制。[0076]在步骤s11中,存储器控制器110(例如,运行着程序码112c的微处理器112)可以判定(determine)存储装置100是否处于该上电阶段或该适应均衡阶段(标示为“上电或适应均衡”以求简明)。如果是(例如,存储装置100处于该上电阶段和该适应均衡阶段的任何阶段),则进入步骤s12;如果否,则进入步骤s17。举例来说,存储装置100刚刚被上电,且因此处于该上电阶段。对于另一示例,存储装置100被配置成进行适应均衡(例如,因应功率/速度模式的改变,诸如存储装置100与主机装置50之间的连接的功率/速度模式的改变),且因此处于该适应均衡阶段。[0077]在步骤s12中,存储器控制器110(例如,修整控制电路118t)可以判定该pll修整的一修整处理是否被启用(标示为“修整处理启用”以求简明)。如果是,则进入步骤s13;如果否,则进入步骤s17。根据至少一预定规则(例如一或多个预定规则),运行着程序码112c的微处理器112可以判定是否启用该pll修整(例如,其修整处理)并相应地设定修整启用参数trim_enable。举例来说,当存储装置100是处于该上电阶段时,或者当存储装置100处于该适应均衡阶段并且该适应均衡是初始适应均衡时,运行着程序码112c的微处理器112可以判定启用该pll修整,并且设定修整启用参数trim_enable以指出该pll修整被启用,所以修整控制电路118t可以参考修整启用参数trim_enable来判定该pll修整(例如,其修整处理)被启用。当存储装置100是处于该适应均衡阶段并且该适应均衡是刷新(refresh)适应均衡(例如,次要适应均衡或后续的适应均衡)而不是该初始适应均衡时,或者当存在一错误记录(例如,微处理器112所记录的一记录,用于指出发生某一类型的错误)时,运行着程序码112c的微处理器112可以判定停用(disable)该pll修整,并且设定修整启用参数trim_enable以指出该pll修整未被启用,所以修整控制电路118t可以参考修整启用参数trim_enable来判定该pll修整(例如,其修整处理)未被启用。[0078]在步骤s13中,存储器控制器110(例如,修整控制电路118t)可以触发一组修整计数器,诸如参考时钟计数器rcnt和tx位元时钟计数器tcnt,以使这些修整计数器开始计数,尤其,控制参考时钟计数器rcnt和tx位元时钟计数器tcnt以分别计数参考时钟refclk和该tx位元时钟的各自的循环计数rcount和tcount。例如,参考时钟计数器rcnt可以从一初始值诸如零开始,针对参考时钟refclk的每一循环,用等于一的增量来增加其计数值,诸如参考时钟refclk的循环计数rcount。再举一个例子,tx位元时钟计数器tcnt可以从一初始值诸如零开始,针对该tx位元时钟的每一循环,用等于一的增量来增加其计数器值,诸如该tx位元时钟的循环计数tcount。针对某一信号诸如参考时钟refclk、该tx位元时钟等的循环检测,当这个信号的从逻辑低电平“0”到逻辑高电平“1”的转变以及从逻辑高电平“1”到逻辑低电平“0”的转被检测到时,这个信号的一个循环被检测到,且因此关联的计数器(例如,参考时钟计数器rcnt和tx位元时钟计数器tcnt中的对应的计数器)可以用等于一的增量来增加其计数值,但是本发明不限于此。[0079]在步骤s14中,存储器控制器110(例如,修剪控制电路118t)可以判定一修剪超时(trimtimeout)条件(标示为“修剪超时”以求简明)是否被满足。如果是,则进入步骤s15;如果否,则重新进入步骤s14以等待该修整超时条件被满足。举例来说,该修整超时条件可以包含:参考时钟refclk的循环计数rcount达到一预定循环计数阈值(predeterminedcyclecountthreshold),诸如一超时计数timeout_count。由于参考时钟refclk的频率等于该多个预定频率中的某一频率,所以参考时钟refclk的周期是固定的。将这个周期乘以参考时钟refclk的循环计数rcount而得到的乘积可以代表等待该修整超时条件被满足的经过时间(elapsedtime),并且将这个周期乘以该预定循环计数阈值(例如,超时计数timeout_count)而得到的乘积可以代表对应于该预定循环计数阈值的时间阈值。[0080]在步骤s15中,存储器控制器110(例如,修整控制电路118t)可以判定tx位元时钟计数器tcnt的循环计数tcount是否落入(例如,命中)一预定范围诸如在计数极限count_limit附近的一目标范围(标示为“命中计数极限”以求简明)。如果是(这表示pll118l的该优化已完成),则进入步骤s16a;如果否,则进入步骤s16b。该目标范围可以是区间[count_limit-count_diff_max,count_limit count_diff_max]的范围,其中最大计数差count_diff_max可以是一非负(non-negative)整数,尤其,可以是正整数。举例来说,存储器控制器110(例如,修整控制电路118t)可以计算循环计数tcount与计数极限count_limit之间的差(tcount-count_limit)的绝对值|tcount-count_limit|以作为一计数差count_diff,并且根据计数差count_diff是否小于或等于最大计数差count_diff_max来判定循环计数tcount是否落入(例如,命中)该预定范围。当计数差count_diff小于或等于最大计数差count_diff_max时,修整控制电路118t可以判定循环计数tcount落入(例如,命中)该预定范围。[0081]在步骤s16a中,当pll118l的该优化(例如,该参数调整)完成时,存储器控制器110(例如,修整控制电路118t)可以分别用结果值vref[result]和结果值vctrl[result]来更新电压参考参数vref和电压控制参数vctrl(标示为“更新vref及vctrl结果”以便有更好的理解)。举例来说,修整控制电路118t可以选择在包含步骤s13~s15和s16b的回圈中刚刚被使用的电压参考参数vref的最新候选值vref[]和电压控制参数vctrl的最新候选值vctrl[],以分别作为电压参考参数vref的结果值vref[result]和电压控制参数vctrl的结果值vctrl[result],并且藉由将电压参考参数vref的结果值vref[result]和电压控制参数vctrl的结果值vctrl[result]回传(return)给微处理器112来更新电压参考参数vref和电压控制参数vctrl。[0082]在步骤s16b中,存储器控制器110(例如,修整控制电路118t)可以调整电压参考参数vref和电压控制参数vctrl。举例来说,修整控制电路118t可以藉由从多个候选值{vref[0],vref[1],...}中选择另一个候选值vref[]作为暂时值vref[trim]来调整电压参考参数vref,并且藉由从多个候选值{vctrl[0],vctrl[1],...}中选择另一个候选值vctrl[]作为暂时值vctrl[trim]来调整电压控制参数vctrl。[0083]在步骤s17中,存储器控制器110(例如,运行着程序码112c的微处理器112)可以将存储装置100保持闲置(标示为“闲置”以求简明),直到发生任何事件为止。[0084]为了更好的理解,该方法可以用图3所示的工作流程来说明,但是本发明不限于此。根据某些实施例,可以在图3所示的工作流程中增加、删除或修改一或多个步骤。例如,将存储装置100保持闲置的状态可以被认为是存储装置100的一闲置状态,并且存储装置100(例如,存储器控制器110)可以因应该任何事件而离开该闲置状态,并且进行对应于该任何事件的相关处理。该任何事件的示例可以包含(但不限于):该功率/速度模式改变,以及从主机装置50接收到的任何主机命令,诸如一写入命令、一读取命令等。存储器控制器110可以因应来自主机装置50的一主机命令诸如该写入命令,为主机装置50将数据储存至非挥发性存储器120中,并且在完成对应于该写入命令的上列处理(例如:将该数据储存至非挥发性存储器120的操作)以后,控制存储装置100再次进入该闲置状态。存储器控制器110可以因应来自主机装置50的另一主机命令诸如该读取命令,从非挥发性存储器120读取储存的数据,并且向主机装置50提供从非挥发性存储器120读取的上述储存的数据,以及在完成对应于该读取命令的上列处理(例如:从非挥发性存储器120读取该储存的数据以及向主机装置50提供上述储存的数据的操作)以后,控制存储装置100再次进入该闲置状态。[0085]图4是依据本发明一实施例所绘示的针对图3所示的工作流程中的某些操作(例如,步骤s13~s15、s16a和s16b的操作)的某些实施细节的示意图。除了修整启用参数trim_enable和计数极限count_limit以外,用于控制修整控制电路118t的上述控制参数还可以包含:[0086](1)一参考时钟选择参数refclk_sel,用于选择该多个预定频率的其中之一作为参考时钟refclk的频率;[0087](2)一齿轮(gear)速度gear_speed,用于选择多个速度模式(例如,多种高速(highspeed,简称hs)齿轮,诸如hs齿轮1、hs齿轮2、hs齿轮3和hs齿轮4,可以分别称为hs-gear1、hs-gear2、hs-gear3和hs-gear4以求简明)的其中之一;[0088](3)一组电压步长(voltagestep)vstep[ref,ctrl],诸如vstep[ref]和vstep[ctrl],分别用于被利用作为一增量或一减量以供调整电压参考参数vref和电压控制参数vctrl;[0089](4)一计数差阈值(countdifferencethreshold)th_diff,例如,一阈值,其用于判定是否将电压参考参数vref和电压控制参数vctrl的各自的调整步长(adjustmentstep)设定为微小步长诸如一、或较大的步长诸如这一组电压步长vstep[ref,ctrl];[0090](5)上述超时计数timeout_count;以及[0091](6)上述最大计数差count_diff_max;[0092]其中,用于控制修整控制电路118t的上述控制参数可以由运行着程序码112c的微处理器112来判定(标示为“fw控制”以便有更好的理解),但是本发明不限于此。[0093]在步骤s14的操作中,修整控制电路118t可以利用参考时钟计数器rcnt对参考时钟refclk的一循环计数域(cyclecountdomain)中的循环计数rcount进行计数(标示为“r计数器refclk域”以求简明),以判定该修剪超时条件是否被满足。当该修整超时条件被满足时(例如,超时的情况),在步骤s15的操作中,修整控制电路118t可以利用tx位元时钟计数器tcnt对该tx位元时钟的一循环计数域中的循环计数tcount进行计数(标示为“t计数器tx位元时钟域”以求简明),以判定pll118l的该优化是否完成。举例来说,在count_diff_max=2的情况下,修整控制电路118t可以根据计数差count_diff是否等于{0,1,2}中的任何一个,来判定循环计数tcount是否落入(例如,命中)该预定范围诸如区间[count_limit-2,count_limit 2]的范围。如果是,则进入步骤s16a以将电压参考参数vref和电压控制参数vctrl的各自的结果值vref[result]和vctrl[result]回传给微处理器112(标示为“回传vref及vctrl”以求简明);如果否,则进入步骤s16b以进行电压参数调整,例如,藉由图4上半部所示的操作。[0094]如果计数差count_diff小于或等于计数差阈值th_diff,则修整控制电路118t可以将电压参考参数vref和电压控制参数vctrl的各自的调整步长{adjust}设定为上述微小步长诸如一(标示为“adjust=1”以求简明);否则,修整控制电路118t可以将电压参考参数vref和电压控制参数vctrl的各自的调整步长{adjust}设定为上述较大的步长诸如上述这一组电压步长vstep[ref,ctrl](标示为“adjust=vstep[ref,ctrl]”以求简明)。如图4的左上方所示,修整控制电路118t可以根据循环计数tcount是否小于计数极限count_limit,来判定电压参考参数vref和电压控制参数vctrl的各自的调整步长{adjust}在该电压参数调整的期间是否应该被用来作一增量或一减量。举例来说,如果循环计数tcount小于计数极限count_limit,则修整控制电路118t可以判定应将电压参考参数vref和电压控制参数vctrl的各自的调整步长{adjust}用来作为一增量,且因此调整电压参考参数vref和电压控制参数vctr,例如,藉由用其各自的调整步长{adjust}来增加它们(标示为“ ”以求简明);否则,修整控制电路118t可以判定应将电压参考参数vref和电压控制参数vctrl的各自的调整步长{adjust}用来作为一减量,且因此调整电压参考参数vref和电压控制参数vctr,例如,藉由用其各自的调整步长{adjust}来减少它们(标示为“‑”以求简明)。于是,修整控制电路118t可以调整vco118v(尤其,藉由调整电压参考参数vref和电压控制参数vctrl来调整vco118v的控制电压,从而调整vco118v的频率),并且依据下列方程序来重新修整(retrim)pll118l(标示为“调整vco及重新修整”以求简明):[0095]vref_next=vref_cur /-adjust;以及[0096]vctrl_next=vctrl_cur /-adjust;[0097]其中adjust=1或vstep。在上列方程序中,“vref_cur”和“ref_next”可以分别代表电压参考参数vref的当前值和下一个值,并且“vctrl_cur”和“vctrl_next”可以分别代表电压控制参数vctrl的当前值和下一个值。举例来说,修整控制电路118t可以设定adjust=1(例如,将电压参考参数vref和电压控制参数vctrl的各自的调整步长{adjust}设定为上述微小步长诸如一),且因此上列的方程序可以重新整理改写如下:[0098]vref_next=vref_cur /-1;以及[0099]vctrl_next=vctrl_cur /-1。[0100]对于另一示例,修整控制电路118t可以设定adjust=vstep(例如,分别将电压参考参数vref和电压控制参数vctrl的各自的调整步长{adjust}设定为上述较大的步长诸如上述这一组电压步长vstep[ref,ctrl]),且因此上列的方程序可以重新整理改写如下:[0101]vref_next=vref_cur /-vstep[ref];以及[0102]vctrl_next=vctrl_cur /-vstep[ctrl]。[0103]另外,计数差阈值th_diff典型地大于最大计数差count_diff_max,以容许修整控制电路118t根据“count_diff≤th_diff”是否为真(true)来选择“adjust=1”的设定和“adjust=vstep[ref,ctrl]”的设定的其中之一,如图4所示。[0104]由于计数差阈值th_diff可以被视为计数差count_diff的阈值,且由于修整控制电路118t可以计算循环计数tcount与计数极限count_limit之间的差(tcount-count_limit)的绝对值|tcount-count_limit|以作为计数差count_diff,所以计数差阈值th_diff可以是一非负整数,尤其,可以是正整数。举例来说,当count_diff_max=2时,计数差阈值th_diff大于最大计数差count_diff_max诸如2,且因此可以大于或等于3。为了更好地理解,假定th_diff=3。在这个情况下,根据“count_diff≤th_diff”诸如“count_diff≤3”是否为真,修整控制电路118t可以设定adjust=1或adjust=vstep[ref,ctrl]。举例来说,当count_diff=3(例如“count_diff≤3”为真)时,修整控制电路118t可以设定adjust=1。在某些示例中,当count_diff等于4、5等(例如“count_diff≤3”为假(false))时,修整控制电路118t可以设定adjust=vstep[ref,ctrl]。[0105]表1[0106]参考时钟19.2mhz38.4mhz26mhz52mhz超时计数192260384520[0107]表2[0108][0109]表1展示了相对于参考时钟refclk的频率(例如:19.2mhz、38.4mhz、26mhz和52mhz)的超时计数timeout_count的某些示例,而表2展示了相对于参考时钟refclk的速率(例如:速率a系列和速率b系列)以及齿轮速度gear_speed(例如:hs-gear1、hs-gear2、hs-gear3和hs-gear4)的计数极限count_limit的某些示例,但是本发明不限于此。根据某些实施例,表1的超时计数timeout_count、及/或表2的计数极限count_limit可予以变化。根据某些实施例,测量周期可以等于10微秒(microsecond)。[0110]表3[0111][0112][0113]表3展示了hs突发速率(hs-burstrate)的例子。根据相关标准,对应于hs齿轮的hs突发速率可以从1.46gbps(例如,齿轮1)分布到11.6gbps(例如,齿轮4)。[0114]图5绘示了该方法所涉及的pll118l的示例,但是本发明不限于此。除了vco118v和上述分频器诸如分频器118d(标示为“div”以求简明)以外,pll118l还可包含一相位检测器pd和一低通滤波器(lowpassfilter,简称lpf)118f。vco118v可以被配置为接收一组电压参数,诸如电压参考参数vref和电压控制参数vctrl,并且根据该组电压参数微调vco118v的该控制电压,以使vco118v的输出端子上的该振荡器输出的频率对应于该控制电压。该振荡器输出可由分频器118d接收,并且被发送到相位检测器pd的一输入端子以作为pll118l内的一反馈信号。相位检测器pd可以对该振荡器输出和参考时钟refclk进行相位检测,以在其输出端子产生一相位检测信号。lpf118f可以对该相位检测信号进行低通滤波以产生一滤波后的结果,以供被输入到vco118v中。[0115]基于图1所示的架构,存储器控制器110可以根据该方法正确且有效地操作,以容许主机装置50和存储装置100之间的连接的数据速率在保持数据存取的正确性的同时达到高数据速率诸如10gbps或更高的数据速率,且因此提升了电子装置10的整体效能。依据某些实施例,修整控制电路118t可对pll118l进行该修整控制,以支持使用该vcxo的pll118l的该优化,其中,pll118l的该优化可以包含pll118l的该参数调整(例如,针对该组电压参数诸如电压参考参数vref和电压控制参数vctrl的该电压参数调整)。另外,暂存器电路118r可以储存pll118l的多个参数,并且可以储存pll118l的该参数调整的多个处理结果,其中该多个参数可以包含多个控制参数,诸如修整启用参数trim_enable、计数极限count_limit、参考时钟选择参数refclk_sel、齿轮速度gear_speed、该组电压步长vstep[ref,ctrl](例如:vstep[ref]和vstep[ctrl])、计数差阈值th_diff、超时计数timeout_count和最大计数差count_diff_max,并且该多个处理结果可以包含电压参考参数vref和电压控制参数vctrl的各自的结果值vref[result]和vctrl[result]。[0116]举例来说,存储器控制器110可以利用该处理电路诸如微处理器112来设定该多个控制参数,以控制pll118l的该参数调整;存储器控制器110可利用修整控制电路118t根据该多个控制参数进行pll118l的该参数调整,以调整在该多个参数中的该组电压参数(例如电压参考参数vref和电压控制参数vctrl),以优化vco118v的该控制电压,其中该控制电压对应于该组电压参数,且该vco118v的该振荡频率对应于该控制电压;并且,在pll118l的该参数调整的期间,因应pll118l的该参数调整的至少一预定条件(predeterminedcondition)被满足(例如,步骤s15的判定结果指出tx位元时钟计数器tcnt的循环计数tcount落入该预定范围诸如在计数极限count_limit附近的该目标范围以内),存储器控制器110可以利用修整控制电路118t暂存器电路118r中产生并储存该多个处理结果(例如,电压参考参数vref和电压控制参数vctrl的各自的结果值vref[result]和vctrl[result]),以供被发送回该处理电路诸如微处理器112,以完成pll118l的该参数调整,从而实现存储装置100的该系统上pll管理。为了更好地理解,存储器控制器110可以藉助于针对vco118v的该控制电压的一优化工作流程(例如图3所示的工作流程)来优化该控制电压。举例来说,该优化工作流程的操作可以包含:[0117](1)在步骤s11中,存储器控制器110判定存储装置100是否处于该上电阶段或该适应均衡阶段,以产生一第一判定结果(例如,步骤s11的判定结果“是”和“否”的其中之一);[0118](2)在步骤s12中,因应指出存储装置100是处于该上电阶段或该适应均衡阶段的该第一判定结果,存储器控制器110根据上述至少一预定规则来判定存储装置100是否需要进行pll118l的该参数调整以产生一第二判定结果(例如,步骤s12的判定结果“是”和“否”的其中之一);[0119](3)因应指出需要进行pll118l的该参数进行调整的该第二判定结果,存储器控制器110在步骤s13中使用该多个控制参数中的修整启用参数trim_enable触发pll118l的该参数调整,尤其,利用修整控制电路118t在包含步骤s13-s15和s16b的回圈中进行pll118l的该参数调整;[0120](4)在步骤s16a中,存储器控制器110利用修整控制电路118t在暂存器电路118r中产生并储存该多个处理结果(例如,电压参考参数vref和电压控制参数vctrl的各自的结果值vref[result]和vctrl[result]),以供被发送回该处理电路诸如微处理器112,以完成pll118l的该参数调整;以及[0121](5)在步骤s17中,在完成pll118l的该参数调整以后,存储器控制器110控制存储装置100进入存储装置100的该闲置状态并保持在该闲置状态中,直到发生该任何事件为止;[0122]其中该任何事件可以代表多个预定事件的其中之一,并且该多个预定事件可以包含该速度模式改变以及从主机装置50接收的该任何主机命令。[0123]存储器控制器110可以进行该系统上pll管理,而不需要使用位于存储装置100外部的任何设施或仪器来校准使用该vcxo的pll118l,其中,存储器控制器110可以藉由进行该系统上pll管理来最佳化该控制电压,而不是藉由在存储装置100的一制造阶段的期间经历任何校准来最佳化该控制电压。此外,存储器控制器110可以间歇地(intermittently)进行pll118l的该参数调整并且因应主机装置50的一或多个主机命令(例如,该任何主机命令,诸如该写入命令、该读取命令等)存取非挥发性存储器120,尤其,可以进行下列操作的至少一部分(例如,一部分或全部):[0124](1)操作#1:当在步骤s11中判定存储装置100是处于该上电阶段时,触发pll118l的该参数调整,例如,藉由在步骤s12中设定修整启用参数trim_enable以进入步骤s13;[0125](2)操作#2:当在步骤s11中判定存储装置100是处于该适应均衡阶段时,触发pll118l的该参数调整,例如,藉由在步骤s12中设定修整启用参数trim_enable以进入步骤s13;[0126](3)操作#3:当从主机装置50接收到该写入命令时,存取非挥发性存储器120,例如,藉由将该写入命令所载有的数据写入至非挥发性存储器120中;以及[0127](4)操作#4:当从主机装置50接收到该读取命令时,存取非挥发性存储器120,例如,藉由从非挥发性存储器120读取上述储存的数据并且向主机装置50提供这个数据;其中,操作#2、#3和#4的任何操作可以进行一次或多次,并且可以因应操作#2、#3和#4的各自的触发事件以任何顺序进行操作#2、#3和#4。举例来说,当有需要时(例如,从步骤s11到步骤s12的局部工作流程以及从步骤s12到步骤s13的局部工作流程),存储器控制器110可以进行pll118l的该参数调整(例如,步骤s13-s15和s16b的回圈中的局部工作流程)。为了简明起见,于本实施例中类似的内容在此不重复赘述。[0128]以上所述仅为本发明的较佳实施例,凡依本发明申请专利范围所做的均等变化与修饰,皆应属本发明的涵盖范围。当前第1页12当前第1页12

再多了解一些

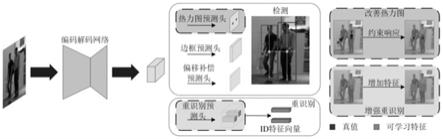

本文用于企业家、创业者技术爱好者查询,结果仅供参考。