1.本公开涉及显示装置,更具体而言,涉及去除绝缘膜的一部分来最小化释气的产生的显示装置。

背景技术:

2.显示装置包括具备显示元件的多个像素,在各像素中配置有多个布线以及与各布线连接且用于驱动显示装置的至少一个晶体管。

3.晶体管可以与显示元件电连接而利用从各布线施加的信号来驱动显示元件。

4.多个布线可以位于彼此不同的层而被绝缘。此时,各布线之间的绝缘层可以包括有机膜。

技术实现要素:

5.各实施例用于提供去除绝缘膜的一部分来最小化释气的产生的显示装置。

6.本发明的一实施例涉及的显示装置包括:基板;多个第一布线,沿着第一方向位于所述基板;第一绝缘膜,位于所述多个第一布线上;多个第二布线,沿着与所述第一方向交叉的第二方向位于所述第一绝缘膜上;第二绝缘膜,位于所述多个第二布线上;以及多个像素电极,位于所述第二绝缘膜上,在沿着所述第一方向与所述基板的面垂直地截取的截面,在所述多个像素电极之间彼此间隔开来不连续地设置所述第二绝缘膜。

7.可以是,在垂直于所述基板的面的方向上与所述多个像素电极重叠地设置所述多个第二布线,所述第二绝缘膜的隔开区域在所述第一方向上位于彼此相邻的所述多个像素电极之间。

8.可以是,所述多个像素电极包括位于所述第二方向上的第一列的第一像素电极和第二像素电极以及位于所述第二方向上的第二列的第三像素电极,所述第二绝缘膜的隔开区域位于所述第一列与所述第二列之间。

9.可以是,与所述多个第一布线重叠地设置所述第一绝缘膜,在沿着所述第二方向与所述基板的面垂直地截取的虚拟截面,在沿着所述第二方向彼此相邻的所述多个第一布线之间间隔开来不连续地设置所述第一绝缘膜。

10.可以是,沿着所述第一方向以连续的线形设置所述第一绝缘膜。

11.可以是,所述第一绝缘膜在与所述第二绝缘膜的隔开区域重叠的区域被间隔开。

12.可以是,沿着所述第一方向以彼此间隔开的多个岛形设置所述第一绝缘膜。

13.可以是,所述显示装置还包括:保护膜,位于所述多个第一布线与所述第一绝缘膜之间。

14.可以是,所述多个第一布线是传递扫描信号的扫描线,所述多个第二布线是传递数据电压的数据线或传递驱动电压的驱动电压线。

15.可以是,所述第一绝缘膜和所述第二绝缘膜的厚度分别是至

16.可以是,所述显示装置还包括:隔壁,位于所述多个像素电极上,所述隔壁具有与

所述多个像素电极重叠的开口,所述隔壁的一部分突出而形成间隔物。

17.可以是,所述隔壁包括黑色物质。

18.可以是,所述第一绝缘膜或所述第二绝缘膜包括黑色物质。

19.可以是,所述第一绝缘膜或所述第二绝缘膜包括硅氧烷。

20.本发明的其他一实施例涉及的显示装置包括:基板;多个第一布线,沿着第一方向位于所述基板;第一绝缘膜,位于所述多个第一布线上;多个第二布线,沿着与所述第一方向交叉的第二方向位于所述第一绝缘膜上;第二绝缘膜,位于所述多个第二布线上;以及多个像素电极,位于所述第二绝缘膜上,在所述第二方向上彼此相邻的所述多个第一布线之间间隔开来不连续地设置所述第一绝缘膜。

21.可以是,在所述第一方向上彼此间隔开来不连续地设置所述第一绝缘膜。

22.可以是,在垂直于所述基板的方向上与所述多个第一布线及所述多个第二布线重叠地设置所述第二绝缘膜。

23.可以是,所述多个第一布线是传递扫描信号的扫描线,所述多个第二布线是传递数据电压的数据线或传递驱动电压的驱动电压线。

24.本发明的其他一实施例涉及的显示装置包括:基板;多个第一布线,沿着第一方向位于所述基板;第一绝缘膜,位于所述多个第一布线上;多个第二布线,沿着与所述第一方向交叉的第二方向位于所述第一绝缘膜上;第二绝缘膜,位于所述多个第二布线上;以及多个像素电极,位于所述第二绝缘膜上,所述第二绝缘膜在所述多个第二布线之间沿着所述第二方向被去除。

25.可以是,在垂直于所述基板的面的方向上与所述多个像素电极重叠地设置所述多个第二布线,所述第二绝缘膜的去除区域位于在所述第一方向上彼此相邻的所述多个像素电极之间。

26.可以是,与所述多个第一布线重叠地设置所述第一绝缘膜,所述第一绝缘膜在沿着所述第二方向彼此相邻的所述多个第一布线之间在所述第一方向上被去除。

27.可以是,沿着所述第一方向以连续的线形设置所述第一绝缘膜。

28.可以是,所述第一绝缘膜在与所述第二绝缘膜的去除区域重叠的区域被去除。

29.可以是,所述多个第一布线是传递扫描信号的扫描线,所述多个第二布线是传递数据电压的数据线或传递驱动电压的驱动电压线。

30.(发明效果)

31.根据各实施例,提供一种去除绝缘膜的一部分来最小化释气的产生的显示装置。

附图说明

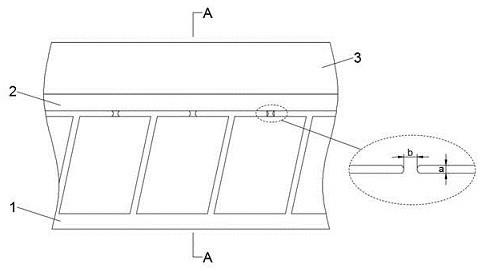

32.图1简单示出本发明的一实施例涉及的显示装置的平面图。

33.图2是沿着图1的ii-ii'线截取示出的剖视图。

34.图3是沿着图1的iii-iii'线截取示出的剖视图。

35.图4在图1的显示区域内分开示出了第二通路所处的区域和被去除的区域。

36.图5对于其他一实施例示出了与图1相同的平面。

37.图6是沿着图5的vi-vi'线截取示出的剖视图。

38.图7是沿着图5的vii-vii'线截取示出的剖视图。

39.图8在图5所示的区域内分开示出了第一通路所处的区域和被去除的区域。

40.图9在图5所示的区域内分开示出了第二通路所处的区域和被去除的区域。

41.图10对于其他一实施例示出了与图1相同的平面。

42.图11是沿着图10的xi-xi'线截取示出的剖视图。

43.图12是沿着图10的xii-xii'线截取示出的剖视图。

44.图13在图10所示的区域内分开示出了第一通路所处的区域和被去除的区域。

45.图14在图10所示的区域内分开示出了第二通路所处的区域和被去除的区域。

46.图15对于其他一实施例示出了与图5相同的平面。

47.图16是沿着图15的xvi-xvi'线截取示出的剖视图,图17是沿着图15的xvii-xvii'线截取示出的剖视图。

48.图18在图15所示的区域内分开示出了第一通路所处的区域和被去除的区域。

49.图19在图15所示的区域内示出了第二通路。

50.图20对于其他一实施例示出了与图10相同的平面。

51.图21是沿着图20的xxi-xxi'线截取示出的剖视图,图22是沿着图20的xxii-xxii'线截取示出的剖视图。

52.图23在图20所示的区域内示出了第一通路所处的区域和被去除的区域。

53.图24在图20所示的区域内示出了第二通路。

54.图25分开示出了显示装置的显示部dia和非显示部nda。

55.图26是沿着图25的xxvi-xxvi'线截取示出的剖视图。

56.图27示出一实施例涉及的显示装置的截面。

57.图28是本发明的一实施例涉及的显示装置的配置图。

58.图29是沿着图28的xxix-xxix'线截取示出的剖视图。

59.图30至图34示出了在图28的显示装置中位于同一层的结构。

60.(符号说明)

61.sub:基板;via1;第一通路;via2:第二通路;act:半导体层;191:像素电极;270:公共电极;de1:第一数据导电层;de2:第二数据导电层;pvx:保护膜;350:隔壁。

具体实施方式

62.以下,参照附图,详细说明本发明的各实施例,以便本领域技术人员能够容易实施。本发明可以由各种不同的形态实现,并不限于在此说明的各实施例。

63.为了明确说明本发明,省略了与说明无关的部分,并在整个说明书中对相同或者类似的构成要素赋予相同的符号。

64.此外,图示的各构成的大小以及厚度为了便于说明而任意示出,本发明并不一定限于图示的情况。在附图中,为了明确表示各层以及区域,有所夸张地示出了厚度。此外,在附图中,为了便于说明,有所夸张地示出了部分层和区域的厚度。

65.此外,层、膜、区域、板等部分位于其他部分上或上方时,不仅包括直接位于其他部分上的情况,还包括其间具有其他部分的情况。相反,某一部分直接位于其他部分上时,是指其间不存在其他部分。此外,位于作为基准的部分上或上方是指位于作为基准的部分的上或下,并不一定指在重力方向侧位于上或上方的情况。

66.此外,在整个说明书中,某一部分包括某一构成要素时,在没有特别相反的记载的情况下,并不是排除包括其他构成要素,而是指还可以包括其他构成要素。

67.此外,在整个说明书中,“平面上”是指从上观察对象部分的情况,“截面上”是指从侧方观察垂直截取对象部分的截面的情况。

68.以下,参照附图,详细说明本发明的一实施例涉及的显示装置。

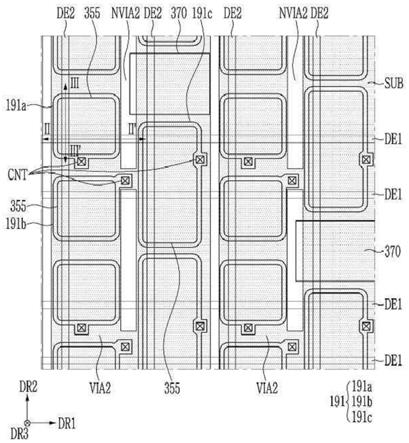

69.图1简单示出了本发明的一实施例涉及的显示装置的平面图。图2是沿着图1的ii-ii'线截取示出的剖视图。图3是沿着图1的iii-iii'线截取示出的剖视图。图1为了说明发明的核心特征而仅示出了部分构成要素,图2至图3也是用于说明发明的主要特征的虚拟截面,并不一定与图1的截面线准确地一致。

70.参照图1,像素电极191位于基板sub。像素电极191可以包括第一像素电极191a、第二像素电极191b以及第三像素电极191c。各第一像素电极191a、第二像素电极191b和第三像素电极191c的一部分可以突出而与接触部cnt连接。第一像素电极191a、第二像素电极191b和第三像素电极191c分别可以从接触部cnt接收电压的供给。接触部cnt可以与晶体管(未图示)连接。第一像素电极191a和第二像素电极191b在第二方向dr2上可以位于同一列,第三像素电极191c可以位于与第一像素电极191a及第二像素电极191b不同的列。第三像素电极191c可以位于与间隔物370相同的列。

71.隔壁(图1中未示出)位于第一像素电极191a、第二像素电极191b和第三像素电极191c上,隔壁可以具有分别与第一像素电极191a、第二像素电极191b及第三像素电极191c重叠的开口355。隔壁的一部分可以突出而构成间隔物370。

72.与第一像素电极191a对应的像素可以发出红色的光,与第二像素电极191b对应的像素可以发出绿色的光,并且与第三像素电极191c对应的像素可以发出蓝色的光。

73.再次参照图1,本实施例涉及的显示装置可以包括沿着第一方向dr1设置的第一数据导电层de1以及沿着与第一方向dr1交叉的第二方向dr2设置的第二数据导电层de2。为了便于说明,对于一个像素电极191a、191b、191c分别仅示出了一个第一数据导电层de1和第二数据导电层de2,但是实际上,第一数据导电层de1和第二数据导电层de2可以有多个位于一个像素电极191a、191b、191c的下部。第一数据导电层de1可以是传递扫描信号的扫描线。此外,第二数据导电层de2可以是传递数据电压的数据线或传递驱动电压的驱动电压线。

74.参照图1,在与基板sub垂直的第三方向dr3上与各像素电极191a、191b、191c重叠地设置第二数据导电层de2。即,与第一像素电极191a、第二像素电极191b及第三像素电极191c重叠地设置第二数据导电层de2,且第二数据导电层de2不位于各像素电极191a、191b、191c之间的区域。

75.在各像素电极191a、191b、191c之间的区域,沿着第二方向dr2,在列方向上去除了第二通路(via)via2。在图1中分开示出了第二通路via2所处的区域和被去除的区域nvia2。第二通路via2所处的区域用阴影进行了表示,第二通路via2被去除的区域nvia2被表示成无图案。

76.第二通路via2被去除的区域nvia2是位于各像素电极191a、191b、191c之间的区域,是不设置第二数据导电层de2的区域。但是,第二通路via2在接触部cnt上不被去除。

77.即,在本实施例涉及的显示装置中,在垂直于基板sub的方向上与像素电极191a、191b、191c重叠地设置第二数据导电层de2,且第二数据导电层de2不位于像素电极191a、

191b、191c之间的区域。因此,在像素电极191a、191b、191c之间的区域可以去除位于第二数据导电层de2上的第二通路via2。因此,可以最小化由第二通路via2引起的释气的产生以及由此引起的收缩(shrink)现象,可以提高显示装置的可靠性。

78.图2是沿着图1的ii-ii'线截取示出的剖视图。图3是沿着图1的iii-iii'线截取示出的剖视图。但是,图2是在图1的第一方向dr1上的截面并且图3是在图1的第二方向dr2上的截面上为了表示第二通路via2和第一通路via1的形态而示意性示出的,相应结构可以不与截面线准确地一致。即,图2和图3为了便于说明,以显示装置的像素的核心结构为中心进行说明,图1所示的截面线和图2及图3所示的截面可以不是准确一致的。具体的平面图和剖视图等后续利用单独的图进行说明。

79.同时参照图2和图3,阻挡层ba可以位于基板sub上。阻挡层ba可以包括无机物质,作为一例,可以包括氮化硅(sin

x

)、氧化硅(sio

x

)、氮氧化硅(sio

x

ny)等无机绝缘物质。此时,所述的x和y分别可以是1至10。阻挡层ba可以是所述物质的单层或多层结构。

80.缓冲层buf可以位于阻挡层ba上。缓冲层buf可以包括氮化硅(sin

x

)、氧化硅(sio

x

)、氮氧化硅(sio

x

ny)等无机绝缘物质。缓冲层buf可以是所述物质的单层或多层结构。

81.半导体层act可以位于缓冲层buf上。半导体层act可以包括非晶硅、多晶硅和氧化物半导体中的任一种。作为一例,半导体层act可以包括低温多晶硅(ltps)或者包括含有锌(zn)、铟(in)、镓(ga)、锡(sn)和它们的混合物中的至少一种的氧化物半导体物质。作为一例,半导体层act可以包括igzo(indium-gallium-zinc oxide,铟镓锌氧化物)。

82.半导体层act可以包括源极区域sa、漏极区域da以及源极区域sa与漏极区域da之间的沟道区域ca。

83.第一栅极绝缘膜gi_1可以位于半导体层act上。第一栅极绝缘膜gi_1可以包括氮化硅(sin

x

)、氧化硅(sio

x

)、氮氧化硅(sio

x

ny)等无机绝缘物质。第一栅极绝缘膜gi_1可以是所述物质的单层或多层结构。第一栅电极gat_1可以位于第一栅极绝缘膜gi_1上。可以在垂直于基板sub的方向上与半导体层act的沟道区域ca重叠地设置第一栅电极gat_1。第一栅电极gat_1可以包括钼(mo)、铝(al)、铜(cu)和/或钛(ti),可以是所述物质的单层或多层结构。

84.接着,第二栅极绝缘膜gi_2可以位于第一栅电极gat_1上。第二栅极绝缘膜gi_2可以包括氮化硅(sin

x

)、氧化硅(sio

x

)、氮氧化硅(sio

x

ny)等无机绝缘物质。

85.第二栅电极gat_2可以位于第二栅极绝缘膜gi_2上。可以与第一栅电极gat_1重叠地设置第二栅电极gat_2,并且在第二栅电极gat_2与第一栅电极gat_1之间夹着第二栅极绝缘膜gi_2。第二栅电极gat_2可以包括钼(mo)、铝(al)、铜(cu)和/或钛(ti),可以是所述物质的单层或多层结构。

86.在其间夹着第二栅极绝缘膜gi_2而彼此重叠的第一栅电极gat_1和第二栅电极gat_2可以构成电容器。

87.层间绝缘膜ild可以位于第二栅电极gat_2上。层间绝缘膜ild可以包括氮化硅(sin

x

)、氧化硅(sio

x

)、氮氧化硅(sio

x

ny)等无机绝缘物质。

88.第一数据导电层de1可以位于层间绝缘膜ild上。第一数据导电层de1可以包括铝(al)、铂(pt)、钯(pd)、银(ag)、镁(mg)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、镍(ni)、钙(ca)、钼(mo)、钛(ti)、钨(w)和/或铜(cu)等,可以是所述物质的单层或多层结构。第一数据

导电层de1可以包括彼此间隔开的第一源电极s1和第一漏电极d1。第一源电极s1可以通过位于第一栅极绝缘膜gi_1、第二栅极绝缘膜gi_2和层间绝缘膜ild的开口op而与半导体层act的源极区域sa连接。此外,第一漏电极d1可以通过位于第一栅极绝缘膜gi_1、第二栅极绝缘膜gi_2和层间绝缘膜ild的开口op而与半导体层act的漏极区域da连接。

89.在图2和3中,将第一数据导电层de1仅简单示出了第一源电极s1和第一漏电极d1,但是这是为了便于说明而示意性示出的,实际结构可以不同于此。

90.保护膜pvx可以位于第一数据导电层de1上。保护膜pvx可以包括氮化硅(sin

x

)、氧化硅(sio

x

)、氮氧化硅(sio

x

ny)等无机绝缘物质。保护膜pvx可以根据实施例而省略。

91.第一通路via1可以位于保护膜pvx上。第一通路via1可以是有机膜。具体而言,第一通路via1可以包括如聚甲基丙烯酸甲酯(pmma)或聚苯乙烯(ps)这样的一般通用高分子、具有酚基的高分子衍生物、丙烯酸系高分子、酰亚胺系高分子、聚酰亚胺、丙烯酸系聚合物、硅氧烷系聚合物等有机绝缘物质。第一通路via1的厚度可以是至第一通路via1除了开口op外可以位于保护膜pvx的整个面。

92.第二数据导电层de2可以位于第一通路via1上。第二数据导电层de2可以包括传递数据电压的数据线。第二数据导电层de2可以包括铝(al)、铂(pt)、钯(pd)、银(ag)、镁(mg)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、镍(ni)、钙(ca)、钼(mo)、钛(ti)、钨(w)和/或铜(cu)等,可以是所述物质的单层或多层结构。第二数据导电层de2可以通过位于第一通路via1和保护膜pvx的开口op而与第一漏电极d1连接。在图2和图3中简单示出了第二数据导电层de2,但是这是为了便于说明而示意性示出的,实际结构可以不同于此。

93.第二通路via2可以位于第二数据导电层de2上。第二通路via2可以是有机膜。具体而言,第二通路via2可以包括如聚甲基丙烯酸甲酯(pmma)或聚苯乙烯(ps)这样的一般通用高分子、具有酚基的高分子衍生物、丙烯酸系高分子、酰亚胺系高分子、聚酰亚胺、丙烯酸系聚合物、硅氧烷系聚合物等有机绝缘物质。第二通路via2的厚度可以是至

94.同时参照图2和图3,第二通路via2其在第一方向dr1上的两个边缘位置被去除。在图2中用虚线示出了第二通路via2被去除的区域nvia2。但是,参照图3,第二通路via2在第二方向dr2上的边缘位置未被去除,而是被连续设置。

95.即,同时参照图1至图3,在第一像素电极191a及第二像素电极191b所处的第一列与第三像素电极191c及间隔物370所处的第二列之间的区域,第二通路via2在列方向上被去除。通过这样去除第二通路via2,在显示装置中可以减少第二通路via2所占的体积,因此可以防止因第二通路via2的释气引起的显示装置的变形。对于具体的效果将在后续中单独叙述。

96.再次参照图2和图3,第一像素电极191a可以位于第二通路via2上。第一像素电极191a可以通过位于第二通路via2的开口op而与第二数据导电层de2连接。

97.隔壁350位于第一像素电极191a上。隔壁350具有与第一像素电极191a重叠的开口355。虽然在图2和图3中未图示,但是隔壁350的一部分可以突出而构成间隔物370。如图1所示,间隔物370可以在第二方向dr2上位于与第三像素电极191c相同的列。

98.发光层360可以位于隔壁350的开口355。公共电极270可以位于隔壁350和发光层

360上。第一像素电极191a、发光层360和公共电极270可以构成发光元件led。

99.图4在图1的显示区域内示出了第二通路via2所处的区域和被去除的区域nvia2。在图4中,用阴影示出了第二通路via2所处的区域。

100.参照图1至图4,在本实施例涉及的显示装置中,第二数据导电层de2在垂直于基板sub的方向上与像素电极191a、191b、191c重叠,并且第二数据导电层de2不位于相邻的像素电极191a、191b、191c之间的空间中。此时,在未设置第二数据导电层de2的像素电极191a、191b、191c之间的空间中,第二通路via2在第二方向dr2上被去除,从而可以防止因第二通路via2的释气引起的显示装置的变形。

101.图5对于其他一实施例示出了与图1相同的平面。图6是沿着图5的vi-vi'线截取示出的剖视图,图7是沿着图5的vii-vii'线截取示出的剖视图。图5为了说明发明的核心特征而仅示出了部分构成要素,图6至图7也是用于说明发明的主要特征的虚拟截面,不一定与图5的截面线准确地一致。

102.参照图5,图5的实施例的情况下,除了第一通路via1的一部分沿着第一方向dr1被去除以外,与图1的实施例相同。省略对相同的构成要素的具体说明。

103.图5中,第一通路via1所处的区域是在垂直于基板sub的第三方向dr3上与第一数据导电层de1重叠的区域。即,第一通路via1沿着第一数据导电层de1位于第一方向dr1上,在其余的区域中被去除。第一通路via1被去除的区域nvia1也沿着第一数据导电层de1位于第一方向dr1上。

104.参照图6,在第一方向dr1上的截面中,第一数据导电层de1所处的区域的第一通路via1被设置成未被去除。图6是为了便于说明的虚拟截面,示出了第一数据导电层de1不连续的构成,但是第一数据导电层de1可以如图5所示那样在第一通路via1所处的区域内被连续设置。

105.参照图7,在第二方向dr2上的截面中,第一通路via1的一部分被去除。在图7中,用虚线示出了第一通路via1被去除的区域nvia1。即,参照图5和图7,第二通路via2沿着第二方向dr2被连续设置,但是第一通路via1仅部分位于与第一数据导电层de1重叠的区域,在其余区域中第一通路via1被去除。

106.图8在图5所示的区域内示出了第一通路via1所处的区域和被去除的区域。在图8中,用斜线示出了第一通路via1所处的区域。第一通路via1被去除的区域nvia1被示为无图案。

107.同样地,图9在图5所示的区域内示出了第二通路via2所处的区域和被去除的区域。在图9中,用斜线示出了第二通路via2所处的区域。在图9中,第二通路via2被去除的区域nvia2被示为无图案。

108.同时参照图5、图8和图9,第二通路via2在像素电极191a、191b、191c之间沿着第二方向dr2在列方向上被去除,第一通路via1沿着第一方向dr1在行方向上被去除。在第一方向dr1上与第一数据导电层de1重叠地设置第一通路via1,且在其余区域第一通路via1被去除。

109.因此,在整个显示装置的结构内,第一通路via1和第二通路via2所占的面积减少,由此可以防止因第一通路via1和第二通路via2的释气引起的显示装置的变形。

110.图10对于其他一实施例示出了与图1相同的平面。图11是沿着图10的xi-xi'线截

取示出的剖视图,图12是沿着图10的xii-xii'线截取示出的剖视图。图10为了说明发明的核心特征而仅示出了部分构成要素,图11至图12也是用于说明发明的主要特征的虚拟截面,不一定与图10的截面线准确地一致。

111.参照图10,图10的实施例的情况下,除了第一通路via1的一部分沿着第一方向dr1被去除并且在与第二通路via2被去除的区域重叠的区域中第一通路via1也被去除以外,与图5的实施例相同。省略对相同的构成要素的具体说明。

112.即,参照图10,在第二方向dr2上与第二通路via2被去除的列重叠的部分的第一通路via1也被去除。因此,如图10所示,以彼此分离的多个岛形设置第一通路via1。这是与在图5的实施例中沿着第一方向dr1以线形设置第一通路via1的结构的区别点。

113.参照图11,在第一方向dr1上的截面中,第一通路via1和第二通路via2在第一像素电极191a的两侧被去除。这是与作为其他实施例的图6中在第一方向dr1上连续地设置第一通路via1的结构的区别点。在图11中,用虚线示出了第一通路via1被去除的区域nvia1和第二通路via2被去除的区域nvia2。

114.参照图12,在第二方向dr2上的截面中,第一通路via1的一部分被去除。在图12中,用虚线示出了第一通路via1被去除的区域nvia1。

115.即,参照图10至图12,第二通路via2的情况下沿着第二方向dr2被连续设置,但是第一通路via1的情况下仅部分位于与第一数据导电层de1重叠的区域。

116.图13在图10所示的区域内示出了第一通路via1所处的区域和被去除的区域。在图13中,用斜线示出了第一通路via1所处的区域。第一通路via1被去除的区域nvia1被示为无图案。

117.同样地,图14在图10所示的区域内示出了第二通路via2所处的区域和被去除的区域。在图14中,用阴影示出了第二通路via2所处的区域。第二通路via2被去除的区域nvia2被示为无图案。

118.同时参照图10、图13和图14,第二通路via2在像素电极191a、191b、191c之间沿着第二方向dr2在列方向上被去除,第一通路via1沿着第一方向dr1在行方向上被去除。在第二通路via2沿着列方向被去除的部分,第一通路via1也被去除。即,如图13所示,第一通路via1可以是沿着第一方向dr1彼此间隔开的区域所处的岛形。

119.本实施例的情况下,在整个显示装置结构内,第一通路via1和第二通路via2所占的面积可以减少,因此可以防止因第一通路via1和第二通路via2的释气引起的显示装置的变形。

120.图15对于其他一实施例示出了与图5相同的平面。图16是沿着图15的xvi-xvi'线截取示出的剖视图,图17是沿着图5的xvii-xvii'线截取示出的剖视图。图15为了说明发明的核心特征而仅示出部分构成要素,图16和图17也是用于说明发明的主要特征的虚拟截面,不一定与图15的截面线准确地一致。

121.参照图15,图15的实施例的情况下,除了未去除第二通路via2以外,与图5的实施例相同。省略对于相同的构成要素的具体说明。

122.同时参照图16和图17,第一通路via1可以仅位于第一数据导电层de1所处的区域中,且在其余区域第一通路via1被去除,但是第二通路via2可以被设置成在整个区域未被去除。

123.图18在图15所示的区域内示出了第一通路via1所处的区域和被去除的区域。在图18中,用斜线示出了第一通路via1所处的区域。第一通路via1被去除的区域nvia1被示为无图案。

124.同样地,图19在图15所示的区域内示出了第二通路via2。第二通路via2未被去除,位于整个区域。

125.图20对于其他一实施例示出了与图10相同的平面。图21是沿着图20的xxi-xxi'线截取示出的剖视图,图22是沿着图20的xxii-xxii'线截取示出的剖视图。图20为了说明发明的核心特征而仅示出了部分构成要素,图21至图22也是用于说明发明的主要特征的虚拟截面,不一定与图20的截面线准确地一致。

126.参照图20,图20的实施例的情况下,除了第二通路via2未被去除以外,与图10的实施例相同。省略对于相同的构成要素的具体说明。

127.同时参照图21和图22,第一通路via1仅部分位于第一数据导电层de1所处的区域中,且在其余区域第一通路via1被去除,但是第二通路via2被设置成在整个区域中未被去除。

128.图23在图20所示的区域内示出了第一通路via1所处的区域和被去除的区域。在图23中,用斜线示出了第一通路via1所处的区域。第一通路via1被去除的区域nvia1被示为无图案。

129.同样地,图24在图20所示的区域内示出了第二通路via2。第二通路via2未被去除,位于整个区域。

130.如上所述,在图15至图19的实施例和图20至图24的实施例中,第一通路via1被部分去除,并且第二通路via2未被去除。即使在这种实施例的情况下,如在前的实施例那样,通路在显示装置内所占的体积也会减少,可以防止因释气引起的显示装置的变形。

131.图1至图24的情况下,说明了在显示装置的显示部内的像素中去除了第一通路via1或第二通路via2的实施例。但是,在显示装置中的不显示图像的虚设像素区域以及驱动部等所处的非显示部内也可以去除第一通路via1和第二通路via2。

132.图25分开示出了显示装置的显示部dia和非显示部nda。图26是沿着图25的xxvi-xxvi'线截取示出的剖视图。

133.参照图25,驱动部dr位于非显示部nda,驱动部dr和显示部dia通过多个布线wr被连接。

134.参照图26,多个布线wr可以包括第一数据导电层de1和第二数据导电层de2,第一通路via1可以位于多个布线wr之间。即,与之前说明的显示部dia的层叠结构类似地,可以包括基板sub、阻挡层ba、缓冲层buf、第一栅极绝缘膜gi_1、第二栅极绝缘膜gi_2以及层间绝缘膜ild。省略对于相同的构成要素的具体说明。非显示部nda的第一数据导电层de1可以与显示部dia的第一数据导电层de1连接。

135.保护膜pvx可以位于第一数据导电层de1上。保护膜pvx可以根据实施例而被省略。

136.第一通路via1可以位于保护膜pvx上。如图26所示,第一通路via1可以在未设置第一数据导电层de1的区域中被去除(nvia1)。

137.第二数据导电层de2可以位于第一通路via1上。非显示部nda的第二数据导电层de2可以与显示部dia的第二数据导电层de2连接。

138.第二通路via2位于第二数据导电层de2上。在图26中示出了第二通路via2未被去除的构成,但是根据实施例,第二通路via2也可以在不与第二数据导电层de2重叠的区域中被去除。

139.即,除了显示装置的显示部dia外,在非显示部nda也可以去除第一通路via1和第二通路via2。

140.以下,参照图27,在本发明的各种实施例中详细说明第一通路via1和第二通路via2的物质、厚度、隔壁350的物质等。

141.图27示出一实施例涉及的显示装置的截面。

142.在图27中说明的对于第一通路via1和第二通路via2的内容都可以适用于之前说明的图1至图26的实施例中。

143.在一实施例中,第一通路via1和第二通路via2的厚度分别可以是至这是可以最小化在第一通路via1和第二通路via2中产生的释气的量的数值范围。当第一通路via1和第二通路via2的厚度在以上的情况下,可能会产生很多释气,并且当第一通路via1和第二通路via2的厚度在以下的情况下,各通路可能无法具有足够的平坦化的特性。

144.第一通路via1和第二通路via2所包括的光敏剂(pac)可以因光而被分解的同时产生释气。在通过光致抗蚀剂(pr)工序形成第一通路via1和第二通路via2时光敏剂(pac)是必备的物质,但是第一通路via1和第二通路via2所包括的光敏剂(pac)可能会因外部光而被分解的同时产生释气。

145.这种释气会引发显示装置的收缩变形,可靠性会变差。一实施例涉及的第一通路via1和第二通路via2中,光敏剂(pac)的含量相对于通常的显示装置可以在60%以下。因此,可以最小化释气的产生。

146.此外,第一通路via1和第二通路via2可以包括释气捕获单元(outgas capture unit)。释气捕获单元可以捕获在有机膜内产生的释气。

147.此外,第一通路via1和第二通路via2可以包括硅氧烷系物质。硅氧烷系的有机膜与聚酰亚胺系或丙烯酸系有机膜相比释气的产生量少。因此,可以最小化释气的产生。

148.此外,第一通路via1和第二通路via2中的一个以上可以包括黑色物质。有机膜的释气的产生因光而产生,在第一通路via1或第二通路via2包括黑色物质的情况下可以阻断外部光的入射,可以减少释气的产生量。

149.此外,在一实施例中,隔壁350也可以包括黑色物质。如图27所示,在隔壁350包括黑色物质的情况下,可以阻断外部光向第一通路via1和第二通路via2的流入,可以减少释气的产生。

150.以下,通过具体的配置图和剖视图来详细说明本发明的一实施例涉及的显示装置的结构。但是,下述的结构是一例示,本发明的结构并不限于此。

151.图28是本发明的一实施例涉及的显示装置的配置图。图29是沿着图28的xxix-xxix'线截取示出的剖视图。图30至图34示出了图28的显示装置中位于同一层的结构。

152.同时参照图28和图29,阻挡层ba和缓冲层buf可以依次位于基板sub上。阻挡层ba和缓冲层buf分别可以包括氮化硅(sin

x

)、氧化硅(sio

x

)、氮氧化硅(sio

x

ny)等无机绝缘物质,可以是所述物质的单层或多层结构。

153.接着,同时参照图28、图29和图30,半导体层act可以位于缓冲层buf上。半导体层act可以包括非晶硅、多晶硅和氧化物半导体中的任一种。

154.接着,参照图29,第一栅极绝缘膜gi_1可以位于半导体层act上。

155.接着,同时参照图28、图29和图31,第一栅极导电层ge1可以位于第一栅极绝缘膜gi_1上。第一栅极导电层ge1可以包括第一栅电极1151、第二栅电极1152、栅极图案1153、前级扫描线152、发光控制线153以及辅助发光线158。

156.与第一栅电极1151重叠的半导体层act可以构成第一晶体管t1,与第二栅电极1152重叠的半导体层act可以构成第二晶体管t2和第三晶体管t3。

157.前级扫描线152、发光控制线153和辅助发光线158可以与第一方向dr1并排设置。与前级扫描线152重叠的半导体层act的区域可以构成第四晶体管t4。

158.前级扫描线152可以将施加到位于前级的像素的前级扫描信号传递至第四晶体管t4。

159.与发光控制线153重叠的半导体层act的区域可以构成第五晶体管t5和第六晶体管t6。发光控制线153可以与发光控制部连接,可以将控制发光元件led发光的时间的发光控制信号传递至第五晶体管t5和第六晶体管t6。

160.与辅助发光线158重叠的半导体层act的区域可以构成第七晶体管t7。

161.接着,参照图29,第二栅极绝缘膜gi_2可以位于第一栅极导电层ge1上。

162.接着,参照图32,第二栅极导电层ge2可以位于第二栅极绝缘膜gi_2上。第二栅极导电层ge2可以包括沿着第一方向dr1设置的维持电极线1154、检修线1155、vsus线1156以及设置成岛形的栅极连接电极1157。

163.维持电极线1154可以沿着第一方向dr1设置,并且可以被设置成在垂直于基板sub的第三方向dr3上与第一栅电极1151重叠。维持电极线1154可以包括维持电极开口1154_op。

164.检修线1155可以沿着第一方向dr1设置。vsus线1156也可以与检修线1155并排地沿着第一方向dr1设置。

165.栅极连接电极1157可以与半导体层act的一部分重叠而被设置成岛形。栅极连接电极1157可以与后续形成的第一连接电极ce1形成电容器。

166.再次参照图29,层间绝缘膜ild位于第二栅极导电层ge2上。

167.接着,同时参照图28、图29和图33,第一数据导电层de1可以位于层间绝缘膜ild上。

168.参照图33,第一数据导电层de1可以包括沿着第一方向设置的扫描线151、辅助线159、设置为岛形的第一连接电极ce1、第二连接电极ce2、第三连接电极ce3、第四连接电极ce4、第五连接电极ce5以及第六连接电极ce6。

169.第一扫描线151可以将扫描信号传递至第二晶体管t2和第三晶体管t3。第一扫描线151可以通过第一开口op1与第二栅电极1152连接。

170.可以在垂直于基板sub的第三方向dr3上与栅极连接电极1157重叠地设置第一连接电极ce1。第一连接电极ce1可以通过第三开口op3与半导体层act连接。

171.第二连接电极ce2可以通过第四开口op4与半导体层act连接。

172.第三连接电极ce3可以通过第五开口op5与维持电极线1154连接,并且可以通过第

六开口op6与半导体层act连接。

173.第四连接电极ce4可以通过第七开口op7和第八开口op8分别与半导体层act连接。

174.第五连接电极ce5可以通过第九开口op9而与半导体层act连接,并且可以通过第十开口op10而与vsus线1156连接。

175.第六连接电极ce6可以通过第十一开口op11而与栅极图案1153连接,并且可以通过第十二开口op12而与前级扫描线152连接。

176.接着,参照图29,保护膜pvx可以位于第一数据导电层de1上。保护膜pvx可以根据实施例而被省略。

177.接着,参照图29,第一通路via1可以位于保护膜pvx上。第一通路via1可以是有机膜。

178.接着,同时参照图28、图29和图34,第二数据导电层de2可以位于第一通路via1上。

179.第二数据导电层de2可以包括沿着第二方向dr2设置的数据线171、驱动电压线172、第一初始化电压线173以及数据辅助线174。

180.数据线171可以沿着第二方向dr2设置,并且在数据开口op_171中与第二连接电极ce2连接。第二连接电极ce2可以通过第四开口op4而与半导体层act连接,可以将传递至数据线171的数据电压传递至半导体层act。

181.数据辅助线174可以与数据线171并排地沿着第二方向dr2设置,可以传递数据电压。数据辅助线174可以与数据线171并排设置来减少电阻。

182.驱动电压线172可以通过第一驱动开口op_1721而与第一连接电极ce1连接。

183.此外,驱动电压线172可以通过第二驱动开口op_1722而与辅助线159连接。

184.第一初始化电压线173可以通过第一初始化开口op_173而与半导体层act连接,可以将第一初始化电压传递至半导体层act。虽然未图示,但是在相邻的不同像素中可以设有第二初始化电压线,第二初始化电压线也可以与半导体层act连接而向半导体层act传递第二初始化电压。

185.接着,同时参照图29和图34,第二通路via2位于包括数据线171等的第二数据导电层de2上。第二通路via2可以在未设置第二数据导电层de2的区域中被去除。对于第二通路via2的去除的内容与之前说明的情况相同。

186.接着,参照图28和图29,隔壁350可以位于第二通路via2上,并且像素电极191可以位于隔壁350上。像素电极191可以包括第一像素电极191a、第二像素电极191b和第三像素电极191c,各像素电极191a、191b、191c可以具有突出部195。

187.隔壁350可以具有与突出部195重叠的开口355,在隔壁350的开口355中像素电极191可以与半导体层act等连接而接收用于驱动发光元件led的驱动电压。发光层360可以位于隔壁350的开口355。公共电极270可以位于隔壁350和发光层360上。像素电极191、发光层360和公共电极270可以构成发光元件led。

188.图28至图34详细示出了与图1至图4的实施例相应的构成。但是这只是一例示,图28至图34所示的结构显然也可以适用于图5至图9所示的实施例、图10至图14所示的实施例、图15至图19所示的实施例、图20至图24所示的实施例。

189.以上,详细说明了本发明的实施例,但是本发明的权利范围并不限于此,本领域技术人员利用权利要求书所定义的本发明的基本概念进行的各种变形以及改良形态也属于

本发明的权利范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。