适用于低电压和/或非易失性能的闪存存储器单元

1.相关专利申请

2.本技术要求于2019年6月6日提交的共同拥有的美国临时专利申请号62/858,088的优先权,该专利申请的全部内容以引用方式并入本文以用于所有目的。

技术领域

3.本公开涉及集成电路存储器设备,并且更具体地涉及适用于低电压和/或非易失性能的修改的闪存存储器。

背景技术:

4.微控制器和其他计算机系统可包括任何一种或多种类型的存储器以满足各种目的,诸如目标数据处理速度、数据保留或成本,这取决于预期用户或相应计算机系统的应用。

5.不同类型的存储器在多个不同特性上不同,诸如例如,速度(例如,如由中央处理单元(cpu)访问存储数据所需时间测量的)、数据存储大小、数据保留(例如,易失性或非易失性)、耐久性(例如,在存储器可能变得劣化或不可靠之后的编程/擦除循环的数量)、功率消耗、物理尺寸和成本。

6.易失性存储器是指仅在其保持连接到电源时才存储数据的存储器。易失性存储器的示例包括各种类型的随机存取存储器(ram),诸如静态ram(sram)和动态ram(dram)。非易失性存储器是指即使在从电源断开时也可存储数据的存储器。非易失性存储器的示例性类型包括硬盘驱动器、闪存存储器和eeprom。图1示出了各种类型的常规易失性和非易失性存储器的示例性分类。

7.某些先进的工艺技术系统对于包括在此类系统中的存储器具有严格的设计和性能要求。例如,先进的工艺技术系统通常需要非常紧密的金属间距,并且仅能以最小的设计规则耐受低电压。如本文所用,“金属间距”是指两条相邻金属线之间的距离,包括两条金属线的宽度。此外,一些系统使用铝金属化,通常需要非常低的能量、高度并行的设计和快速的数据传输。

8.现代先进系统通常并入闪存、sram和/或dram存储器设备。常规的闪存存储器单元通常为小(例如,1个晶体管(1t)或1.5个晶体管(1.5))并且提供高数据保留(例如,》10年),但是需要高电压(通常》10v)并且具有缓慢的数据访问时间。例如,通常用于高保留应用的nor闪存存储器(例如,microchip的superflash

tm

esf1、esf3和esf4单元)为小(例如,1.5t),但是对于编程/擦除操作通常需要》7v,并且与dram或sram存储器相比具有缓慢的访问时间。在先进系统中,高电压存储器设备通常增加所需的管芯尺寸,并且可能与最小金属间距的逻辑规则不兼容。

9.相比之下,易失性存储器单元(诸如例如,dram和sram)通常为大并且渴求电力。例如,sram通常为快速并且被设计成在低电压下操作,但是物理上为大(通常6个晶体管(6t))并且具有高功率消耗。

10.表1示出了各种性能和物理尺寸特性,例如存储器设备的类型,包括sram、dram和闪存。如图所示,易失性存储器(诸如sram和dram)比典型的非易失性闪存存储器快得多,消耗更少的每比特能量,并且具有更长的耐久性。

11.表1.选择的存储器类型的比较

[0012][0013][0014]

对于一些系统,需要在低电压域中操作并且与先进、高密度、低能耗的数据计算应用兼容的存储器设备(存储器单元)。

技术实现要素:

[0015]

本发明的实施方案提供具有通常基于闪存存储器单元设计的结构的存储器单元,但是(与常规闪存存储器不同)该存储器单元被配置为在与先进、高密度、低能耗的数据计算应用兼容的低电压域中操作。在一些实施方案或应用中,这些本发明的存储器单元可替换包括在常规设备(例如,微控制器或其他计算机设备)中的ram(例如,sram或dram)的至少一部分。因此,根据本发明实施方案的存储器单元在本文中称为“ram闪存存储器单元”或“ram闪存单元”。

[0016]

如本文所用,“低电压”操作是指施加到单元的电压具有≤6v的绝对值或幅度的存储器单元操作(例如,编程或擦除操作)。例如,在一些实施方案中,ram闪存单元被配置用于使用各自具有≤6v的电压幅度的源极线电压(vsl)、字线电压(vwl)和控制栅电压(vcg)进行编程和擦除操作。如下所述,在一些实施方案中,ram闪存单元被配置用于使用各自具有在3v至6v范围内的电压幅度,或各自具有在1.5v至6v范围内的电压幅度,或各自具有在2v至5v范围内的电压幅度,或各自具有在2v至4v范围内的电压幅度,或各自具有3v或约3v的幅度的源极线电压(vsl)、字线电压(vwl)和控制栅电压(vcg)进行编程和擦除操作。此处列出的所有电压均与地电位或其他公共基准电位相关。

[0017]

如以上背景部分中所述,sram单元通常为快速,但是物理上为大(通常6个晶体管(6t))且具有高功耗。另一方面,dram单元通常使用1t-1c(一个晶体管、一个电容器)架构,并且通常与标准逻辑/微控制器处理流程不兼容。此外,用dram单元,必须例如每64ms执行连续的数据刷新循环,以保持数据存储在单元中。相比之下,如上所述,闪存存储器单元通常为小,例如1t或1.5t。本发明的一些实施方案提供形成为修改的闪存存储器单元的ram闪存单元,该修改的闪存存储器单元被配置为在通常分配给sram或dram的空间中操作。例如,ram闪存单元可被配置用于低电压(≤6v)编程/擦除操作,以在最小或小的金属间距规则下

以高密度先进逻辑流程有效地操作。

[0018]

在一些实施方案中,ram闪存单元可提供灵活、可控的保留-保持方法,以延长数据保留(与传统闪存存储器单元相比),例如延长到周或月的时间范围。在一些实施方案中,存储在ram闪存单元中的数据可周期性地(例如,每一天或多天)从外部nand闪存、hdd或其他数据源恢复。

[0019]

在一些实施方案中,ram闪存单元可集成到与微控制器和/或cpu相同的管芯中,这可提供(a)优于外部dram的总线延迟(数据传输延迟)的优点,和/或(b)与常规dram单元相比低得多的数据刷新频率(例如,每n天或每n个月的刷新速率)的优点(例如,每64ms的刷新速率)。

[0020]

在一些实施方案中,ram闪存单元的结构为常规闪存存储器单元的修改版本,其中至少一个电介质层(例如,氧化物层)与常规闪存存储器单元相比具有减小的厚度。减小的电介质层厚度可允许低电压编程和/或擦除操作,这可允许使用先进低k电介质金属间距,其中最小化或减小泄漏和可靠性问题。

[0021]

在一些实施方案中,ram闪存单元可具有任何已知的闪存存储器单元的基本结构,例如1t闪存存储器单元或分栅闪存存储器单元(例如,微芯片公司(microchip inc.)的1.5t superflash

tm

存储器单元),但是修改的结构具有厚度减小的至少一个电介质层。例如,在根据一些实施方案的1t ram闪存单元中,(a)将浮栅与在下的沟道分开的电介质层和(b)浮栅与重叠的控制栅之间的电介质层中的一者或两者与常规1t闪存存储器单元相比可具有减小的厚度。又如,在根据一些实施方案的1.5t分栅ram闪存单元(例如,形成为修改的superflash

tm

存储器单元的1.5t ram闪存单元)中,(a)将浮栅与在下的沟道分开的浮栅电介质(例如,氧化物)和/或(b)浮栅(侧壁)和相邻控制栅之间的fg控制栅多晶硅层间电介质(例如,多晶硅层间氧化物)层,和/或(c)浮栅(侧壁)和相邻字线之间的fg-字线多晶硅层间电介质(例如,多晶硅层间氧化物)层中的每一者与常规分栅闪存存储器单元的对应层相比可具有减小的厚度。

附图说明

[0022]

下文结合附图描述了本公开的示例方面,其中:

[0023]

图1示出了各种类型的常规易失性和非易失性存储器的示例性分类;

[0024]

图2示出了根据本发明的某些实施方案的包括ram闪存单元的示例性电子设备;

[0025]

图3示出了根据某些示例性实施方案的示例性1t ram闪存单元;

[0026]

图4示出了示例性已知的分栅闪存存储器单元,即superflash

tm

(esf1 )存储器单元;

[0027]

图5示出了根据本发明的一个示例性实施方案的被配置为ram闪存单元的示例性分栅闪存存储器单元;

[0028]

图6是示出根据本发明的一个示例性实施方案的用于确定要施加到图5所示的示例性分栅ram闪存单元的保持电压的示例性技术的图;

[0029]

图7示出了常规控制器(例如,微控制器)的示例;并且

[0030]

图8示出了根据本发明的一个示例性实施方案的包括ram闪存单元的示例性控制器。

[0031]

应当理解,出现在多个不同附图中的任何所示元件的参考标号在多个附图中具有相同含义,并且本文在任何特定附图的上下文中提及或讨论任何所示元件也适用于每个其他附图(如果有的话),其中示出了相同的所示元件。

具体实施方式

[0032]

本发明的实施方案提供了ram闪存单元,该ram闪存单元具有基于常规闪存存储器单元的修改版本的结构,但是(与常规闪存存储器不同)被配置为在低电压(≤6v)域中操作。在一些实施方案中,与常规闪存单元相比,ram闪存单元形成有更薄的电介质区(例如,氧化物层)。例如,与常规闪存存储器单元相比,ram闪存单元可形成有更薄的浮栅电介质区(例如,浮栅氧化物层)和/或更薄的多晶硅层间电介质区(例如,多晶硅层间氧化物层),这与常规闪存单元相比可降低编程和擦除操作所需的电压。由于被配置用于低电压操作,根据本发明的ram闪存单元可与先进、高密度、低能耗的数据计算应用兼容,并且以最小或小的金属间距规则与先进逻辑流程兼容。

[0033]

在一些实施方案中,ram闪存单元可被配置用于改善的数据保留特性。例如,在一些实施方案中,ram闪存单元的数据保留可通过以下方式增加(例如,增加到数天、数月或数年的时间范围):(a)在单元的选定节点处施加静态保持电压,和/或(b)周期性地例如从外部存储器(例如,外部闪存存储器或外部dram)刷新/恢复存储在ram闪存单元中的数据。

[0034]

一些实施方案提供了包括ram闪存单元的电子设备(例如,计算机或微控制器)。ram闪存单元可替换或减少通常包括在常规电子设备(例如,常规闪存存储器、sram和/或dram)中的存储器的至少一部分,从而减小电子设备的尺寸和/或成本,和/或增加电子设备的性能(例如,增加操作速度和/或电池寿命)。

[0035]

图2示出了根据本发明的某些实施方案的包括ram闪存单元的示例性电子设备10。电子设备10可包括处理器(例如,微处理器)12、至少一个ram闪存阵列14、电源16、ram闪存控制电子器件20和/或用于提供电子设备10的任何功能的任何其他硬件、软件、固件或其他电路。电子设备10可以是计算机系统(例如,服务器、台式计算机、笔记本、平板、智能电话或任何其他类型的计算机系统)、微控制器或利用数据存储装置的任何其他类型的电子设备。电源16可包括至少一个电池、主电源或者在电子设备10中或外部设置的任何其他电源。

[0036]

每个ram闪存阵列14可包括本文所公开的或以其他方式符合所公开原理的任何数量和类型的ram闪存单元,包括但不限于下文参考图3讨论的示例性1t ram闪存单元50和/或下文参考图5讨论的示例性1.5t分栅ram闪存单元200。

[0037]

ram闪存控制电子器件20可包括用于控制ram闪存阵列14的操作的任何硬件、软件、固件或其他电路,该操作包括控制施加到ram闪存阵列14内的ram闪存单元的相关触点的电压,以对此类ram闪存单元执行编程、擦除和读取操作。在一些实施方案中,ram闪存控制电子器件20可包括例如体现为软件或固件的ram闪存控制逻辑22,该ram闪存控制逻辑被编程为执行本文所公开的任何功能,包括例如:(a)控制编程、擦除和读取操作,(b)确定和/或动态调整保持电压(vh)以施加到ram闪存单元以增加数据保留(例如,如下所述),(c)执行和控制数据恢复或刷新操作,以进一步增加ram闪存单元的数据保留,如下所述,和/或(d)ram闪存阵列14的任何其他功能或与ram闪存阵列相关的任何其他功能。ram闪存控制电子器件20可与处理器12协作,或者在一些实施方案中,可包括处理器12。

读取1v-2v0v1v-2v [0046]

用于1t ram闪存单元50的编程和擦除操作的3v至6v的示例性电压与常规1t闪存单元的10v至15v范围内的所需电压有利地比较。因此,与常规闪存存储器单元相比,根据本发明的1t ram闪存单元50可显著降低所需的操作电压。

[0047]

图4示出了已知的1.5t分栅闪存存储器单元100的侧剖视图。示例性分栅闪存存储器单元100可以是可购自亚利桑那州钱德勒的微芯片技术公司(microchip technology inc.,chandler,arizona)的superflash

tm

存储器单元(例如,superflash

tm

esf1 单元)。

[0048]

闪存存储器单元100包括形成在衬底104上方的一对浮栅102a和102b、分别在浮栅102a和102b上方延伸的字线端子106a和106b以及在浮栅102a和102b两者上方延伸的控制栅110。氧化物区108a、108b分别形成在每个浮栅102a、102b上方。字线端子106a和106b可耦接例如到奇数行字线和偶数行字线。掺杂源极区或结124可形成在控制栅110下方的衬底104中并且在每个浮栅102a和102b下方部分地延伸,并且一对掺杂位线区或结124a和124b可形成在衬底104中分别与字线端子106a和106b相邻。

[0049]

存储器单元100还可包括与字线端子106a和106b、控制栅110、源极区124以及位线区124a和124b接触的导电接触区,用于向各个单元部件施加电压以提供各种存储器单元功能,例如编程、擦除和读取功能。如图所示,这些触点可包括分别耦接到字线电压vwl odd和vwl even的字线触点130a和130b、耦接到控制栅电压vcg的控制栅触点132、源极触点134以及相应的位线触点136a和136b。源极触点134可相对于所示的横截面位于页面中或页面外,例如,在控制栅110中的裂口位置处。

[0050]

每个浮栅102a、102b由浮栅氧化物层140与在下的沟道区124分开。此外,每个浮栅102a、102b由多晶硅层间氧化物区142a与共享控制栅110分开,并且每个浮栅102a、102b由多晶硅层间氧化物区142b与相应的字线端子106a、106b分开。

[0051]

浮栅氧化物层140以及多晶硅层间氧化物区142a和142b形成为具有允许分栅闪存存储器单元100(例如,superflash

tm

存储器单元)作为非易失性、高电压单元的常规操作的厚度。例如,每个浮栅氧化物层140可具有约的厚度,而每个多晶硅层间氧化物区142a和142b可各自具有约的厚度。

[0052]

分栅闪存存储器单元100可通过向以下中的一者或多者在限定时间施加限定电压来编程和擦除:选定的字线触点130a或130b(分别耦接到字线电压v

wl odd和v

wl even)、控制栅触点132(耦接到控制栅电压v

cg

)、源极触点134(耦接到源极线电压v

sl

)和/或选定的位线触点136a或136b(耦接到位线电压v

bl

),以提供(a)与单元的编程状态(“断开”状态)对应的单元电流ir0或(b)与单元的擦除状态(“导通”状态)对应的单元电流ir1。此外,单元的编程/擦除状态可通过向选定的字线触点130a或130b(v

wl

)和相邻的位线触点136a或136b(v

bl

)施加限定电压来读取。

[0053]

表3示出了根据常规单元操作的可施加到图4所示的分栅闪存存储器单元100的各个触点以执行编程、擦除和读取操作的示例性电压。如图所示,通过将限定的v

wl

和v

bl

施加到选定的字线触点130a或130b和相关联的位线触点136a或136b,读取功能经由字线106a或106b和相关联的位线124a或124b执行,而没有电压施加到源极触点134(v

sl

=0)或控制栅触点132(v

cg

=0)。

[0054]

表3.常规分栅闪存存储器单元的操作的示例性偏置条件。

[0055] vwlvslvblvcg编程1.5v9v-15v~0.6v9v-15v擦除9v-15v0v0v-9v至-15v读取1.8v0v1.8v0v

[0056]

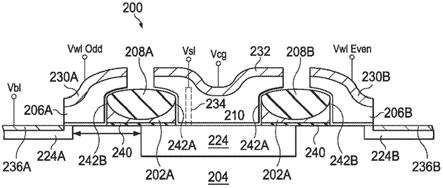

图5示出了根据本发明的示例性实施方案的示例性1.5t分栅ram闪存单元200(例如,修改的superflash

tm

存储器单元)。分栅ram闪存存储器单元200包括形成在衬底204上方的一对浮栅202a和202b、分别在浮栅202a和202b上方延伸的字线端子206a和206b以及在浮栅202a和202b两者上方延伸的控制栅210。氧化物区208a、208b分别形成在浮栅202a、202b上方。字线端子206a和206b可耦接例如到奇数行字线和偶数行字线。掺杂源极区或结224可形成在控制栅210下方的衬底204中并且在每个浮栅202a和202b下方部分地延伸,并且一对掺杂位线区或结224a和224b可形成在衬底204中分别与字线端子206a和206b相邻。

[0057]

分栅ram闪存单元200还可包括与字线端子206a和206b、控制栅210、源极区224以及位线区224a和224b接触的导电接触区,用于向各个单元部件施加电压以提供各种存储器单元功能,例如编程、擦除和读取功能。如图所示,这些触点可包括分别耦接到字线电压vwl odd和vwl even的字线触点230a和230b、耦接到控制栅电压vcg的控制栅触点232、源极触点234以及相应的位线触点236a和236b。源极触点234可相对于所示的横截面位于页面中或页面外,例如,在控制栅210中的裂口位置处。

[0058]

每个浮栅202a、202b由浮栅电介质区(例如,浮栅氧化物层)240与在下的沟道区224分开。此外,每个浮栅202a、202b由多晶硅层间电介质区242a与共享控制栅210分开,并且由多晶硅层间电介质区242b与相应的字线端子206a、206b分开。

[0059]

在一些实施方案中,浮栅电介质区240和多晶硅层间电介质区242a和/或242b以允许分栅ram闪存单元200在与先进、高密度、低能耗的数据计算应用兼容的低电压(≤6v)域中操作(例如,包括编程、擦除和读取功能)的相应厚度形成。在一些实施方案中,与常规分栅闪存存储器单元(例如,图4所示的常规分栅闪存存储器单元100的氧化物层/区140、142a和142b)的相应电介质层/区相比,一个、一些或所有浮栅电介质区240和多晶硅层间电介质区242a和/或242b具有减小的厚度。例如,每个浮栅202a、202b与在下的沟道区124之间的相应浮栅电介质区240可具有小于或小于的厚度,例如在的范围内。又如,每个浮栅202a、202b之间的相应多晶硅层间电介质区242a以及共享控制栅210之间的相应字线端子206a、206b可具有小于或小于的厚度,例如在的范围内。又如,每个浮栅202a、202b与其相邻字线端子206a、206b之间的相应多晶硅层间电介质区242b可具有小于或小于的厚度,例如在的范围内。在一些实施方案中,(a)每个浮栅电介质区240具有小于或小于的厚度,例如在的范围内,并且(b)每个多晶硅层间电介质区242a和242b具有小于或小于的厚度,例如在的范围内。

[0060]

取决于具体实施方案,每个电介质区(例如,氧化物层或区),包括浮栅电介质区240、多晶硅层间电介质区242a和/或多晶硅层间电介质区242b,可热生长或沉积在结构上。在一些实施方案中,每个电介质区240、242a和242b的厚度可通过选择或调整与相应区240、

242a、242b的生长或沉积相关的参数(例如,每个相应电介质(例如,氧化物)生长或沉积工艺的时间、温度和/或气流参数)来控制。

[0061]

分栅闪存存储器单元200可例如由图2所示的ram闪存控制电子器件20向以下一者或多者在限定时间施加限定电压来编程和擦除:选定的字线触点230a或230b(分别耦接到字线电压v

wl

odd和v

wl

even)、控制栅触点232(耦接到控制栅电压v

cg

)、源极触点234(耦接到源极线电压v

sl

)和/或选定的位线触点236a或236b(耦接到位线电压v

bl

),从而提供(a)与单元的编程状态(“断开”状态)对应的单元电流ir0或(b)与单元的擦除状态(“导通”状态)对应的单元电流ir1。此外,可通过向选定的字线触点230a或230b(v

wl

)和相邻的位线触点236a或236b(v

bl

)施加限定电压来读取单元的编程/擦除状态。

[0062]

由于电介质区240、242a和/或242b的厚度减小(与常规闪存存储器单元相比),ram闪存单元200上的编程和擦除功能可使用比常规闪存存储器单元(诸如分栅闪存存储器单元100)更低的电压来执行。例如,在ram闪存单元200的一些实施方式中:(a)通过源极侧热电子注入来执行编程;因此,浮栅电介质区(例如,浮栅氧化物层)240的减小的厚度产生了更高的场;以及(b)通过浮栅202a、202b的上尖端与相邻字线206a、206b之间的fowler-nordheim隧穿来执行擦除;因此,相应的多晶硅层间氧化物区242b的减小的厚度产生了更高的场。此外,低电压(≤6v)编程或擦除操作可允许使用先进低k电介质金属间距而没有泄漏和可靠性问题。

[0063]

对于相应的ram闪存单元,电介质区240、242a和242b的厚度、在擦除电压和编程电压期间施加的电压以及单元的数据保留都彼此相关。例如,减小电介质区240、242a和242b的厚度可允许较低电压的编程和擦除功能,但是可减小单元的数据保留,反之亦然。又如,对于具有特定电介质区厚度的单元,减小用于编程和擦除功能的操作电压通常减小了单元的数据保留,反之亦然。因此,对于任何特定的ram闪存单元或ram闪存单元阵列,可选择或调节上述各种因素(例如,电介质区厚度、编程和擦除电压以及数据保留)以提供单元的所需功能,例如取决于提供单元的特定的应用、设备或产品。

[0064]

根据四个示例性实施方案,以下表4a至表4d示出了可(例如,由图2所示的ram闪存控制电子器件20)施加到图5所示的示例性ram闪存单元200的各个触点的示例性电压,以用于执行编程、擦除和读取功能。表4a至表4d的示例性实施方案可对应于具有电介质区240、242a和242b的选定厚度的单元,以用于相应单元的所需数据保留特性。如图所示,通过将限定的v

wl

和v

bl

施加到选定的字线触点230a或230b和相关联的位线触点236a或236b,常规读取功能经由字线206a或206b和相关联的位线224a或224b执行,而没有电压施加到源极触点234(v

sl

=0)或控制栅触点232(v

cg

=0)。

[0065]

表4a.分栅ram闪存单元200的操作的示例性偏置条件(图5),示例性实施方案a。

[0066] vwlvslvblvcg编程1.5v1.5v-6.0v~0.6v1.5v-6.0v擦除1.5v-6.0v0v0v-1.5v至-6.0v读取1.8v0v1.8v0v

[0067]

表4b.分栅ram闪存单元200的操作的示例性偏置条件(图5),示例性实施方案b。

[0068] vwlvslvblvcg编程1.5v2.0v-5.0v~0.6v2.0v-5.0v

擦除2.0v-5.0v0v0v-2.0v至-5.0v读取1.8v0v1.8v0v

[0069]

表4c.分栅ram闪存单元200的操作的示例性偏置条件(图5),示例性实施方案c。

[0070] vwlvslvblvcg编程1.5v2.0v-4.0v~0.6v2.0v-4.0v擦除2.0v-4.0v0v0v-2.0v至-4.0v读取1.8v0v1.8v0v

[0071]

表4d.分栅ram闪存单元200的操作的示例性偏置条件(图5),示例性实施方案d。

[0072] vwlvslvblvcg编程1.5v3.0v~0.6v3.0v擦除3.0v0v0v-3.0v读取1.8v0v1.8v0v

[0073]

在一些实施方案中,ram闪存控制电子器件20可至少基于浮栅电介质区240和多晶硅层间电介质区242a和/或242b的厚度来选择要施加的电压或电压范围以用于单元200中的有效编程和擦除操作,例如,其中施加的电压可减小以用于减小电介质厚度。如表4a至表4d(分栅ram闪存单元200的示例性操作)与表3(常规分栅闪存存储器单元100的示例性操作)的比较所示,图5所示的示例性分栅ram闪存单元200允许比常规分栅闪存存储器单元100显著更低的编程电压和擦除电压。

[0074]

除了允许低电压操作的ram闪存单元的本发明结构之外,本发明的另一个方面还提供了操作ram闪存单元(例如,上述示例性1t ram闪存单元50或示例性分栅ram闪存单元200)的方法,以基于保留损耗的关键路径以可定制和/或动态可控或可调的方式改善保留特性。如下所述,在一些实施方案中,ram闪存单元的数据保留可通过以下方式增加(例如,增加到数天、数月或数年的时间范围):(a)在单元的选定节点处施加静态保持电压,和/或(b)周期性地例如从外部存储器(例如,外部闪存存储器或外部dram)刷新/恢复存储在ram闪存单元中的数据。

[0075]

表5示出了根据一个示例性实施方案的用于增加图5所示的示例性分栅ram闪存单元200的存储保留的一个示例性方法。如表5所示,合适的控制电子器件(例如,图2所示的ram闪存控制电子器件20)可将非零静态保持电压vh施加到字线端子206a、206b和控制栅(cg)210,以降低跨浮栅(fg)202a、202b周围的电介质区的场,从而改善保留。在一些实施方案中,在此类保持条件下汲取低静电流,这可产生跨浮栅氧化物到相邻多晶硅区(例如,poly2区)的低场。表5示出了用于向ram闪存单元200施加静态保持电压vh的示例性偏置条件。

[0076]

表5.分栅ram闪存的改善保留的示例性偏置条件(图5)。

[0077] vwlvslvblvcg静态保持vh0v0vvh

[0078]

在一些实施方案中,ram闪存控制电子器件20可被配置为例如基于随时间确定或监测的特定单元操作和/或性能特性来选择和/或动态调整(或“调节”)保持电压vh。图6是示出根据示例性实施方案的用于基于示例性ram闪存单元的性能来选择保持电压vh的一种

示例性方法的图。在图6所示的示例中,在擦除状态期间单元的电压阈值为 xv,而处于编程状态的单元的电压阈值为-yv,这些电压可由任何合适的电子器件(例如,与ram闪存单元设置在同一微控制器或计算机上)测量并且在多个循环内取平均。在一些实施方案中,要施加到ram闪存单元的保持电压vh可确定为擦除状态电压阈值( xv)和编程状态电压阈值(-yv)的数学函数。例如,可选择保持电压vh为擦除状态电压阈值( xv)与编程状态电压阈值(-yv)之间的中点,其可表示为|x y|/2,如图6所示,并且其可称为“擦除状态/编程状态中点电压”。

[0079]

在一些实施方案中,ram闪存单元或ram闪存单元组在给定状态(擦除状态和/或编程状态)下的保留电荷损耗可在制造时(在产品测试或产品表征过程期间)表征,并且较弱状态(编程或擦除)可通过施加适当的保持电压vh来补偿。例如,如果对于特定ram闪存单元,确定擦除状态保留电荷损耗占主导(与编程状态保留电荷损耗相比),则ram闪存控制电子器件20可在浮栅周围的所有节点上施加正vh(例如,使用如上所述确定的值)。相反,ram闪存控制电子器件20可施加负vh以增强编程状态下的保留,例如,对于编程状态保留电荷损耗占主导的ram闪存单元。

[0080]

此外,对于擦除状态保留电荷损耗占主导的ram闪存单元,ram闪存控制电子器件20还可向源极线施加正电压(例如,除了施加到字线(wl)和控制栅(cg)的保持电压vh之外),以进一步改善单元中的数据保留。施加到源极线的正电压可与保持电压vh相同、小于或大于保持电压vh,这取决于特定实施方式。

[0081]

在一些实施方案中,ram闪存单元的擦除状态电压和/或编程状态电压可随时间而改变(例如,在n个编程/擦除循环之后),并且因此ram闪存控制电子器件20可相应地重新计算并且动态调整保持电压vh,例如,通过以限定的重复频率重新计算并且动态调节擦除状态/编程状态中点电压接通。

[0082]

在一些实施方案中,ram闪存单元可经历比某些常规存储器单元(例如,基于细丝的电阻ram)显著更小的可变性,这是由于与基于电介质存储的ram闪存单元相比,细丝形成过程中固有的可变性更大。因此,在一些实施方案中,对制造变量和操作变量的严格控制可使ram闪存控制电子器件20能够对ram闪存单元阵列施加公共保持电压vh,而不是向阵列内的不同单元施加不同的保持电压vh。此外,与电阻存储器相比,保持模式可允许较低的电流消耗,从而允许在密集应用中的低总功率消耗。

[0083]

在一些实施方案中,ram闪存控制电子器件20可被配置为通过实现受控的数据恢复/刷新协议来进一步增加ram闪存单元中的数据存储保留。如本文所公开的ram闪存单元的预期保留可以是数天到数月,这取决于特定ram闪存单元结构、施加的电压以及用于形成相关电介质层的工艺(例如,用于形成浮栅电介质区和/或多晶硅层间电介质区的特定工艺)。在一些实施方案中,ram闪存控制电子器件20可被编程为周期性地(例如,在每n小时或每n天之后)从外部数据存储装置(例如,从相关ram闪存阵列外部的dram、nand或hdd)恢复存储在ram闪存单元中的数据,以进一步增加ram闪存单元的数据保留,例如增加到数年的保留期。例如,通过首先将ram闪存单元的内容读取到其他存储器(例如sram、dram或其他闪存存储器),然后将每个ram闪存单元重新擦除或重新编程,ram闪存控制电子器件20可被编程为对ram闪存单元或ram闪存单元组执行数据刷新。

[0084]

在一些实施方案中,例如与常规dram(其通常需要64ms的刷新频率)或其他常规存

储器单元相比,被配置用于扩展的数据保留(例如,通过施加保持电压vh和/或通过实现数据刷新协议,例如如上所述)的ram闪存可用于需要扩展的数据保留和低数据刷新速率的应用中。降低的刷新速率可延长相应电子设备10(例如,计算机或微控制器)的电池寿命。

[0085]

此外,如上所述,在一些实施方案中,ram闪存数据保留可通过在选定节点处(例如,在分栅ram闪存单元中的字线(wl)和控制栅(cg)电极处)提供保持电压vh来扩展。在一些实施方案中,保持电压vh的值可依据每个相应的ram闪存单元或ram闪存阵列的保留损耗特性来确定和/或动态调节,诸如ram闪存单元在擦除状态还是编程状态下表现出更大的保留电荷损耗。

[0086]

通过形成具有各种类型的常规闪存存储器单元的修改结构的ram闪存单元(例如,通过减小此类闪存存储器单元的浮栅电介质区和/或多晶硅层间电介质区的厚度),本文所公开的概念可应用于任何合适类型的闪存存储器单元,该常规闪存存储器单元包括单晶体管(1t)闪存存储器单元和多晶体管闪存存储器单元(例如,1.5t分栅闪存单元),该多晶体管闪存存储器单元包括例如一系列nor闪存存储器单元,诸如覆盖宽泛的工艺几何形状范围的superflash

tm

esf1、esf2、esf3或esf4单元。

[0087]

如上所述,如本文所公开的ram闪存单元可被配置用于低电压(≤6v)编程/擦除操作。因此,ram闪存单元可以最小或小的金属间距规则与高密度先进逻辑流程兼容。图7和图8示出了使用常规存储器设备(图7)的常规微控制器(例如,物联网(iot)应用的控制器)的示例与并入根据本发明的ram闪存存储器(图8)的对应控制器之间的比较,这些控制器可减少或替换常规控制器中所需的sram、dram和/或常规闪存存储器。

[0088]

图7所示的示例性常规控制器300包括芯片302,该芯片包括cpu 304、sram 306、常规闪存存储器308、逻辑/模拟设备310和/或其它各种电子器件。芯片302由电池312供电,并且与sram 316、dram 318、外部传感器和通信协议(例如,wifi、以太网等)交互。闪存存储器308是高保留存储器(通常》10年)并且对于编程/擦除操作需要高电压(例如,》10v),并且以低速执行此类编程/擦除操作。如图7所示,对于先进节点应用,cpu 304、sram 306和芯片302上的逻辑/模拟设备310可以是低电压设备,因此与小金属间距结构兼容,而闪存308由于高电压(》10v)操作要求而需要大得多的金属间距。

[0089]

相比之下,根据本发明的一个示例性实施方案,图8所示的示例性控制器400包括芯片402,该芯片包括cpu 404、sram 406、ram闪存存储器420、常规闪存存储器(可选的)408、逻辑/模拟设备410和/或其他各种电子器件。芯片402可由电池412供电,并且可与常规芯片302一样与外部传感器和通信协议(例如,wifi、以太网等)交互,并且可(可选地)与外部sram 416和/或dram 418交互。如图所示,与常规控制器(例如,上文所述的控制器300)相比,在芯片402上包括ram闪存420可减少或消除对控制器400中的一种或多种其他类型的存储器的需要。例如,ram闪存420可(a)允许片上sram 406减小,(b)允许片上常规闪存存储器408减小或消除,和/或(c)允许外部sram 416和/或dram 418减小或消除。ram闪存420可利用常规控制器中sram或dram通常使用的芯片占位,可使用较少的功率和空间(例如,因为闪存存储器小于sram),并且具有增加的速度,因为操作速度由ram闪存访问时间限定,而不是如在常规控制器300中从外部dram获得数据。另外,因为ram闪存420被配置为低电压操作,所以它可以小金属间距(例如,由芯片cpu 404、sram 406和逻辑/模拟设备408使用的间距)产生,从而减少芯片402上所需的占位面积。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。