用于存储器内计算的双极全忆阻器电路

1.相关申请的交叉引用

2.本技术涉及并要求2019年5月7日提交的美国临时申请no.62/844,611、2019年6月13日提交的美国临时申请no.62/860,915和202年3月3日提交的美国非临时申请no.16/808,227的优先权,这些申请以引用的方式并入本文中。本技术还涉及于2020年3月3日提交的美国非临时申请no.16/808,222和pct申请(参考号no.632140

‑

4),这两项申请同时提交。

3.关于联邦资金的声明

4.本发明是根据美国政府合同fa8650

‑

18

‑

c

‑

7869作出的。美国政府在本发明中具有某些权利。

技术领域

5.本公开涉及神经网络。

背景技术:

6.深度卷积神经网络(cnn)是当前机器学习和视觉数据处理的主流架构。在典型的神经网络中,大量的乘法

‑

累加(mac)算术运算用于计算输入图像块的卷积以用于特征提取。卷积是cnn中用于视觉或音频数据处理的计算最密集的部分。在基于冯诺依曼(von neumann)架构的传统数字计算机中,算术逻辑单元(alu)和数据存储器在空间上是分开的,用于移动数据的能量可以比用于计算的能量高10倍。因此,期望开发新的电路架构,以实现能量高效且高吞吐量的存储器内(in

‑

memory)或存储器附近(near

‑

memory)计算。

7.对存储器内计算有益的电路架构是神经形态尖峰神经网络(snn),其结合了三个主要优点。

8.首先,一种非易失性交叉(crossbar)存储器架构,允许在本地保存和再次使用mac运算中的两个操作数中的一个,这大大减少了移动数据时使用的能量。第二,无源忆阻器突触的模拟(连续)切换,具有中等比特精度(每个突触的单个元素高达约7比特),从而实现节能模拟计算。第三,尖峰域数据表示,允许能量高效的mac操作和最小的电流消耗。

9.然而,现有技术神经形态snn演示主要是用cmos电子器件构建的。cmos电子器件不是仿生的,因此需要大的电路开销来构建神经元和突触构建块,这抵消了snn架构的好处。

10.参考文献[1]由本发明人于2019年6月13日提交(632128)(准备中的np 632152)的美国临时申请62/860,915通过引用并入本文,其描述了用于能量高效且并行的存储器内mac运算和卷积计算的无晶体管全忆阻器snn电路和方法。模拟全忆阻器神经形态卷积电路(神经突触处理器)由以兴奋性有源忆阻器为基础的尖峰神经元和无源忆阻器突触组成。表示卷积权重的突触元素被组织成二维交叉阵列,其中尖峰忆阻器神经元在边缘处连接行(字线)和列(位线)。存储器内向量矩阵乘法(vmm)算术运算,可以使用欧姆定律和基尔霍夫电流定律原理并行计算,以实现高通量的多核卷积。尖峰域数据编码保证了比数字电路更好的能量效率。通过器件级spice模拟分析了图像分类中的卷积性能,结果表明,无晶体管卷积电路可以提供比最先进(soa)cmos神经形态处理器(ibm truenorth)高10倍或更好的

能量效率(每输入比特0.3nj相比于每输入比特6.7nj)。

[0011]

然而,使用参考文献[1]的神经元和突触进行存储器内计算的无晶体管全忆阻器神经形态电路只能与所有权重都为正的内核执行卷积。这使得该电路不适用于某些应用,例如在某些神经网络图像分类器中实现卷积层。

[0012]

参考文献[2]中描述的电路通过引用并入本文,描述了利用忆阻器工具栏(toolbar)突触的模拟信号和图像处理,但它没有示出集成忆阻器神经元的使用。此外,参考文献[2]的电路可能需要外部神经元,这将导致更大的电路消耗更多的功率。

[0013]

参考文献

[0014]

在此引入以下参考文献,如同全文阐述的一样。

[0015]

[1]美国临时申请62/860,915,2019年6月13日提交(632128)(准备中np 632152)

[0016]

[2]li,c.,hu,m.,li,y.,jiang,h.,ge,n.,montgomery,e.,zhang,j.,song,w.,d

á

vila,n.,graves,c.e.和li,z.,2018。“大型忆阻器交叉的模拟信号和图像处理(analogue signal and image processing with large memristor crossbars)”,自然电子学(nature electronics),1(1),p.52。

[0017]

[3]美国专利申请no.15/976,687,2018年5月10日提交。

[0018]

[4]美国专利申请no.15/417,049,2017年1月26日提交。

[0019]

[5]美国专利申请no.16/005,529,提交日期不详。

[0020]

[6]美国专利申请no.15/879,363,2018年1月24日提交。

[0021]

[7]m.d.pickett,g.medeiros

‑

ribeiro和r.s.williams,“用莫特忆阻器构建的可扩展神经电阻器(a scalable neuristor built with mott memristors)”,自然材料(nature mater),12,114(2013)。

[0022]

[8]m.d.pickett,“使用神经元的逻辑电路(logic circuits using neuristors)”,美国专利8,669,785b2(2014)。

[0023]

[9]yoon,j.h.,zhang,j.,ren,x.,wang,z.,wu,h.,li,z.,barnell,m.,wu,q.,lauhon,l.j.,xia,q.,和yang,j.j.,“具有预调节导电隧穿路径的真正无电铸和低能忆阻器(truly electroforming

‑

free and low

‑

energy memristors with preconditioned conductive tunneling paths)。”,先进功能材料(advanced functional materials)27,第1702010页(2017)。

[0024]

所需要的是能够有效地执行与核的卷积的电路,其中权重可以具有正值或负值,并且允许实现用于神经网络图像分类器的卷积层,并且该电路具有低功率。本公开的实施例解决了这些和其他需要。

技术实现要素:

[0025]

在本文公开的第一实施例中,一种用于执行能量高效且高吞吐量乘法

‑

累加(mac)算术点积运算和卷积计算的电路,包括二维交叉阵列和输出忆阻器神经元电路,二维交叉阵列包括多个行输入和具有多个列电路的至少一列,其中,每个列电路耦接到相应的行输入,其中,每个相应列电路包括:兴奋性忆阻器神经元电路,其具有耦接到相应行输入的输入;第一突触电路,其耦接到所述兴奋性忆阻器神经元电路的输出,所述第一突触电路具有第一输出;抑制性忆阻器神经元电路,其具有耦接到相应行输入的输入;以及第二突触电

路,其耦接到所述抑制性忆阻器神经元电路的输出,所述第二突触电路具有第二输出,输出忆阻器神经元电路耦接到每个列电路的第一输出和第二输出,所述输出忆阻器神经元电路具有输出。

[0026]

在本文公开的另一个实施例中,一种用于设置兴奋性忆阻器突触电路和抑制性忆阻器突触电路的电导值的方法,包括:使用流行的随机梯度下降法训练卷积核权重;以及通过以下操作将第k个卷积核的经训练的卷积核权重元素w(i,j)转换为双象限突触电导值,其中,i和j是二维权重矩阵的行和列索引,该双象限突触电导值可以是正的或负的:通过使用线性转换方案将经训练的卷积核权重元素w(i,j)转换为突触权重g(i,j)使得g(i,j)=(w(i,j)x 1.2e

‑6)/max(w(i,j));确定g(i,j)是正还是负,并且如果突触权重g(i,j)是零或正,则将相应抑制性忆阻器突触电路的电导g

inh

(i,j)设置为第一下界值,并且将相应兴奋性忆阻器突触电路的电导g

exc

(i,j)设置为使得总电导g(i,j)或g

exc

(i,j)和g

inh

(i,j)的带符号和等于w(i,j)x 1.2e

‑6)/max(w(i,j)的值,如果突触权重g(i,j)为负,则将相应兴奋性忆阻器突触电路的电导g

exc

(i,j)设置为第二下限值,并将相应抑制性忆阻器突触电路的电导g

inh

(i,j)设置为使得总电导g(i,j)或g

inh

(i,j)和g

exc

(i,j))的带符号和等于w(i,j)x 1.2e

‑6)/max(w(i,j)的值。

[0027]

在本文公开的另一实施例中,一种用于执行能量高效且高吞吐量乘法

‑

累加(mac)算术点积运算和卷积计算的方法,包括:提供二维交叉阵列,其包括多个行输入和具有多个列电路的至少一列,其中,每个列电路耦接到相应的行输入,其中,每个相应列电路包括:兴奋性忆阻器神经元电路,其具有耦接到相应行输入的输入;第一突触电路,其耦接到所述兴奋性忆阻器神经元电路的输出,所述第一突触电路具有第一输出;抑制性忆阻器神经元电路,其具有耦接到相应行输入的输入;以及第二突触电路,其耦接到所述抑制性忆阻器神经元电路的输出,所述第二突触电路具有第二输出;以及提供输出忆阻器神经元电路,其耦接到每个列电路的第一输出和第二输出,所述输出忆阻器神经元电路具有输出。

[0028]

从下面的详细描述和附图中,这些和其他特征和优点将变得更加明显。在附图和说明书中,附图标记表示各种特征,贯穿附图和说明书,相同的标记表示相同的特征。

附图说明

[0029]

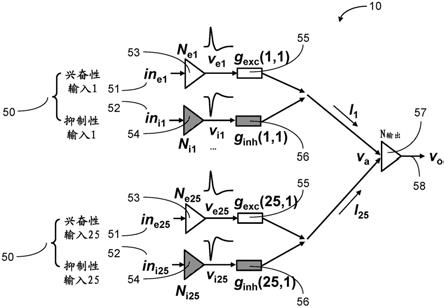

图1a示出了具有25个兴奋性输入神经元、25个抑制性输入神经元和一个兴奋性输出神经元的双极性(“双象限”)全忆阻器卷积核的符号图,图1b示出了双极性全忆阻器卷积电路的图,图1c示出了具有10个并联运行的如图1a中所示的卷积核的双极性全忆阻器卷积电路的图,图1d示出了在一个抑制性忆阻器神经元和一个兴奋性忆阻器神经元的输入和输出处的模拟尖峰波形,图1e示出了兴奋性忆阻器神经元的电路图,图1f示出了根据本公开的抑制性忆阻器神经元的电路图。

[0030]

图2示出了示出根据本公开的用于基于从预训练的cnn卷积核权重w(i,j)转换的突触权重g(i,j)的符号来设置兴奋性突触元素g

exc

(i,j)和抑制性突触元素g

inh

(i,j)的电导值的算法的框图。

[0031]

图3a示出了根据本公开的使用图2中所示的算法的双极性全忆阻器卷积电路的250个兴奋性忆阻器突触的计算电阻值,图3b示出了根据本公开的使用图2中所示的算法的双极性全忆阻器卷积电路的250个抑制性忆阻器突触的计算电阻值。

[0032]

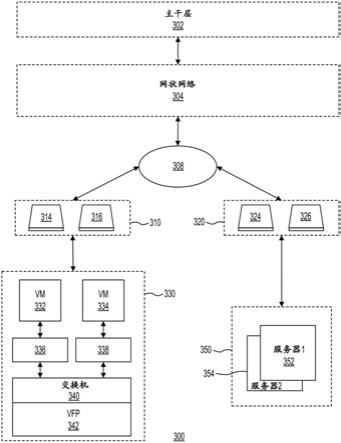

图4示出了根据本公开的定制matlab cnn模型,其用于对图1b所示的双极性全忆阻器卷积电路的能量效率和吞吐量度量进行基准测试(benchmark)。

[0033]

图5示出了使用图4中的matlab cnn模型进行基准测试的mnist图像分类的示例,其中,卷积层操作用全忆阻器卷积电路来模拟,如图1b所示在spice模拟器中,其示出了输入图像的类,在这种情况下是手写数字“2”,由根据本公开的十个分类器输出中的最大值确定。

[0034]

图6示出了根据本公开的包含(50x10)无源忆阻器突触交叉阵列的全忆阻器双极性卷积电路的基准测试mnist图像卷积性能度量的表。

具体实施方式

[0035]

在以下描述中,阐述许多特定细节以清楚地描述本文所公开的各种特定实施例。然而,本领域技术人员将理解,可在不具有下文论述的所有特定细节的情况下实践本发明。在其他情况下,没有描述公知的特征,以免混淆本发明。

[0036]

在本公开中,描述了一种无晶体管记忆神经形态电子电路和用于能量高效且高通量乘法

‑

累加(mac)算术运算和卷积计算的方法。与参考文献[1]中描述的其中缩放元素(突触权重)的值仅可以是正的电路相比,本发明利用兴奋性和抑制性忆阻器神经元和突触来实现正和负突触权重。双极性(或“双象限”)突触权重有助于提高基于卷积神经网络(cnn)的图像分类应用的训练收敛和推理精度。

[0037]

参考文献[1]描述了全忆阻器存储器内向量矩阵乘法(vmm)算数运算的基本操作原理(基于欧姆定律和基尔霍夫电流定律)。本发明应用相同的操作原理;然而,本发明的电路允许正和负突触权重两者。

[0038]

本公开描述了用于能量高效且高吞吐量乘法

‑

累加(mac)算术运算的无晶体管记忆神经形态电子电路和方法,乘法

‑

累加(mac)算术运算有时被称为点积运算、向量矩阵乘法(vmm)运算和卷积计算。

[0039]

模拟全忆阻器神经形态卷积电路(神经突触处理器)由基于有源忆阻器的兴奋性和抑制性尖峰神经元和无源忆阻器突触组成。可以将表示正和负卷积权重的突触元素组织成具有尖峰忆阻器兴奋性神经元和尖峰忆阻器抑制性神经元的二维交叉阵列。存储器内向量矩阵乘法(vmm)算术运算,可以使用欧姆定律和基尔霍夫电流定律原理并行计算,以实现高通量的多核卷积。尖峰域数据编码具有比数字电路实现更好的能量效率。通过器件级spice仿真分析了视觉数据处理(图像分类)中的卷积性能,并表明所提出的无晶体管卷积电路可以提供比最先进(soa)cmos神经形态处理器高10倍或更好的能量效率。

[0040]

本公开的实施例利用例如在参考文献[3]美国专利申请no.15/976,687、参考文献[5]美国专利申请no.16/005,529和参考文献[6]美国专利申请no.15/879,363中描述的有源和无源忆阻器器件和电路,这些文献通过引用并入本文。

[0041]

图1a示出了双极性(“双象限”)全忆阻器卷积电路10的电路架构,其提供对称的“双象限”卷积核权重。该电路类似于参考文献[1]中描述的“单象限”忆阻器卷积电路,但包括一组额外的抑制性输入神经元54和突触56,如图1a所示,不存在参考文献[1]中所述的“单象限”忆阻器卷积电路。

[0042]

图1a示出了示例性双极性全忆阻器卷积核10,其包含25个兴奋性忆阻器神经元电

路53、25个抑制性忆阻器神经元电路54和一个兴奋性输出忆阻器神经元电路57。连接到突触电路56的附加抑制性神经元电路54允许对称mac运算,其中突触权重可以是正的或负的。相比之下,参考文献[1]中描述的电路只使用正突触权重执行非对称mac运算。

[0043]

如图1a所示,每个相应兴奋性忆阻器神经元电路53的输出是连接的相应突触电路55的输入,每个相应抑制性忆阻器神经元电路54的输出是连接的相应突触电路56的输入。每个突触电路55和56的输出是到兴奋性输出忆阻器神经元57的输入。双极性全忆阻器卷积核10的输出58是输入50(对于图1a中所示的示例,具有25个输入50)与由连接到突触电路55的兴奋性忆阻器神经元电路53提供的有效权重和由连接到突触电路56的抑制性忆阻器神经元电路54提供的有效权重的卷积。每个相应的输入50连接到兴奋性忆阻器神经元电路53的相应输入51和抑制性忆阻器神经元电路54的相应输入52。

[0044]

兴奋性忆阻器神经元电路53和连接的突触电路55的有效权重可以为零或正。抑制性忆阻器神经元电路54和连接的突触电路56的有效权重可以为零或负,但是可以被配置为仅为负。

[0045]

图1b示出了根据图1a的双极性全忆阻器卷积电路的简化图,其中到兴奋性忆阻器神经元电路53和到抑制性忆阻器神经元电路54的输入来自图像块100。

[0046]

图1c示出了类似于图1b的双极性全忆阻器卷积电路60的简化物理图,但是其包括并行操作的十(10)个卷积核。例如,out

1 66是连接到二维矩阵的各行的25个输入50in1至in

25

与矩阵的第一列62中的连接到突触电路55的兴奋性忆阻器神经元电路53的有效权重以及抑制性忆阻器神经元电路54和连接的突触电路56的有效权重的卷积,如图1c中所示。out

10 68是连接到二维矩阵的各行的25个输入50in1至in

25

与矩阵的列64中的连接到突触电路55的兴奋性忆阻器神经元电路53的有效权重以及抑制性忆阻器神经元电路54和连接的突触电路56的有效权重的卷积,如图1c中所示。

[0047]

图1e示出了兴奋性忆阻器神经元的电路图,图1f示出了抑制性忆阻器神经元的电路示意图。

[0048]

在图1e和图1f中,x1和x2表示氧化钒(vo2)有源忆阻器器件,re1和re2是从电极线到vo2有源忆阻器器件的寄生串联电阻(150ω)。标签in是神经元的输入端口,标签out是神经元的输出端口。vdd是正电源电压,并且vss是负电源电压。

[0049]

x1和x2的spice模型参数为:deltat=43、rch=56e

‑

9、lchan=100e

‑

9、rhoins=1e

‑

2、rhomet=3e

‑

6、kappa=3.5、cp=3.3e6、deltahtr=2.35e8。兴奋性和抑制性vo2忆阻器神经元操作的更多细节在参考文献[7]中有所描述:2018年5月10日提交的美国专利申请no.15/976,687,其通过引用并入本文。

[0050]

图1e示出了兴奋性忆阻器神经元电路20的示意图,其具有以相反极性(

‑

vdc; vdc)偏置的第一(x1)和第二(x2)负差分电阻(ndr)器件。第一和第二ndr器件(x1、x2)分别耦接到第一和第二接地电容器(c1、c2)。

[0051]

第一ndr器件(x1)具有通过第一负载电阻器rl1连接到神经元电路20的输入节点32的第一节点30和连接到第一电压源36的第二节点34,第一ndr器件(x1)的第一节点(30)耦接到第一接地电容器(c1)。第二ndr器件(x2)具有通过第二负载电阻器rl2连接到第一ndr器件x1的第一节点30的第一节点38和连接到第二电压源42的第二节点40,第二ndr器件x2的第一节点38耦接到第二接地电容器c2,第二ndr器件x2的第一节点38形成神经元电路

20的输出节点44。

[0052]

第一电压源36是负电压源,而第二电压源42是正电压源。由电压源36和42提供的电压

‑

vdc、 vdc可以具有相同的幅度,或者其可以具有不同的幅度。只有当两个ndr器件x1和x2在其开关阈值电压上很好地匹配时,dc电压源36和42才是幅度匹配的。如果x1和x2的开关阈值电压不同,则必须不同地选择其直流电压源的值,使得两个ndr器件在适当的操作点(小于但接近其开关阈值电压)被偏置,以使神经元电路适当地生成尖峰。

[0053]

第一和第二ndr器件x1、x2中的每一个可以在其第一节点(分别为30、38)和第二节点(分别为36、40)之间包括与ndr材料串联的电阻(分别为re1、re2)。第一和第二ndr器件x1、x2的ndr材料可以是二氧化钒的层或薄膜。re1可以具有几百欧姆的值,并且可以是布置在第一节点(30)和x1的ndr材料的第一侧之间的第一金属纳米线电极以及布置在第二节点(34)和x1的ndr材料的第二侧之间的第二金属纳米线电极的累积电阻。类似地,re2可以具有几百欧姆的值,并且可以是布置在第一节点(38)和x2的ndr材料的第一侧之间的第一金属纳米线电极以及布置在第二节点(40)和x2的ndr材料的第二侧之间的第二金属纳米线电极的累积电阻。

[0054]

二氧化钒层可以通过由五氧化二钒层电铸而产生,如美国专利申请no.15/417,049(提交于2017年1月26日,上面的参考文献[8])中详述的,该申请通过引用并入本文。

[0055]

或者,二氧化钒层可以通过各种薄膜沉积方法直接制备,包括但不限于钒金属或氧化钒靶的反应直流或射频磁控溅射、原子层沉积接着沉积后退火、或金属前体氧化。

[0056]

第一和第二电压源(36,42)被布置成使第一和第二ndr器件(x1、x2)接近其各自的莫特(mott)绝缘体到金属的转变,并且可以调节电压偏置以设置用于神经元动作电位生成(尖峰激发)和期望信号增益的期望电压或电流阈值电平。第一负载电阻器、第一ndr器件、第一电压源和第一接地电容器被布置成形成第一张弛振荡器,第二负载电阻器、第二ndr器件、第二电压源和第二接地电容器被布置成形成第二张弛振荡器。

[0057]

第一和第二ndr器件x1、x2的ndr材料可以是二氧化钒层或薄膜,其中二氧化钒具有340k(67℃)的mott绝缘体到金属(imt)转变温度tc。这种二氧化二钒ndr器件的操作只需要非常温和的焦耳加热,就可以将局部温度提高到室温以上40k(或℃)。例如,已经计算出,具有半径为10nm的二氧化钒通道(例如位于五氧化二钒薄膜中)的ndr器件具有1.2fj的极低估计开关能量,其比nbo2器件低50倍,如pickett等人所公开的参考文献[7]和[8],通过引用并入本文。预期根据本说明书的实施例的基于二氧化钒的神经元电路能够实现生物学上有竞争力的0.1pj/尖峰或更少的神经元能量使用。单个vo

2 ndr器件可以低至1.2fj地操作,但是整个神经元电路(x1、x2、c1、c2、rl1、rl2)的能量消耗由两个电容器的充电能量支配。假定示例性直流偏压水平接近0.5v并且具有40~50ff电容器(根据神经元大小和尖峰频率的考虑选择这样的小电容器值),估计0.1pj/尖峰总能量消耗。

[0058]

神经元电路20可以用在具有连接在网络中的多个神经元电路的神经电路中,例如,如图1a所示;输入节点32被布置为通过输入阻抗zin接收输入波形;并且输出节点44被布置为通过输出阻抗zout提供输出波形。

[0059]

图1f示出了抑制性忆阻器神经元电路26的示意图,其具有以相反极性( vdc;

‑

vdc)偏置的第一(x2)和第二(x1)ndr器件。第一和第二ndr器件(x2、x1)分别耦接到第一和第二接地电容器(c2、c1)。

[0060]

第一ndr器件(x2)具有通过第一负载电阻器rl1连接到神经元电路26的输入节点32的第一节点38和连接到第一电压源42的第二节点40。第一ndr器件x2的第一节点38耦接至第一接地电容器c2。第二ndr器件(x1)具有通过第二负载电阻器rl2连接到第一ndr器件x2的第一节点38的第一节点30和连接到第二电压源36的第二节点34。第二ndr器件x1的第一节点30耦接至第二接地电容器c2l。第二ndr器件x1的第一节点30是神经元电路26的输出节点44。

[0061]

神经元电路26的第一电压源42是正电压源,而第二电压源36是负电压源。如上所述,由电压源36和42提供的电压

‑

vdc、 vdc可以具有相同的幅度或者其可以具有不同的幅度。

[0062]

第一和第二ndr器件x2、x1中的每一个可以在其第一节点(分别为38、30)和第二节点(分别为40、34)之间包括与ndr材料串联的电阻(分别为re1、re2)。第一和第二ndr器件x2、x1的ndr材料可以是二氧化钒的层或薄膜,例如与先前针对神经元电路20详细说明的层或薄膜相同。

[0063]

re1可以具有几百欧姆的值,并且可以是布置在第一节点(38)和x2的ndr材料的第一侧之间的第一金属纳米线电极以及布置在第二节点(40)和x2的ndr材料的第二侧之间的第二金属纳米线电极的累积电阻。类似地,re2可以具有几百欧姆的值,并且可以是布置在第一节点(30)和x1的ndr材料的第一侧之间的第一金属纳米线电极以及布置在第二节点(34)和x1的ndr材料的第二侧之间的第二金属纳米线电极的累积电阻。

[0064]

二氧化钒层可以通过由五氧化二钒层电铸而产生,如美国专利申请no.15/417,049(提交于2017年1月26日,上面的参考文献[8])中详述的,该申请通过引用并入本文。

[0065]

或者,二氧化钒层可以通过各种薄膜沉积方法直接制备,包括但不限于钒金属或氧化钒靶的反应直流或射频磁控溅射、原子层沉积接着沉积后退火、或金属前体氧化。

[0066]

第一和第二电压源(42,36)被布置成使第一和第二ndr器件(x2、x1)接近其各自的莫特绝缘体到金属的转变,并且可以调节电压偏置以设置用于神经元动作电位生成(尖峰激发)和期望信号增益的期望电压或电流阈值电平。第一负载电阻器、第一ndr器件、第一电压源和第一接地电容器被布置成形成第一张弛振荡器,第二负载电阻器、第二ndr器件、第二电压源和第二接地电容器被布置成形成第二张弛振荡器。

[0067]

神经元电路20和26中的一个或多个可以用在具有多个连接在网络中的神经元电路的神经电路中,例如图1a所示,并且例如,如图1b所示(参考文献[7]:提交于2018年5月10日的美国专利申请no.15/976,687)。

[0068]

vo

2 ndr器件的基于莫特imt物理的spice模型用于分别模拟图1e和图1f中所示的兴奋性神经元电路和抑制性神经元电路。在spice模型中,vo2传导通道被建模为具有28~56nm的半径和50~100nm的长度的圆柱形体积。这些尺寸接近于电铸vo

2 ndr器件(参见2017年1月26日提交的美国专利申请15/417,049,上文参考文献[8])或无电铸vo

2 ndr器件中的实验观测值。

[0069]

注意到图1e中的兴奋性神经元电路20和图1f中的抑制性神经元电路26都是紧张性(tonic)神经元电路。根据本说明书的实施例,并且如下文所详述的,通过用电容器或与电阻器串联的电容器替换输入负载电阻器(20中的rl1或26中的rl2),可以使紧张性神经元电路20和26成为时相性(phasic)。

[0070]

如图1a中所示,每个兴奋性忆阻器神经元电路53可以用图1e中的兴奋性神经元电路来实现,并且每个抑制性忆阻器神经元电路54可以用图1f中的抑制性神经元电路来实现。兴奋性输出忆阻器神经元57也可以用图1e中的兴奋性神经元电路来实现。

[0071]

突触电路55和56可以是无源忆阻器突触电路。无源忆阻器的一个示例在如下文献中有描述:参考文献[9]yoon,j.h.,zhang,j.,ren,x.,wang,z.,wu,h.,li,z.,barnell,m.,wu,q.,lauhon,l.j.,xia,q.,和yang,j.j.,“具有预调节导电隧穿路径的真正无电铸和低能忆阻器(truly electroforming

‑

free and low

‑

energy memristors with preconditioned conductive tunneling paths)。”,先进功能材料(advanced functional materials)第27期,第1702010页(2017),其内容通过引用结合于此。

[0072]

在本公开中,每个无源忆阻器突触电路可以是电阻值为正值的2端电阻器。

[0073]

图1d示出抑制性忆阻器神经元电路54的输入70和输出72处的典型模拟尖峰波形。图1d还示出兴奋性忆阻器神经元电路53的输入74和输出76处的典型模拟尖峰波形。一个值得注意的特征是,如果输入74低于阈值或在阈值以下,如为负输入,则兴奋性忆阻器神经元电路53不启动,而如果输入70高于阈值或在阈值以上,如为零或正输入,则抑制性忆阻器神经元电路54不启动。

[0074]

为了评估和基准测试如图1c中所示的双极性全忆阻器卷积电路的存储器内计算性能,使用定制的卷积神经网络(cnn)图像分类模型,采用matlab神经网络工具箱对mnist图像集进行分类。在cnn模型中使用流行的随机梯度下降法训练卷积核(滤波器)权重。然后将预训练的卷积核权值转换为双象限突触电导值,该值可以是正的也可以是负的。

[0075]

图2中示出了转换算法,如下所述。

[0076]

1、在步骤80中,来自第k个卷积核的预训练的cnn权重元素w(i,j)(i和j是2d权重矩阵的行和列索引)。

[0077]

2、在步骤82中,使用线性转换方案将预训练的cnn权重元素w(i,j)转换为突触权重g(i,j),使得g(i,j)=(w(i,j)x 1.2e

‑6)/max(w(i,j))。

[0078]

3、在步骤84中确定g(i,j)是正还是负。

[0079]

4、在步骤86中,如果突触权重g(i,j)为零或正,则将抑制性突触的电导g

inh

(i,j)设置为下界值(例如,下界值可以是2mω的电阻),并且将兴奋性突触的电导g

exc

(i,j)设置为使得总电导g(i,j)(g

inh

(i,j)和g

exc

(i,j)的带符号求和)等于步骤82中的突触权重的值。

[0080]

5、在步骤88中,如果突触权重g(i,j)为负,则将兴奋性突触的电导g

exc

(i,j)设置为下界值(例如,下界值可以是2mω的电阻),并且将抑制性突触的电导g

inh

(i,j)设置为使得总电导g(i,j)(g

inh

(i,j)和g

exc

(i,j)的带符号求和)等于步骤82中的突触权重的值。

[0081]

图3a和图3b示出了图1c中的双极性全忆阻器卷积电路的250个兴奋性忆阻器突触和250个抑制性忆阻器突触的计算电阻值的示例集合,使用图2中的算法从定制matlab cnn模型的预训练的卷积核权重转换而来。在评估双极性全忆阻器卷积电路和方法时,使用了与参考文献[1]中描述的相同的基于速率的数据编码方案和基准测试方法。

[0082]

图4示出了用于基准测试的定制matlab cnn图像分类模型。该模型被设计成对28x28像素灰度(256级)mnist手写数字输入图像60进行分类。mnist图像集90具有总共10,000个图像并且具有总共10个图像类别100(对于数字0至9)。该简化的cnn模型包括具有用于特征提取的10(5x5)个卷积核94(滤波器)的一个卷积层92、两个非线性(“nl”)层96和98、

以及一个完全连接的神经网络(nn)层95,该模型的输出是层4,附图标记为97。卷积之后的第一非线性层96基于整流线性单元(relu)变换。完全连接的层95执行乘法和求和。最终非线性层98执行赢者全取(winner take all,wta)操作,其中仅选择十个输出中具有最高输出值的一个输出类别作为最终输出类别。为了简单起见,没有使用批量标准化层或池化层(最初是层3)。忽略这些层不会使图像分类精度劣化(训练后达到93.4%的精度)。在模拟的基准测试中,卷积层92由全忆阻器卷积电路实现,如图1b所示,并且通过spice模拟器(cadence verilog ams)模拟。将模拟的尖峰域中的卷积层激活(输出)转换回并加载到matlab cnn模型的其余部分,以使用matlab数值计算来完成图像分类过程。

[0083]

mnist图像分类所需的乘法和累加(mac)(或可比较的)数值运算的数目对于层1、卷积层92是144,000个mac,对于层2、relu非线性层96是5,760个运算,以及对于层4、完全连接的层95是57,600个mac。显然,卷积层92是cnn模型中计算最密集的部分。在这个行业中使用的更复杂的深cnn模型也是如此。

[0084]

图5示出了简化(无池化)matlab cnn模型的示例基准测试操作,如图4所示,用于图像分类基准测试。在该示例中,输入90是手写数字(数字“2”)的28x28像素mnist图像。具有10个5x5双极性卷积核的卷积层92由具有50x10无源忆阻器突触55和56的忆阻器神经突触卷积电路模拟(在cadence verilog ams中),如图1b中所示。模拟的忆阻器卷积输出是10个24x24像素输出图像94,并且它们中的两个在图5中示出。然后将图像94发送回matlab模型以计算分类输出。非线性分类器层即层4 98具有十个输出,每个数字类别100一个输出。十个输出中的最高值(本例中为10.9178)指向数字“2”的正确类别。

[0085]

图6示出了一个表格,这是对基准测试分析的总结。模拟的每输入比特的全忆阻器卷积能量效率为0.52nj/b,转化为每输入比特的总图像分类能量效率为0.61nj/b,这比现有技术cmos神经形态处理器(ibm truenorth,6.7nj/b)提高了10倍。

[0086]

图1b中所示的用于双极性(双象限)卷积的(50x10)无源忆阻器交叉阵列的模拟忆阻器卷积吞吐量约为7.5mb/s。作为比较,现有技术cmos神经形态处理器具有30.7mb/s的图像分类吞吐量。这表明,本发明的电路仅使用4个副本的这种(50x10)忆阻器交叉阵列,总突触计数仅为4x50x10=2000,就可以与现有技术的吞吐量相媲美。现有技术的truenorth芯片在其基准测试中使用了4096个神经突触核心中的4042个。每个truenorth神经突触核心包含(256x256)=65536个突触,使使用的突触总数达到约2.65亿个。这表明对于truenorth相比于使用本发明的电路,为了实现类似的吞吐量,突触计数比为1.32x105。所需突触计数中的如此大的对比可以由操作尖峰速率中的大差异来解释,操作尖峰速率对于本发明具有约100mhz的速率,而对于现有技术(truenorth)仅具有约200hz的速率。

[0087]

注意,si现有技术(truenorth)使用更复杂的cnn模型用于图像分类基准测试,其涉及更多卷积层和乘法和累加(mac)操作。因此,比较与架构无关的能量使用或每次操作的焦耳(j/op)是有帮助的。但是,truenorth没有这个数字。在本发明中,每个mac运算的模拟全忆阻器能量使用为~6pj/op。该值基于对每个输出像素的基于速率的卷积计数~40个尖峰。这是确保尖峰速率准确性的相当保守的实践。在每个输出像素计算~4个尖峰卷积的最佳情况下,每次运算的全忆阻器能量使用可以达到~0.6pj/op。从而使得可以访问用于近似计算应用的亚pj/op机制。注意,该估计基于0.4pj/尖峰vo2神经元能量效率,这不是本技术的下限。

[0088]

根据专利法的要求描述了本发明,本领域的技术人员将理解如何对本发明进行改变和修改,以满足其特定的要求或条件。可以在不背离如本文所公开的本发明的范围和精神的情况下进行这样的改变和修改。

[0089]

上述示例性和优选实施例的详细描述是用于说明目的和根据法律要求进行公开。其并非旨在穷举或将本发明限制于所描述的精确形式,而是仅使本领域技术人员能够理解本发明如何适合于特定用途或实施。修改和变化的可能性对于本领域技术人员将是显而易见的。对可能具有包括公差、特征尺寸、特定操作条件、工程规范等的示例性实施例的描述并不意图进行限制,并且其可以在实现之间变化或者随着对现有技术的改变而变化,并且不应当由此暗示限制。申请人已经针对现有技术进行了本公开,但是也考虑了改进,并且在未来的修改可以考虑这些改进,即根据现有技术的现有技术。本发明的范围由权利要求书限定为书面的和可适用的等同物。除非明确说明,否则以单数形式提及权利要求要素并不意味着“一个且仅一个”。此外,本公开中的元件、组件或方法或工艺步骤都不旨在专用于公众,而不管所述元件、组件或步骤是否在权利要求书中明确地陈述。本文中的任何权利要求要素都不应被解释为按照35u.s.c.第112节,第六段中所规定的内容,除非该要素是使用短语“用于

……

的装置”明确地陈述的,并且本文件中的任何方法或工艺步骤都不得根据这些规定解释,除非该一个或多个步骤明确陈述“包括以下步骤

…”

。

[0090]

广义地,本技术公开了至少如下内容:一种用于执行能量高效且高吞吐量乘法

‑

累加(mac)算术点积运算和卷积计算的电路,包括二维交叉阵列,该二维交叉阵列包括多个行输入和具有多个列电路的至少一列,其中,每个列电路耦接到相应的行输入。每个相应列电路包括:兴奋性忆阻器神经元电路,其具有耦接到相应行输入的输入;第一突触电路,其耦接到所述兴奋性忆阻器神经元电路的输出,所述第一突触电路具有第一输出;抑制性忆阻器神经元电路,其具有耦接到相应行输入的输入;以及第二突触电路,其耦接到所述抑制性忆阻器神经元电路的输出,所述第二突触电路具有第二输出。输出忆阻器神经元电路耦接到每个列电路的第一输出和第二输出,并且具有输出。

[0091]

概念

[0092]

已经公开了至少以下概念。

[0093]

概念1.一种用于执行能量高效且高吞吐量乘法

‑

累加(mac)算术点积运算和卷积计算的电路,包括:

[0094]

二维交叉阵列,其包括多个行输入和具有多个列电路的至少一列,其中,每个列电路耦接到相应的行输入;

[0095]

其中,每个相应列电路包括:

[0096]

兴奋性忆阻器神经元电路,其具有耦接到相应行输入的输入;

[0097]

第一突触电路,其耦接到所述兴奋性忆阻器神经元电路的输出,所述第一突触电路具有第一输出;

[0098]

抑制性忆阻器神经元电路,其具有耦接到相应行输入的输入;以及

[0099]

第二突触电路,其耦接到所述抑制性忆阻器神经元电路的输出,所述第二突触电路具有第二输出;以及

[0100]

输出忆阻器神经元电路,其耦接到每个列电路的第一输出和第二输出,所述输出忆阻器神经元电路具有输出。

[0101]

概念2.根据概念1所述的电路,

[0102]

其中,每个第一突触电路和每个第二突触电路包括无源忆阻器突触电路。

[0103]

概念3.根据概念1或2所述的电路,

[0104]

其中,每个相应的兴奋性忆阻器神经元电路和耦接到相应的兴奋性忆阻器神经元电路的相应的第一突触电路具有正卷积权重或零卷积权重;并且

[0105]

其中,每个相应的抑制性忆阻器神经元电路和耦接到相应的抑制性忆阻器神经元电路的相应的第二突触电路具有负卷积权重。

[0106]

概念4.根据概念1、2或3所述的电路,其中,每个相应的兴奋性忆阻器神经元电路包括:

[0107]

第一负差分电阻(ndr)器件,其利用第一电压源发生偏置;

[0108]

第二负差分电阻(ndr)器件,其利用第二电压源发生偏置,其中,所述第一电压源和所述第二电压源极性相反;

[0109]

第一电容器,其耦接到地电位且耦接到所述第一ndr器件的第一节点;

[0110]

第一负载电阻器,其耦接在所述兴奋性有源忆阻器神经元电路或自兴奋性有源忆阻器输出神经元电路的输入节点与所述第一电容器之间;

[0111]

第二电容器,其耦接到地电位;以及

[0112]

第二负载电阻器,其耦接于所述第一电容器与所述第二电容器之间,且耦接至所述第二ndr器件的第一节点;

[0113]

其中,所述第二ndr器件的第一节点形成所述兴奋性有源忆阻器神经元电路或所述自兴奋性有源忆阻器输出神经元电路的输出节点;

[0114]

其中,所述第一电压源是负电压源;并且

[0115]

其中,所述第二电压源是正电压源。

[0116]

概念5.根据概念4所述的电路,所述电路还包括:

[0117]

第三负载电阻器,其耦接于所述第一电容器与所述第一ndr器件的所述第一节点之间;以及

[0118]

第四负载电阻器,其耦接于所述第二电容器与所述第二ndr器件的第一节点之间。

[0119]

概念6.根据概念4所述的电路,其中,

[0120]

所述第一ndr器件和所述第二ndr器件中的至少一个包括二氧化钒层。

[0121]

概念7.根据概念4所述的电路,其中,

[0122]

所述第一电压源和所述第二电压源被配置为使所述第一负差分电阻(ndr)器件和所述第二负差分电阻(ndr)器件接近其各自的莫特绝缘体到金属的转变。

[0123]

概念8.根据概念1、2、3、4、5、6或7所述的电路,其中,每个相应的抑制性忆阻器神经元电路包括:

[0124]

第一负差分电阻(ndr)器件,其利用第一电压源发生偏置;

[0125]

第二负差分电阻(ndr)器件,其利用第二电压源发生偏置,其中,所述第一电压源和所述第二电压源极性相反;

[0126]

第一电容器,其耦接到地电位且耦接到所述第一ndr器件的第一节点;

[0127]

第一负载电阻器,其耦接在所述抑制性有源忆阻器神经元电路的输入节点和所述第一电容器之间;

[0128]

第二电容器,其耦接到地电位;以及

[0129]

第二负载电阻器,其耦接于所述第一电容器与所述第二电容器之间,且耦接至所述第二ndr器件的第一节点;

[0130]

其中,所述第二ndr器件的第一节点形成所述抑制性有源忆阻器神经元电路的输出节点;

[0131]

其中,所述第一电压源是正电压源;并且

[0132]

其中,所述第二电压源是负电压源。

[0133]

概念9.根据概念8所述的电路,所述电路还包括:

[0134]

第三负载电阻器,其耦接于所述第一电容器与所述第一ndr器件的所述第一节点之间;以及

[0135]

第四负载电阻器,其耦接于所述第二电容器与所述第二ndr器件的第一节点之间。

[0136]

概念10.根据概念8所述的电路,其中,

[0137]

所述第一ndr器件和所述第二ndr器件中的至少一个包括二氧化钒层。

[0138]

概念11.根据概念8所述的电路,其中,

[0139]

所述第一电压源和所述第二电压源被配置为使所述第一负差分电阻(ndr)器件和所述第二负差分电阻(ndr)器件接近其各自的莫特绝缘体到金属的转变。

[0140]

概念12.根据概念1、2、3、4、5、6、7、8、9、10或11所述的电路,

[0141]

其中,所述二维交叉阵列还包括多个列,其中,每一列具有多个列电路,并且相应列中的每个列电路耦接到相应行输入。

[0142]

概念13.根据概念1、2、3、4、5、6、7、8、9、10、11或12所述的电路,

[0143]

其中,如果耦接到相应的兴奋性忆阻器神经元电路的相应行输入低于阈值或具有负值,则相应的兴奋性忆阻器神经元电路不激发;并且

[0144]

其中,如果耦接到相应的兴奋性忆阻器神经元电路的相应行输入高于阈值或具有正值,则相应的抑制性忆阻器神经元电路不激发。

[0145]

概念14.一种设置兴奋性忆阻器突触电路和抑制性忆阻器突触电路的电导值的方法,包括:

[0146]

使用流行的随机梯度下降法来训练卷积核权重;以及

[0147]

通过以下操作将第k个卷积核的经训练的卷积核权重元素w(i,j)转换为双象限突触电导值,其中,i和j是二维权重矩阵的行和列索引,所述双象限突触电导值可以是正的或负的:

[0148]

使用线性转换方案将经训练的卷积核权重元素w(i,j)转换为突触权重g(i,j)使得g(i,j)=(w(i,j)x 1.2e

‑6)/max(w(i,j));

[0149]

确定g(i,j)是正还是负;并且

[0150]

如果突触权重g(i,j)是零或正,则将相应抑制性忆阻器突触电路的电导g

inh

(i,j)设置为第一下界值,并且将相应兴奋性忆阻器突触电路的电导g

exc

(i,j)设置为使得总电导g(i,j)或g

inh

(i,j)和g

exc

(i,j)的带符号和等于w(i,j)x1.2e

‑6)/max(w(i,j)的值;

[0151]

如果突触权重g(i,j)为负,则将相应兴奋性忆阻器突触电路的电导g

exc

(i,j)设置为第二下限值,并将相应抑制性忆阻器突触电路的电导g

inh

(i,j)设置为使得总电导g(i,j)或g

inh

(i,j)和g

exc

(i,j))的带符号和等于w(i,j)x 1.2e

‑6)/max(w(i,j)的值。

[0152]

概念15.根据概念14所述的方法,

[0153]

其中,所述第一下界值为

[0154]

g

inh

(i,j)=0.5e

‑6;并且

[0155]

其中,所述第二下界值为

[0156]

g

exc

(i,j)=0.5e

‑6。

[0157]

概念16.一种用于执行能量高效且高吞吐量乘法

‑

累加(mac)算术点积运算和卷积计算的方法,包括:

[0158]

提供二维交叉阵列,其包括多个行输入和具有多个列电路的至少一列,其中,每个列电路耦接到相应的行输入;

[0159]

其中,每个相应列电路包括:

[0160]

兴奋性忆阻器神经元电路,其具有耦接到相应行输入的输入;

[0161]

第一突触电路,其耦接到所述兴奋性忆阻器神经元电路的输出,所述第一突触电路具有第一输出;

[0162]

抑制性忆阻器神经元电路,其具有耦接到相应行输入的输入;以及

[0163]

第二突触电路,其耦接到所述抑制性忆阻器神经元电路的输出,所述第二突触电路具有第二输出;以及

[0164]

提供输出忆阻器神经元电路,其耦接到每个列电路的第一输出和第二输出,所述输出忆阻器神经元电路具有输出。

[0165]

概念17.根据概念16所述的方法,

[0166]

其中,每个相应的兴奋性忆阻器神经元电路和耦接到相应的兴奋性忆阻器神经元电路的相应的第一突触电路具有正卷积权重或零卷积权重;并且

[0167]

其中,每个相应的抑制性忆阻器神经元电路和耦接到相应的抑制性忆阻器神经元电路的相应的第二突触电路具有负卷积权重。

[0168]

概念18.根据概念16或17所述的方法,其中,每个相应的兴奋性忆阻器神经元电路包括:

[0169]

第一负差分电阻(ndr)器件,其利用第一电压源发生偏置;

[0170]

第二负差分电阻(ndr)器件,其利用第二电压源发生偏置,其中,所述第一电压源和所述第二电压源极性相反;

[0171]

第一电容器,其耦接到地电位且耦接到所述第一ndr器件的第一节点;

[0172]

第一负载电阻器,其耦接在所述兴奋性有源忆阻器神经元电路或自兴奋性有源忆阻器输出神经元电路的输入节点与所述第一电容器之间;

[0173]

第二电容器,其耦接到地电位;以及

[0174]

第二负载电阻器,其耦接于所述第一电容器与所述第二电容器之间,且耦接至所述第二ndr器件的第一节点;

[0175]

其中,所述第二ndr器件的第一节点形成所述兴奋性有源忆阻器神经元电路或所述自兴奋性有源忆阻器输出神经元电路的输出节点;

[0176]

其中,所述第一电压源是负电压源;并且

[0177]

其中,所述第二电压源是正电压源。

[0178]

概念19.根据概念16、17或18所述的方法,其中,每个相应的抑制性忆阻器神经元

电路包括:

[0179]

第一负差分电阻(ndr)器件,其利用第一电压源发生偏置;

[0180]

第二负差分电阻(ndr)器件,其利用第二电压源发生偏置,其中,所述第一电压源和所述第二电压源极性相反;

[0181]

第一电容器,其耦接到地电位且耦接到所述第一ndr器件的第一节点;

[0182]

第一负载电阻器,其耦接在所述抑制性有源忆阻器神经元电路的输入节点和所述第一电容器之间;

[0183]

第二电容器,其耦接到地电位;以及

[0184]

第二负载电阻器,其耦接于所述第一电容器与所述第二电容器之间,且耦接至所述第二ndr器件的第一节点;

[0185]

其中,所述第二ndr器件的第一节点形成所述抑制性有源忆阻器神经元电路的输出节点;

[0186]

其中,所述第一电压源是正电压源;并且

[0187]

其中,所述第二电压源是负电压源。

[0188]

概念20.根据概念16、17、18或19所述的方法,

[0189]

其中,所述二维交叉阵列还包括多个列,其中,每一列具有多个列电路,并且相应列中的每个列电路耦接到相应行输入。

[0190]

概念21.根据概念16、17、18、19或20所述的方法,

[0191]

其中,如果耦接到相应的兴奋性忆阻器神经元电路的相应行输入低于阈值或具有负值,则相应的兴奋性忆阻器神经元电路不激发;并且

[0192]

其中,如果耦接到相应的兴奋性忆阻器神经元电路的相应行输入高于阈值或具有正值,则相应的抑制性忆阻器神经元电路不激发。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。