一种具有隐埋层的brt及其制造方法

技术领域

1.本发明属于电力半导体器件技术领域,涉及一种具有隐埋层的brt,本发明还涉及该种具有隐埋层的brt的制造方法。

背景技术:

2.基区电阻控制晶闸管(brt)是在现有mos控制晶闸管(mct)的基础上开发的另一种mos栅控晶闸管。相对于mct而言,虽然brt的制作工艺大大简化,但在低电流下仍存在一种非常严重的电压折回(snapback)现象,导致其开通速度较慢,开通损耗较大。

技术实现要素:

3.本发明的目的是提供一种具有隐埋层的brt,解决了现有技术的brt由于结构的局限,导致开通速度较慢,开通损耗较大的问题。

4.本发明的另一目的是提供该种具有隐埋层的brt的制造方法。

5.本发明采用的技术方案是,一种具有隐埋层的brt,以n

‑

漂移区作为衬底,在n

‑

漂移区上部中间位置设置有p基区,在p基区上部中间位置设置有n

阴极区;在n

‑

漂移区上部的p基区的两侧分别设置有与p基区两侧相接触的隐埋层;在隐埋层上方靠外侧设置有p

分流区,两侧的p

分流区上表面的铝层与n

阴极区上表面中间位置的铝层相连构成阴极k;部分n

阴极区、p基区及部分p

分流区的上表面共同设置有一层栅氧化层,在栅氧化层上表面设置有重掺杂的多晶硅层,该多晶硅层作为栅极g;在阴极k与栅极g之间设置有磷硅玻璃层psg;在n

‑

漂移区下表面设置有nfs层,在nfs层下表面设置有p

阳极区,在p

阳极区的下表面设置有多层的金属化阳极a;

6.该隐埋层选用n型的掺杂层作为载流子存储层,简称隐埋n型载流子存储层;或者选用隐埋二氧化硅层作为载流子阻挡层,简称埋氧层。

7.本发明采用的另一技术方案是,一种具有隐埋层的brt的制造方法,按照以下步骤具体实施:

8.步骤1、选用原始的高阻区熔中照硅单晶抛光片作为n

‑

漂移区,进行预先处理,在处理后的n

‑

漂移区下表面,先采用磷离子注入,退火兼推进,在下表面形成nfs层;

9.步骤2、去掉步骤1处理后的硅片表面的氧化层,采用干氧氧化形成上、下表面的牺牲氧化层;

10.步骤3、对步骤2处理后的硅片上表面进行光刻,形成p基区以及终端场环区的硼离子注入窗口,采用光刻胶掩蔽进行硼离子注入;然后,在下表面也进行硼离子注入,去胶后进行高温退火兼推进,在硅片上表面形成选择性p基区,使得下表面形成p

阳极区;

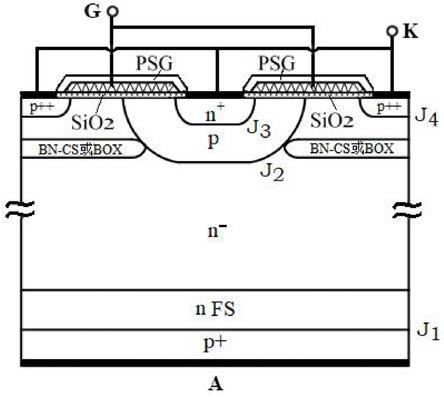

11.步骤4、在步骤3处理后的硅片的上表面,通过光刻形成与p基区注入窗口完全相同的n

阴极区的磷离子注入窗口,然后采用光刻胶掩蔽进行磷离子注入,去胶后高温推进兼退火,形成n

阴极区,实现自对准的n沟道;

12.步骤5、在步骤4处理后的硅片的上表面,通过光刻形成n型隐埋层的离子注入窗

口,利用光刻胶掩蔽进行高能磷离子或者氧离子注入,采用倒掺杂工艺形成隐埋n型载流子存储层bn

‑

cs或者隐埋二氧化硅层box;

13.步骤6、去掉步骤5处理后的硅片表面的氧化层,重新进行干氧氧化,然后采用化学气相淀积形成多晶硅层,并掺杂;

14.步骤7、在步骤6处理后的硅片上表面进行光刻,去掉多晶硅层并保留栅极氧化层,形成p

分流区的硼离子注入窗口,然后采用光刻胶掩蔽进行硼离子注入,去胶后进行退火,形成p

分流区;

15.步骤8、在步骤7处理后的硅片上表面淀积磷硅玻璃,并在高温下回流实现元胞表面平整化;

16.步骤9、在步骤8处理后的硅片的上表面光刻形成阴极接触孔,二次回流,然后上表面淀积金属铝层并反刻,下表面依次溅射铝、钛、镍、银四层金属化膜,经合金化后,上表面形成金属化的阴极k、下表面形成多层金属化阳极a;

17.步骤10、对步骤9处理后的硅片的上表面甩聚酰亚胺膜,通过光刻形成栅极和阴极的压焊区图形,并进行聚酰亚胺固化处理,终端区表面钝化保护,划片,即成。

18.本发明的有益效果是,隐埋层的引入能够在器件导通时起到阻挡空穴从p

分流区抽取的作用,使器件产生类似于igbt的电子注入增强(ie)效应,加速晶闸管导通,从而抑制电压折回现象。该发明具有很低的通态压降和较快的关断速度,制作工艺与igbt完全兼容,工艺成本低,适于实际应用。本发明的器件结构,不仅驱动电路简单,而且具有低的通态压降及快的开关速度,同时能够有效抑制brt的电压折回(snapback)现象,改善通态压降与关断能耗的折衷关系。

附图说明

19.图1为现有技术的基区电阻控制晶闸管(brt)的基本结构示意图;

20.图2为本发明具有隐埋层的brt的基本结构示意图;

21.图3为本发明具有隐埋n型载流子存储层的brt(以下简称bn

‑

cs

‑

brt)和具有隐埋二氧化硅层的brt(以下简称box

‑

brt)与现有技术的brt在常温(300k)和高温(400k)下的正向阻断特性曲线;

22.图4为本发明bn

‑

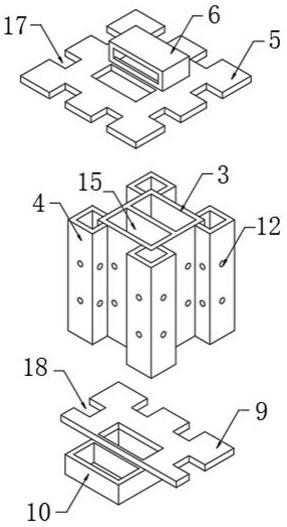

cs

‑

brt和box

‑

brt与现有技术的brt在常温(300k)和高温(400k)时的通态特性对比曲线;

23.图5为本发明bn

‑

cs

‑

brt和box

‑

brt与现有技术的brt阴极侧电子注入效率γ

n

随阴极电流密度j

k

的变化曲线对比;

24.图6为本发明bn

‑

cs

‑

brt和box

‑

brt与现有技术的brt阳极侧空穴注入效率γ

p

随阳极电流密度j

a

的变化曲线对比;

25.图7是本发明bn

‑

cs

‑

brt的隐埋n型载流子存储层的浓度对器件通态压降v

t

和击穿电压v

br

的影响;

26.图8是本发明bn

‑

cs

‑

brt的隐埋n型载流子存储层的厚度对器件通态压降v

t

和击穿电压v

br

的影响;

27.图9是本发明bn

‑

cs

‑

brt和box

‑

brt与现有技术的brt通态压降与少子寿命τ

p0

的关系曲线;

28.图10是本发明bn

‑

cs

‑

brt和box

‑

brt与现有技术的brt通态压降与关断损耗的折衷关系曲线对比图;

29.图11是本发明bn

‑

cs

‑

brt的隐埋n型载流子存储层与p基区的横向间距偏差δx对器件通态压降v

t

和击穿电压v

br

的影响;

30.图12是本发明bn

‑

cs

‑

brt的隐埋n型载流子存储层与p

分流区的纵向间距δy对器件通态压降v

t

和击穿电压v

br

的影响;

31.图13是本发明box

‑

brt的埋氧层与p基区的横向间距偏差δx对器件通态压降v

t

和击穿电压v

br

的影响;

32.图14是本发明box

‑

brt的埋氧层与p

分流区的纵向间距δy对器件通态压降v

t

和击穿电压v

br

的影响;

33.图15是本发明具有隐埋层的brt的制作工艺流程示意图。

具体实施方式

34.下面结合附图和具体实施方式对本发明进行详细说明。

35.参照图1,现有技术的基区电阻控制晶闸管(brt)的主体结构是,由n

阴极区、p基区、n

‑

漂移区、nfs层和p

阳极区构成,其中,p

分流区与n

阴极区通过铝层相连形成阴极;重掺杂的多晶硅层与其下方的栅氧化层和n

‑

漂移区、p基区分别形成pmos和nmos,由同一个栅极电压控制。

36.参照图2,本发明具有隐埋层的brt的结构是,整个器件以n

‑

漂移区作为衬底,在n

‑

漂移区上部中间位置设置有p基区,在p基区上部中间位置设置有n

阴极区;在n

‑

漂移区上部的p基区的两侧分别设置有与p基区两侧相接触的隐埋层,该隐埋层选用n型的掺杂层或二氧化硅层,该隐埋层就是指图2中显示的bn

‑

cs或box;在隐埋层上方靠外侧设置有p

分流区,两侧的p

分流区上表面的铝层与n

阴极区上表面中间位置的铝层相连构成阴极k;部分n

阴极区、p基区及部分p

分流区的上表面共同设置有一层栅氧化层,在栅氧化层上表面设置有重掺杂的多晶硅层,该多晶硅层作为栅极g;在阴极k与栅极g之间设置有磷硅玻璃层(psg);在n

‑

漂移区下表面设置有nfs层,在nfs层下表面设置有p

阳极区,在p

阳极区的下表面设置有多层的金属化阳极a。

37.对比图1、图2可见,本发明brt器件结构相比现有技术的brt结构不同的是,本发明在n

‑

漂移区上方的p基区的两侧,分别设置了与p基区两侧相接触的隐埋层(即bn

‑

cs或box),该隐埋层选用n型的掺杂层作为载流子存储层(简称隐埋n型载流子存储层,bn

‑

cs)或者隐埋二氧化硅层(简称埋氧层,box)作为载流子阻挡层。

38.隐埋n型载流子存储层的浓度是1

×

10

15

cm

‑3~9

×

10

15

cm

‑3,厚度是0.6μm~2μm;隐埋n型载流子存储层与p基区的横向间距偏差δx是

‑

0.25μm~1.2μm;隐埋n型载流子存储层与p

分流区的纵向间距δy是0.5μm~1.5μm。

39.隐埋二氧化硅层的厚度是0.5μm;隐埋二氧化硅层与p基区的横向间距偏差δx是

‑

0.5μm~1.5μm;隐埋二氧化硅层与p

分流区的纵向间距δ是0μm~1.5μm。

40.本发明brt器件结构的工作原理是:

41.当在栅

‑

阴极加的正电压大于阈值电压时,栅极下方p基区表面的n沟道形成,电子从n

阴极区经过n沟道注入到n

‑

漂移区,使n

‑

漂移区电位下降;当由p

阳极区与nfs层形成的

j1结的电位大于其开启电压时,p

阳极区开始向n

‑

漂移区注入空穴。阳极区注入的空穴除了与n沟道过来的电子复合外,会在隐埋层下方积累,并进入p基区,引起p基区的电位升高。若p基区电位升高并超过p基区与n

阴极区形成的j3结的开启电压时,n

阴极区开始向n

‑

漂移区注入电子,于是阴极侧的npn晶体管和阳极侧的pnp相互驱动。当两者的电流放大系数大于1时,主晶闸管开通,从而使器件的通态压降大大降低。可见,在导通的过程中,隐埋层有助于空穴在隐埋层下方及p基区内的积累,从而导致阴极侧产生电子注入增强,加快器件中晶闸管的导通,从而避免了电压折回(snapback)现象。

42.当栅极加负电压大于阈值电压时,栅极下方的n

‑

漂移区的表面形成p沟道,将p基区与p

分流区连通,于是空穴通过p沟道抽取到阴极,器件快速关断。若器件要使恢复到正向阻断状态下,仍需在栅

‑

阴极间加

‑

5v电压以维持p沟道,为泄漏电流提供通路。否则,无法维持较高的正向阻断电压。

43.特性验证

44.为了评价本发明具有隐埋层的brt的多个特性,以6.5kv电压等级为例,利用专业仿真软件对上述的具有两种隐埋层的brt在常温(300k)和高温(400k)下的正向阻断特性、导通特性及开关特性分别进行仿真,并与现有技术的brt的特性进行了对比。

45.1、正向阻断特性

46.参照图3,是本发明具有隐埋n型载流子存储层的brt(以下简称bn

‑

cs

‑

brt)和具有隐埋二氧化硅层的brt(以下简称box

‑

brt)与现有技术的brt在常温(300k)和高温(400k)下的正向阻断特性曲线。由图3可见,在300k室温时,三者的阻断电压均可达到7800v;在400k高温下,与现有技术的brt相比,本发明bn

‑

cs

‑

brt的阻断电压和漏电流均有所降低,而本发明box

‑

brt的阻断电压有所提高,同时漏电流显著下降。这就说明本发明box

‑

brt具有更好的阻断特性。

47.2、正向导通特性

48.参照图4,是本发明bn

‑

cs

‑

brt和box

‑

brt与现有技术的brt在常温(300k)和高温(400k)时的通态特性对比曲线。可见,本发明两种具有隐埋层brt的器件均可以有效抑制snapback现象,并且在阳极电流密度j

a

低于40a/cm2时box

‑

brt和bn

‑

cs

‑

brt的通态压降显著低于现有技术的brt。

49.参照图5,是本发明bn

‑

cs

‑

brt和box

‑

brt与现有技术的brt阴极侧电子注入效率γ

n

随阴极电流密度j

k

的变化曲线对比。由图5可见,本发明bn

‑

cs

‑

brt和box

‑

brt器件的阴极电子注入效率γ

n

高于现有技术的brt结构,并且box

‑

brt在大电流下更为显著,说明本发明box

‑

brt中的ie效应比bn

‑

cs

‑

brt更为强烈。

50.参照图6,是本发明bn

‑

cs

‑

brt和box

‑

brt与现有技术的brt阳极侧空穴注入效率γ

p

随阳极电流密度j

a

的变化曲线对比。由图6可见,本发明bn

‑

cs

‑

brt与现有技术的brt的阳极侧空穴注入效率γ

p

完全相同,而本发明box

‑

brt器件的阳极空穴注入效率γ

p

稍高于bn

‑

cs

‑

brt和现有技术的brt。

51.参照图7,是本发明bn

‑

cs

‑

brt和box

‑

brt与现有技术的brt在相同的阳极电流密度下通态压降v

t

与少子寿命τ

p0

的关系曲线对比。由图7可见,三种结构的通态压降均随基区载流子寿命的增加而减小,在相同的少子寿命下,现有技术的brt的v

t

最大,bn

‑

cs

‑

brt的v

t

次之,box

‑

brt的v

t

最低。这说明采用本发明bn

‑

cs

‑

brt和box

‑

brt可以改善器件通态压降。

52.参照图8,本发明bn

‑

cs

‑

brt和box

‑

brt与现有技术的brt在相同的寿命下关断能耗密度e

off

与通态压降v

t

的折衷关系曲线对比。由图8可见,box

‑

brt的通态特性与关断特性的折衷最好,bn

‑

cs

‑

brt次之,现有技术的brt较差。这说明采用本发明bn

‑

cs

‑

brt和box

‑

brt可以改善器件通态压降与关断能耗的折衷关系。

53.3、关键结构参数对器件特性的影响

54.影响器件特性的关键结构参数为隐埋n型载流子存储层的浓度和厚度以及位置或者埋氧层的位置。

55.参照图9,是本发明bn

‑

cs

‑

brt的隐埋n型载流子存储层的浓度对器件通态压降v

t

和击穿电压v

br

的影响。由图9可见,当n型载流子存储层的浓度从1

×

10

15

cm

‑3增大到1

×

10

16

cm

‑3,通态压降v

t

逐渐下降,击穿电压v

br

先缓慢下降,并当n型载流子存储层的浓度大于9

×

10

15

cm

‑3时v

br

急剧下降,此时v

t

很小。

56.参照图10,是本发明bn

‑

cs

‑

brt的隐埋n型载流子存储层的厚度对器件通态压降v

t

和击穿电压v

br

的影响。由图10可见,当n型载流子存储层的厚度从0.6μm增大到2.5μm时,通态压降v

t

逐渐下降,击穿电压v

br

也是先缓慢下降,但当n型载流子存储层的厚度大于2μm时v

br

急剧下降,此时v

t

也很小。

57.参照图11,是本发明bn

‑

cs

‑

brt的隐埋n型载流子存储层与p基区的横向间距偏差δx对器件通态压降v

t

和击穿电压v

br

的影响。由图11可见,当隐埋n型载流子存储层与p基区的横向间距偏差δx=0(即两者恰好相接)时,通态压降v

t

较低,同时击穿电压v

br

较高。当n型载流子存储层与p基区的横向间距偏差δx<0(即两者相交叠)时,随δx绝对值增大,通态压降v

t

变化很小,击穿电压v

br

急剧下降;当隐埋n型载流子存储层与p基区的横向间距置偏差δx>0(即两者不交叠)时,随δx值增大,通态压降v

t

逐渐增加,击穿电压v

br

几乎保持不变。

58.参照图12,是本发明bn

‑

cs

‑

brt的隐埋n型载流子存储层与p

分流区的纵向间距δy对器件通态压降v

t

和击穿电压v

br

的影响。由图12可见,随隐埋n型载流子存储层与p

分流区的纵向间距δy增加,通态压降v

t

逐渐增加,击穿电压v

br

先增加而后下降;当δy=1μm时,通态压降v

t

较低,同时击穿电压v

br

较高。

59.由上述图9、图10、图11、图12可知,隐埋n型载流子存储层的浓度越高、厚度越厚,导通特性越好,但阻断特性变差;隐埋n型载流子存储层与p基区的横向间距偏差δx越大,导通特性越好,阻断特性越差;隐埋n型载流子存储层与p

分流区的纵向间距δy越大,导通特性越差,阻断电压先增后减。故在实际制作工艺中,隐埋n型载流子存储层的浓度可以控制在2

×

10

15

cm

‑3~9

×

10

15

cm

‑3范围内,厚度可以控制在0.6μm~2.0μm范围内;隐埋n型载流子存储层与p基区的横向间距偏差δx可以控制在

‑

0.25μm~1.5μm,与p

分流区的纵向间距δy可以控制在0.5μm~2μm。

60.参照图13,是本发明box

‑

brt的埋氧层与p基区的横向间距偏差δx对器件通态压降v

t

和击穿电压v

br

的影响。由图13可见,当埋氧层与p基区的横向间距偏差δx<0(即两者相交叠)时,随δx绝对值增大,通态压降v

t

有所减小,击穿电压v

br

变化很小;当埋氧层与p基区的横向间距偏差δx>0(即两者不交叠)时,随δx值增大,通态压降v

t

明显增加,击穿电压v

br

增加较慢。

61.参照图14,是本发明box

‑

brt的埋氧层与p

分流区的纵向间距δy对器件通态压降

v

t

和击穿电压v

br

的影响;由图14可见,随埋氧层与p

分流区的纵向间距δy增加时,通态压降v

t

逐渐增大,击穿电压v

br

先稍有增加然后保持不变;当δy=0.2μm时,通态压降v

t

较低,同时击穿电压v

br

较高。

62.参照图13、图14,埋氧层与p基区的横向间距偏差越大,阻断特性越好,导通特性越差;埋氧层与p

分流区的纵向间距越大,阻断电压变化较小,导通特性越差。故在实际制作工艺中,埋氧层与p基区的横向间距偏差δx可控制在

‑

0.5μm~1.5μm,与p

分流区的纵向间距δy可以控制在0~1.5μm。

63.参照图15,本发明具有隐埋层的brt的制造方法,按照以下步骤具体实施:

64.步骤1、选用原始的高阻区熔中照硅单晶抛光片作为n

‑

漂移区,进行预先处理,在处理后的n

‑

漂移区下表面,先采用磷离子注入,退火兼推进,在下表面形成nfs层;

65.步骤2、去掉步骤1处理后的硅片表面的氧化层,采用干氧氧化形成上、下表面的牺牲氧化层;

66.步骤3、对步骤2处理后的硅片上表面进行光刻,形成p基区以及终端场环区(图15中未画出)的硼离子注入窗口,然后采用光刻胶掩蔽进行硼离子注入;然后,在下表面也进行硼离子注入,去胶后进行高温退火兼推进,在硅片上表面形成选择性p基区,使得下表面形成p

阳极区;

67.步骤4、在步骤3处理后的硅片的上表面,通过光刻形成与p基区注入窗口完全相同的n

阴极区的磷离子注入窗口,然后采用光刻胶掩蔽进行磷离子注入,去胶后高温推进兼退火,形成n

阴极区,实现自对准的n沟道;

68.步骤5、在步骤4处理后的硅片的上表面,通过光刻形成n型隐埋层的离子注入窗口,利用光刻胶掩蔽进行高能磷离子(p )或者氧离子(o )注入,采用倒掺杂工艺形成隐埋n型载流子存储层(bn

‑

cs)或者隐埋二氧化硅层(box);

69.步骤6、去掉步骤5处理后的硅片表面的氧化层,重新进行干氧氧化,然后采用化学气相淀积形成多晶硅层,并掺杂;

70.步骤7、在步骤6处理后的硅片上表面进行光刻,去掉多晶硅层并保留栅极氧化层,形成p

分流区的硼离子注入窗口,然后采用光刻胶掩蔽进行硼离子注入,去胶后进行退火,形成p

分流区;

71.步骤8、在步骤7处理后的硅片上表面淀积磷硅玻璃,并在高温下回流实现元胞表面平整化;

72.步骤9、在步骤8处理后的硅片的上表面光刻形成阴极接触孔,二次回流,然后上表面淀积金属铝层并反刻,下表面依次溅射铝、钛、镍、银四层金属化膜,经合金化后,上表面形成金属化的阴极k、下表面形成多层金属化阳极a;

73.步骤10、最后对步骤9处理后的硅片的上表面甩聚酰亚胺膜,通过光刻形成栅极和阴极的压焊区图形,并进行聚酰亚胺固化处理,终端区表面钝化保护,划片,即成。

74.参照图15,本发明器件在制造过程中,共需要进行五次离子注入:第一次是磷离子(p

)注入,在背面形成nfs层;第二次是硼离子(b

)注入,推进兼退火后在上表面形成选择性p基区以及终端的场环区、下表面形成p

阳极区;第三次是在p基区表面中央进行磷离子(p

)注入,推进兼退火后形成n

阴极区;第四次是在p基区两侧进行高能磷离子(p

)注入或氧离子(o

)注入,退火后形成隐埋的n型载流子存储层或埋氧层;第五次是在n

‑

漂移区表面p基区

两侧进行硼离子(b

)注入,退火后形成p

分流区。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。