1.本公开涉及存储器装置,且特定来说涉及用于耦合多个半导体装置的设备及方法。

背景技术:

2.近年来,已引入三维(3d)存储器装置。一些3d存储器装置是通过垂直地堆叠裸片且使用穿硅(或穿衬底)通路(tsv)及/或引线接合耦合裸片而形成。因此,3d存储器也可被称为“堆叠式存储器”。3d存储器可提供比非3d存储器更大的存储器容量及/或更高的带宽而面积增加更少。实例3d存储器装置包含混合存储器立方体(hmc)、高带宽存储器(hbm)及主从式存储器(msm),其中的每一者可包含在堆叠中彼此耦合的多个动态随机存取存储器(dram)裸片。

3.存储器装置可经耦合到将命令、地址及数据信号提供到堆叠式裸片以存取存储器的外部电路。堆叠式裸片通常在最低高度裸片处耦合到外部电路,其中级联接合向上连接到所述堆叠中的其余裸片。

4.然而,随着存储器速度的增加,到达所述堆叠中的最低高度裸片与最高高度裸片的信号之间的延迟变得不可忽略。通常通过基于最坏情况(即,所述堆叠中的最高高度裸片处的信号到达时间)设置存储器装置的操作时序来适应到达信号的时序差异。这种方法可能导致存储器装置的性能降低。另外,随着存储器速度继续增加,从所述堆叠中的最低裸片到最高裸片的信号到达时间的时序差异对于所要系统性能可能不再是可容忍的。

技术实现要素:

5.根据本公开的一方面,公开一种设备。所述设备包括:多个存储器装置,其包含第一、第二及第三存储器装置,所述第一存储器装置包含第一接合垫,所述第二存储器装置包含第二接合垫,所述第三存储器装置包含第三接合垫,所述第二存储器装置经安置在所述第一与第三存储器装置之间;第一导体,其经耦合到所述第一及第二接合垫;第二导体,其经耦合到所述第二及第三接合垫;及第三导体,其经耦合到所述第二接合垫且经配置以将信号提供到所述第二接合垫,其中所述第一导体以第一信号时序将所述信号从所述第二接合垫提供到所述第一接合垫且所述第二导体以等于所述第一信号时序的第二信号时序将所述信号从所述第二接合垫提供到所述第三接合垫。

6.根据本公开的另一方面,提供一种多裸片装置。所述多裸片装置包括:衬底,其包含导电信号线;半导体装置堆叠,其经附接到所述衬底;及导体,其经耦合到所述衬底的导电信号线且到所述半导体装置堆叠的中间半导体装置的接合垫。

7.根据本公开的又一方面,提供一种设备。所述设备包括:半导体装置堆叠,其包含最低半导体装置、最高半导体装置及安置在所述最低与最高半导体装置之间的至少一个中间半导体装置;多个导体,其经耦合到所述堆叠的所述半导体装置的接合垫;及源导体,其经耦合到所述至少一个中间半导体装置中的一者的接合垫处的耦合点,其中所述多个导体

中的第一及第二者还经耦合到所述至少一个中间半导体装置中的一者的所述接合垫。

8.根据本公开的又一方面,提供一种方法。所述方法包括:将信号提供到半导体装置堆叠的中间半导体装置,所述中间半导体装置经安置在也包含在所述半导体装置堆叠中第一与第二半导体装置之间;通过耦合到所述中间半导体装置及所述第一半导体装置的第一信号路径将所述信号远离所述中间半导体装置传播到所述第一半导体装置;及通过耦合到所述中间半导体装置及所述第二半导体装置的第二信号路径将所述信号远离所述中间半导体装置传播到所述第二半导体装置。

附图说明

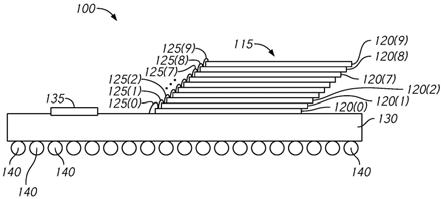

9.图1是展示多裸片装置的图。

10.图2是根据本公开的实施例的半导体装置的框图。

11.图3是根据本公开的一个实施例的半导体装置的布局图。

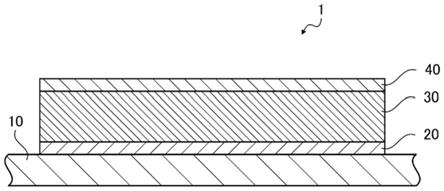

12.图4是根据本公开的实施例的半导体装置的导电结构的横截面视图。

13.图5是展示根据本公开的实施例的多裸片装置的图。

14.图6是根据本公开的实施例的耦合在一起的半导体装置的示意图。

15.图7是根据本公开的实施例的耦合在一起的半导体装置的接合垫的平面图。

16.图8是根据本公开的实施例的用于将信号提供到半导体装置堆叠的半导体装置的流程图。

具体实施方式

17.公开用于耦合半导体装置的设备及方法。在半导体装置群组(例如,半导体装置堆叠)中,将信号提供到所述群组的中间半导体装置处的耦合点,且在不同(例如,相反)信号路径上将所述信号远离所述耦合点传播到到所述群组的其它半导体装置。与例如在群组的末端处的半导体装置(例如,堆叠的最低半导体装置、所述堆叠的最高半导体装置等)处具有耦合点且从所述耦合点提供信号相比,从所述中间半导体装置处的所述耦合点到所述群组的其它半导体装置的负载可能更加平衡。更加平衡的拓扑可减少信号到达所述半导体装置中的每一者的时间之间的时序差异。

18.下文将参考附图详细地解释本公开的各种实施例。以下详细描述参考以说明方式展示本公开的特定方面及实施例的附图。所述详细描述包含足够细节以使所属领域的技术人员能够实践本公开的实施例。在不脱离本公开的范围的情况下,可利用其它实施例,且可进行结构、逻辑及电改变。本文中所公开的各种实施例不一定是互斥的,因为一些所公开实施例可与一或多个其它所公开实施例组合以形成新实施例。

19.图1是展示多裸片装置100的图。多裸片装置100可包含半导体装置120的堆叠115。堆叠115被展示为包含10个半导体装置120(0)到120(9)。半导体装置120(0)到120(9)中的每一者可为例如存储器装置,例如动态随机存取存储器(dram)装置。

20.堆叠115的半导体装置120可彼此附接,且堆叠115可经附接到衬底130。衬底130可包含导电信号线以沿着所述衬底将信号路由到半导体装置120的堆叠115及从半导体装置120的堆叠115路由信号。所述信号线中的一或多者可经耦合到外部端子140,例如焊球等。其它电路也可经附接到衬底130且还经耦合到导电信号线。因此,附接到衬底130的电路可

例如通过导电信号线耦合到半导体装置120的堆叠115。图1中展示附接到衬底130且耦合到半导体装置120的堆叠115的电路135。电路135可为寄存器时钟驱动器(rcd)。rcd电路接收及缓冲提供到多裸片装置100的信号且可将所述信号提供到半导体装置120的堆叠115。

21.半导体装置120可以交错方式堆叠,从而为堆叠115提供“叠瓦式堆叠”配置。即,半导体装置120彼此偏移以允许半导体装置120的边缘区被暴露。经暴露边缘区可包含导体125所耦合到的接合垫。导体125可为接合线,且所述边缘区的接合垫可通过接合线耦合在一起。

22.除最低高度半导体装置120(0)以外,每一半导体装置120的接合垫经耦合到所述堆叠中的紧接在前的半导体装置120的接合垫。例如,如图1中所展示,半导体裸片120(9)的接合垫通过接合线125(9)耦合到半导体装置120(8)的接合垫,半导体装置120(8)的接合垫通过接合线125(8)耦合到半导体装置120(7)的接合垫,半导体装置120(7)的接合垫通过接合线125(7)耦合到半导体装置120(6)的接合垫以此类推一直到半导体装置120(0)的接合垫。半导体装置120(0)通过接合线125(0)耦合到衬底130的导电信号线。因此,附接到衬底130的电路(例如,电路135)可例如通过导电信号线及接合线125耦合到半导体装置120。

23.利用图1中所展示的布置,由于通过接合线125的固有传播延迟,提供到堆叠115(例如,从电路135)的信号的到达时间对于半导体装置120来说是不同的。例如,信号首先通过接合线125(0)到达半导体装置120(0),接着在传播通过接合线125(1)之后的稍后时间到达半导体装置120(1),接着在传播通过接合线125(2)之后的更晚时间到达半导体装置120(2)以此类推,直到信号在传播通过接合线125(9)之后最终到达半导体装置120(9)为止。由于堆叠中包含数个半导体装置120,且随着存储器速度继续增加,信号到达堆叠115的半导体装置120中的第一者的时间与到达半导体装置120中的最后一者的时间之间的时间延迟可能对多裸片装置100的性能具有更大影响。

24.图2是根据本公开的实施例的半导体装置210的框图。例如,在一些实施例中,半导体装置210可为集成到单个半导体芯片(例如,半导体裸片)中的存储器。实例存储器可包含易失性存储器(例如动态随机存取存储器(dram)及静态随机存取存储器(sram)),及非易失性存储器(例如快闪存储器、电阻式存储器及铁电存储器或上述的任何组合)。

25.半导体装置210包含存储器单元阵列211。存储器单元阵列211包含多个存储体,每一存储体包含多个字线wl、多个位线bl及布置在多个字线wl与多个位线bl的相交点处的多个存储器单元mc。字线wl的选择由行解码器/驱动器212来执行且位线bl的选择由列解码器/驱动器213来执行。感测放大器218经耦合到对应位线bl且经连接到本地i/o线对liot/b。本地io线对liot/b经由用作开关的转移门tg 219连接到主io线对miot/b。

26.半导体装置210包含多个端子。在本公开的一些实施例中,所述端子可为裸片垫。多个端子包含命令及地址端子221、时钟端子223及223’、数据端子224、数据选通端子224’、电力供应器端子225及226。数据端子224可经耦合到输入/输出电路217的输出缓冲器以用于读取操作。替代地,数据端子224可经耦合到输入/输出电路217的输入缓冲器以响应于数据选通端子224’处提供的数据选通信号dqs而对存储器进行写入存取。

27.向命令及地址端子221供应命令及地址信号ca,所述命令及地址信号ca包含命令及存储器地址。经由命令及地址输入电路231将提供到命令及地址端子221的地址转移到地址解码器232。地址解码器232接收所述地址并将经解码行地址供应到行解码器/驱动器

212,且将经解码列地址供应到列解码器/驱动器213。地址解码器232还接收存储体地址且将存储体地址提供到行解码器/驱动器212及/或列解码器/驱动器213。在自刷新模式下,自刷新电路238可将行地址提供到行解码器/驱动器212以用于自刷新操作。

28.经由命令及地址输入电路231将提供到命令及地址端子221的命令提供到命令解码器234。命令解码器234对所述命令进行解码且将经解码命令提供到内部控制信号生成器237。内部控制信号生成器237可响应于来自命令解码器234的经解码命令而生成各种内部命令信号。例如,内部命令可包含用于选择字线的行命令信号及用于选择位线的列命令信号,例如读取命令或写入命令。

29.因此,当发出激活命令并及时向行地址供应激活命令,且及时向列地址供应读取命令时,从存储器单元阵列211中由行地址及列地址指定的存储器单元mc读取读取数据。经由读取/写入放大器215及输入/输出电路217从数据端子224输出读取数据dq。类似地,当发出激活命令并及时向行地址供应激活命令时,且及时向列地址供应写入命令时,供应到数据端子224的写入数据dq经由输入/输出电路217及读取/写入放大器215供应到存储器单元阵列211且写入在由行地址及列地址指定的存储器单元mc中。

30.分别向时钟端子223供应时钟信号ck_t及ck_c,且向时钟端子223’供应数据时钟信号wck_t及wck_c。时钟输入电路235接收时钟信号ck_t及ck_c与wck_t及wck_c且生成内部时钟信号iclk。内部时钟信号iclk可包含基于时钟信号ck_t及ck_c的内部时钟信号及/或基于数据时钟信号wck_t及wck_c的内部时钟信号。一些或所有内部时钟信号iclk经供应到内部时钟及时序生成器236,所述内部时钟及时序生成器236作为响应而生成相位控制内部时钟信号lclk。内部时钟及时序生成器236可包含dll电路,但不限于此。相位控制内部时钟信号lclk可经供应到输入/输出电路217且用于对数据的输入及/或输出进行定时。内部时钟及时序生成器236可进一步生成用于各种存储器操作的各种其它内部时钟信号。

31.向电力供应器端子225供应电力供应器电势vdd及vss。将这些电力供应器电势vdd及vss供应到电源电路239。电源电路239可生成各种内部电势,例如,vpp、vod、vary、vperi等。内部电势vpp主要用于行解码器/驱动器212中,内部电势vod及vary主要用于存储器单元阵列211中包含的感测放大器218中,且内部电势vperi用于许多其它电路块中。向电力供应器端子226供应电力供应器电势vddq及vssq。将这些电力供应器电势vddq及vssq供应到输入/输出电路217。电力供应器电势vddq及vssq可分别为与供应到电力供应器端子225的电力供应器电势vdd及vss相同的电势。然而,电力供应器电势vddq及vssq可用于输入/输出电路217,使得由输入/输出电路217生成的电力供应器噪声不会传播到其它电路块。

32.图3是根据本公开的一个实施例的半导体装置310的布局图。在本公开的一些实施例中,半导体装置310包含图2的半导体装置210。

33.半导体装置310可具有边缘350a、350b、350c及350d,所述边缘界定半导体装置310的端。边缘350b及350d可沿着第一方向357a延伸且边缘350a及350c可沿着第二方向357b延伸,第二方向357b可垂直于第一方向357a。半导体装置310可包含垫形成区域351、外围电路区域352及包含存储器单元、电路及信号线(例如,感测放大器电路、地址解码器电路、数据输入/输出线等)的存储器单元阵列区域353。外围电路区域352可包含用于执行半导体装置310的各种操作的各种电路及信号线。例如,外围电路区域352可包含命令及地址输入电路、地址及命令解码器、时钟电路、电源电路及输入/输出电路。外围电路区域352还可包含耦合

到半导体装置的各种电路的端子(例如,如先前针对图1的半导体装置170所描述)。所述端子可为例如半导体装置的裸片垫。

34.垫形成区域351可包含沿着边缘350a安置的多个接合垫354。多个接合垫354可经耦合到半导体装置的端子(例如,裸片垫)且表示半导体装置310的外部端子。例如,多个接合垫354可包含数据端子、命令及地址端子、时钟端子及/或电力供应器端子。

35.存储器单元阵列区域353中包含的电路及/或外围电路区域352的电路可经耦合到垫形成区域351中包含的一或多个接合垫354。如先前所描述,半导体装置300的各种电路可经耦合到所述端子(例如,裸片垫)。导电结构可用于将所述端子耦合到接合垫354中的一或多者。因此,耦合到所述端子的电路也耦合到接合垫354。导电结构可从存储器单元阵列区域353及/或外围电路区域352中包含的端子的位置延伸到垫形成区域351。在本公开的一些实施例中,导电结构可包含导电重布层(rdl)。

36.图4是根据本公开的实施例的半导体装置的导电结构的横截面视图。在本公开的一些实施例中,导电结构可被包含在图2的半导体装置210、图1的多裸片装置100的半导体装置120、图3的半导体装置310及/或根据本公开的实施例的的任何半导体装置中。例如,在本公开的一些实施例中,导电结构可被包含在图1到3的半导体装置中的一或多者中的导电重布层(rdl)中。

37.导电结构430可将半导体装置的端子440耦合到接合垫420。在本公开的一些实施例中,端子440可为裸片垫。端子440可经耦合到半导体装置的一或多个电路445。因此,接合垫420可通过导电结构430及端子440耦合到电路445。在本公开的一些实施例中,电路445可为例如包含在存储器单元阵列区域(例如,图3的存储器单元阵列区域352)中的电路。在本公开的一些实施例中,电路445可为例如包含在外围电路区域(例如,图3的外围电路区域354)中的电路。电路445可用于执行半导体装置的各种操作。在本公开的一些实施例中,电路445可包含命令及地址输入电路、地址及命令解码器、时钟电路、电源电路及输入/输出电路以及其它电路。

38.半导体装置的接合垫420、导电结构430、端子440及电路445可由半导体结构形成。半导体结构可包含导电层、导电通路、绝缘夹层等。端子440可通过例如金属层及/或导电通路耦合到电路445。导电结构430可经安置在一或多个绝缘夹层上。如先前所描述,导电结构430可进一步经耦合到接合垫420。导电结构430从端子440延伸到接合垫420,使得接合垫420及电路端子440可经耦合在一起。因此,可通过接合垫420从外部存取耦合到端子440的电路445。接合垫420可通过钝化层435中的开口425暴露。在本公开的一些实施例中,钝化层435可为聚酰亚胺材料。

39.在本公开的一些实施例中,导电结构430可经耦合到半导体装置的端子440(例如,半导体装置的裸片垫)以提供用于在不同位置中耦合到端子440的接合垫420。例如,端子440可表示通常位于沿着半导体装置的中心区的外围电路区中的裸片垫,且导电结构430可将中心区中的裸片垫耦合到沿着半导体装置的边缘定位的接合垫420。沿着边缘的接合垫420可更方便地定位且提供到半导体装置的电路445的耦合,即,通过导电结构430及端子440。

40.图5是展示根据本公开的实施例的多裸片装置500的图。多裸片装置500可包含半导体装置520的堆叠515。本公开的实施例不限于图5中所展示的堆叠515中包含的特定数目

的半导体装置520。在本公开的一些实施例中,半导体装置520中的每一者包含图2的半导体装置210。半导体装置520中的每一者可为例如存储器装置,例如动态随机存取存储器(dram)装置。

41.堆叠515的半导体装置520可彼此附接,且堆叠515可经附接到衬底530。在本公开的一些实施例中,半导体装置520彼此附接及/或通过粘性环氧树脂附接到衬底530。衬底530可包含导电信号线以沿着衬底将信号路由到半导体装置520的堆叠515及从半导体装置520的堆叠515路由信号。所述信号线中的一或多者可经耦合到外部端子540。在本公开的一些实施例中,外部端子540可包含焊球等。其它电路也可经附接到衬底530且还经耦合到导电信号线。因此,附接到衬底530的电路可例如通过导电信号线耦合到半导体装置520的堆叠515。图5中展示附接到衬底530且耦合到半导体装置520的堆叠515的电路535。在本公开的一些实施例中,电路535可为寄存器时钟驱动器(rcd)。在本公开的此类实施例中,rcd电路接收及缓冲提供到多裸片装置500的信号且可将所述信号提供到半导体装置520的堆叠515。在不脱离本公开的范围的情况下,额外或替代电路可被包含在多裸片装置500中,及/或电路535也可为其它电路。

42.半导体装置520可以交错方式堆叠,从而为堆叠515提供“叠瓦式堆叠”配置。即,半导体装置520彼此偏移以允许半导体装置520的边缘区被暴露。经暴露边缘区可包含导体525所耦合到的接合垫。在本公开的一些实施例中,导体525可为接合线,且所述边缘区的接合垫可通过接合线耦合在一起。

43.除最低高度半导体装置520(0)以外,每一半导体装置520的接合垫经耦合到所述堆叠中的至少一个其它半导体装置520的接合垫。例如,如图5中所展示,半导体装置520(8)的接合垫通过导体525(9)耦合到半导体装置520(9)的接合垫,且所述接合垫通过导体525(8)进一步耦合到半导体装置520(7)的接合垫。类似地,半导体装置520(1)的接合垫通过导体525(2)耦合到半导体装置520(2)的接合垫,且所述接合垫通过导体525(1)进一步耦合到半导体装置520(0)的接合垫。

44.半导体装置520(4)通过源导体510耦合到衬底530的导电信号线。源导体510可经耦合到例如半导体装置520(4)的接合垫。半导体装置520(4)经耦合到半导体装置520(3),所述半导体装置520(3)经耦合到半导体装置520(2),所述半导体装置520(2)经耦合到半导体装置520(1),所述半导体装置520(1)经耦合到半导体装置520(0)。半导体装置520(4)还经耦合到半导体装置520(5),所述半导体装置520(5)经耦合到半导体装置520(6),所述半导体装置520(6)经耦合到半导体装置520(7),所述半导体装置520(7)经耦合到半导体装置520(8),所述半导体装置520(8)经耦合到半导体装置520(9)。因此,附接到衬底530的电路(例如,电路535)可例如通过导电信号线及源导体510及导体525耦合到半导体装置520的堆叠515。

45.在本公开的实施例中,在半导体装置520的中间半导体装置处耦合到堆叠515可减少信号到达半导体装置中的每一者的时间之间的时序差异。中间半导体装置可为最低半导体装置与最高半导体装置之间(例如,半导体装置520(0)(最低)及半导体装置520(9)(最高))之间的任何半导体装置。从耦合的角度来看,到堆叠515的中间半导体装置耦合可提供更加平衡的拓扑。

46.虽然图5说明堆叠515中的半导体装置520,但在本公开的其它实施例中,半导体装

置520可以不同方式布置成群组。例如,所述半导体装置可相对于彼此横向地布置成一行。耦合点可到横向布置的半导体装置的群组的中间半导体装置。在此类实施例中,提供到耦合点的信号可在相反方向上从耦合点到半导体装置的横向布置的相对端处的半导体装置横向地传播。在本公开的一些实施例中,半导体装置520在其它布置中物理上相对于彼此定位。更一般来说,本公开的范围并不意在仅限于半导体装置的堆叠式布置。

47.例如,在图5中所展示的本公开的实施例中,衬底530的导电信号线通过源导体510在中间半导体装置520(4)处耦合到堆叠515。与例如在最低半导体装置处具有耦合点相比,从半导体装置520(4)处的耦合点到最低半导体装置520(0)与到最高半导体装置520(9)的负载更加平衡。因此,可减小从半导体装置520(4)处的耦合点到所述堆叠的最低半导体装置520(0)与到最高半导体装置520(9)的信号的时序差异。

48.在半导体装置群组(例如,堆叠)的中心附近的中间半导体装置处具有耦合点可能是有利的。“中心”半导体装置是群组的中间半导体装置,其可经定位在所述群组中,使得在从中心半导体装置到相对端半导体装置的任一方向上存在相等数目个半导体装置。例如,在九个半导体装置的堆叠中,中心半导体装置是第五半导体装置,其经定位在所述堆叠中,因此在到第一端半导体装置(例如,最低半导体装置)的第一方向上且在到第二端半导体装置(例如,最高半导体装置)的第二方向上存在四个半导体装置。在群组包含偶数个半导体装置的情况下,中心半导体装置可为定位在所述群组中使得在从中心半导体装置到相对端半导体装置的任一方向上存在几乎相等数目个半导体装置的两个半导体装置中的任一者(例如, /

‑

1个半导体装置)。例如,在八个半导体装置的堆叠中,中心半导体装置是第四或第五半导体装置,其经定位在所述堆叠中,使得在到第一端半导体装置的第一方向上存在四个半导体装置且在到第二端半导体装置的第二方向上存在三个半导体装置。

49.图6是根据本公开的实施例的耦合在一起的半导体装置的示意图。在本公开的一些实施例中,图6的半导体装置可表示图5的半导体装置520的堆叠515。在本公开的一些实施例中,图6的半导体装置可表示相对于彼此横向地布置的半导体装置群组。在本公开的一些实施例中,图6的半导体装置可表示呈其它物理布置的半导体装置。出于便于描述的目的,将参考图5的半导体装置520描述图6的半导体装置。然而,图6的半导体装置不一定限于此。

50.半导体装置520(0)到520(9)的接合垫通过导体525(1)到525(9)耦合。例如,半导体装置520(0)的接合垫通过导体525(1)耦合到半导体装置520(1)的接合垫;半导体装置520(1)的接合垫通过导体525(2)耦合到半导体装置520(2)的接合垫;半导体装置520(2)的接合垫通过导体525(3)耦合到半导体装置520(3)的接合垫;半导体装置520(3)的接合垫通过导体525(4)耦合到半导体装置520(4)的接合垫;半导体装置520(4)的接合垫通过导体525(5)耦合到半导体装置520(5)的接合垫;半导体装置520(5)的接合垫通过导体525(6)耦合到半导体装置520(6)的接合垫;半导体装置520(6)的接合垫通过导体525(7)耦合到半导体装置520(7)的接合垫;半导体装置520(7)的接合垫通过导体525(8)耦合到半导体装置520(8)的接合垫;且半导体装置520(8)的接合垫通过导体525(9)耦合到半导体装置520(9)的接合垫。

51.源导体510经耦合到半导体装置520(4)的接合垫。源导体510可经耦合到例如衬底的另一电路及/或导电信号线。因此,电路及/或导电信号线可经耦合到其它半导体装置。

52.在图6的实例中,对于半导体装置520中的每一者展示仅一个接合垫。然而,在不脱离本公开的范围的情况下,半导体装置520中的每一者可包含可耦合到其它半导体装置520的额外接合垫。半导体装置520的接合垫还可表示可耦合在一起的一或多个物理接合垫,且因此不限于多个导体所耦合到的仅一个物理接合垫。例如,在本公开的一些实施例中,半导体装置的接合垫可表示耦合在一起的两个接合垫,耦合到第一相邻半导体装置的接合垫的一个接合垫及耦合到第二相邻半导体装置的接合垫的另一接合垫。在本公开的一些实施例中,半导体装置的接合垫可表示耦合在一起的三个接合垫,耦合到第一相邻半导体装置的接合垫的第一接合垫,耦合到第二相邻半导体装置的接合垫的第二接合垫,以及源导体510可耦合到的第三接合垫。

53.导体525包含可影响信号到达相应半导体装置的时间的时序的固有传播延迟。然而,在源导体510经耦合到半导体装置520(0)到520(9)中的中间一者的情况下,可提供更加平衡的拓扑。中间半导体装置可为例如第一端半导体装置与第二端半导体装置之间(例如,半导体装置520(0)(第一端)与半导体装置520(9)(第二端)之间)的半导体装置。更加平衡的拓扑可减少信号到达半导体装置520中的每一者的时间之间的时序差异。例如,如图6的实例中所展示,利用半导体装置520(4)的接合垫处的耦合点,源导体510上提供的信号传播通过四个导体525(4)到525(1)以到达半导体装置520(0)(例如,第一端半导体装置)且传播通过五个导体525(5)到525(9)以到达半导体装置520(9)(例如,第二端半导体装置)。

54.在其中导体525中的每一者提供类似传播延迟的本公开的实施例中,源导体510上提供的信号到半导体装置520(0)与到半导体装置520(9)的到达时间的差异近似于一个导体525(例如,导体525(9),第五导体)的传播延迟,其在本公开的一些实施例中可被视为近似于到半导体装置520(0)及到半导体装置520(9)的相同传播延迟。

55.相比之下,与其中首先将信号提供到半导体装置520(0)(例如,第一端半导体装置)且信号传播通过导体525(1)到525(9)到半导体装置520(9)的布置相比,信号时序的差异可显著更大。例如,信号在九个导体525的传播延迟之后到达半导体装置520(9)。因此,半导体装置520(0)与半导体装置520(9)之间的信号时序的差异是九个导体525的总传播延迟,其可为比与一个导体525的传播延迟的时序差异显著更长的延迟,例如对于图6的实例。

56.将源导体耦合到半导体装置群组(例如,半导体装置堆叠)的中间半导体装置的布置在减少信号到达两端半导体装置的时序差异方面可为有利的。此布置可为具有高负载的单向信号(例如,命令及地址信号、芯片选择信号、时钟以及其它信号)提供改进的信号完整性。如所公开的布置还可能需要较轻驱动及较轻端子端接(例如,在裸片端接上)以在接收器电路处提供有效数据眼。

57.图7是根据本公开的实施例的耦合在一起的半导体装置的接合垫的平面图。虽然图7展示五个半导体装置720(2)到720(6),但在不脱离本公开的范围的情况下,额外半导体装置可经耦合到半导体装置720(2)到720(6)。例如,在本公开的一些实施例中,所述半导体装置可被包含在多裸片装置(例如,图2的多裸片装置200)中。

58.接合垫715到717可被包含在相应半导体装置720(2)到720(6)的垫形成区域中。每一半导体装置的对应接合垫通过导体725耦合在一起。例如,半导体装置720(2)到720(6)的接合垫715(2)到715(6)通过导体725(3)a到725(6)a耦合在一起;半导体装置720(2)到720(6)的接合垫716(2)到716(6)通过导体725(3)b到725(6)b耦合在一起;且半导体装置720

(2)到720(6)的接合垫717(2)到717(6)通过导体725(3)c到725(6)c耦合在一起。虽然对于每一半导体装置720展示仅三个接合垫715到717,但在不脱离本公开的范围的情况下可包含额外接合垫。

59.相应导体710a到710c经耦合到中间半导体装置720(4)的接合垫715(4)到717(4)。导体710a到710c中的每一者可经耦合到例如衬底的电路及/或导电信号线。相应导体710上提供的信号可通过耦合到相应接合垫715到717的导体725提供到所述半导体装置中的每一者。通过在中间半导体装置处具有耦合点且通过导体在两个不同(例如,相反)信号路径上将信号远离耦合点传播到半导体装置,可使信号的信号时序更加平衡。例如,信号到达半导体装置720(2)与到达半导体装置720(6)的信号时序可近似相等,这是因为通过导体725的传播延迟应近似等于从半导体装置720(4)的接合垫715(4)到717(4)处的耦合点到半导体装置720(2)的对应接合垫715(2)到717(2)的传播延迟,且近似等于从接合垫715(4)到717(4)处的耦合点到半导体装置720(6)的对应接合垫715(6)到717(6)的传播延迟。

60.图8是根据本公开的实施例的将信号提供到半导体装置堆叠的半导体装置的流程图。在本公开的一些实施例中,半导体装置可被包含在图5的半导体装置堆叠及/或图6的经耦合半导体装置中。在本公开的一些实施例中,用于图8的方法的堆叠的半导体装置可包含如参考图7所描述的耦合在一起的接合垫。半导体装置是存储器装置,例如在本公开的一些实施例中是dram装置。出于便于描述的目的,将参考图5的半导体装置520的堆叠515描述图8的流程图的方法800。然而,图8的方法800不一定限于此。

61.在步骤801处,将信号提供到半导体装置堆叠的中间半导体装置。中间半导体装置可在第一半导体装置与第二半导体装置之间。例如,参考图5的半导体装置520的堆叠515,半导体装置520(4)可为在半导体装置520(3)与520(5)之间的中间半导体装置。所述信号可例如为由所述堆叠外部的电路(例如电路535)提供的信号。如先前所描述,电路535及堆叠515可经附接到包含导电信号线的衬底。所述信号可通过导电信号线且通过耦合到导电信号线并耦合到半导体装置520(4)的接合垫的源导体510提供到半导体装置520(4)。

62.在步骤803处,在第一信号路径上将信号远离中间半导体装置提供到第一半导体装置。例如,再次参考图5的半导体装置520的堆叠515,半导体装置520(3)可为第一半导体装置且第一信号路径可为导体525(3)。导体525(3)可经耦合到半导体装置520(4)的接合垫且到半导体装置520(3)的接合垫。提供到半导体装置520(4)(例如,到半导体装置520(4)的接合垫)的信号可在导体525(3)上远离半导体装置520(4)提供到半导体装置520(3)。

63.在步骤805处,还在第二信号路径上将信号远离中间半导体装置提供到第二半导体装置。例如,再次参考图5的半导体装置520的堆叠515,半导体装置520(5)可为第二半导体装置且第二信号路径可为导体525(5)。导体525(5)可经耦合到半导体装置520(4)的接合垫且到半导体装置520(5)的接合垫。提供到半导体装置520(4)的信号可在导体525(5)上远离半导体装置520(4)提供到半导体装置520(5)。在本公开的一些实施例中,第二信号路径(例如,导体525(5))及第一信号路径(例如,导体525(3))可为相反信号路径以远离中间半导体装置(例如,半导体装置520(4))提供信号。

64.信号路径(例如,导体525(3)及525(5))包含可影响信号到达相应半导体装置的时间的时序的固有传播延迟。如先前所描述,将信号提供到半导体装置中的中间一者(例如,中间半导体装置520(4)且将信号远离中间半导体装置的提供到相应信号路径上的第一及

第二半导体装置(例如,导体525(3)上的半导体装置520(3)及导体525(5)上的半导体装置520(5))可提供更加平衡的拓扑。因此,可减少信号到达第一与第二半导体装置的时间的时序差异。例如,在本公开的一些实施例中,由于通过中间半导体装置的耦合,信号通过第一信号路径到第一半导体装置的传播延迟可等于信号通过第二信号路径到第二半导体装置的传播延迟。

65.已描述某些细节以提供对本公开的实例的充分理解。然而,对于所属领域的技术人员将显而易见的是,可在没有这些特定细节的情况下实践本公开的实例。此外,本文中所描述的本公开的特定实例不应被解释为将本公开的范围限于这些特定实例。在其它例子中,未详细地展示众所周知的电路、控制信号、时序协议及软件操作以避免不必要地模糊本公开。另外,例如“耦合(couples及coupled)”的术语表示两个组件可直接或间接电耦合。间接耦合可暗示两个组件通过一或多个中间组件耦合。

66.从前述内容将明白,尽管本文中已出于说明目的描述本公开的特定实施例,但在不脱离本公开的精神及范围的情况下可进行各种修改。因此,本公开的范围不应限于本文中所描述的任何特定实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。