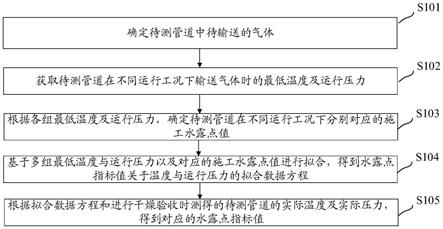

1.本发明涉及一种使用电阻变化型存储元件的纵横式数组(crossbar array),尤其涉及向电阻变化型存储元件进行的尖峰时序相依可塑性(stdp)的写入方法及突触数组装置。

背景技术:

2.所谓突触,是指于神经信息的输出侧与输入侧之间发展起来的用于信息传输的接触结构。最基本的结构为突触前神经元的轴突末端与突触后神经元的树突接触。当突触前神经元与突触后神经元均以高频率连续放电时,突触的传输效率会增加。近年来,已知仅因突触前神经元与突触后神经元的放电时间差,结合强度中亦显现出变化。将此称为尖峰时序相依突触可塑性(stdp;spike timing dependent plasticity)。

3.例如,专利文献1涉及一种生成stdp的神经元网络(neuron network),神经元网络具有多个电子神经元以及为了将多个电子神经元互连而结合的互连电路。互连电路包括用于经由轴突、树突等通路将电子神经元互连的多个突触装置。各突触装置包括可变电阻器与晶体管,各突触装置结合于轴突与树突之间。

4.现有技术文献

5.专利文献

6.专利文献1美国专利第9,269,042号公报

技术实现要素:

7.[发明所要解决的问题]

[0008]

人工类神经网络(artificial neural network)于图案识别等识别分类技术中作为软件的算法而被引入,其已成为通过高集成的数字互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)技术进行安装的必要技术。然而,通过数字技术安装的类神经网络于功率、规模的方面逐渐达到极限。特别是于将来受到期待的物联网(internet of things,iot)领域中重视规模、功率、成本,难以将该类神经网络直接引入设备中。另一方面,最近几年,正在进行将电阻组件用作突触的类神经网络的研究及开发,低功率且小规模、达成终极学习功能的类神经网络的实用化取得进展。

[0009]

已知脑部的记忆及学习与神经网的突触的结合强度有关。当进行其信号传输时使用电位脉冲,且因两个电位脉冲的时间差,突触的结合强度被调节。此为所述尖峰时序相依性可塑性(stdp),且于脑部的记忆及学习中具有重要的作用。

[0010]

图1中示出使用了可变电阻组件的纵横式数组的一例。纵横式数组包括于列方向上延伸存在的多个列线10、以与列线10正交的方式于行方向上延伸存在的多个行线20、以及连接于各列线10与行线20之间的交叉部的忆阻器(memristor)30而构成。忆阻器30例如为通过施加电压或电流来记忆不同的电阻状态的非挥发性电阻变化型存储元件。

[0011]

于将此种纵横式数组应用于神经元网络的情况下,通过将stdp的电信号写入忆阻

器(电阻变化型存储元件)30中来进行突触的结合强度的调节。

[0012]

图2是说明stdp的写入方法的原理的图。于图2中,作为纵横式数组的一部分40而示出了两个列线r1、r2、两个行线c1、c2、以及连接于该些的交叉部分的四个电阻变化型存储元件。于该例子中,设为选择的是电阻变化型存储元件mc,列线r1表示突触前神经元(前神经元(pre neuron)),行线c1表示突触后神经元(后神经元(post neuron)),电阻变化型存储元件mc表示突触。

[0013]

电阻变化型存储元件使用氧化铪等金属过渡氧化物构成,且是使设定(set)/重设(reset)时施加的写入电压的极性反转的双极型,设定是将电阻变化型存储元件设为低电阻状态,重设是将电阻变化型存储元件设为高电阻状态。例如,来自列线r1的写入电压的施加为设定,来自行线c1的写入电压的施加为重设。对列线r1施加尖峰信号spre,对行线c1施加尖峰信号spost,于电阻变化型存储元件mc中写入由突触前神经元与突触后神经元生成的尖峰信号spre/spost的差,藉此,电阻变化型存储元件mc的电导、即突触的结合强度被调节。

[0014]

图3的(a)表示通过stdp突触的结合强度被强化的例子,图3的(b)表示通过stdp突触的结合强度被抑制的例子。对电阻变化型存储元件mc的实际写入是使用对尖峰信号spre/spost进行近似而成的脉冲状的电压信号vpre/vpost来进行。电压信号vpre是由突触前神经元生成的脉冲信号,电压信号vpost是由突触后神经元生成的脉冲信号。电压信号vpre/vpost由正矩形波脉冲(pa/ta)、以及陡峭的自负电位缓慢衰减的负三角波脉冲(pb/tb)构成。

[0015]

如图3的(a)所示,于电压信号vpre比电压信号vpost于时间上更早地产生时(δt>0),vpost

‑

vpre的电位差vnet中产生比设定时的写入的临限值vtset大veff的正脉冲。若该脉冲重复多次,则电阻变化型存储元件mc的电导变大,即突触的结合强度被强化(长效强化(ltp:long term potentiation))。相反,如图3的(b)所示,当电压信号vpre比电压信号vpost于时间上更晚地产生时(δt<0),vpost

‑

vpre的电位差vnet中产生比重设时的写入的临限值vtreset大veff的负脉冲。若该脉冲重复多次,则电阻变化型存储元件mc的电导降低,即突触的结合强度被抑制(长效抑制(ltd:long term depression))。

[0016]

vpost

‑

vpre的时间差δt与突触结合强度的变化δw的关系被称为stdp学习规则,且将该关系示于图4的图表中。如图4所示,δt与δw的关系由直角双曲线表示。可进行极性不同的写入的双极型的电阻变化型存储元件是适合于表现突触的结合强度的器件。然而,vpost

‑

vpre的电位差vnet包括负电位或负脉冲,因此纵横式数组的周边电路必须处理负电位。例如,需要用于生成负电位或负电源的内部电路,因此必须使半导体制程为三重井(triple

‑

well),其结果,产生器件的成本增加且电流消耗增加的问题。

[0017]

本发明是为解决此种课题而成者,其目的在于提供一种可使用正电位进行stdp的写入的电阻变化型突触数组装置。

[0018]

[解决问题的技术手段]

[0019]

本发明的写入方法向使用了双极型的电阻变化型存储元件的纵横式数组进行stdp的写入,其中,由利用正电位的第一驱动器生成与由突触前神经元生成的尖峰信号的正部分相对应的第一电压信号,由利用正电位的第二驱动器生成与由突触后神经元生成的尖峰信号的负部分相对应的第二电压信号,由利用正电位的第三驱动器生成与由突触后神

经元生成的尖峰信号的正部分相对应的第三电压信号,由利用正电位的第四驱动器生成与由突触前神经元生成的尖峰信号的负部分相对应的第四电压信号,将第一电压信号与第二电压信号相加而得的第一驱动信号施加至所选择的电阻变化型存储元件的一个端子,将第三电压信号与第四电压信号相加而得的第二驱动信号施加至所述所选择的电阻变化型存储元件的另一个端子。

[0020]

于某实施方式中,第一驱动信号为设定或重设时的写入电压,第二驱动信号为重设或设定时的写入电压。stdp是由突触前神经元生成的尖峰信号与由突触后神经元生成的尖峰信号的差。第一驱动信号及第二驱动信号为正的脉冲信号。第一电压信号为正的矩形波脉冲信号,第二电压信号为正的三角波脉冲信号,第三电压信号为正的矩形波脉冲信号,第四电压信号为正的三角波脉冲信号。

[0021]

本发明的突触数组装置具有:纵横式数组,使用了双极型的电阻变化型存储元件;选择单元,选择所述纵横式数组的电阻变化型存储元件;以及写入单元,向电阻变化型存储元件进行写入,所述写入单元包括与电阻变化型存储元件的一个端子连接的正电位的第一驱动器及第二驱动器、以及与另一个端子连接的正电位的第三驱动器及第四驱动器,第一驱动器生成与由突触前神经元生成的尖峰信号的正部分相对应的第一电压信号,第二驱动器生成与由突触后神经元生成的尖峰信号的负部分相对应的第二电压信号,第三驱动器生成与由突触后神经元生成的尖峰信号的正部分相对应的第三电压信号,第四驱动器生成与由突触前神经元生成的尖峰信号的负部分相对应的第四电压信号,所述写入单元将第一电压信号与第二电压信号相加而得的第一驱动信号施加至所选择的电阻变化型存储元件的一个端子,将第三电压信号与第四电压信号相加而得的第二驱动信号施加至所述所选择的电阻变化型存储元件的另一个端子。

[0022]

于某实施方式中,第一驱动信号为设定或重设时的写入电压,第二驱动信号为重设或设定时的写入电压。stdp是由突触前神经元生成的尖峰信号与由突触后神经元生成的尖峰信号的差。电阻变化型存储元件包括选择器器件。选择器器件为二极管或晶体管。

[0023]

[发明的效果]

[0024]

根据本发明,由利用正电位的第一驱动器至第四驱动器生成第一电压信号至第四电压信号,将第一电压信号与第二电压信号相加而得的第一驱动信号施加至所选择的电阻变化型存储元件的一个端子,将第三电压信号与第四电压信号相加而得的第二驱动信号施加至所述所选择的电阻变化型存储元件的另一个端子,因此可向电阻变化型存储元件进行使用了正电位的stdp的写入。

附图说明

[0025]

图1是表示纵横式数组结构例图;

[0026]

图2是说明向使用了电阻变化型存储元件的纵横式数组进行stdp写入方法图;

[0027]

图3的(a)~图3的(b)是表示进行stdp的写入时脉冲波形图;

[0028]

图4是说明stdp学习规则图;

[0029]

图5是表示本发明实施例突触数组装置的一例的框图;

[0030]

图6的(a)~图6的(d)是说明由本发明实施例提供的向使用了电阻变化型存储元件的纵横式数组进行stdp写入方法图;

[0031]

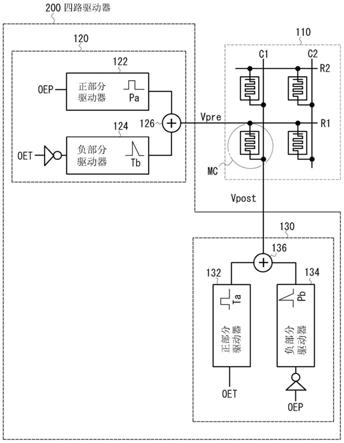

图7表示由本发明实施例提供的四路型写入电路的结构图。

[0032]

符号说明

[0033]

10:列线,110:纵横式数组,120:列选择/驱动电路,30:忆阻器,100:突触数组装置,20:行线,122:列_正部分驱动器,124:列_负部分驱动器,126:加法器,130:行选择/驱动电,132:行_正部分驱动器,136:加法器,150:输入/输出部,40:纵横式数组的一部分,δt:时间差,134:行_负部分驱动器,140:控制部,200:四路驱动器,mc:电阻变化型存储元件,pa、ta:矩形波脉冲,r1、r2:列线,vnet:电位差,c1、c2:行线,oet、oep:赋能信号,pb、tb:三角波脉冲,spre、spost:尖峰信号,vpre、vpost:电压信号/驱动信号,vtset、vtreset:临限值,δw:突触结合强度的变化。

具体实施方式

[0034]

接着,参照附图对本发明的实施方式进行详细说明。于本发明的某实施方式中,纵横式数组被用作构成人工智能(artificial intelligence,ai)硬件的类神经网络的突触数组装置。纵横式数组于矩阵的交叉部包括作为忆阻器的电阻变化型存储元件,电阻变化型存储元件为双极型,可通过施加极性不同的电流或电压来记忆不同的电导状态(高电阻状态与低电阻状态)。电阻变化型存储元件构成突触,纵横式数组构成突触数组装置。突触数组装置被组入计算机装置或计算机系统中,负责由微处理机或中央处理单元(central processing unit,cpu)等进行的数据处理或演算处理的至少一部分。

[0035]

[实施例]

[0036]

图5是表示本发明实施例突触数组装置的结构例框图。本实施例的突触数组装置100包括具有电阻变化型存储元件的纵横式数组110、列选择/驱动电路120、行选择/驱动电路130、控制部140及输入/输出(input/output,i/o)部150。突触数组装置100例如安装于ai芯片或半导体集成电路中。

[0037]

例如,如图1所示,纵横式数组110包括于列方向上延伸存在的多个列线、于行方向上延伸存在的多个行线、以及连接于列线与行线之间的交叉部的电阻变化型存储元件。电阻变化型存储元件使用氧化铪(hfox)或氧化钽(taox)等金属过渡氧化物而构成。列线及行线的数量、形状、导电性材料等为任意的。另外,纵横式数组110亦可为将如图1所示的纵横式数组成对地于垂直方向上积层多对而成者。

[0038]

列选择/驱动电路120基于来自控制部140的列选择信号或控制信号等选择纵横式数组110的列线,并对所选择的列线施加写入电压或读出电压,或者对非选择的列线施加写入禁止电压等。如后所述(参照图7),列选择/驱动电路120包括两个可独立地运作的列_正部分驱动器122、列_负部分驱动器124、以及加法器126。两个驱动器122、124使用正电位运作,列_正部分驱动器122生成与由突触前神经元(pre neuron)生成的尖峰信号的正部分相对应的电压信号,列_负部分驱动器124生成与由突触后神经元(post neuron)生成的尖峰信号的负部分相对应的电压信号。

[0039]

行选择/驱动电路130基于来自控制部140的行选择信号或控制信号等选择纵横式数组110的行线,并对所选择的行线施加写入电压或读出电压,或者对非选择的行线施加写入禁止电压等。如后所述(参照图7),行选择/驱动电路130包括两个可独立地运作的行_正部分驱动器132、行_负部分驱动器134、以及加法器136。两个驱动器132、134使用正电位运

作,行_正部分驱动器132生成与由突触后神经元(post neuron)生成的尖峰信号的正部分相对应的电压信号,行_负部分驱动器134生成与由突触前神经元(pre neuron)生成的尖峰信号的负部分相对应的电压信号。

[0040]

控制部140由硬件和/或软件构成,并对读出动作或写入动作进行控制。于某实施方式中,控制部140包括具有只读存储器/随机存取内存(read

‑

only memory/random access memory,rom/ram)的微控制器、微处理机或状态机(state machine)等,并例如通过执行rom/ram中所存储的软件来对读出动作或写入动作进行控制。

[0041]

于本实施例中,控制部件140包括向纵横式数组部件110的电阻变化型存储元件进行stdp的写入的功能。控制部140经由列选择/驱动电路120,对所选择的列施加与由突触前神经元生成的尖峰信号相当的驱动信号vpre,并经由行选择/驱动电路130,对所选择的行施加与由突触后神经元生成的尖峰信号相当的驱动信号vpost。对列施加的驱动信号vpre是将由列_正部分驱动器122生成的电压信号与由列_负部分驱动器124生成的电压信号相加而得的信号,其对应于电阻变化型存储元件的设定时的写入。对行施加的驱动信号vpost是将由行_正部分驱动器132生成的电压信号与由行_负部分驱动器134生成的电压信号相加而得的信号,其对应于电阻变化型存储元件的重设时的写入。

[0042]

另外,控制器140可包括感测电路,当进行读出动作时,感测电路感测由列选择/驱动电路120或行选择/驱动电路130选择的列或行的电压或电流。

[0043]

输入/输出部150例如经由内部数据总线而与控制部140连接,并向控制部140提供自外部接收的数据,或者将自控制部140接收的数据输出至外部。控制部140可自输入/输出部150获得用于向电阻变化型存储元件mc进行stdp的写入的数据。

[0044]

接着,参照图6的(a)~图6的(d)对本实施例的stdp的写入方法进行说明。图6的(a)是由突触前神经元生成的电压信号vpre与由突触后神经元生成的电压信号vpost的原始波形。电压信号vpre包括正的矩形波脉冲pa、以及陡峭的自负电位缓慢衰减的负三角波脉冲pb,电压信号vpost包括正的矩形波脉冲ta、以及陡峭的自负电位缓慢衰减的负三角波脉冲tb。此处,设为电压信号vpre比电压信号vpost更早地产生(δt>0)。

[0045]

stdp是将电压信号vpre与电压信号vpost之差(vpost

‑

vpre)施加至电阻变化型存储元件的过程。所述差可如式(1)般进行转换。

[0046]

vpost

‑

vpre=(ta

‑

tb)

‑

(pa

‑

pb)

[0047]

=(ta pb)

‑

(pa tb)

…

(1)

[0048]

式(1)中,于使(ta pb)对应于电阻变化型存储元件的设定写入的情况下,可使极性与(ta pb)不同的(pa tb)对应于重设写入。或者,于使(ta pb)对应于重设写入的情况下,可使(pa tb)对应于设定写入。于以下的例子中,将(pa tb)设为设定写入电压,将(ta pa)设为重设写入电压。

[0049]

图6的(b)表示将原始的电压信号vpre、电压信号vpost分别转换为式(1)所示的四个项的状况。此处应注意,负的三角波脉冲pb、三角波脉冲tb被转换为正的三角波脉冲pb、三角波脉冲tb,四个脉冲全部为正。因此,四个脉冲可由利用正电位的四个驱动器分别生成。

[0050]

图6的(c)例示了依照式(1)将电压信号vpre的矩形波脉冲pa与电压信号vpost的三角波脉冲tb合成而得的驱动信号vpre、以及将电压信号vpost的矩形波脉冲ta与电压信

号vpre的三角波脉冲pb合成而得的驱动信号vpost。图6的(d)例示了对电阻变化型存储元件施加的电位差vnet(=vpost

‑

vpre)。对电阻变化型存储元件施加超过设定写入的临限值vtset的脉冲,电阻变化型存储元件的电导变大,即,突触的结合强度被强化。再者,虽然此处未示出δt<0的情况,但于该情况下,对电阻变化型存储元件施加超过重设写入的临限值vtreset的脉冲,电阻变化型存储元件的电导降低,即突触的结合强度衰减。

[0051]

图7表示本实施例的列选择/驱动电路120及行选择/驱动电路130中所含的四路驱动器(quad driver)200。四路驱动器200包括以下四个驱动器:列选择/驱动电路120中所含的列_正部分驱动器122及列_负部分驱动器124、以及行选择/驱动电路130中所含的行_正部分驱动器132及行_负部分驱动器134。列_正部分驱动器122及列_负部分驱动器124分别生成式(1)的(pa tb)的脉冲信号,行_正部分驱动器132及行_负部分驱动器134分别生成(ta pb)的脉冲信号。四个驱动器122、124、132、134生成正的脉冲波形,且全部利用正电位运作,而不利用负电位或负电源。

[0052]

当向纵横式数组110的电阻变化型存储元件mc进行stdp的写入时,列选择/驱动电路120基于来自控制部140的列地址,将列_正部分驱动器122及列_负部分驱动器124连接于所选择的列线r1,行选择/驱动电路130基于来自控制部140的行地址,将行_正部分驱动器132及行_负部分驱动器134连接于所选择的行线c1。

[0053]

列_正部分驱动器122响应于来自控制部140的赋能信号oep而生成矩形波脉冲pa,列_负部分驱动器124响应于来自控制部140的赋能信号oet而生成三角波脉冲tb,利用加法器126对矩形波脉冲pa与三角波脉冲tb进行合成,并将所合成的驱动信号vpre作为设定写入电压而经由列线r1施加至电阻变化型存储元件mc的一个端子。另外,行_正部分驱动器132响应于来自控制部140的赋能信号oet而生成矩形波脉冲ta,行_负部分驱动器134响应于来自控制部140的赋能信号oep而生成三角波脉冲pb,利用加法器136对矩形波脉冲ta与三角波脉冲pb进行合成,并将所合成的驱动信号vpost作为重设写入电压而经由行线c1施加至电阻变化型存储元件mc的另一个端子。另外,列选择/驱动电路120使非选择的列线r2成为浮接(floating)状态或对非选择的列线r2施加写入禁止电压vinh,行选择/驱动电路130使非选择的行线c2成为浮接状态或对非选择的行线c2施加写入禁止电压vinh。

[0054]

控制部140可经由赋能信号使四个驱动器分别独立地运作,并将(pa tb)的驱动信号vpre及(ta pb)的驱动信号vpost以所期望的时序施加至电阻变化型存储元件mc。藉此,向电阻变化型存储元件mc进行stdp的写入。

[0055]

如上所述,根据本实施例,通过针对一个神经元而使用至少四个正电位的驱动器,纵横式数组的周边电路可于不处理负电位的情况下,通过利用正电位的双极动作来进行stdp的写入。藉此,可谋求突触数组装置的低成本化及低电力消耗化。

[0056]

于所述实施例中,通过选择列线及行线来对电阻变化型存储元件施加驱动信号vpre/vpost,但若纵横式数组进一步高集成化或小型化,则于通过列线及行线的偏压(bias)而进行的控制中,有与邻接的电阻变化型存储元件的隔离不充分之虞。因此,亦可设置用于选择电阻变化型存储元件的选择装置(选择器器件)。

[0057]

选择装置例如为存取用晶体管,且电阻变化型存储元件包括可变电阻组件与晶体管(1t1r)。该情况下,存取用晶体管的闸极与列线(字线)连接,当存取用晶体管导通时,可变电阻组件的一个端子与位线电性连接,另一个端子与源极线电性连接。当进行stdp的写

入时,例如对位线施加驱动信号vpre,并对源极线施加驱动信号vpost。另外,作为选择装置,亦可使全部的可变电阻组件与二极管整合,以防止不期望的电流流至非选择的可变电阻组件。该情况下,二极管具有如下特性:当正向偏压成为一定以上时,正向地流动电流,当反向偏压成为一定以上时,反向地流动电流。

[0058]

于所述实施例中,将尖峰信号近似成正的矩形波脉冲与负的三角波脉冲,其结果,为了向一个电阻变化型存储元件进行stdp的写入而使用了四个正电位的驱动器122、124、132、134,但本发明并非一定限定于此。例如,于将一个尖峰信号近似为一个正的矩形波脉冲、一个负的矩形波脉冲、以及一个负的三角波脉冲的情况下,对列线施加的驱动信号vpre为三个正电位的驱动器的正的脉冲信号的合成,对行线施加的驱动信号vpost为三个正电位的驱动器的正的脉冲信号的合成。

[0059]

对本发明的较佳实施方式进行了详述,但本发明并不限定于特定的实施方式,而是可于权利要求所记载的本发明的主旨的范围内进行各种变形、变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。