1.本发明涉及半导体器件及其温度测量技术领域,特别是涉及一种压接型功率半导体器件及其温度分布测量系统。

背景技术:

2.随着柔性直流输电技术的发展,绝缘栅双极性晶体管(insulated gate bipolar transistor,igbt)器件作为换流阀和断路器中的关键器件,越来越受到重视。近年来,出现了压接封装形式的igbt器件,与传统焊接式igbt模块相比,具有功率密度大、易于串联和失效短路等优点,现已逐步应用于高压大功率输电的场合。

3.对多芯片规模化并联成组的压接型igbt器件而言,由于内部各物理场的相互作用,使得各半导体芯片的结温间出现差异,进而对器件性能及可靠性产生影响。因此,各半导体芯片的结温的准确测量成为压接型igbt器件应用中最为关注的问题之一。

4.由于压接封装形式的特殊性,在焊接封装形式中广泛应用的红外测温法、接触式测温法难以应用到压接器件温度测量中来。目前广泛应用于压接型igbt器件的温度测量方法是热敏电参数法,其原理是首先得到器件小电流下饱和压降与结温的关系,而后通过测量小电流下器件的饱和压降,转换获得器件的结温。对单芯片器件来说,热敏电参数法可以得到芯片的结温,满足测量需求,但对多芯片器件而言,热敏电参数法仅能得到所有芯片的平均结温,并不能精确获得各半导体芯片的结温的分布情况。

技术实现要素:

5.本发明的目的是提供一种压接型功率半导体器件及其温度分布测量系统,以解决现有技术中存在的不能精确获得各半导体芯片的结温分布情况的问题,且具有结构简单、测量精确等特点。

6.为实现上述目的,本发明提供了如下方案:

7.一种压接型功率半导体器件,包括:多个子模组、多个凸台和pcb板;所述子模组一一对应设置在所述凸台上;所述pcb板上设置有多个通孔,且所述凸台设置于所述通孔中;所述pcb板上设置有多个接口端子;

8.所述子模组包括:上钼片、半导体芯片和下钼片;

9.所述半导体芯片设置于所述上钼片和所述下钼片之间;所述半导体芯片的栅极与所述pcb板上的接口端子一一对应连接;

10.所述pcb板用于对每一所述子模组进行驱动;所述上钼片与所述下钼片形成应力缓冲区。

11.优选的,压接型功率半导体器件还包括:集电极极板和发射极极板;

12.所述集电极极板和所述发射极极板用于与外部电路连接;且所述集电极极板、所述上钼片、所述半导体芯片、所述下钼片和所述发射极极板形成电流回路。

13.优选的,所述子模组还包括:数量与所述子模组数量相同的子模组框架;所述子模

组框架套设在所述子模组上;所述子模组框架用于固定所述子模组。

14.优选的,所述子模组还包括:银垫片;所述银垫片设置于所述下钼片和所述凸台之间;所述银垫片用于补偿各所述子模组中组件的高度公差。

15.优选的,压接型功率半导体器件还包括:外接引线;所述外接引线的数量与所述pcb板上的接口端子的数量相同,且所述外接引线与所述接口端子一一对应连接。

16.一种压接型功率半导体器件的温度分布测量系统,用于测量上述压接型功率半导体器件的温度分布;所述温度分布测量系统包括:第一电流源、测试支路开关、第二电流源、时序驱动电路和探头;

17.所述第一电流源、所述测试支路开关和待测压接型功率半导体器件依次串联,以构成加热通路;所述第一电流源用于提供加热电流;所述测试支路开关用于控制所述加热通路的开启和关断;

18.所述第二电流源和所述探头均与所述待测压接型功率半导体器件并联;所述第二电流源用于提供测量电流;所述探头用于测量所述待测压接型功率半导体器件的饱和压降;

19.所述时序驱动电路通过外接引线与所述待测压接型功率半导体器件中pcb板上的接口端子连接;所述时序驱动电路用于控制所述待测压接型功率半导体器件中各半导体芯片的导通和关断。

20.优选的,所述探头包括电压探头;

21.所述电压探头与所述待测压接型功率半导体器件并联;所述电压探头用于测量所述待测压接型功率半导体器件的饱和压降。

22.根据本发明提供的具体实施例,本发明公开了以下技术效果:

23.本发明提供的压接型功率半导体器件,将每一半导体芯片的栅极分别连接于pcb板的接口端子上,以便于对压接型功率半导体器件中的每一半导体芯片的结温进行测量,进而提高温度分布测量的准确性。

24.并且,本发明提供的压接型功率半导体器件的温度分布测量系统,通过采用时序驱动电路使得待测压接型功率半导体器件进行周期开断,以模拟压接型功率半导体器件在不同工况下的发热情况。且通过与测量支路开关的时序配合,能够实现各半导体芯片的结温分布的时序准确测量,突破了现有测量方法仅能获得各半导体芯片平均结温的局限性。

附图说明

25.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

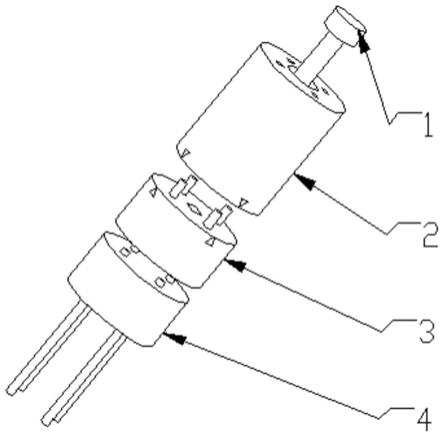

26.图1为本发明提供的压接型功率半导体器件的结构示意图;

27.图2为本发明实施例中各半导体芯片栅极与pcb板上各接口端子的连接示意图;

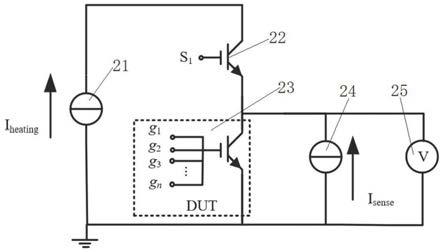

28.图3为本发明提供的压接型功率半导体器件的温度分布测量系统的电路图;

29.图4为本发明实施例校准过程中各半导体芯片栅极电压施加时序的示意图;

30.图5为本发明实施例中获得各半导体芯片校准曲线的转换过程示意图;

31.图6为本发明实施例中测温过程驱动控制时序图;

32.图7为本发明实施例中获得各半导体芯片温度分布的转换过程示意图。

33.附图中符号说明:

34.1集电极极板,2上钼片,3半导体芯片,3-1半导体芯片的栅极,4下钼片,5银垫片,6凸台,7子模组框架,8pcb板,8-1接口端子,9发射极极板,10电极法兰,11陶瓷管壳,12外接引线,21第一电流源,22测试支路开关,23待测器件,24第二电流源,25探头。

具体实施方式

35.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

36.本发明的目的是提供一种压接型功率半导体器件及其温度分布测量系统,以解决现有技术中存在的不能精确获得各半导体芯片的结温分布情况的问题,且具有结构简单、测量精确等特点。

37.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

38.图1为本发明提供的压接型功率半导体器件的结构示意图,如图1所示,一种压接型功率半导体器件,包括:集电极极板1、多个子模组(图1中未对其进行具体标号)、凸台6、pcb板8、陶瓷管壳11及外接引线12。

39.所述子模组一一对应设置在所述凸台6上;所述pcb板上设置有多个通孔,且所述凸台设置于所述通孔中;所述pcb板8上设置有多个接口端子8-1;凸台6用于支撑子模组,并对各子模组进行定位。

40.所述子模组包括:上钼片2、半导体芯片3、下钼片4、银垫片5和子模组框架7。

41.所述半导体芯片3设置于所述上钼片2和所述下钼片4之间;所述半导体芯片3的栅极3-1与所述pcb板8上的接口端子8-1一一对应连接;其具体连接关系如图2所示。

42.所述集电极极板1和所述发射极极板9用于与外部电路连接;

43.所述pcb板8用于对每一所述子模组进行驱动;所述上钼片2与所述下钼片4形成应力缓冲区,可以使半导体芯片3应力分布更均匀,起保护作用。

44.所述银垫片5设置于所述下钼片4和所述凸台6之间;所述银垫片5用于补偿各所述子模组中组件的高度公差。

45.所述子模组框架7套设在所述子模组上;所述子模组框架7用于固定所述子模组。

46.所述外接引线12的数量与所述pcb板8上的接口端子8-1的数量相同,且所述外接引线12与所述接口端子8-1一一对应连接。pcb板8及引线12用于提供栅极驱动信号。为了与所述温度分布时序测量方法配合,相对于现有商用器件中pcb板而言,本发明所采用的pcb板8中的各驱动回路为单独控制。

47.此外,为了使器件免受外界污染,压接型功率半导体器件还可以进一步包括电极法兰10和陶瓷管壳11,以为其提供密封环境。

48.本发明还对应提供了一种压接型功率半导体器件的温度分布测量系统,以用于测

量上述压接型功率半导体器件的温度分布;在对压接型功率半导体器件进行温度测量的过程中,集电极极板1与发射极极板9与外部电路相连,集电极极板1、上钼片2、半导体芯片3、下钼片4、银垫片5、凸台6和发射极极板9形成电流和热流通路,半导体芯片3的栅极通过pcb板8及引线12与外部驱动回路相连,进而通过图1中外接引线12引出到器件外部,与驱动电路相连,实现对各并联半导体芯片栅极的单独控制,并配合驱动信号的时序控制,突破了现有测量方式对各并联半导体芯片栅极一起控制,仅能获得器件平均结温的局限。

49.图3为本发明提供的压接型功率半导体器件的温度分布测量系统的结构示意图,如图3所示,该温度分布测量系统包括:第一电流源21(电流源i

heating

)、测试支路开关22、第二电流源24(电流源i

sense

)、时序驱动电路(图3中未示出)和探头25(探头v)。

50.所述第一电流源21、所述测试支路开关22和待测压接型功率半导体器件(待测器件23)依次串联,以构成加热通路;所述第一电流源21用于提供加热电流;所述测试支路开关22用于控制所述加热通路的开启和关断。

51.所述第二电流源24和所述探头25均与所述待测压接型功率半导体器件并联;所述第二电流源24用于提供测量电流;所述探头25用于测量所述待测压接型功率半导体器件的饱和压降。

52.所述时序驱动电路通过外接引线12与所述待测压接型功率半导体器件中pcb板8上的接口端子8-1连接;所述时序驱动电路用于控制所述待测压接型功率半导体器件中各半导体芯片3的导通和关断。

53.上述探头25可以包括电压探头。

54.所述电压探头与与所述待测压接型功率半导体器件并联;所述电压探头用于测量所述待测压接型功率半导体器件的饱和压降。

55.进一步,上述电压探头的第一连接端与所述待测压接型功率半导体器件的集电极极板1连接,第二连接端与所述待测压接型功率半导体器件的发射极极板9连接。

56.具体的,待测器件23内各半导体芯片栅极信号g1,g2,

…

,g

n

通过图2所述pcb板8引出,与外部驱动电路相连。电压探头与图1所述器件集电极极板1和发射极极板9相连,用于实时记录待测压接型功率半导体器件两端的压降。电流源i

sense

提供测量用直流小电流(通常为数十毫安),用于测量饱和压降v

ce

,该电流大小足以使v

ce

超过其饱和值并与芯片的结温呈较好的线性关系,又可避免大电流下自加热效应。电流源i

heating

为加热电流,通过测试支路开关s1控制支路的开通关断,实现待测压接型功率半导体器件在不同工况下的发热。与现有技术中所有半导体芯片栅极一起控制相比,该测量过程中各半导体芯片的栅极由前述pcb板8通过外部驱动电路单独控制,可以实现各半导体芯片的结温的时序测量。

57.采用本发明提供的温度分布测量系统对上述压接型功率半导体器件的温度分布进行测量的步骤分为两个,第一步是校准各半导体芯片电学参数v

ce

与结温tj关系;第二步是依据校准曲线,对待测器件dut中各半导体芯片的结温进行周期性测量。

58.步骤一:测量各半导体芯片电学参数v

ce

与结温t

j

的关系,获得校准曲线

59.11)校准过程中图3所述测试支路开关s1断开,测量电流i

sense

流经待测器件dut,待测器件dut与相应的测量夹具放入恒温箱中。将恒温箱升高到指定温度(依据需要人为设定),而后在降温过程中通过探头v实时记录器件两端饱和压降v

ce

数值和待测器件dut的温度t

j

。降温过程中,通过外部驱动电路控制各半导体芯片的栅极g1,g2,

…

,g

n

依次开通关断,

并周期性循环,以使测量电流i

sense

依次流过所有半导体芯片,从而在保持原有封装结构条件下,能够一次校准所有并联芯片,驱动信号时序如图4所示。

60.12)将所记录的待测器件dut两端饱和压降v

ce

数值和温度t

j

的关系转换成各半导体芯片饱和压降v

ce

数值和温度t

j

的关系,以得到校准曲线。

61.上述转换过程如图5所示,依据步骤11)中所测不同时刻的v

ce

和t

j

数据,可以获得不同时刻待测器件dut两端的饱和压降v

ce

和t

j

的逐点对应关系(v

ce

,t

j

)。进一步地,结合图4中不同时刻各半导体芯片的导通情况,可分别将不同半导体芯片导通时所对应时刻的(v

ce

,t

j

)连接成线,以生成各半导体芯片的校准曲线。

62.步骤二:是依据校准曲线,对待测器件dut中各半导体芯片的结温进行周期性测量,得到待测器件dut中各半导体芯片的结温分布。

63.21)温度测量过程中,图3所述电路中测试支路开关s1在图6的(a)部分中信号g1的控制下周期性开通关断。当测试支路开关s1开通时,电流源i

heating

使待测器件dut升温。当测试支路开关s1关断时,待测器件dut降温,待测器件dut内各半导体芯片温度如图6中的(b)部分所示。在不同周期的待测器件dut的降温过程中,电流源i

sense

通过图6中的(b)部分到图6中的(f)部分,驱动信号的时序控制依次流经各半导体芯片,同时,通过电压探头实时记录待测器件dut两端饱和压降v

ce

的数值。

64.22)依据步骤一中获得的各半导体芯片校准曲线,将器件两端饱和压降v

ce

转换为各半导体芯片的结温。转换过程如图7所示。首先,根据图6(b)部分到图6(f)部分中的驱动信号控制时序,可以确定各周期降温过程中开通半导体芯片的编号。其次,选择步骤一所获得的各半导体芯片的v

ce-t

j

校准曲线,即可将待测器件dut两端的饱和压降v

ce

转换为所对应半导体芯片的结温。最后,由于在周期加热过程中待测器件dut已经到达稳态,各周期下待测器件dut内各半导体芯片的结温分布是相同的,因而,通过上述过程可以等价获得同一周期内各半导体芯片的结温分布。

65.总而言之,与现有温敏电参数法只能获得待测器件的平均结温相比,本发明所提供的温度分布测量系统可以通过对各半导体芯片栅极的单独控制,在不同周期内获得不同半导体芯片的结温,进而获得同一周期内各半导体芯片的结温分布,为压接型功率半导体器件的设计提供可靠性参考。

66.上述测量过程中所采用的待测器件dut为本发明提供的压接型功率半导体器件,但不限于此。

67.与最接近的现有技术相比,本使用新型所提供的技术方案还具有以下优点:

68.1、现有压接型igbt器件结温测量技术采用热敏电参数法,仅能测量各半导体芯片的平均结温,不能得到各半导体芯片间的结温分布情况。本发明提供的技术方案通过将栅极驱动回路设计为单独控制,且通过与测量支路开关的时序配合,可以获得不同工况下各半导体芯片的结温分布情况。

69.2、本发明提供的技术方案仅对栅极驱动回路进行了优化设计,改造部分少,更换灵活,便于科学研究。此外,还可以方便地集成在器件中,在离线情况评估器件内部各半导体芯片处的老化情况。

70.3、本发明提供的技术方案通过各半导体芯片栅极的单独控制,还可以实现多颗半导体芯片电参数与结温关系的快速校准,进一步为各半导体芯片的结温分布的测量提供便

利。

71.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。

72.本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本发明的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。