1.本技术实施例涉及计算机技术领域,尤其涉及一种数据备份方法、装置及存储介质。

背景技术:

2.车控电子控制单元(electronic control unit,ecu)可以控制车辆的运行状态,也可以采集驾驶过程中产生的行驶数据。这些数据中包含一些有非易失存储要求的数据(non volatile data,nv data)。现有的,可以采用非易失性存储器(non volatile memory,nvm)管理组件对nv data进行管理维护等操作,根据存储介质的不同,目前对于nv data的管理有两种方式,包括基于外设带电可擦可编程只读存储器(electrically erasable programmable read only memory,eeprom)的管理机制和基于flash模拟eeprom的管理机制。

3.对于外设eeprom的管理机制而言,微控制单元(microcontroller unit,mcu)通过串行外设接口(serial peripheral interface,spi)与eeprom外设芯片通信,mcu与外设的spi可能会被干扰或中断,可能会造成存储数据的失效。对于flash模拟eeprom的管理机制而言,如相关flash操作被意外中断,可能导致flash误差校正码(error correcting code,ecc)错误,导致flash整块失效,造成更大规模的数据损坏。可以看出,现有的两种对于nv data的管理机制存储数据的可靠性不足。

技术实现要素:

4.本技术提供一种数据备份方法、装置及存储介质,通过将flash模拟eeprom的管理机制与外设eeprom的管理机制两种机制相结合,实现对非易失性数据的备份,从而提高对非易失性数据存储的可靠性。

5.为达到上述目的,本技术采用如下技术方案:

6.第一方面,本技术提供一种数据备份方法,包括:在检测到有非易失性数据写入的情况下,将非易失性数据同步写入微控制单元的第一随机存取存储器和第二随机存取存储器;在执行系统周期性任务的剩余时长内,将第一随机存取存储器中的非易失性数据写入微控制单元的flash,并且通过执行预设周期性任务将第二随机存取存储器中的非易失性数据写入微控制单元外设的eeprom。

7.本技术提供的技术方案中,在检测到有非易失性数据写入时,将非易失性数据同步写入两个随机存取存储器,然后分别将两个随机存取存储器中的非易失性数据写入两种不同的存储介质(flash和eeprom)。由于写入两种存储介质的非易失性数据同时失效或损坏的可能性较低,所以本技术技术方案通过两种存储介质对非易失性数据进行双重备份,可以提高对非易失性数据存储的可靠性。另外,由于现有的flash模拟eeprom的管理机制与外设eeprom的管理机制的存储对象的限制,写入过程要求差异较大,所以本技术中还对两种机制的写入过程进行了优化,在执行系统周期性任务的剩余时长内,实现flash模拟

eeprom的管理机制的写入(对应本技术中的将第一随机存取存储器中的非易失性数据写入微控制单元的flash)。并且,通过预设周期性任务实现外设eeprom的管理机制的写入(对应本技术中的将第二随机存取存储器中的非易失性数据写入微控制单元外设的eeprom)。这样,能够减小两种机制写入过程的差异,从而更好的完成双重机制写入,以保证车控ecu的正常运行和上下电时间要求。

8.可选的,在一种可能的设计方式中,本技术提供的数据备份方法还可以包括:

9.将flash中的非易失性数据读取至第一随机存取存储器,并将外设eeprom中的非易失性数据读取至第二随机存取存储器;

10.对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行一致性校验;

11.在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据一致的情况下,将第一随机存取存储器中的非易失性数据或第二随机存取存储器中的非易失性数据读取至微控制单元。

12.可选的,在另一种可能的设计方式中,上述“对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行一致性校验”之后,可以包括:

13.在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据不一致的情况下,对比第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据的时间戳;

14.根据时间戳的先后顺序,将第一随机存取存储器中的非易失性数据或第二随机存取存储器中的非易失性数据读取至微控制单元。

15.可选的,在另一种可能的设计方式中,上述“对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行一致性校验”之前,可以包括:

16.对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行有效性检验;

17.确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据均为有效数据。

18.可选的,在另一种可能的设计方式中,上述“对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行有效性检验”之后,可以包括:

19.在确定第一随机存取存储器中的非易失性数据为有效数据,且第二随机存取存储器中的非易失性数据为无效数据的情况下,将第一随机存取存储器中的非易失性数据读取至微控制单元;

20.或者,在确定第二随机存取存储器中的非易失性数据为有效数据,且第一随机存取存储器中的非易失性数据为无效数据的情况下,将第二随机存取存储器中的非易失性数据读取至微控制单元。

21.可选的,在另一种可能的设计方式中,上述“对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行有效性检验”之后,可以包括:

22.在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据均为无效数据的情况下,将预设数据读取至微控制单元。

23.可选的,在另一种可能的设计方式中,上述“将第一随机存取存储器中的非易失性

数据写入微控制单元的flash”可以包括:在接收到第一反馈信息的情况下,将第一随机存取存储器中的非易失性数据写入flash;第一反馈信息用于指示,非易失性数据写入flash完成;上述“将第二随机存取存储器中的非易失性数据写入微控制单元外设的eeprom”可以包括:在接收到第二反馈信息的情况下,将第二随机存取存储器中的非易失性数据写入外设eeprom;第二反馈信息用于指示,非易失性数据写入外设eeprom完成。

24.第二方面,本技术提供一种数据备份装置,包括:检测模块和写入模块;

25.检测模块,用于检测是否有非易失性数据写入;

26.写入模块,用于在检测模块检测到有非易失性数据写入的情况下,将非易失性数据同步写入微控制单元的第一随机存取存储器和第二随机存取存储器;

27.写入模块,还用于在执行系统周期性任务的剩余时长内,将第一随机存取存储器中的非易失性数据写入微控制单元的flash,并且通过执行预设周期性任务将第二随机存取存储器中的非易失性数据写入微控制单元外设的eeprom。

28.可选的,在一种可能的设计方式中,本技术提供的数据备份装置还可以包括:读取模块和校验模块;

29.读取模块用于,将flash中的非易失性数据读取至第一随机存取存储器,并将外设eeprom中的非易失性数据读取至第二随机存取存储器;

30.校验模块用于,对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行一致性校验;

31.读取模块还用于,在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据一致的情况下,将第一随机存取存储器中的非易失性数据或第二随机存取存储器中的非易失性数据读取至微控制单元。

32.可选的,在另一种可能的设计方式中,本技术提供的数据备份装置还可以包括:对比模块;

33.对比模块,用于在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据不一致的情况下,对比第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据的时间戳;

34.读取模块,还用于根据时间戳的先后顺序,将第一随机存取存储器中的非易失性数据或第二随机存取存储器中的非易失性数据读取至微控制单元。

35.可选的,在另一种可能的设计方式中,校验模块,还用于:

36.对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行有效性检验;

37.确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据均为有效数据。

38.可选的,在另一种可能的设计方式中,

39.读取模块还用于,在确定第一随机存取存储器中的非易失性数据为有效数据,且第二随机存取存储器中的非易失性数据为无效数据的情况下,将第一随机存取存储器中的非易失性数据读取至微控制单元;

40.或者,读取模块还用于,在确定第二随机存取存储器中的非易失性数据为有效数据,且第一随机存取存储器中的非易失性数据为无效数据的情况下,将第二随机存取存储

器中的非易失性数据读取至微控制单元。

41.可选的,在另一种可能的设计方式中,

42.读取模块还用于,在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据均为无效数据的情况下,将预设数据读取至微控制单元。

43.可选的,在另一种可能的设计方式中,写入模块具体用于:在接收到第一反馈信息的情况下,将第一随机存取存储器中的非易失性数据写入flash;第一反馈信息用于指示,非易失性数据写入flash完成;写入模块还具体用于:在接收到第二反馈信息的情况下,将第二随机存取存储器中的非易失性数据写入外设eeprom;第二反馈信息用于指示,非易失性数据写入外设eeprom完成。

44.第三方面,本技术提供一种数据备份装置,包括存储器、处理器、总线和通信接口;存储器用于存储计算机执行指令,处理器与存储器通过总线连接;当数据备份装置运行时,处理器执行存储器存储的计算机执行指令,以使数据备份装置执行如上述第一方面提供的数据备份方法。

45.可选的,该数据备份装置可以是用于实现数据备份的芯片系统。该芯片系统用于支持数据备份装置实现第一方面中所涉及的功能,例如,接收,发送或处理上述数据备份方法中所涉及的数据和/或信息。该芯片系统包括芯片,也可以包括其他分立器件或电路结构。

46.第四方面,本技术提供一种计算机可读存储介质,计算机可读存储介质中存储有指令,当计算机执行指令时,使得计算机执行如第一方面提供的数据备份方法。

47.第五方面,本技术提供一种计算机程序产品,该计算机程序产品包括计算机指令,当计算机指令在计算机上运行时,使得计算机执行如第一方面提供的数据备份方法。

48.需要说明的是,上述计算机指令可以全部或者部分存储在计算机可读存储介质上。其中,计算机可读存储介质可以与数据备份装置的处理器封装在一起的,也可以与数据备份装置的处理器单独封装,本技术对此不做限定。

49.本技术中第二方面、第三方面、第四方面以及第五方面的描述,可以参考第一方面的详细描述;并且,第二方面、第三方面、第四方面以及第五方面的描述的有益效果,可以参考第一方面的有益效果分析,此处不再赘述。

50.在本技术中,上述数据备份装置的名字对设备或功能模块本身不构成限定,在实际实现中,这些设备或功能模块可以以其他名称出现。只要各个设备或功能模块的功能和本技术类似,属于本技术权利要求及其等同技术的范围之内。

51.本技术的这些方面或其他方面在以下的描述中会更加简明易懂。

附图说明

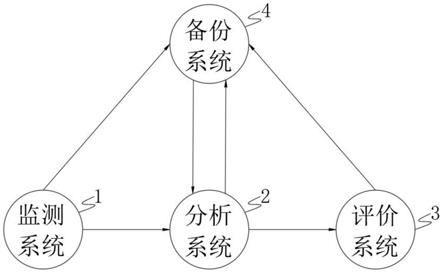

52.图1为本技术实施例提供的一种数据备份系统的架构示意图;

53.图2为本技术实施例提供的一种数据备份方法的流程示意图;

54.图3为本技术实施例提供的另一种数据备份方法的流程示意图;

55.图4为本技术实施例提供的又一种数据备份方法的流程示意图;

56.图5为本技术实施例提供的一种数据备份装置的结构示意图;

57.图6为本技术实施例提供的另一种数据备份装置的结构示意图。

具体实施方式

58.下面结合附图对本技术实施例提供的数据备份方法、装置及存储介质进行详细地描述。

59.本文中术语“和/或”,仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。

60.本技术的说明书以及附图中的术语“第一”和“第二”等是用于区别不同的对象,或者用于区别对同一对象的不同处理,而不是用于描述对象的特定顺序。

61.此外,本技术的描述中所提到的术语“包括”和“具有”以及它们的任何变形,意图在于覆盖不排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备没有限定于已列出的步骤或单元,而是可选的还包括其他没有列出的步骤或单元,或可选的还包括对于这些过程、方法、产品或设备固有的其它步骤或单元。

62.需要说明的是,本技术实施例中,“示例性的”或者“例如”等词用于表示作例子、例证或说明。本技术实施例中被描述为“示例性的”或者“例如”的任何实施例或设计方案不应被解释为比其它实施例或设计方案更优选或更具优势。确切而言,使用“示例性的”或者“例如”等词旨在以具体方式呈现相关概念。

63.在本技术的描述中,除非另有说明,“多个”的含义是指两个或两个以上。

64.车控ecu可以控制车辆的运行状态,也可以采集驾驶过程中产生的行驶数据。这些数据中包含一些nv data。现有的,可以采用nvm管理组件对nv data进行管理维护等操作,根据存储介质的不同,目前对于nv data的管理有两种方式,包括基于外设eeprom的管理机制和基于flash模拟eeprom的管理机制。

65.对于外设eeprom的管理机制而言,mcu通过spi与eeprom外设芯片通信,mcu与外设的spi可能会被干扰或中断,可能会造成存储数据的失效。对于flash模拟eeprom的管理机制而言,如相关flash操作被意外中断,可能导致flash的ecc错误,导致flash整块失效,造成更大规模的数据损坏。可以看出,现有的两种对于nv data的管理机制存储数据的可靠性不足。

66.针对上述现有技术中存在的问题,本技术实施例提供了一种数据备份方法,该方法通过两种存储介质对非易失性数据进行双重备份,可以提高对非易失性数据存储的可靠性,并且通过对两种存储介质的存储机制进行优化,可以更好的完成双重机制写入,以保证车控ecu的正常运行和上下电时间要求。

67.本技术实施例提供的数据备份方法可以适用于数据备份系统,数据备份系统中可以包括数据备份装置、第一随机存取存储器(random access memory,ram)、第二随机存取存储器、flash以及外设eeprom。

68.示例性的,数据备份装置可以为nvm管理组件。参照图1,数据备份系统可以包括nvm管理组件、第一随机存取存储器、第二随机存取存储器、flash以及外设eeprom。其中,nvm管理组件、第一随机存取存储器、第二随机存取存储器、flash以及外设eeprom为同一mcu的不同存储介质。

69.如图1所示,nvm管理组件和第一随机存取存储器之间可以实现读写操作,nvm管理组件和第二随机存取存储器之间可以实现读写操作,第一随机存取存储器与flash之间可以实现读写操作,第二随机存取存储器与外设eeprom之间可以实现读写操作。

70.下面结合上述图1示出的数据备份系统对本技术提供的数据备份方法进行说明。

71.参照图2,本技术实施例提供的数据备份方法包括s201

‑

s203:

72.s201、检测是否有非易失性数据写入。

73.非易失性数据也即是有非易失存储要求的数据。

74.s202、在检测到有非易失性数据写入的情况下,将非易失性数据同步写入微控制单元的第一随机存取存储器和第二随机存取存储器。

75.s203、在执行系统周期性任务的剩余时长内,将第一随机存取存储器中的非易失性数据写入微控制单元的flash,并且通过执行预设周期性任务将第二随机存取存储器中的非易失性数据写入微控制单元外设的eeprom。

76.其中,系统周期性任务可以是微控制单元原有的一些周期性任务。在检测到有非易失性数据写入的情况下,可以利用系统周期性任务的剩余时长将第一随机存取存储器中的非易失性数据写入微控制单元的flash。

77.示例性的,若系统周期性任务的第一周期与第二周期的时间间隔为10ms,在第一周期内,执行系统周期性任务所需时长为5ms,在第二周期内,执行系统周期性任务所需时长为7ms。这样,就可以在第一周期内的剩余时长5ms内将第一随机存取存储器中的非易失性数据写入微控制单元的flash,在第二周期内的剩余时长3ms内将第一随机存取存储器中的非易失性数据写入微控制单元的flash。

78.可选的,在一种可能的实现方式中,对flash模拟eeprom的管理机制的优化可以通过设置系统周期性任务与将第一随机存取存储器中的非易失性数据写入微控制单元的flash任务的优先级的高低来实现。具体的,可以确定系统周期性任务的优先级高于flash模拟eeprom操作任务的优先级,这样,可以按照优先级的高低顺序,优先执行系统周期性任务,在执行系统周期性任务的剩余时长内将第一随机存取存储器中的非易失性数据写入微控制单元的flash,保证不对原有的系统周期性任务造成影响。

79.预设周期性任务可以是事先确定的周期性任务,该预设周期性任务专用于执行将第二随机存取存储器中的非易失性数据写入微控制单元外设的eeprom。其中,预设周期性任务的周期可以根据外设eeprom的忙碌状态的时长确定。示例性的,若外设eeprom的忙碌状态为4ms,则预设周期性任务的周期可以为5ms。这样,mcu可以在外设eeprom的4ms忙碌状态下去执行其他任务,在忙碌状态解除后,预设周期性任务再次调度,将第二随机存取存储器中的非易失性数据写入微控制单元外设的eeprom。

80.可选的,本技术实施例提供的数据备份方法还可以包括:将flash中的非易失性数据读取至第一随机存取存储器,并将外设eeprom中的非易失性数据读取至第二随机存取存储器;对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行一致性校验;在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据一致的情况下,将第一随机存取存储器中的非易失性数据或第二随机存取存储器中的非易失性数据读取至微控制单元。

81.由于本技术实施例中是通过双重机制对非易失性数据进行备份的,所以在读取非易失性数据的过程中,可以先对双重备份的非易失性数据进行一致性校验。若第一随机存取存储器和第二随机存取存储器中的非易失性数据一致,表示通过两种机制存储的非易失性数据均未受到损坏,数据的更新时间相同,此时读取通过任一机制存储的非易失性数据

均可。

82.可选的,本技术实施例提供的数据备份方法还可以包括:在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据不一致的情况下,对比第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据的时间戳;根据时间戳的先后顺序,将第一随机存取存储器中的非易失性数据或第二随机存取存储器中的非易失性数据读取至微控制单元。

83.本技术实施例对两种机制的写入过程进行了优化,减少了写入过程的差异,但是两种写入机制仍存在微小差异。这样,非易失性数据从第一随机存取存储器写入flash的写入时间与非易失性数据从第二随机存取存储器写入外设eeprom的写入时间可能存在差异,第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据可能不一致。所以,本技术实施例中可以对比两中机制存储的非易失性数据的时间戳,将时间戳较新的非易失性数据读取至微控制单元。

84.可选的,在对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行一致性校验之前,本技术实施例提供的数据备份方法还可以包括:对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行有效性检验;确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据均为有效数据。

85.由于将第一随机存取存储器中的非易失性数据写入微控制单元的flash的过程中可能会导致存储数据失效,将第二随机存取存储器中的非易失性数据写入微控制单元外设的eeprom的过程中也可能会导致存储数据失效,所以,在对双重备份的数据进行一致性校验之前,可以分别对双重备份的数据进行有效性检验。

86.可选的,在一种可能的实现方式中,在确定第一随机存取存储器中的非易失性数据为有效数据,且第二随机存取存储器中的非易失性数据为无效数据的情况下,将第一随机存取存储器中的非易失性数据读取至微控制单元。

87.可选的,在另一种可能的实现方式中,在确定第二随机存取存储器中的非易失性数据为有效数据,且第一随机存取存储器中的非易失性数据为无效数据的情况下,将第二随机存取存储器中的非易失性数据读取至微控制单元。

88.可选的,在又一种可能的实现方式中,在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据均为无效数据的情况下,将预设数据读取至微控制单元。

89.其中,预设数据为人为事先根据需求确定的数据。

90.示例性的,车控ecu可以根据非易失性数据控制车辆的运行状态,不同数值的非易失性数据可以对应不同的车辆时速。在双重备份的非易失性数据均为无效数据的情况下,为了避免车辆迫停,可以使得车辆根据预设数据行驶。预设数据可能不是最佳行驶数据,比如,可以对应车辆的跛行模式,但是可以保证车辆依然处于行驶状态。

91.可选的,在接收到第一反馈信息的情况下,可以将第一随机存取存储器中的非易失性数据写入flash;第一反馈信息用于指示,非易失性数据写入flash完成;在接收到第二反馈信息的情况下,可以将第二随机存取存储器中的非易失性数据写入外设eeprom;第二反馈信息用于指示,非易失性数据写入外设eeprom完成。

92.综合以上描述,本技术实施例提供的数据备份方法中,在检测到有非易失性数据写入时,将非易失性数据同步写入两个随机存取存储器,然后分别将两个随机存取存储器中的非易失性数据写入两种不同的存储介质(flash和eeprom)。由于写入两种存储介质的非易失性数据同时失效或损坏的可能性较低,所以本技术技术方案通过两种存储介质对非易失性数据进行双重备份,可以提高对非易失性数据存储的可靠性。另外,由于现有的flash模拟eeprom的管理机制与外设eeprom的管理机制的存储对象的限制,写入过程要求差异较大,所以本技术中还对两种机制的写入过程进行了优化,在执行系统周期性任务的剩余时长内,实现flash模拟eeprom的管理机制的写入(对应本技术中的将第一随机存取存储器中的非易失性数据写入微控制单元的flash)。并且,通过预设周期性任务实现外设eeprom的管理机制的写入(对应本技术中的将第二随机存取存储器中的非易失性数据写入微控制单元外设的eeprom)。这样,能够减小两种机制写入过程的差异,从而更好的完成双重机制写入,以保证车控ecu的正常运行和上下电时间要求。

93.综合以上描述,如图3所示,本技术实施例还提供了一种数据备份方法,包括s301

‑

s306:

94.s301、在检测到有非易失性数据写入时,将非易失性数据同步写入微控制单元的第一随机存取存储器和第二随机存取存储器。

95.在步骤s301之后,执行步骤s302和步骤s304。

96.s302、在执行系统周期性任务的剩余时长内,将第一随机存取存储器中的非易失性数据写入微控制单元的flash。

97.s303、确定非易失性数据写入flash完成。

98.在步骤s303之后执行步骤s306。

99.s304、通过执行预设周期性任务将第二随机存取存储器中的非易失性数据写入微控制单元外设的eeprom。

100.s305、确定非易失性数据写入外设eeprom完成。

101.s306、确定非易失性数据双重备份完成。

102.可选的,如图4所示,本技术实施例还提供了一种数据备份方法,包括s401

‑

s4014:

103.s401、微控制单元启动运行,初始化flash和eeprom。

104.在步骤s401之后,执行步骤s402和步骤s405。

105.s402、将flash中的非易失性数据读取至第一随机存取存储器。

106.s403、确定非易失性数据读取至第一随机存取存储器完成。

107.s404、对第一随机存取存储器中的非易失性数据进行有效性校验。

108.在步骤s404之后,执行步骤s408。

109.s405、将eeprom中的非易失性数据读取至第二随机存取存储器。

110.s406、确定非易失性数据读取至第二随机存取存储器完成。

111.s407、对第二随机存取存储器中的非易失性数据进行有效性校验。

112.s408、判断第一随机存取存储器和第二随机存取存储器中的非易失性数据是否均为有效数据。

113.在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据均为有效数据的情况下,执行步骤s409;在确定第一随机存取存储器中的非易失

性数据和第二随机存取存储器中的非易失性数据中存在无效数据的情况下,执行步骤s4012。

114.s409、判断第一随机存取存储器和第二随机存取存储器中的非易失性数据是否一致。

115.在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据一致的情况下,执行步骤s4010;在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据不一致的情况下执行步骤s4011。

116.s4010、将第一随机存取存储器或第二随机存取存储器中的非易失性数据读取至微控制单元。

117.s4011、将时间戳较新的非易失性数据读取至微控制单元。

118.s4012、判断第一随机存取存储器和第二随机存取存储器中的非易失性数据是否均为无效数据。

119.在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据均为无效数据的情况下,执行步骤s4013;在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据中存在有效数据的情况下,执行步骤s4014。

120.s4013、将第一随机存取存储器和第二随机存取存储器中的非易失性数据置为预设数据,并将预设数据读取至微控制单元。

121.s4014、将第一随机存取存储器和第二随机存取存储器中的非易失性数据二者中的有效数据读取至微控制单元。

122.可以理解的是,在本技术实施例中涉及的eeprom为mcu外设的eeprom。

123.如图5所示,本技术实施例还提供了一种数据备份装置,比如,该数据备份装置可以是上述实施例中图1所涉及的数据备份系统中的nvm管理组件。该数据备份装置可以包括:检测模块11和写入模块12。

124.其中,检测模块11执行上述方法实施例中的s201,写入模块12执行上述方法实施例中的s202和s203。

125.具体地,检测模块11,用于检测是否有非易失性数据写入;

126.写入模块12,用于在检测模块11检测到有非易失性数据写入的情况下,将非易失性数据同步写入微控制单元的第一随机存取存储器和第二随机存取存储器;

127.写入模块12,还用于在执行系统周期性任务的剩余时长内,将第一随机存取存储器中的非易失性数据写入微控制单元的flash,并且通过执行预设周期性任务将第二随机存取存储器中的非易失性数据写入微控制单元外设的eeprom。

128.可选的,在一种可能的实现方式中,本技术提供的数据备份装置还可以包括:读取模块和校验模块;

129.读取模块用于,将flash中的非易失性数据读取至第一随机存取存储器,并将外设eeprom中的非易失性数据读取至第二随机存取存储器;

130.校验模块用于,对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行一致性校验;

131.读取模块还用于,在确定第一随机存取存储器中的非易失性数据和第二随机存取

存储器中的非易失性数据一致的情况下,将第一随机存取存储器中的非易失性数据或第二随机存取存储器中的非易失性数据读取至微控制单元。

132.可选的,在另一种可能的实现方式中,本技术提供的数据备份装置还可以包括:对比模块;

133.对比模块,用于在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据不一致的情况下,对比第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据的时间戳;

134.读取模块,还用于根据时间戳的先后顺序,将第一随机存取存储器中的非易失性数据或第二随机存取存储器中的非易失性数据读取至微控制单元。

135.可选的,在另一种可能的实现方式中,校验模块,还用于:

136.对第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据进行有效性检验;

137.确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据均为有效数据。

138.可选的,在另一种可能的实现方式中,

139.读取模块还用于,在确定第一随机存取存储器中的非易失性数据为有效数据,且第二随机存取存储器中的非易失性数据为无效数据的情况下,将第一随机存取存储器中的非易失性数据读取至微控制单元;

140.或者,读取模块还用于,在确定第二随机存取存储器中的非易失性数据为有效数据,且第一随机存取存储器中的非易失性数据为无效数据的情况下,将第二随机存取存储器中的非易失性数据读取至微控制单元。

141.可选的,在另一种可能的实现方式中,

142.读取模块还用于,在确定第一随机存取存储器中的非易失性数据和第二随机存取存储器中的非易失性数据均为无效数据的情况下,将预设数据读取至微控制单元。

143.可选的,在另一种可能的实现方式中,写入模块12具体用于:在接收到第一反馈信息的情况下,将第一随机存取存储器中的非易失性数据写入flash;第一反馈信息用于指示,非易失性数据写入flash完成;写入模块12还具体用于:在接收到第二反馈信息的情况下,将第二随机存取存储器中的非易失性数据写入外设eeprom;第二反馈信息用于指示,非易失性数据写入外设eeprom完成。

144.可选的,数据备份装置还可以包括存储模块,存储模块用于存储该数据备份装置的程序代码等。

145.如图6所示,本技术实施例还提供一种数据备份装置,包括存储器41、处理器42(42

‑

1和42

‑

2)、总线43和通信接口44;存储器41用于存储计算机执行指令,处理器42与存储器41通过总线43连接;当数据备份装置运行时,处理器42执行存储器41存储的计算机执行指令,以使数据备份装置执行如上述实施例提供的应用于mcu的数据备份方法。

146.在具体的实现中,作为一种实施例,处理器42可以包括一个或多个中央处理器(central processing unit,cpu),例如图6中所示的cpu0和cpu1。且作为一种实施例,数据备份装置可以包括多个处理器42,例如图6中所示的处理器42

‑

1和处理器42

‑

2。这些处理器42中的每一个cpu可以是一个单核处理器(single

‑

cpu),也可以是一个多核处理器(multi

‑

integrated circuit,asic)中。在本技术实施例中,计算机可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。

155.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何在本技术揭露的技术范围内的变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应该以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。