一种基于axi协议wrap访问的ddr控制器及处理方法

技术领域

1.本发明涉及信息技术领域,特别是涉及一种基于axi协议wrap访问的ddr控制器及处理方法。

背景技术:

2.目前,随着soc芯片设计的规模和集成度不断提高,ddr存储器广泛应用于各类芯片之中。而axi协议作为读写通道分离的一种协议,提升了芯片速度,对于ddr的控制访问具有独特的优势。其中,axi协议通过wrap的访问类型对ddr进行访问,区别于incr类型的访问地址只能是从低到高,wrap类型访问能从中间地址为起始地址,并以最快的速度让主机从中间地址开始拿到一段存于ddr数据。因此,以axi协议为基础的ddr控制器中,如何优化调度wrap类型的访问,并提高对ddr访问效率,对提升芯片速度,具有重大的现实意义和实用价值。

技术实现要素:

3.为了解决现有技术存在的不足,本发明的目的在于提供一种基于axi协议wrap访问的ddr控制器及处理方法,适用于axi访问不同的触发位宽,能够最快的从axi主机发送的起始地址开始,依次返回axi主机需要的数据。

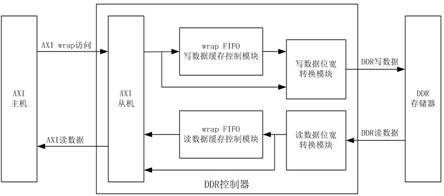

4.为实现上述目的,本发明提供的基于axi协议wrap访问的ddr控制器,包括,axi从机、写数据缓存控制模块、写数据位宽转换模块、读数据缓存控制模块,以及读数据位宽转换模块,其中,所述axi从机,接收axi主机发送的wrap访问,并将axi读数据返回给所述axi主机;所述写数据缓存控制模块,其对写命令和写数据进行缓存;所述读数据缓存控制模块,其对读命令和读数据进行缓存;所述写数据位宽转换模块,其接收写命令,并对接收的写数据进行位宽转换;所述读数据位宽转换模块,其接收读命令,对从ddr存储器返回的数据进行位宽转换。

5.进一步地,所述读数据缓存控制模块,对于写命令,当写数据的首地址与ddr存储器突发访问的地址不对齐时,存储第一笔数据;所述读数据缓存控制模块,对于读命令,当读数据的首地址与ddr存储器突发访问的地址不对齐时,存储第一笔数据。

6.更进一步地,所述写数据位宽转换模块,当写数据的首地址与ddr存储器突发访问的地址对齐时接收写数据,将写数据转换成ddr存储器的位宽并传输至ddr存储器;所述读数据位宽转换模块,当读数据的首地址与ddr存储器突发访问的地址对齐时,将从ddr存储器返回的数据转换成axi总线的位宽,并按axi访问的顺序,依次返回到所述axi主机。

7.为实现上述目的,本发明还提供一种基于axi协议wrap访问的ddr控制器处理方

法,包括以下步骤:axi从机对axi主机发送的wrap访问命令和写数据进行缓存;对于wrap访问的写命令,当写数据的首地址与ddr存储器突发访问的地址对齐时,将数据传输至写数据位宽转换模块,通过写数据位宽转换模块转换成ddr存储器的位宽并传输至ddr存储器;对于wrap访问的读命令,当读数据的首地址与ddr存储器突发访问的地址对齐时,将从ddr存储器返回的数据在读数据位宽转换模块中转换成axi总线的位宽,并按axi访问的顺序,依次返回给axi主机。

8.进一步地,所述axi从机对axi主机发送的wrap访问命令和写数据进行缓存的步骤,还包括,当axi总线以wrap类型访问ddr时,将该访问以ddr存储器一个突发访问的总字节长度为单位进行分片处理;若axi总线的起始地址与ddr存储器突发访问的长度对齐且axi访问的总字节数为ddr存储器突发访问长度的总字节数的整数倍,则以wrap访问的起始地址为ddr存储器访问首地址;依次增加ddr存储器突发访问长度的总字节数,对分片后的访问命令进行多次操作。

9.进一步地,所述对于wrap访问的写命令,当写数据的首地址与ddr存储器突发访问的地址对齐时,将数据传输至写数据位宽转换模块,通过写数据位宽转换模块转换成ddr存储器的位宽并传输至ddr存储器的步骤,还包括,若是写数据的首地址与ddr存储器突发访问的地址不对齐的情况下,将第一笔数据存入写数据缓存控制模块,从第二笔数据开始,先传输给ddr存储器,在检测到传输的最后一笔axi数据时,从写数据缓存控制模块中读出第一笔数据,并与最后一笔数据组合成一笔完整的ddr存储器突发访问数据,传输给ddr存储器。

10.进一步地,还包括,所述写数据缓存控制模块的空间为ddr存储器突发访问的数据量,若整个axi的wrap访问数据都不足ddr存储器一笔突发访问的数据量,则无需将数据存入fifo中,直接在写数据位宽转换模块中将数据转换成ddr存储器的位宽,传输给ddr存储器。

11.更进一步地,所述对于wrap访问的读命令,当读数据的首地址与ddr存储器突发访问的地址对齐时,将从ddr存储器返回的数据在读数据位宽转换模块中转换成axi总线的位宽,并按axi访问的顺序,依次返回给axi主机的步骤,还包括,若是读数据的首地址与ddr存储器突发访问的地址不对齐的情况下,将第一笔数据存入读数据缓存控制模块,从第二笔数据开始,先返回给axi主机,在检测到传输的最后一笔axi数据时,从读数据缓存控制模块中读出第一笔数据,并与最后一笔数据组合成一笔完整的ddr存储器突发访问数据,返回给axi主机;所述读数据缓存控制模块的空间为ddr存储器一次突发访问的数据量,若整个axi的wrap访问数据都不足ddr存储器一笔突发访问的数据量,则无需将数据存入fifo中,直接返回给axi主机。

12.为实现上述目的,本发明还提供一种电子设备,包括存储器和处理器,所述存储器上储存有在所述处理器上运行的计算机程序,所述处理器运行所述计算机程序时执行如上文所述的基于axi协议wrap访问的ddr控制器处理方法的步骤。

13.为实现上述目的,本发明还提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序运行时执行如上文所述的基于axi协议wrap访问的ddr控制器处理方法的步骤。

14.本发明的基于axi协议wrap访问的ddr控制器处理方法,具有以下有益效果:1)访问速度快,控制器能最快的从axi主机发送的起始地址开始,依次返回axi主机需要的数据;2)适用于axi访问不同的触发位宽,适应不同位宽的ddr存储器;3)消耗的存储资源少(只需一次ddr突发访问的存储空间);4)减少ddr的访问次数,若axi的wrap访问与ddr突发访问起始地址不对齐或访问长度不同的情况,则可减少ddr的访问次数,提高效率。

15.本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。

附图说明

16.附图用来提供对本发明的进一步理解,并且构成说明书的一部分,并与本发明的实施例一起,用于解释本发明,并不构成对本发明的限制。在附图中:图1为根据本发明的基于axi协议wrap访问的ddr控制器结构示意图;图2为根据本发明的基于axi协议wrap访问的ddr控制器处理方法流程图;图3为根据本发明的axi写地址与ddr突发访问地址对齐的情况示意图;图4为根据本发明的axi读地址与ddr突发访问地址对齐的情况示意图;图5为根据本发明的axi一笔写窄传输访问不足ddr一次突发访问时访问数据的情况示意图;图6为根据本发明的axi一笔写窄传输访问不足ddr一次突发访问时返回数据的情况示意图;图7为根据本发明的axi wrap类型窄传输对ddr写数据的情况示意图;图8为根据本发明的axi wrap类型窄传输对ddr读数据的情况示意图。

具体实施方式

17.以下结合附图对本发明的优选实施例进行说明,应当理解,此处所描述的优选实施例仅用于说明和解释本发明,并不用于限定本发明。

18.实施例1图1为根据本发明的基于axi协议wrap访问的ddr控制器结构示意图,如图1所示本发明的基于axi协议wrap访问的ddr控制器,包括axi从机、wrap fifo写数据缓存控制模块、写数据位宽转换模块、wrap fifo读数据缓存控制模块,以及读数据位宽转换模块,其中,axi从机接收axi主机发送的wrap访问,并向axi主机发送axi读数据。

19.wrap fifo写数据缓存控制模块对写命令和写数据进行缓存,对于写命令,若是写数据的首地址与ddr突发访问的地址不对齐的情况下,存储第一笔数据。

20.wrap fifo读数据缓存控制模块对读命令和读数据进行缓存,对于读命令,若是读数据的首地址与ddr突发访问的地址不对齐的情况下,存储第一笔数据。

21.写数据位宽转换模块,用于接收写命令,在写数据的首地址与ddr突发访问的地址对齐的情况下接收写数据,同时将写数据转换成ddr的位宽并传输至ddr存储器。

22.读数据位宽转换模块,用于接收读命令,在读数据的首地址与ddr突发访问的地址对齐的情况下,将从ddr存储器返回的数据转换成axi总线的位宽,并按axi访问的顺序,依次返回给axi主机。

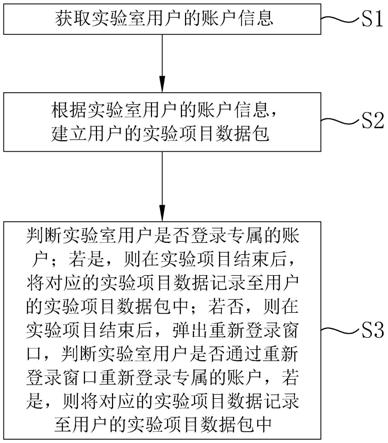

23.实施例2图2为根据本发明的基于axi协议wrap访问的ddr控制器处理方法流程图,下面将参考图2,对本发明的基于axi协议wrap访问的ddr控制器处理方法进行详细描述。

24.首先,在步骤201,axi主机发送一个wrap访问,在ddr控制器的axi从机中,先对命令和写数据做一个缓存。

25.在步骤202,若是写命令,在写数据的首地址与ddr突发访问的地址对齐的情况下,将数据传输至写数据位宽转换模块,同时转换成ddr的位宽并传输至ddr。

26.本发明实施例中,当axi总线以wrap类型访问ddr时,将该访问以ddr一个突发访问的总字节长度为单位进行分片处理。

27.本发明实施例中,若axi总线的起始地址可与ddr突发访问的长度对齐且axi访问的总字节数m为ddr突发访问长度的总字节数n的整数倍,则以wrap访问的起始地址为ddr访问首地址,依次增加n字节的方式,对分片后的访问命令共进行m/n次操作。

28.本发明实施例中,若访问的地址触及wrap访问地址的上边界,则下次访问以wrap访问的下边界作为起始地址。

29.本发明实施例中,如图3所示,若axi总线的位宽是8字节,ddr的位宽是2字节,ddr的突发访问长度是4,则axi一笔数据存于写数据位宽转换模块的寄存器中,分4次,每次发2字节,依次传输给ddr存储器。

30.本发明实施例中,若ddr位宽为1,突发访问长度是8,则1笔ddr访问传输的数据也是8字节,每次传1字节数据,分8次传完;若ddr位宽为1,突发访问长度是4,则分两次ddr访问,每次传输1字节数据,分4次传完。

31.本发明实施例中,若是写数据的首地址与ddr突发访问的地址不对齐的情况下,将第一笔数据存入wrap fifo写数据缓存控制模块(该fifo的空间为ddr存储器一次突发访问的数据量)。从第二笔数据开始,先传输给ddr存储器,在最后一笔axi数据到来的时候,从fifo中读出第一笔数据,并与最后一笔数据组合成一笔完整的ddr突发访问数据,传输给ddr存储器。该步骤中,若wrap访问的起始地址恰好位于一次ddr突发操作的中间,对于写操作,先将wrap起始地址至一次ddr突发操作边界的数据存入写wrap fifo中,以第二个ddr突发操作的下边界作为首地址,对ddr进行第一次写访问,依次以ddr突发操作的总长度为单位对ddr进行写访问,直至最后一次操作,将axi wrap访问的尾部数据与存入wrap fifo的数据进行重组为最后一次ddr突发写操作。

32.本发明实施例中,如图7所示,axi的访问1,存入fifo中,访问2和访问3组合为一笔完整的ddr突发访问,首先传输给ddr,在访问4到来时,将fifo的数据读出并与访问4的数据组合成第二笔完整的ddr突发访问,传输给ddr。

33.本发明实施例中,如图4所示,若整个axi的wrap访问数据都不足ddr一笔突发访问的数据量,则无需将数据存入fifo中,直接在写数据位宽转换模块中将数据转换成ddr的位

宽,传输给ddr。

34.在步骤203,若是读命令,在读数据的首地址与ddr突发访问的地址对齐的情况下,将从ddr返回的数据在读数据位宽转换模块中,转换成axi总线的位宽,并按axi访问的顺序,依次返回给axi主机。

35.本发明实施例中,如图4所示,若axi总线的位宽是8字节,ddr的位宽是2字节,ddr的突发访问长度是4,则进行1次ddr的突发访问会返回4组2字节的数据,在读数据位宽转换模块中将这4组2字节的数据,组合成1个8字节的数据,返回给axi主机。

36.本发明实施例中,若是读数据的首地址与ddr突发访问的地址不对齐的情况下,将第一笔数据存入wrap fifo读数据缓存控制模块(该fifo的空间为ddr存储器一次突发访问的数据量)。从第二笔数据开始,先返回给axi主机,在最后一笔axi数据到来的时候,从wrap fifo读数据缓存控制模块中读出之前写入的数据,并与最后一笔数据组合成一笔完整的ddr突发访问数据,返回给axi主机。

37.本发明实施例中,若wrap访问的起始地址恰好位于一次ddr突发操作的中间,对于读操作,以wrap起始地址对应的ddr突发访问的下边界作为起始地址,将本应处于wrap访问尾部的数据存入读wrap fifo中,将wrap起始地址的数据依次返回axi读通道中,依次以ddr突发操作的总长度为单位对ddr进行写访问,直至最后一次操作完成,再将存于读wrap fifo中的数据读出,返回给axi读通道。

38.本发明实施例中,如图7所示,axi从地址4开始访问,访问大小为4字节,访问长度为4,ddr的位宽是1字节,突发长度是8(或ddr的位宽是2字节,突发长度是4也是一样的),则一次ddr的读访问会返回地址0~7的8字节数据,将地址0~3的数据存入fifo,将地址4~7的数据作为第一笔数据返回给axi主机。ddr的第二次访问返回地址8~15的8字节数据,则地址8~11的数据作为第二笔,地址12~15的数据作为第三笔数据,依次返回给axi主机,最后将fifo的数据读出,作为最后一笔数据返回给axi主机。

39.本发明实施例中,若整个axi的wrap访问数据都不足ddr一笔突发访问的数据量,则无需将数据存入fifo中,直接返回给axi主机。如图6所示,axi的访问地址为6,访问大小为1字节,访问长度是4,依次ddr突发访问为8字节,则从ddr存储器返回的数据,依次以地址6、7、4、5的顺序返回给axi主机,将地址0~3的数据丢弃。

40.本发明的一个实施例中,还提供一种电子设备,包括存储器和处理器,所述存储器上储存有在所述处理器上运行的计算机程序,所述处理器运行所述计算机程序时执行如上文所述的基于axi协议wrap访问的ddr控制器处理方法的步骤。

41.本发明的一个实施例中,还提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序运行时执行如上文所述的基于axi协议wrap访问的ddr控制器处理方法的步骤。

42.本领域普通技术人员可以理解:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。