技术特征:

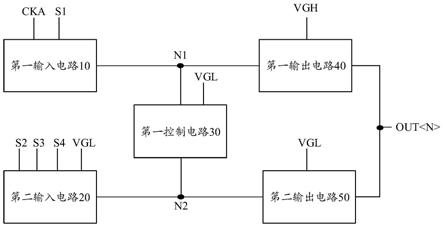

1.一种移位寄存器,其特征在于,所述移位寄存器包括:第一输入电路,与第一信号端、第一时钟信号端及第一节点电连接;所述第一输入电路被配置为,在所述第一时钟信号端传输的第一时钟信号的控制下,将在所述第一信号端处接收的第一信号传输至所述第一节点;第二输入电路,与第二信号端、第三信号端、第二电压信号端、第四信号端及第二节点电连接;所述第二输入电路被配置为,在所述第二信号端所传输的第二信号的控制下,将在所述第三信号端处接收的第三信号传输至所述第二节点,在所述第四信号端的控制下,将在所述第二电压信号端处接收的第二电压信号传输至所述第二节点;所述第二信号端和所述第三信号端均包括第一电压信号端和所述第一时钟信号端中的一者;第一控制电路,与所述第一节点、所述第二节点及所述第二电压信号端电连接;所述第一控制电路被配置为,在所述第二节点的电压的控制下,将所述第二电压信号传输至所述第一节点;第一输出电路,与所述第一节点、所述第一电压信号端及输出信号端电连接;所述第一输出电路被配置为,在所述第一节点的电压的控制下,将所述第一电压信号传输至所述输出信号端;以及,第二输出电路,至少与所述第二节点、所述第二电压信号端及所述输出信号端电连接;所述第二输出电路被配置为,在所述第二节点的电压的控制下,将所述第二电压信号传输至所述输出信号端。2.根据权利要求1所述的移位寄存器,其特征在于,所述第一输入电路包括:第一晶体管;所述第一晶体管的栅极与所述第一时钟信号端电连接,所述第一晶体管的第一极与所述第一信号端电连接,所述第一晶体管的第二极与所述第一节点电连接。3.根据权利要求1所述的移位寄存器,其特征在于,所述第二输入电路包括:第二晶体管和第三晶体管;所述第二晶体管的栅极与所述第二信号端电连接,所述第二晶体管的第一极与所述第三信号端电连接,所述第二晶体管的第二极与所述第二节点电连接;所述第三晶体管的栅极与所述第四信号端电连接,所述第三晶体管的第一极与所述第二电压信号端电连接,所述第三晶体管的第二极与所述第二节点电连接。4.根据权利要求3所述的移位寄存器,其特征在于,所述第二输入电路还包括:第四晶体管和第五晶体管;所述第四晶体管的栅极与所述第三节点电连接,所述第四晶体管的第一极与所述第三信号端电连接,所述第四晶体管的第二极与第二节点电连接;所述第二晶体管的第二极还与所述第三节点电连接,并通过所述第四晶体管与所述第二节点电连接;所述第五晶体管的栅极与所述第四信号端电连接,所述第五晶体管的第一极与所述第二电压信号端电连接,所述第五晶体管的第二极与所述第三节点电连接。5.根据权利要求1~4中任一项所述的移位寄存器,其特征在于,所述第一信号端为第一电压信号端,所述第四信号端为第一级联信号端;或,

所述第一信号端为所述第一级联信号端,所述第四信号端为所述第一节点。6.根据权利要求5所述的移位寄存器,其特征在于,所述移位寄存器还包括第二控制电路;所述第二控制电路与所述第一级联信号端、第三电压信号端、第四电压信号端、第二级联信号端及第四节点电连接;所述第二控制电路被配置为,在所述第三电压信号端所传输的第三电压信号的控制下,将所述第一级联信号端所传输的第一级联信号传输至所述第四节点,或,在所述第四电压信号端所传输的第四电压信号的控制下,将所述第二级联信号端所传输的第二级联信号传输至所述第四节点;其中,所述第三电压信号和所述第四电压信号互为反相信号;在所述第一信号端为第一级联信号端、所述第四信号端为所述第一节点的情况下,所述第一输入电路还与所述第四节点电连接,并通过所述第二控制电路与所述第一级联信号端电连接;在所述第一信号端为所述第一电压信号端、所述第四信号端为第一级联信号端的情况下,所述第二输入电路还与所述第四节点电连接,并通过所述第二控制电路与所述第一级联信号端电连接。7.根据权利要求6所述的移位寄存器,其特征在于,所述第二控制电路包括:第六晶体管和第七晶体管;所述第六晶体管的栅极与第三电压信号端电连接,所述第六晶体管的第一极与所述第一级联信号端电连接,所述第六晶体管的第二极与所述第四节点电连接;所述第七晶体管的栅极与第四电压信号端电连接,所述第七晶体管的第一极与所述第二级联信号端电连接,所述第七晶体管的第二极与所述第四节点电连接;在所述第一信号端为第一级联信号端、所述第四信号端为所述第一节点、且所述第一输入电路包括第一晶体管的情况下,所述第一晶体管的第一极还与所述第四节点电连接,并通过所述第六晶体管与所述第一级联信号端电连接;在所述第一信号端为第一电压信号端,所述第四信号端为所述第一级联信号端、且所述第二输入电路包括第三晶体管的情况下,所述第三晶体管的栅极还与所述第四节点电连接,并通过所述第六晶体管与所述第一级联信号端电连接。8.根据权利要求1所述的移位寄存器,其特征在于,所述第一控制电路包括:第八晶体管;所述第八晶体管的栅极与所述第二节点电连接,所述第八晶体管的第一极与所述第二电压信号端电连接,所述第八晶体管的第二极与所述第一节点电连接;所述第一输出电路包括:第九晶体管和第一电容器;所述第九晶体管的栅极与所述第一节点电连接,所述第九晶体管的第一极与所述第一电压信号端电连接,所述第九晶体管的第二极与所述输出信号端电连接;所述第一电容器的第一极与所述第一节点电连接,所述第一电容器的第二极与所述输出信号端电连接;所述第二输出电路包括:第十晶体管和第二电容器;

所述第十晶体管的栅极与所述第二节点电连接,所述第十晶体管的第一极与所述第二电压信号端电连接,所述第十晶体管的第二极与所述输出信号端电连接;所述第二电容器的第一极与所述第二节点电连接,所述第二电容器的第二极与所述第二电压信号端电连接;在所述第二输出电路还与第二时钟信号端电连接的情况下,所述第二电容器的第二极与所述第二电压信号端或所述第二时钟信号端电连接。9.根据权利要求5所述的移位寄存器,其特征在于,在所述第一信号端为第一电压信号端,所述第四信号端为第一级联信号端的情况下,所述移位寄存器还包括:第三控制电路;所述第三控制电路与第五节点、第二时钟信号端及所述第一节点电连接;所述第三控制电路被配置为,在所述第五节点的电压及所述第二时钟信号端所传输的第二时钟信号的控制下,将所述第二时钟信号传输至所述第一节点;其中,所述第一输入电路还与所述第五节点电连接,并通过所述第三控制电路与所述第一节点电连接;所述第一输入电路被配置为,在所述第一时钟信号的控制下,将所述第一信号传输至所述第五节点。10.根据权利要求9所述的移位寄存器,其特征在于,所述第三控制电路包括:第十一晶体管、第十二晶体管和第三电容器;所述第十一晶体管的栅极与所述第五节点电连接,所述第十一晶体管的第一极与所述第二时钟信号端电连接,所述第十一晶体管的第二极与第六节点电连接;所述第十二晶体管的栅极与所述第二时钟信号端电连接,所述第十二晶体管的第一极与所述第六节点电连接,所述第十二晶体管的第二极与所述第一节点电连接;所述第三电容器的第一极与所述第五节点电连接,所述第三电容器的第二极与所述第六节点电连接;在所述第一输入电路包括第一晶体管的情况下,所述第一晶体管的第二极与所述第五节点电连接,并依次通过所述第十一晶体管和所述第十二晶体管与所述第一节点电连接。11.根据权利要求9所述的移位寄存器,其特征在于,所述移位寄存器还包括:第四控制电路;所述第四控制电路与所述第五节点、所述第二电压信号端、所述第二时钟信号端及所述第二节点电连接;所述第四控制电路被配置为,在所述第五节点的电压和所述第二时钟信号的控制下,将所述第二电压信号传输至所述第二节点。12.根据权利要求11所述的移位寄存器,其特征在于,所述第四控制电路包括:第十三晶体管和第十四晶体管;所述第十三晶体管的栅极与所述第五节点电连接,所述第十三晶体管的第一极与所述第二电压信号端电连接,所述第十三晶体管的第二极与所述第十四晶体管的第一极电连接;所述第十四晶体管的栅极与所述第二时钟信号端电连接,所述第十四晶体管的第二极与所述第二节点电连接。13.根据权利要求9所述的移位寄存器,其特征在于,所述移位寄存器还包括:第五控制电路;所述第五控制电路与所述第二电压信号端和所述第一时钟信号端中的一者、所述第二

节点及所述第五节点电连接;所述第五控制电路被配置为,在所述第二节点的电压的控制下,将所述第二电压信号或所述第一时钟信号传输至所述第五节点。14.根据权利要求13所述的移位寄存器,其特征在于,所述第五控制电路包括:第十五晶体管;所述第十五晶体管的栅极与所述第二节点电连接,所述第十五晶体管的第一极与所述第二电压信号端和所述第一时钟信号端中的一者电连接,所述第十五晶体管的第二极与所述第五节点电连接。15.根据权利要求9所述的移位寄存器,其特征在于,所述移位寄存器还包括:第一开关电路;所述第一开关电路与所述第二节点、第七节点及所述第一时钟信号端电连接;所述第一开关电路被配置为,在所述第一时钟信号的控制下,将来自所述第七节点的信号传输至所述第二节点;所述第二输入电路还与所述第七节点电连接,并通过所述第一开关电路与所述第二节点电连接。16.根据权利要求15所述的移位寄存器,其特征在于,所述第一开关电路包括:第十六晶体管;所述第十六晶体管的栅极与所述第一时钟信号端电连接,所述第十六晶体管的第一极与所述第七节点电连接,所述第十六晶体管的第二极与所述第二节点电连接;在所述第二输入电路包括所述第二晶体管和所述第三晶体管的情况下,所述第二晶体管的第二极与所述第七节点电连接,并通过所述第十六晶体管与所述第二节点电连接,所述第三晶体管的第二极与所述第七节点电连接,并通过所述第十六晶体管与所述第二节点电连接。17.根据权利要求1所述的移位寄存器,其特征在于,所述移位寄存器还包括:第三输入电路和第六控制电路;所述第三输入电路与所述第三信号端、所述第二电压信号端、所述第五电压信号端、所述第四信号端及第八节点电连接;所述第三输入电路被配置为,在所述第五电压信号端所传输的第五电压信号的控制下,将所述第三信号传输至所述第八节点,或,在所述第二信号的控制下,将所述第二电压信号传输至所述第八节点;所述第三信号端包括所述第一电压信号端、所述第一时钟信号端和所述第五电压信号端中的一者;所述第六控制电路与所述第八节点、所述第一节点及所述第二电压信号端电连接;所述第六控制电路被配置为,在所述第八节点的电压的控制下,将所述第二电压信号传输至所述第一节点;所述第二输出电路还与所述第八节点电连接;所述第二输出电路还被配置为,在所述第八节点的电压的控制下,将所述第二电压信号传输至所述输出信号端;其中,所述第二信号端还包括第六电压信号端;在所述第二信号端为所述第六电压信号端的情况下,所述第二输入电路还被配置为,在所述第六电压信号端传输的第六电压信号的控制下,将所述第三信号传输至所述第八节点;所述第五电压信号和所述第六电压信号互为反相信号。

18.根据权利要求17所述的移位寄存器,其特征在于,所述第三输入电路包括:第十七晶体管和第十八晶体管;所述第十七晶体管的栅极与所述第五电压信号端电连接,所述第十七晶体管的第一极与所述第三信号端电连接,所述第十七晶体管的第二极与所述第八节点电连接;所述第十八晶体管的栅极与所述第四信号端电连接,所述第十八晶体管的第一极与所述第二电压信号端电连接,所述第十八晶体管的第二极与所述第八节点电连接;所述第六控制电路包括:第十九晶体管;所述第十九晶体管的栅极与所述第八节点电连接,所述第十九晶体管的第一极与所述第二电压信号端电连接,所述第十九晶体管的第二极与所述第一节点电连接;所述第二输出电路还包括:第二十晶体管;所述第二十晶体管的栅极与所述第八节点电连接,所述第二十晶体管的第一极与所述第二电压信号端电连接,所述第二十晶体管的第二极与所述输出信号端电连接。19.根据权利要求18所述的移位寄存器,其特征在于,所述第三输入电路还包括:第二十一晶体管和第二十二晶体管;所述第二十一晶体管的栅极与第九节点电连接,所述第二十一晶体管的第一极与所述第三信号端电连接,所述第二十一晶体管的第二极与所述第八节点电连接;所述第二十二晶体管的栅极与所述第四信号端电连接,所述第二十二晶体管的第一极与所述第二电压信号端电连接,所述第二十二晶体管的第二极与所述第九节点电连接;其中,所述第十七晶体管的第二极还与所述第九节点电连接,通过所述第二十一晶体管与所述第八节点电连接。20.根据权利要求17所述的移位寄存器,其特征在于,所述移位寄存器还包括第七控制电路、第八控制电路和第二开关电路中的至少一者;所述第七控制电路与所述第五节点、所述第二电压信号端、第二时钟信号端及所述第八节点电连接;所述第七控制电路被配置为,在所述第五节点的电压和所述第二时钟信号端所传输的第二时钟信号的控制下,将所述第二电压信号传输至所述第八节点;所述第八控制电路与所述第八节点、所述第五节点及所述第二电压信号端电连接;所述第八控制电路被配置为,在所述第八节点的电压的控制下,将所述第二电压信号传输至所述第五节点;所述第二开关电路与所述第一时钟信号端、第十节点及所述第八节点电连接;所述第二开关电路被配置为,在所述第一时钟信的控制下,将所述第十节点的信号传输至所述第八节点;所述第三输入电路还与所述第十节点电连接,并通过所述第二开关电路与所述第八节点电连接。21.根据权利要求20所述的移位寄存器,其特征在于,所述第七控制电路包括:第二十三晶体管和第二十四晶体管;所述第二十三晶体管的栅极与所述第五节点电连接,所述第二十三晶体管的第一极与所述第二电压信号端电连接,所述第二十三晶体管的第二极与所述第二十四晶体管的第一极电连接;所述第二十四晶体管的栅极与所述第二时钟信号端电连接,所述第二十四晶体管的第

二极与所述第八节点电连接;所述第八控制电路包括:第二十五晶体管;所述第二十五晶体管的栅极与所述第八节点电连接,所述第二十五晶体管的第一极与所述第二电压信号端电连接,所述第二十五晶体管的第二极与所述第五节点电连接;所述第二开关电路包括:第二十七晶体管;所述第二十七晶体管的栅极与所述第一时钟信号端电连接,所述第二十七晶体管的第一极与所述第十节点电连接,所述第二十七晶体管的第二极与所述第八节点电连接;在所述第三输入电路包括所述第十七晶体管和所述第十八晶体管的情况下,所述第十七晶体管的第二极与所述第十节点电连接,并通过所述第二十七晶体管与所述第八节点电连接,所述第十八晶体管的第二极与所述第十节点电连接,并通过所述第二十七晶体管与所述第八节点电连接。22.根据权利要求8~17中任一项所述的移位寄存器,其特征在于,所述移位寄存器还包括:第一防漏电电路;所述第一防漏电电路与所述第一节点和所述输出信号端中的一者、所述第一电压信号端及第一防漏电节点电连接;所述第一防漏电电路被配置为,在所述第一节点的电压或所述输出信号端传输的输出信号的控制下,将所述第一电压信号传输至所述第一防漏电节点;其中,所述第一控制电路还与所述第一防漏电节点电连接;所述第二输出电路还与所述第一防漏电节点电连接;在所述移位寄存器还包括所述第六控制电路的情况下,所述第六控制电路还与所述第一防漏电节点电连接。23.根据权利要求22所述的移位寄存器,其特征在于,所述第一防漏电电路包括:第二十六晶体管;所述第二十六晶体管的栅极与所述第一节点和所述输出信号端中的一者电连接,所述第二十六晶体管的第一极与所述第一电压信号端电连接,所述第二十六晶体管的第二极与所述第一防漏电节点电连接;所述第八晶体管包括:第一子晶体管和第二子晶体管;所述第一子晶体管的栅极与所述第二节点电连接,所述第一子晶体管的第一极与所述第二电压信号端电连接,所述第一子晶体管的第二极与所述第一防漏电节点电连接;所述第二子晶体管的栅极与所述第二节点电连接,所述第二子晶体管的第一极与所述第一防漏电节点电连接,所述第二子晶体管的第二极与所述第一节点电连接;所述第十晶体管包括:第三子晶体管和第四子晶体管;所述第三子晶体管的栅极与所述第二节点电连接,所述第三子晶体管的第一极与所述第二电压信号端电连接,所述第三子晶体管的第二极与所述第一防漏电节点电连接;所述第四子晶体管的栅极与所述第二节点电连接,所述第四子晶体管的第一极与所述第一防漏电节点电连接,所述第四子晶体管的第二极与所述输出信号端电连接;在所述第六控制电路包括所述第十九晶体管的情况下,所述第十九晶体管包括:第五子晶体管和第六子晶体管;所述第五子晶体管的栅极与所述第八节点电连接,所述第五子晶体管的第一极与所述

第二电压信号端电连接,所述第五子晶体管的第二极与所述第一防漏电节点电连接;所述第六子晶体管的栅极与所述第八节点电连接,所述第六子晶体管的第一极与所述第一防漏电节点电连接,所述第六子晶体管的第二极与所述第一节点电连接;在所述第二输出电路还包括第二十晶体管的情况下,所述第二十晶体管包括:第七子晶体管和第八子晶体管;所述第七子晶体管的栅极与所述第八节点电连接,所述第七子晶体管的第一极与所述第二电压信号端电连接,所述第七子晶体管的第二极与所述第一防漏电节点电连接;所述第八子晶体管的栅极与所述第八节点电连接,所述第八子晶体管的第一极与所述第一防漏电节点电连接,所述第八子晶体管的第二极与所述输出信号端电连接。24.根据权利要求23所述的移位寄存器,其特征在于,在所述移位寄存器还包括所述第三控制电路的情况下,所述第三控制电路还与所述第一防漏电节点电连接。25.根据权利要求23所述的移位寄存器,其特征在于,在所述第三控制电路包括第十一晶体管和第十二晶体管的情况下,所述第十一晶体管包括:第九子晶体管和第十子晶体管;和/或,所述第十二晶体管包括:第十一子晶体管和第十二子晶体管;所述第九子晶体管的栅极与所述第五节点电连接,所述第九子晶体管的第一极与所述所述第二时钟信号端电连接,所述第九子晶体管的第二极与所述第一防漏电节点电连接;所述第十子晶体管的栅极与所述第五节点电连接,所述第十子晶体管的第一极与所述第一防漏电节点电连接,所述第十子晶体管的第二极与所述第六节点电连接;所述第十一子晶体管的栅极与所述第二时钟信号端电连接,所述第十一子晶体管的第一极与所述第六节点电连接,所述第十一子晶体管的第二极与所述第一防漏电节点电连接;所述第十二子晶体管的栅极与所述第二时钟信号端电连接,所述第十二子晶体管的第一极与所述第一防漏电节点电连接,所述第十二子晶体管的第二极与所述第一节点电连接。26.根据权利要求23所述的移位寄存器,其特征在于,在所述移位寄存器还包括所述第五控制电路的情况下,所述第五控制电路还与所述第一防漏电节点电连接;在所述移位寄存器还包括所述第八控制电路的情况下,所述第八控制电路还与所述第一防漏电节点电连接;或,所述移位寄存器还包括:第二防漏电电路;所述第二防漏电电路与所述第五节点、所述第一电压信号端、第二防漏电节点电连接;所述第二防漏电电路被配置为,在所述第五节点的电压的控制下,将所述第一电压信号传输至所述第二防漏电节点;所述第五控制电路还与所述第二防漏电节点电连接;所述第八控制电路还与所述第二防漏电节点电连接。27.根据权利要求26所述的移位寄存器,其特征在于,在所述第五控制电路还与所述第一防漏电节点电连接的情况下,所述第十五晶体管包括:第十三子晶体管和第十四子晶体

管;在所述第八控制电路还与所述第一防漏电节点电连接的情况下,所述第二十五晶体管包括:第十五子晶体管和第十六子晶体管;所述第十三子晶体管的栅极与所述第二节点电连接,所述第十三子晶体管的第一极与所述第二电压信号端电连接,所述第十三子晶体管的第二极与所述第一防漏电节点电连接;所述第十四子晶体管的栅极与所述第二节点电连接,所述第十四子晶体管的第一极与所述第一防漏电节点电连接,所述第十四子晶体管的第二极与所述第五节点电连接;所述第十五子晶体管的栅极与所述第八节点电连接,所述第十五子晶体管的第一极与所述第二电压信号端电连接,所述第十五子晶体管的第二极与所述第一防漏电节点电连接;所述第十六子晶体管的栅极与所述第八节点电连接,所述第十六子晶体管的第一极与所述第一防漏电节点电连接,所述第十六子晶体管的第二极与所述第五节点电连接;在所述第五控制电路还与所述第二防漏电节点电连接的情况下,所述第十五晶体管包括:第十七子晶体管和第十八子晶体管;在所述第八控制电路还与所述第二防漏电节点电连接的情况下,所述第二十五晶体管包括:第十九子晶体管和第二十子晶体管;所述第十七子晶体管的栅极与所述第二节点电连接,所述第十七子晶体管的第一极与所述第二电压信号端电连接,所述第十七子晶体管的第二极与所述第二防漏电节点电连接;所述第十八子晶体管的栅极与所述第二节点电连接,所述第十八子晶体管的第一极与所述第二防漏电节点电连接,所述第十八子晶体管的第二极与所述第五节点电连接;所述第十九子晶体管的栅极与所述第八节点电连接,所述第十九子晶体管的第一极与所述第二电压信号端电连接,所述第十九子晶体管的第二极与所述第二防漏电节点电连接;所述第二十子晶体管的栅极与所述第八节点电连接,所述第二十子晶体管的第一极与所述第二防漏电节点电连接,所述第二十子晶体管的第二极与所述第五节点电连接。28.一种扫描驱动电路,其特征在于,所述扫描驱动电路包括:多个如权利要求1~27中任一项所述的移位寄存器。29.一种显示装置,其特征在于,所述显示装置包括:如权利要求28所述的扫描驱动电路及多个像素驱动电路;其中,所述像素驱动电路包括:开关晶体管、感测晶体管、驱动晶体管、控制晶体管及存储电容器;所述扫描驱动电路中的移位寄存器与所述控制晶体管的栅极电连接,以提供使能信号。

技术总结

本公开实施例公开了一种移位寄存器、扫描驱动电路及显示装置,涉及显示技术领域,用于避免显示画面出现闪烁现象。移位寄存器包括:第一输入电路、第二输入电路、第一控制电路、第一输出电路和第二输出电路。第一输入电路与第一信号端、第一时钟信号端及第一节点电连接。第二输入电路与第二信号端、第三信号端、第二电压信号端、第四信号端及第二节点电连接。第一输出电路与第一节点、第一电压信号端及输出信号端电连接。第二输出电路至少与第二节点、第二电压信号端及输出信号端电连接。移位寄存器的输出信号端与像素驱动电路的控制晶体管的栅极电连接,以提供使能信号。本公开实施例提供的移位寄存器、扫描驱动电路及显示装置用于图像显示。于图像显示。于图像显示。

技术研发人员:冯雪欢 姚星 许静波 张大成

受保护的技术使用者:京东方科技集团股份有限公司

技术研发日:2021.09.27

技术公布日:2021/12/13

再多了解一些

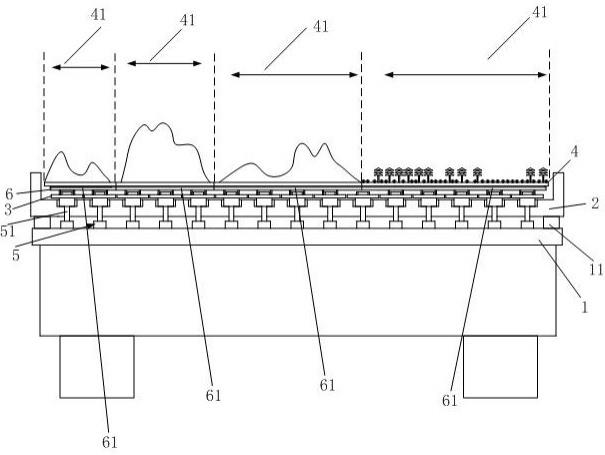

本文用于企业家、创业者技术爱好者查询,结果仅供参考。