一种适用于soc fpga的片内总线系统安全传输装置

技术领域

1.本发明涉及一种适用于soc fpga的片内总线系统安全传输装置,属于总线的安全传输技术领域。

背景技术:

2.soc fpga基于cpu fpga架构提出,致力于将处理器的软件可编程性和fpga的硬件可编程性完美整合,具体实现包括处理器系统部分和可编程逻辑部分,其中处理器系统部分是以处理器为基础的硬核资源,一般包括处理器、高带宽的总线互联单元和配套的外设接口模块,主要完成高层次管理功能,可编程逻辑部分即通常的fpga,包含可配置逻辑块、存储资源、数字信号处理模块、高速io接口等。处理器系统部分和可编程逻辑部分的交互通过总线接口实现,需要在可编程逻辑部分例化总线互联组件,片内总线系统是处理器系统部分和可编程逻辑部分的必然选择。soc fpga作为可扩展处理平台或嵌入式计算平台被广泛推广使用。

3.soc fpga的处理器系统部分作为一个开放性的可配置硬核资源,总线架构处于完全公开的透明状态;可编程逻辑部分配套有完备的传输监控和信号采集装置,总线系统结构和数据流处于完全可监控状态;处理器系统部分和可编程逻辑部分交互通过固定的总线接口完成,容易被第三方侦听。如何根据用户需要引入对模块互联和数据流的保护、保证soc fpga片内总线系统传输安全性是soc fpga产品化和特殊领域应用的重大问题。

技术实现要素:

4.本发明要解决的技术问题是:如何提供一种保证传输通路安全性的总线互联系统。

5.为了解决上述技术问题,本发明提出的技术方案是:一种适用于soc fpga的片内总线系统安全传输装置,包括主机端moi和从机端soi;所述主机端moi包括第一认证与密钥控制单元、写数据加密单元、读数据解密单元、第一写数据同步缓存单元和第一读数据同步缓存单元;所述第一认证与密钥控制单元,用于完成认证和密钥信息配置、fpga uid信息的确认、认证信息的发送和数据加解密信息的协商;所述从机端soi包括第二认证与密钥控制单元、写数据解密单元、读数据解密单元、第二写数据同步缓存单元和第二读数据同步缓存单元;所述第二认证与密钥控制单元,用于认证和密钥信息配置、fpga uid信息的确认、认证信息的确认、访问白名单的建立、传输异常报告、数据加解密信息的协商;第一写数据同步缓存单元和第二写数据同步缓存单元均用于缓存所述总线系统内写通路的数据;第一读数据同步缓存单元和第二读数据同步缓存单元均用于缓存所述总线系统内读通路的数据。

6.上述方案的进一步改进是:所述主机端moi为所述总线系统中主机端的一部分,嵌入所述主机端内部;所述从机端soi为所述总线系统中从机端的一部分,嵌入所述从机端内部。

7.上述方案的进一步改进是:所述主机端moi以桥接方式嵌入所述总线系统中主机端与所述总线系统的总线控制器之间;所述从机端soi以桥接方式嵌入所述总线系统中从机端与所述总线控制器之间。

8.上述方案的进一步改进是:所述主机端moi和从机端moi为所述总线系统的总线控制器的一部分,嵌入所述总线控制器内部。

9.本发明的有益效果是:本发明在最大限度上适配传统系统架构,并实现了具有安全性的传输通路的总线互联系统。

附图说明

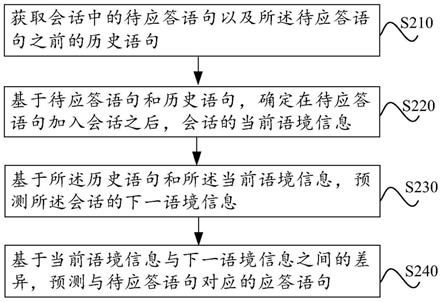

10.图1是本发明实施例一的一种适用于soc fpga的片内总线系统安全传输装置示意图。

11.图2是本发明实施例一的一种适用于soc fpga的片内总线系统安全传输装置与总线控制器之间的三种嵌入方式示意图。

12.图3是本发明实施例一的一种适用于soc fpga的片内总线系统安全传输装置的身份认证流程示意图。

13.图4是本发明实施例一的一种适用于soc fpga的片内总线系统安全传输装置的数据通路密钥协商流程示意图。

具体实施方式

14.实施例一如图1所示,一种适用于soc fpga的片内总线系统安全传输装置,包括主机端moi和从机端soi;主机端moi包括第一认证与密钥控制单元、写数据加密单元、读数据解密单元、第一写数据同步缓存单元和第一读数据同步缓存单元;第一认证与密钥控制单元,用于完成认证和密钥信息配置、fpga uid信息的确认、认证信息的发送和数据加解密信息的协商;从机端soi包括第二认证与密钥控制单元、写数据解密单元、读数据解密单元、第二写数据同步缓存单元和第二读数据同步缓存单元;第二认证与密钥控制单元,用于认证和密钥信息配置、fpga uid信息的确认、认证信息的确认、访问白名单的建立、传输异常报告、数据加解密信息的协商;第一写数据同步缓存单元和第二写数据同步缓存单元均用于缓存总线系统内写通路的数据;第一写数据同步缓存单元放置于写数据加密模块前则缓存未加密的写数据,放置于写数据加密模块后则缓存加密后的写数据;第二数据缓存单元放置于写数据解密模块前则缓存未解密的写数据,放置于写数据解密模块后则缓存解密后的写数据;第一读数据同步缓存单元和第二读数据同步缓存单元均用于缓存总线系统内读通路的数据。第一读数据同步缓存单元放置于读解密模块前则缓存未解密的读数据,放置

于读解密模块后则缓存解密后的读数据;第二读数据同步缓存单元放置于读加密模块前则缓存未加密的读数据,放置于读加密模块后则缓存加密后的读数据;其中,写数据加密单元根据协商的加密密钥完成写数据加密;读数据解密单元根据协商的解密密钥完成读数据解密;写数据解密单元根据协商的解密密钥完成写数据解密;读数据加密单元根据协商的加密密钥完成读数据加密。

15.如图2 a)所示,嵌入主从机内部的情况,主机端moi为总线系统中主机端的一部分,嵌入主机端内部;从机端soi为总线系统中从机端的一部分,嵌入从机端内部。

16.如图2b)所示,以桥接方式接入总线系统的情况,主机端moi以桥接方式接入总线系统中主机端与总线系统的总线控制器之间;从机端soi以桥接方式接入总线系统中从机端与总线控制器之间。

17.如图2c)所示,主机端moi和从机端moi为总线系统的总线控制器的一部分,嵌入总线控制器内部。

18.如图3所示,本实施例的主从机身份认证使用的验证方法包括但不限于非对称密码算法,从机端 soi内有配置完成的认证信息列表,主机端moi向从机端soi发起认证请求,从机端soi收到请求后生成公钥信息,并将生成的公钥信息反馈给主机端moi, 主机端moi使用收到的公钥信息加密自身的身份识别信息(身份识别信息包含fpga的uid和认证信息)并传送给从机端soi,从机端soi利用私钥进行身份信息解密,解密后与内部存储的认证信息列表进行一致性匹配,匹配完成后将主机端moi更新进传输白名单,并向主机端moi反馈识别成功,匹配失败后向主机端moi反馈识别失败。

19.如图4所示,对数据通路的加密保护使用对称密码算法进行,对称密码算法不改变传输的数据量,主机端moi发送数据传输部分使用的公钥给从机端soi,从机端soi利用此公钥将使用的对称加密的密钥加密后回传给主机端moi,主机端moi利用数据传输部分使用的私钥对从机端soi回传的数据进行解密,获得对称加密的密钥,主从机端soi之间受保护的数据传输通道建立,二者之间传输的数据使用对称加密的密钥进行加解密。

20.本实施例的装置,采用嵌入式设计,可灵活选择嵌入位置,最大限度的适配传统系统架构;实现方式多样,装置支持在处理器系统部分通过硬核固化实现,支持在可编程逻辑部分通过软核配置实现,支持在二者之间协同配置实现;增加主从机身份认证功能,通过授权开启访问,防止访问被篡改、系统架构被窃取;数据传输受加密保护,防止通道数据被监听泄露;传输数据使用对称加密,不影响传输带宽和速度;身份认证信息和fpga uid信息绑定,形成针对特定fpga的差异性保护。

21.本发明不局限于上述实施例所述的具体技术方案,除上述实施例外,本发明还可以有其他实施方式。对于本领域的技术人员来说,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等形成的技术方案,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。