一种借由自动工具完成的模块化半定制fpga芯片设计方法

技术领域

1.本发明涉及一种借由自动工具完成的模块化半定制fpga芯片设计方法,属于芯片设计技术领域。

背景技术:

2.现场可编程门阵列(fpga)芯片主要由可编程输入输出单元,可配置逻辑单元块,时钟管理模块,嵌入式ram块,布线资源,以及内嵌专用硬核等资源构成。针对不同的应用场景fpga芯片内部资源的种类和数量会有所不同。

3.在大规模数据处理应用需求的推动下,当前fpga芯片在计算系统中发挥着越来越大的作用。为了针对特定领域应用所面临的前所未有的处理能力的挑战,可对fpga芯片进行领域定制。然而,定制fpga芯片的设计和开发是一个复杂过程,需要具备强大的专业知识人员,花费大量的时间进行手动的布局布线。另一方面,针对不同的应用场景,为了达到最优的系统性能和功耗,需要对fpga芯片内部资源种类、数量和排布进行调整。因此需要一种新的设计方法,其能够根据需求,快速定制芯片架构并设计出fpga芯片,以降低fpga芯片设计难度,缩短设计时间。

技术实现要素:

4.本发明要解决的技术问题是:如何快速进行芯片设计。

5.为了解决上述技术问题,本发明提出的技术方案是:一种借由自动工具完成的模块化半定制fpga芯片设计方法,执行如下步骤:1)完成芯片架构的描述文件;所述描述文件需包括工艺参数、资源块分布、时序约束信息及其他待定制化整体架构信息;2)解析架构文件生成格式化综合电路网表和时序约束文件;3)资源块库文件调用;4)定制单元添加;5)综合布局布线;6)生成版图。

6.上述技术方案的改进是:所述资源块包括,可配置输入输出单元块:可配置输入输出单元块是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配;可配置逻辑单元块:可配置逻辑单元块是fpga内的基本逻辑单元;时钟管理单元块:提供芯片内部时钟管理功能;嵌入式ram单元块:嵌入式ram单元块,为大容量的片内存储单元;可配置布线资源块:可配置布线资源块连通fpga内部的所有单元。

7.本发明的有益效果是:基于fpga内部资源的可扩展性,设计人员可根据特定的应用场景,自由的扩展或者裁剪fpga内部资源,实现快速定制fpga芯片,缩短芯片设计时间,

在提高开发效率的同时,达到资源块的面积,功耗,性能达到最优。

附图说明

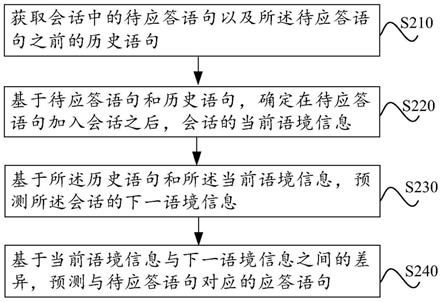

8.图1是本发明实施例一的一种借由自动工具完成的模块化半定制fpga芯片设计方法的流程示意图。

具体实施方式

9.实施例一如图1所示,一种借由自动工具完成的模块化半定制fpga芯片设计方法,执行如下步骤:1)完成芯片架构的描述文件;所述描述文件需包括工艺参数、资源块分布、时序约束信息及其他待定制化整体架构信息;2)解析架构文件生成格式化综合电路网表和时序约束文件;3)资源块库文件调用;4)定制单元添加;5)综合布局布线;6)生成版图。

10.所述资源块包括:可配置输入输出单元块:可配置输入输出单元块是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配。

11.可配置逻辑单元块:可配置逻辑单元块是fpga内的基本逻辑单元。可配置逻辑单元块由多输入查找表、多路开关选择器和触发器等组成。可配置逻辑单元是高度灵活的,可以对其进行配置以实现组合逻辑、时序逻辑或分布式ram等功能。

12.时钟管理单元块:提供芯片内部时钟管理功能,包括时钟的分频、倍频、相移,降低抖动等功能。

13.嵌入式ram单元块:嵌入式ram单元块,为大容量的片内存储单元,其可被配置为单端口ram、双端口ram以及fifo等常用存储结构。

14.可配置布线资源块:可配置布线资源块连通fpga内部的所有单元,是所有单元之间信号传递的桥梁。连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。

15.所述的对架构文件解析,是指对架构描述文件做自动解析,以得到设计所需的基本电路单元类型、数量、位置分布以及单元间的连接关系。

16.进一步地,输出全芯片的可综合的电路网表文件和时序约束文件。

17.所述的定制化设计替换,是指对所述的基本电路单元块做定制化的开发,以达到对基本电路单元在面积,功耗,性能上的优化。

18.进一步地,采用定制化设计的基本电路单元替换标准单元库中的电路单元。

19.最后,使用自动工具完成后端流程,生成半定制化的fpga版图文件,实现快速半定制fpga芯片设计。

20.本发明不局限于上述实施例所述的具体技术方案,除上述实施例外,本发明还可以有其他实施方式。对于本领域的技术人员来说,凡在本发明的精神和原则之内,所作的任

何修改、等同替换、改进等形成的技术方案,均应包含在本发明的保护范围之内。

技术特征:

1.一种借由自动工具完成的模块化半定制fpga芯片设计方法,其特征在于执行如下步骤:1)完成芯片架构的描述文件;所述描述文件需包括工艺参数、资源块分布、时序约束信息及其他待定制化整体架构信息;2)解析架构文件生成格式化综合电路网表和时序约束文件;3)资源块库文件调用;4)定制单元添加;5)综合布局布线;6)生成版图。2.如权利要求1所述的借由自动工具完成的模块化半定制fpga芯片设计方法,其特征在于:所述资源块包括,可配置输入输出单元块,可配置输入输出单元块是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配;可配置逻辑单元块,可配置逻辑单元块是fpga内的基本逻辑单元;时钟管理单元块,提供芯片内部时钟管理功能;嵌入式ram单元块,嵌入式ram单元块,为大容量的片内存储单元;可配置布线资源块,可配置布线资源块连通fpga内部的所有单元。

技术总结

本发明涉及一种借由自动工具完成的模块化半定制FPGA芯片设计方法,属于芯片设计技术领域。该方法执行如下步骤:1)完成芯片架构的描述文件;所述描述文件需包括工艺参数、资源块分布、时序约束信息及其他待定制化整体架构信息;2)解析架构文件生成格式化综合电路网表和时序约束文件;3)资源块库文件调用;4)定制单元添加;5)综合布局布线;6)生成版图。本发明基于FPGA内部资源的可扩展性,设计人员可根据特定的应用场景,自由的扩展或者裁剪FPGA内部资源,实现快速定制FPGA芯片,缩短芯片设计时间,在提高开发效率的同时,达到资源块的面积,功耗,性能最优。性能最优。性能最优。

技术研发人员:赵飞 舒毅 杨海钢 贾一平 秋小强

受保护的技术使用者:北京中科胜芯科技有限公司

技术研发日:2021.09.15

技术公布日:2021/12/7

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。