1.本发明属于主板设计技术领域,具体涉及一种通过独立板卡来适配不同需求主板的系统及方法。

背景技术:

2.随着intel的x86架构不断更新和升级,服务器内部cpu、内存、pch等关键器件摆放位置也在intel的建议下逐渐固化,各个服务器设计厂商也基本都是根据intel的参考设计而进行部分修改,以便适配各家的要求。但随着服务器的机构外壳尺寸基本定型的情况下,内部需要放置的主板等主要板卡的尺寸也都限定在一定范围内,从而限定了主板的占用空间,即要求了板卡尺寸。在服务器功能日趋相同的情形下,接收得到厂商提出的服务器要求后,首先件主板占用空间评估,再进行公板设计,从而兼容各家的设计,主板作为公板可减少每个项目为每个客户单独设计主板带来的人力成本、物料成本。

3.但是公板设计需要按照各个客户需求进行一下定制化开发及设定,不同的客户根据不同的需求,需要维护多个主板bom,并需要安排不同项目的人力维护主板bom,造成人力浪费,且由于物料种类繁多还容易出错。

4.此为现有技术的不足,因此,针对现有技术中的上述缺陷,提供一种通过独立板卡来适配不同需求主板的系统及方法,是非常有必要的。

技术实现要素:

5.针对现有技术的上述主板作为公板设计,需要维护多个主板bom,浪费人力,并由于物料种类繁多容易出错的缺陷,本发明提供一种通过独立板卡来适配不同需求主板的系统及方法,以解决上述技术问题。

6.第一方面,本发明提供一种通过独立板卡来适配不同需求主板的系统,包括独立板卡和主板;

7.独立板卡上设置有第一接口;

8.主板上设置有第二接口、pch和bmc;

9.第一接口与第二接口能够配合,第二接口与pch和bmc均连接;

10.独立板卡上设置有选择模块,选择模块用于实现不同需求主板的区分。

11.进一步地,第一接口及第二接口上均设置有项目编号管脚组、sku编号管脚组以及bios/bmc版本管脚组;

12.第二接口的项目编号管脚组通过项目编号线排与pch和bmc连接,第二接口的sku编号管脚组通过sku编号线排与pch和bmc连接,第二接口的bios/bmc版本管脚组通过版本编号组线排与pch和bmc连接;

13.选择模块包括项目编号上下拉电阻排、sku编号上下拉电阻排以及版本编号上下拉电阻排;第一接口的项目编号管脚组与项目编号上下拉电阻排连接,第一接口的sku编号管脚组与sku编号上下拉电阻排连接,第一接口的bios/bmc版本管脚组与版本编号上下拉

电阻排连接。

14.进一步地,第一接口及第二接口上均设置有独立板卡在位信号管脚、电源管脚和接地管脚;

15.第二接口的独立板卡在位信号管脚连接在位上拉电阻的第一端,并在位信号管脚与pch及bmc均连接,在位上拉电阻的第二端与主板的3.3v旁路电源连接,第一接口的独立板卡在位信号管脚连接在位下拉电阻的第一端,在位下拉电阻第二端接地;第二接口的电源管脚与主板的3.3v旁路电源连接,第二接口的接地管脚接地;

16.第一接口的独立板卡在位信号管脚与第二接口的独立板卡在位信号管脚插接,第一接口的电源管脚与第二接口的电源管脚插接,第一接口的接地管脚与第二接口的接地管脚插接。独立板卡在位信号管脚用于指示独立板卡是否在位。

17.进一步地,第一独立板卡接口的项目编号管脚组包括若干项目编号管脚;

18.项目编号上下拉电阻排包括若干并联的项目编号电阻支路,每个项目编号电阻支路上设置有项目编号上拉电阻或项目编号下拉电阻;

19.第一接口的各项目编号管脚与对应项目编号电阻支路的项目编号上拉电阻或项目编号下拉电阻连接,且各项目编号上拉电阻均与第一接口的电源管脚连接,各项目编号下拉电阻均接地;

20.第一接口的sku编号管脚组包括若干sku编号管脚;

21.sku编号上下拉电阻排包括若干并联的sku编号电阻支路,每个sku编号电阻支路上设置有sku编号上拉电阻或sku编号下拉电阻;

22.第一接口的各sku编号管脚与对应sku编号电阻支路的sku编号上拉电阻或sku编号下拉电阻连接,且各sku编号上拉电阻均与第一接口的电源管脚连接,各sku编号下拉电阻均接地;

23.第一接口的bios/bmc版本管脚组包括若干bios/bmc版本管脚;

24.版本编号上下拉电阻排包括若干并联的版本编号电阻支路,每个版本编号电阻支路上设置有版本编号上拉电阻或版本编号下拉电阻;

25.第一接口的各bios/bmc版本管脚与对应版本编号电阻支路的版本编号上拉电阻或版本编号下拉电阻连接,且各版本编号上拉电阻均与第一接口的电源管脚连接,各版本编号下拉电阻均接地。项目编号管脚组用于指示项目编号,sku编号管脚组用于指示项目中套餐细化,bios/bmc版本管脚组用于指示不同bios/bmc版本。

26.进一步地,第一接口的项目编号管脚组中项目编号管脚的数量为八个;

27.第一接口的sku编号管脚组中sku编号管脚的数量为三个;

28.第一接口的bios/bmc版本管脚组中bios/bmc版本管脚的数量为三个。

29.进一步地,第一接口的项目编号管脚组与第二接口的项目编号管脚组插接;

30.第一接口的sku编号管脚组与第二接口的sku编号管脚组插接;

31.第一接口的bios/bmc版本管脚组与第二接口的bios/bmc版本管脚组插接。第一接口与第二接口插接将用于区分不同项目的上下电阻排从主板中分离出来。

32.进一步地,第一接口及第二接口上均设置有预留管脚。预留管脚可用于功能扩展

33.第二方面,本发明提供一种基于上述第一方面的通过独立板卡来适配不同需求主板的方法,包括如下步骤:

34.s1.根据项目需求不同区分各个主板项目,并为各个主板项目建立编号真值表;

35.s2.根据各个主板项目的编号真值表为独立板卡上的各电阻排对应电阻支路选定上拉电阻或下拉电阻;

36.s3.将独立板卡上的第一接口与主板的第二接口插接。

37.进一步地,步骤s1具体步骤如下:

38.s11.根据项目需求不同区分各个主板项目,根据项目不同生成项目编号,根据项目套餐不同生成sku编号,以及根据bios/bmc版本不同生成版本编号;

39.s12.根据各主板项目的项目编号、sku编号以及版本编号,为对应主板项目生成不同编号;

40.s13.将各主板项目的编号转换为二进制,生成编号真值表。编号真值表用于根据不同需求区分不同项目。

41.进一步地,所述二进制位数与项目编号管脚及sku编号管脚及bios/bmc版本管脚数量和,且每一位二进制与一个管脚对应。转换为二进制,从而便于选择上拉或下拉电阻,选择上拉电阻表示为1,选择下拉电阻表示为0。

42.进一步地,步骤s2具体步骤如下:

43.s21.获取编号真值表中各二进制的值及其对应的管脚;

44.s22.定位一个管脚;

45.s23.获取定位管脚的二进制值,并判断定位管脚的二进制值是否为1;

46.若是,进入步骤s24;

47.若否,进入步骤s25;

48.s24.设置定位管脚对应电阻支路连接上拉电阻,并设置上拉电阻与主板的3.3v旁路电源连接,进入步骤s26;

49.s25.设置定位管脚对应电阻支路连接下拉电阻,并设置下拉电阻接地,进入步骤s26;

50.s26.判断各管脚是否均已定位;

51.若是,进入步骤s3;

52.若否,定位下一个管脚,返回步骤s23。根据具体真值表中值进行上下电阻的选择,从而实现不同项目的区分。

53.进一步地,步骤s3具体步骤如下:

54.s31.通过第一接口与第二接口的插接,实现独立板卡与主板的插接;

55.s32.主板的3.3v旁路电源上电;

56.s33.bmc及pch通过第一接口及第二接口的独立板卡在位信号管脚获取到独立板卡在位,并实现不同主板项目的区分。通过独立板卡在位信号管脚向bmc及pch提供独立板卡是否在位的信号。

57.本发明的有益效果在于,

58.本发明提供的通过独立板卡来适配不同需求主板的系统及方法,通过独立板卡上上拉电阻及下拉电阻设计,选择项目编号、sku编号及版本编号,实现不同项目需求的满足,减少了人力资源浪费,提高了主板的复用性,保证了服务器主板设计的一致性。

59.此外,本发明设计原理可靠,结构简单,具有非常广泛的应用前景。

60.由此可见,本发明与现有技术相比,具有突出的实质性特点和显著的进步,其实施的有益效果也是显而易见的。

附图说明

61.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

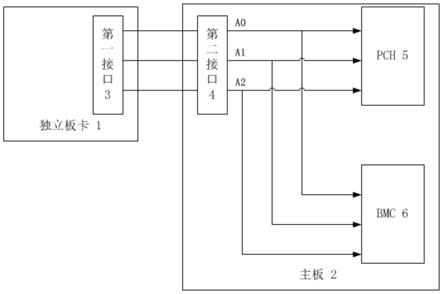

62.图1是本发明通过独立板卡来适配不同需求主板的系统三个管脚组插接示意图。

63.图2是本发明通过独立板卡来适配不同需求主板的系统独立板卡在位信号管脚插接示意图。

64.图3是本发明通过独立板卡来适配不同需求主板的系统项目编号管脚组在独立板卡的与项目编号上下拉电阻排连接电路示意图。

65.图4是本发明通过独立板卡来适配不同需求主板的系统第一接口及第二接口结构示意图。

66.图5是本发明通过独立板卡来适配不同需求主板的系统第一接口及第二接口各管脚名称示意图。

67.图6是本发明通过独立板卡来适配不同需求主板的系统第一接口的项目编号管脚组内各管脚对应真值表示意图。

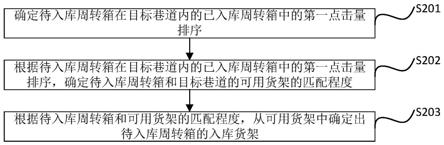

68.图7是本发明的通过独立板卡来适配不同需求主板的方法流程示意图一。

69.图8是本发明的通过独立板卡来适配不同需求主板的方法流程示意图二。

70.图中,1

‑

独立板卡;2

‑

主板;3

‑

第一接口;4

‑

第二接口;5

‑

pch;6

‑

bmc;a0

‑

项目编号管脚组;a1

‑

sku编号管脚组;a2

‑

bios/bmc版本管脚组;p1

‑

电源管脚;p2

‑

独立板卡在位信号管脚;p3

‑

接地管脚;p3v3_stby

‑

3.3v旁路电源;r0

‑

在位下拉电阻;r100

‑

在位上拉电阻;board id0

‑

7,八个项目编号管脚;sku id0

‑

2,三个sku编号管脚;fw ver0

‑

2,三个bios/bmc版本管脚;reserved0

‑

2,三个预留管脚;r1

‑

第一电阻;r2

‑

第二电阻;r3

‑

第三电阻;r4

‑

第四电阻;r5

‑

第五电阻;r6

‑

第六电阻;r7

‑

第七电阻;r8

‑

第八电阻;r9

‑

第九电阻;r10

‑

第十电阻;r11

‑

第十一电阻;r12

‑

第十二电阻;r13

‑

第十三电阻;r14

‑

第十四电阻;r15

‑

第十五电阻;r16

‑

第十六电阻。

具体实施方式

71.为了使本技术领域的人员更好地理解本发明中的技术方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

72.bmc,是baseboard manager controller的简称,基板管理控制器。

73.pch,是platform controller hub的简称,intel公司的集成南桥。

74.实施例1:

75.如图1所示,本发明提供一种通过独立板卡来适配不同需求主板的系统,包括独立

板卡1和主板2;

76.独立板卡1上设置有第一接口3;

77.主板2上设置有第二接口4、pch 5和bmc 6;

78.第一接口3与第二接口4能够配合,第二接口4与pch 5和bmc 6均连接;

79.独立板卡1上设置有选择模块,选择模块用于实现不同需求主板的区分。独立板卡采用sku板,sku,是stock keeping unit的简称,是库存量单位,即库存进出计量的基本单元,可以是以件,盒,托盘等为单位。现在已经被引申为产品统一编号的产品,每种产品均对应有唯一的sku号,对于服务器产品sku编号用于各自项目区分不同的套餐及细化要求。

80.实施例2:

81.如图1及图2所示,本发明提供一种通过独立板卡来适配不同需求主板的系统,包括独立板卡1和主板2;

82.独立板卡1上设置有第一接口3;

83.主板2上设置有第二接口4、pch 5和bmc 6;

84.第一接口3与第二接口4能够配合,第二接口4与pch 5和bmc 6均连接;

85.独立板卡1上设置有选择模块,选择模块用于实现不同需求主板的区分;

86.第一接口3及第二接口4上均设置有项目编号管脚组a0、sku编号管脚组a1以及bios/bmc版本管脚组a2;

87.第二接口3的项目编号管脚组a0通过项目编号线排与pch 5和bmc 6连接,第二接口4的sku编号管脚组a1通过sku编号线排与pch 5和bmc 6连接,第二接口4的bios/bmc版本管脚组a2通过版本编号组线排与pch 5和bmc 6连接;

88.选择模块包括项目编号上下拉电阻排、sku编号上下拉电阻排以及版本编号上下拉电阻排;第一接口3的项目编号管脚组a0与项目编号上下拉电阻排连接,第一接口3的sku编号管脚组a1与sku编号上下拉电阻排连接,第一接口3的bios/bmc版本管脚组a2与版本编号上下拉电阻排连接;

89.第一接口3及第二接口4上均设置有独立板卡在位信号管脚p2、电源管脚p1和接地管脚p3;

90.第二接口4的独立板卡在位信号管脚p2连接在位上拉电阻r100的第一端,并在位信号管脚p2与pch 5及bmc 6均连接,在位上拉电阻r100的第二端与主板的3.3v旁路电源p3v3_stby连接,第一接口3的独立板卡在位信号管脚p2连接在位下拉电阻r0的第一端,在位下拉电阻r0第二端接地;

91.第二接口4的电源管脚p 1与主板的3.3v旁路电源p3v3_stby连接,第二接口4的接地管脚p3接地;

92.第一接口3的独立板卡在位信号管脚p2与第二接口4的独立板卡在位信号管脚p2插接,第一接口3的电源管脚p1与第二接口4的电源管脚p1插接,第一接口3的接地管脚p3与第二接口4的接地管脚p3插接;

93.第一接口3的项目编号管脚组a0包括若干项目编号管脚;

94.项目编号上下拉电阻排包括若干并联的项目编号电阻支路,每个项目编号电阻支路上设置有项目编号上拉电阻或项目编号下拉电阻;

95.第一接口3的各项目编号管脚与对应项目编号电阻支路的项目编号上拉电阻或项

目编号下拉电阻连接,且各项目编号上拉电阻均与第一接口3的电源管脚p1连接,各项目编号下拉电阻均接地;

96.第一接口3的sku编号管脚组a1包括若干sku编号管脚;

97.sku编号上下拉电阻排包括若干并联的sku编号电阻支路,每个sku编号电阻支路上设置有sku编号上拉电阻或sku编号下拉电阻;

98.第一接口3的各sku编号管脚与对应sku编号电阻支路的sku编号上拉电阻或sku编号下拉电阻连接,且各sku编号上拉电阻均与第一接口3的电源管脚p1连接,各sku编号下拉电阻均接地;

99.第一接口3的bios/bmc版本管脚组a2包括若干bios/bmc版本管脚;

100.版本编号上下拉电阻排包括若干并联的版本编号电阻支路,每个版本编号电阻支路上设置有版本编号上拉电阻或版本编号下拉电阻;

101.第一接口3的各bios/bmc版本管脚与对应版本编号电阻支路的版本编号上拉电阻或版本编号下拉电阻连接,且各版本编号上拉电阻均与第一接口3的电源管脚p1连接,各版本编号下拉电阻均接地;

102.第一接口3的项目编号管脚组a0与第二接口4的项目编号管脚组a0插接;

103.第一接口3的sku编号管脚组a1与第二接口4的sku编号管脚组a1插接;

104.第一接口3的bios/bmc版本管脚组a2与第二接口4的bios/bmc版本管脚组a2插接;

105.第一接口3及第二接口4上均设置有预留管脚。

106.实施例3:

107.如图1及图2所示,本发明提供一种通过独立板卡来适配不同需求主板的系统,包括独立板卡1和主板2;

108.独立板卡1上设置有第一接口3;

109.主板2上设置有第二接口4、pch 5和bmc 6;

110.第一接口3与第二接口4能够配合,第二接口4与pch 5和bmc 6均连接;

111.独立板卡1上设置有选择模块,选择模块用于实现不同需求主板的区分;

112.第一接口3及第二接口4上均设置有项目编号管脚组a0、sku编号管脚组a1以及bios/bmc版本管脚组a2;

113.第二接口3的项目编号管脚组a0通过项目编号线排与pch 5和bmc 6连接,第二接口4的sku编号管脚组a1通过sku编号线排与pch 5和bmc 6连接,第二接口4的bios/bmc版本管脚组a2通过版本编号组线排与pch 5和bmc 6连接;

114.选择模块包括项目编号上下拉电阻排、sku编号上下拉电阻排以及版本编号上下拉电阻排;

115.第一接口3的项目编号管脚组a0连接有项目编号上下拉电阻排,第一接口3的sku编号管脚组a1连接有sku编号上下拉电阻排,第一接口3的bios/bmc版本管脚组a2连接有版本编号上下拉电阻排;

116.第一接口3及第二接口4上均设置有独立板卡在位信号管脚p2、电源管脚p1和接地管脚p3;

117.第二接口4的独立板卡在位信号管脚p2连接在位上拉电阻r100第第一端,并在位信号管脚p2与pch 5及bmc 6均连接,在位上拉电阻r100的第二端与主板的3.3v旁路电源

p3v3_stby连接,第一接口3的独立板卡在位信号管脚p2连接在位下拉电阻r0的第一端,在位下拉电阻r0第二端接地;在位下拉电阻r0的值取100欧姆,独立板卡在位信号管脚p2用于指示独立板卡在位;

118.第二接口4的电源管脚p1与主板的3.3v旁路电源p3v3_stby连接,第二接口4的接地管脚p3接地;

119.第一接口3的独立板卡在位信号管脚p2与第二接口4的独立板卡在位信号管脚p2插接,第一接口3的电源管脚p1与第二接口4的电源管脚p1插接,第一接口3的接地管脚p3与第二接口4的接地管脚p3插接;

120.第一接口3的项目编号管脚组a0包括八个项目编号管脚board id0

‑

7;

121.项目编号上下拉电阻排包括八个并联的项目编号电阻支路,每个项目编号电阻支路上设置有项目编号上拉电阻或项目编号下拉电阻;每个项目编号电阻支路可选项目编号上拉电阻与项目编号下拉电阻中的一个;项目编号管脚board id0对应的项目编号电阻支路连接有第一电阻r1或第二电阻r2,其中第一电阻r1为上拉电阻,第二电阻r2为下拉电阻,第一电阻r1和第二电阻r2只能选一个;项目编号管脚board id1对应的项目编号电阻支路连接有第三电阻r3或第四电阻r4,其中第三电阻r3为上拉电阻,第四电阻r4为下拉电阻,第三电阻r3和第四电阻r4只能选一个;项目编号管脚board id2对应的项目编号电阻支路连接有第五电阻r5或第六电阻r6,其中第五电阻r5为上拉电阻,第六电阻r6为下拉电阻,第五电阻r5和第六电阻r6只能选一个;项目编号管脚board id3对应的项目编号电阻支路连接有第七电阻r7或第八电阻r8,其中第七电阻r7为上拉电阻,第八电阻r8为下拉电阻,第七电阻r7和第八电阻r8只能选一个;项目编号管脚board id4对应的项目编号电阻支路连接有第九电阻r9或第十电阻r10,其中第九电阻r9为上拉电阻,第十电阻r10为下拉电阻,第九电阻r9和第十电阻r10只能选一个;项目编号管脚board id5对应的项目编号电阻支路连接有第十一电阻r11或第十二电阻r12,其中第十一电阻r11为上拉电阻,第十二电阻r12为下拉电阻,第十一电阻r11和第十二电阻r12只能选一个;项目编号管脚board id6对应的项目编号电阻支路连接有第十三电阻r13或第十四电阻r14,其中第十三电阻r13为上拉电阻,第十四电阻r14为下拉电阻,第十三电阻r13和第十四电阻r14只能选一个;项目编号管脚board id7对应的项目编号电阻支路连接有第十五电阻r15或第十六电阻r16,其中第十五电阻r15为上拉电阻,第十六电阻r16为下拉电阻,第十五电阻r15和第十六电阻r16只能选一个;不选择的电阻采用“cn”标识,表示不上件,如图3所示,以项目编号管脚board_id0为例,对应上拉电阻为第一电阻r1,下拉电阻为第二电阻r2,其中第二电阻r2为“cn”标识,即不上件,第一电阻r1没有“cn”标识,即上件,这样就使得board_id0为3.3v的电平,即高电平,经第一接口3和第二接口4后,在主板2端的pch 5和bmc 6即可表示为“1”;当第一电阻r1不上件,第二电阻r2上件时,则表示为“0”;具体选择根据编号真值表中项目编号管脚对应值进行;图6为不同项目的编号真值表中项目编号管脚对应值的示意图;项目列代表不同的项目,a项目、b项目、c项目以及d项目等,通过维护这样的一张真值表来设定不同的项目,并决定了每个不同的独立板卡的上下拉电阻设定,通过设定次真值表来表示不同的项目;sku编号管脚sku id0

‑

2对应的真值表与项目编号管脚board id0

‑

7的原理相同,采用上下拉方式来按照不同项目套餐需求进行上下拉电阻的上件;bios/bmc版本管脚fw ver0

‑

2对应真值表与sku编号管脚sku id0

‑

2的原理相同,用于区分不同的bios/bmc版本;

122.第一接口3的各项目编号管脚与对应项目编号电阻支路的项目编号上拉电阻或项目编号下拉电阻连接,且各项目编号上拉电阻均与第一接口3的电源管脚p1连接,各项目编号下拉电阻均接地;

123.第一接口3的sku编号管脚组a1包括三个sku编号管脚sku id0

‑

2;

124.sku编号上下拉电阻排包括三个并联的sku编号电阻支路,每个sku编号电阻支路上设置有sku编号上拉电阻或sku编号下拉电阻;

125.第一接口3的各sku编号管脚与对应sku编号电阻支路的sku编号上拉电阻或sku编号下拉电阻连接,且各sku编号上拉电阻均与第一接口3的电源管脚p1连接,各sku编号下拉电阻均接地;

126.第一接口3的bios/bmc版本管脚组a2包括三个bios/bmc版本管脚fw ver0

‑

2;

127.版本编号上下拉电阻排包括三个并联的版本编号电阻支路,每个版本编号电阻支路上设置有版本编号上拉电阻或版本编号下拉电阻;

128.第一接口3的各bios/bmc版本管脚与对应版本编号电阻支路的版本编号上拉电阻或版本编号下拉电阻连接,且各版本编号上拉电阻均与第一接口3的电源管脚p1连接,各版本编号下拉电阻均接地;

129.第一接口3的项目编号管脚组a0与第二接口4的项目编号管脚组a0插接;

130.第一接口3的sku编号管脚组a1与第二接口4的sku编号管脚组a1插接;

131.第一接口3的bios/bmc版本管脚组a2与第二接口4的bios/bmc版本管脚组a2插接;

132.第一接口3及第二接口4的结构如图4所示;

133.第一接口3及第二接口4上还设置有三个预留管脚reserved0

‑

2,具体各个管脚名称和功能如图5所示。

134.实施例4:

135.如图7所示,本发明提供一种基于上述实施例1、实施例2或实施例3的通过独立板卡来适配不同需求主板的方法,包括如下步骤:

136.s1.根据项目需求不同区分各个主板项目,并为各个主板项目建立编号真值表;

137.s2.根据各个主板项目的编号真值表为独立板卡上的各电阻排对应电阻支路选定上拉电阻或下拉电阻;

138.s3.将独立板卡上的第一接口与主板的第二接口插接。

139.实施例5:

140.如图8所示,本发明提供一种通过独立板卡来适配不同需求主板的方法,包括如下步骤:

141.s1.根据项目需求不同区分各个主板项目,并为各个主板项目建立编号真值表;具体步骤如下:

142.s11.根据项目需求不同区分各个主板项目,根据项目不同生成项目编号,根据项目套餐不同生成sku编号,以及根据bios/bmc版本不同生成版本编号;

143.s12.根据各主板项目的项目编号、sku编号以及版本编号,为对应主板项目生成不同编号;

144.s13.将各主板项目的编号转换为二进制,生成编号真值表;所述二进制位数与项目编号管脚及sku编号管脚及bios/bmc版本管脚数量和,且每一位二进制与一个管脚对应;

145.s2.根据各个主板项目的编号真值表为独立板卡上的各电阻排对应电阻支路选定上拉电阻或下拉电阻;具体步骤如下:

146.s21.获取编号真值表中各二进制的值及其对应的管脚;

147.s22.定位一个管脚;

148.s23.获取定位管脚的二进制值,并判断定位管脚的二进制值是否为1;

149.若是,进入步骤s24;

150.若否,进入步骤s25;

151.s24.设置定位管脚对应电阻支路连接上拉电阻,并设置上拉电阻与主板的3.3v旁路电源连接,进入步骤s26;

152.s25.设置定位管脚对应电阻支路连接下拉电阻,并设置下拉电阻接地,进入步骤s26;

153.s26.判断各管脚是否均已定位;

154.若是,进入步骤s3;

155.若否,定位下一个管脚,返回步骤s23;

156.s3.将独立板卡上的第一接口与主板的第二接口插接;具体步骤如下:

157.s31.通过第一接口与第二接口的插接,实现独立板卡与主板的插接;

158.s32.主板的3.3v旁路电源上电;

159.s33.bmc及pch通过第一接口及第二接口的独立板卡在位信号管脚获取到独立板卡在位,并实现不同主板项目的区分。

160.尽管通过参考附图并结合优选实施例的方式对本发明进行了详细描述,但本发明并不限于此。在不脱离本发明的精神和实质的前提下,本领域普通技术人员可以对本发明的实施例进行各种等效的修改或替换,而这些修改或替换都应在本发明的涵盖范围内/任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。