1.本发明的实施例是有关于一种制造半导体装置的方法。

背景技术:

2.由于不同电子组件(例如,晶体管、二极管、电阻器、电容器等)的集成密度(integration density)的持续提高,半导体行业已经历快速增长。在很大程度上,集成密度的提高是由于最小特征大小(feature size)的不断减小,这允许更多的组件能够集成到给定区域内。随着对缩小电子装置的需求的增长,出现了对更小且更具创造性的半导体管芯封装技术的需要。这种封装系统的实例是叠层封装(package

‑

on

‑

package,pop)技术。在叠层封装装置中,顶部半导体封装被堆叠在底部半导体封装的顶部上,以提供高集成水平及组件密度。叠层封装技术一般能够生产功能性得到增强且在印刷电路板(printed circuit board,pcb)上覆盖面积小的半导体装置。

技术实现要素:

3.本发明实施例提供一种制造半导体装置的方法,包括以下步骤。将聚合物材料放置在衬底之上。对聚合物材料进行图案化。以及,在介于170℃到230℃范围内的温度下对聚合物材料进行固化。聚合物材料包含聚合物前体、感光剂、交联剂及溶剂。感光剂包括4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑。

4.本发明实施例提供一种,包括以下步骤。在衬底之上施加聚合物混合物。对聚合物混合物的至少一部分进行曝光及显影以形成介电层。对介电层进行固化。及,在介电层之上形成金属化图案。聚合物混合物包含聚合物前体、溶剂、交联剂及感光剂。交联剂包括二甲基丙烯酸四乙二醇酯,聚合物混合物含2重量%到10重量%的交联剂。感光剂包括4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑。

5.本发明实施例提供一种半导体封装,包括管芯、包封体、穿孔及重布线结构。管芯位于第一介电层上。包封体位于第一介电层上,且包封体包封管芯。穿孔延伸穿过包封体。重布线结构位于包封体、管芯及穿孔之上。重布线结构包括第二介电层及位于第二介电层上的金属化图案。第二介电层具有介于175mpa到190mpa范围内的拉伸强度,且具有3gpa的杨氏模量。金属化图案包括延伸穿过第二介电层以实体耦合及电耦合管芯的第一导通孔及延伸穿过第二介电层以实体耦合及电耦合穿孔的第二导通孔。

附图说明

6.结合附图阅读以下详细说明,会最好地理解本揭露的各个方面。应注意,根据本行业中的标准惯例,各种特征并非按比例绘制。事实上,为论述清晰起见,可任意增大或减小各种特征的尺寸。

7.图1示出根据一些实施例的集成电路管芯的剖视图。

8.图2到图8示出根据一些实施例的用于形成封装组件的工艺期间的各中间步骤的

剖视图。

9.图9示出根据一些实施例的封装组件的介电层的形成的剖视图。

10.图10a及图10b进一步示出根据一些实施例的封装组件的介电层的形成。

11.图11示出根据一些实施例的封装组件的介电层的图案化的剖视图。

12.图12a及图12b进一步示出根据一些实施例的封装组件的介电层的性质。

13.图13到图21示出根据一些实施例的用于形成封装组件的工艺期间的进一步的中间步骤的剖视图。

14.图22及图23示出根据一些实施例的装置堆叠的形成及实现的剖视图。

具体实施方式

15.以下揭露内容提供用于实现本发明的不同特征的诸多不同的实施例或实例。以下阐述组件及布置的具体实例以简化本揭露。当然,这些仅为实例而非旨在进行限制。举例来说,在以下说明中,在第二特征之上或第二特征上形成第一特征可包括其中第一特征与第二特征被形成为直接接触的实施例,且也可包括其中第一特征与第二特征之间可形成附加特征从而使得第一特征与第二特征可不直接接触的实施例。另外,本揭露在各种实例中可重复使用参考编号和/或字母。此种重复使用是为了简明及清晰起见,且自身并不表示所论述的各个实施例和/或配置之间的关系。

16.此外,为易于说明,本文中可能使用例如“在...之下”、“在...下方”、“下部的”、“在...上方”、“上部的”等空间相对性用语来阐述图中所示一个元件或特征与另一(其他)元件或特征的关系。所述空间相对性用语旨在除图中所绘示的取向外还囊括装置在使用或操作中的不同取向。设备可另外取向(旋转90度或处于其他取向),且本文中所用的空间相对性描述语可同样相应地进行解释。

17.现在将针对其中利用聚酰亚胺材料来形成介电层的特定实施例以及半导体装置来阐述实施例。然而,所阐述的实施例并不旨在局限于本文阐述的实施例,且可在各种实施例中使用。

18.图1示出根据一些实施例的集成电路管芯50的剖视图。集成电路管芯50将在后续处理中被封装以形成集成电路封装。集成电路管芯50可为逻辑管芯(例如,中央处理单元(central processing unit,cpu)、图形处理单元(graphics processing unit,gpu)、系统芯片(system

‑

on

‑

a

‑

chip,soc)、应用处理器(application processor,ap)、微控制器等)、存储器管芯(例如,动态随机存取存储器(dynamic random access memory,dram)管芯、静态随机存取存储器(static random access memory,sram)管芯等)、电力管理管芯(例如,电力管理集成电路(power management integrated circuit,pmic)管芯)、射频(radio frequency,rf)管芯、传感器管芯、微机电系统(micro

‑

electro

‑

mechanical

‑

system,mems)管芯、信号处理管芯(例如,数字信号处理(digital signal processing,dsp)管芯)、前端管芯(例如,模拟前端(analog front

‑

end,afe)管芯)、类似管芯或其组合。

19.集成电路管芯50可形成在晶片(wafer)中,所述晶片可包括不同的装置区,这些装置区在后续步骤中被单体化以形成多个集成电路管芯,例如(举例来说)通过锯切工艺。集成电路管芯50可根据可适用的制造工艺进行处理以形成集成电路。例如,集成电路管芯50包括半导体衬底52,例如经掺杂的或未经掺杂的硅、或绝缘体上半导体(semiconductor

‑

on

‑

insulator,soi)衬底的有源层。半导体衬底52可包含:其他半导体材料,例如锗;化合物半导体,包括碳化硅、镓砷、磷化镓、磷化铟、砷化铟、和/或锑化铟;合金半导体,包括sige、gaasp、alinas、algaas、gainas、gainp、和/或gainasp;或者其组合。也可使用例如多层式衬底或梯度衬底等其他衬底。半导体衬底52具有有源表面(例如,图1中面朝上的表面),有时称为前侧;以及无源表面(例如,图1中面朝下的表面),有时称为背侧。

20.装置(由晶体管表示)54可形成在半导体衬底52的前表面处。装置54可为有源装置(例如,晶体管、二极管等)、电容器、电阻器等。层间介电质(inter

‑

layer dielectric,ild)56位于半导体衬底52的前表面之上。ild56环绕并可覆盖装置54。ild 56可包括由例如磷硅酸盐玻璃(phospho

‑

silicate glass,psg)、硼硅酸盐玻璃(boro

‑

silicate glass,bsg)、硼掺杂磷硅酸盐玻璃(boron

‑

doped phospho

‑

silicate glass,bpsg)、未掺杂硅酸盐玻璃(undoped silicate glass,usg)等材料形成的一个或多个介电层。

21.导电插塞58延伸穿过ild 56,以电耦合及实体耦合装置54。例如,当装置54是晶体管时,导电插塞58可耦合晶体管的栅极及源极/漏极区。导电插塞58可由钨、钴、镍、铜、银、金、铝、类似材料或其组合形成。内连线结构60位于ild 56及导电插塞58之上。内连线结构60将装置54内连以形成集成电路。内连线结构60可由例如ild 56上的介电层中的金属化图案形成。金属化图案包括形成在一个或多个低介电常数(low

‑

k)介电层中的金属线及通孔。内连线结构60的金属化图案通过导电插塞58电耦合到装置54。

22.集成电路管芯50还包括进行外部连接的焊盘62,例如铝焊盘。焊盘62位于集成电路管芯50的有源侧上,例如位于内连线结构60中和/或内连线结构60上。一个或多个钝化膜64位于集成电路管芯50上,例如位于内连线结构60及焊盘62的部分上。开口穿过钝化膜64延伸到焊盘62。例如导电柱或导通孔(例如,由例如铜等金属形成)等管芯连接件66延伸穿过钝化膜64中的开口,且实体耦合及电耦合到焊盘62中的相应一者。管芯连接件66可通过例如镀覆等来形成。管芯连接件66电耦合集成电路管芯50的相应的集成电路。

23.任选地,焊料区(例如,焊料球或焊料凸块)可设置在焊盘62上。焊料球可用于对集成电路管芯50执行芯片探针(chip probe,cp)测试。可对集成电路管芯50执行cp测试,以确定集成电路管芯50是否是已知良好管芯(known good die,kgd)。因此,仅作为kgd的集成电路管芯50经历后续处理并被封装,而未通过cp测试的管芯不被封装。在测试之后,可在后续处理步骤中移除焊料区。

24.介电层68可(或可不)位于集成电路管芯50的有源侧上,例如位于钝化膜64及管芯连接件66上。介电层68在横向上包封管芯连接件66,且介电层68在横向上与集成电路管芯50相接。最初,介电层68可掩埋管芯连接件66,使得介电层68的最上表面位于管芯连接件66的最顶表面上方。在其中焊料区设置在管芯连接件66上的一些实施例中,介电层68也可掩埋焊料区。作为另一选择,可在形成介电层68之前移除焊料区。

25.介电层68可为聚合物,例如聚苯并恶唑(polybenzoxazole,pbo)、聚酰亚胺、苯并环丁烯(benzocyclobutene,bcb)等;氮化物,例如氮化硅等;氧化物,例如氧化硅、psg、bsg、bpsg等;类似材料或其组合。介电层68可例如通过旋转涂布、叠层、化学气相沉积(chemical vapor deposition,cvd)等来形成。在一些实施例中,在集成电路管芯50的形成期间,管芯连接件66通过介电层68被暴露出,例如通过研磨工艺。在一些实施例中,管芯连接件66保持被掩埋,且在封装集成电路管芯50的后续工艺期间被暴露出。暴露出管芯连接件66可移除

管芯连接件66上可能存在的任何焊料区。

26.在一些实施例中,集成电路管芯50是包括多个半导体衬底52的堆叠式装置。例如,集成电路管芯50可为包括多个存储器管芯的存储器装置,例如混合存储器立方体(hybrid memory cube,hmc)模块、高带宽存储器(high bandwidth memory,hbm)模块等。在此种实施例中,集成电路管芯50包括通过衬底穿孔(through

‑

substrate via,tsv)内连的多个半导体衬底52。半导体衬底52中的每一者可具有(或者可不具有)内连线结构60。

27.图2到图20示出根据一些实施例的用于形成第一封装组件100的工艺期间的各中间步骤的剖视图。示出第一封装区100a及第二封装区100b,并且封装集成电路管芯50中的一者或多者以在封装区100a及100b中的每一者中形成集成电路封装。集成电路封装也可被称为集成扇出型(integrated fan

‑

out,info)封装。

28.在图2中,提供载体衬底102,且在载体衬底102上形成释放层104。载体衬底102可为玻璃载体衬底、陶瓷载体衬底等。载体衬底102可为晶片,使得可在载体衬底102上同时形成多个封装。

29.释放层104可由聚合物系材料形成,其可与载体衬底102一起从将在后续步骤中形成的上覆结构被移除。在一些实施例中,释放层104是在受热时会失去其粘合性质的环氧系热释放材料,例如光热转换(light

‑

to

‑

heat

‑

conversion,lthc)释放涂层。在其他实施例中,释放层104可为紫外(ultra

‑

violet,uv)胶,其在被暴露于紫外光时会丧失其粘合性质。释放层104可作为液体进行分配并进行固化,可为被叠层到载体衬底102上的叠层体膜(laminate film),或可为类似物。释放层104的顶表面可被整平(leveled)且可具有高平面度(degree of planarity)。

30.在图3中,可在释放层104上形成背侧重布线结构106。在所示实施例中,背侧重布线结构106包括介电层108、金属化图案110(有时被称为重布线层或重布线走线)及介电层112。背侧重布线结构106是任选的。在一些实施例中,在释放层104上形成没有金属化图案的介电层来代替背侧重布线结构106。

31.可在释放层104上形成介电层108。介电层108的底表面可与释放层104的顶表面接触。在一些实施例中,介电层108是由例如聚苯并恶唑(pbo)、聚酰亚胺(polyimide)、苯并环丁烯(bcb)等聚合物形成。在其他实施例中,介电层108是由以下材料形成:氮化物,例如氮化硅;氧化物,例如氧化硅、磷硅酸盐玻璃(psg)、硼硅酸盐玻璃(bsg)、硼掺杂磷硅酸盐玻璃(bpsg)等;或者类似材料。介电层108可通过例如旋转涂布、cvd、叠层(laminating)、类似工艺或其组合等任何可接受的沉积工艺来形成。

32.可在介电层108上形成金属化图案110。作为形成金属化图案110的实例,在介电层108之上形成晶种层。在一些实施例中,晶种层为金属层,其可为单一层或包括由不同材料形成的多个子层的复合层。在一些实施例中,晶种层包括钛层及位于所述钛层之上的铜层。晶种层可利用例如物理气相沈积(physical vapor deposition,pvd)等来形成。接着在晶种层上形成光刻胶(未示出)并将其图案化。光刻胶可通过旋转涂布等来形成且可被暴露于光以进行图案化。光刻胶的图案对应于金属化图案110。所述图案化形成穿过光刻胶的开口以暴露出晶种层。在光刻胶的开口中及晶种层的被暴露的部分上形成导电材料。所述导电材料可通过例如电镀或无电镀覆等镀覆来形成。导电材料可包括金属,如铜、钛、钨、铝等。接着,移除光刻胶以及晶种层的上面未形成导电材料的部分。光刻胶可通过可接受的灰化

工艺或剥除工艺来移除,例如使用氧等离子体等。一旦光刻胶被移除,便例如通过使用可接受的刻蚀工艺(例如通过湿法刻蚀或干法刻蚀)来移除晶种层的被暴露的部分。晶种层的剩余部分及导电材料会形成金属化图案110。

33.可在金属化图案110及介电层108上形成介电层112。在一些实施例中,介电层112是由可使用光刻掩模(lithography mask)进行图案化的聚合物形成,所述聚合物可为例如pbo、聚酰亚胺、bcb等感光性材料。在其他实施例中,介电层112是由以下材料形成:氮化物,例如氮化硅;氧化物,例如氧化硅、psg、bsg、bpsg;或类似物。介电层112可通过旋转涂布、叠层、cvd、类似工艺或其组合来形成。接着将介电层112图案化以形成暴露出金属化图案110的部分的开口114。所述图案化可通过可接受的工艺来形成,例如当介电层112是感光性材料时通过将介电层112暴露于光来形成,或者通过使用例如各向异性刻蚀进行刻蚀来形成。如果介电层112为感光性材料,则可在曝光之后对介电层112进行显影。

34.图3示出具有单个金属化图案110的重布线结构106用于说明性目的。在一些实施例中,背侧重布线结构106可包括任何数量的介电层及金属化图案。如果将形成更多介电层及金属化图案,则可重复以上论述的步骤及工艺。金属化图案可包括一个或多个导电元件,例如导电线及导通孔。导电元件可在金属化图案形成期间通过在下伏介电层的表面之上及下伏介电层的开口中形成晶种层及金属化图案的导电材料来形成,从而对各种导电线进行内连及电耦合。

35.在图4中,在开口114中形成延伸远离背侧重布线结构106的最顶部介电层(例如,介电层112)的穿孔116。作为形成穿孔116的实例,在背侧重布线结构106之上(例如,在介电层112及金属化图案110的被开口114暴露出的部分上)形成晶种层(未示出)。在一些实施例中,晶种层为金属层,其可为单一层或包括由不同材料形成的多个子层的复合层。在特定实施例中,晶种层包括钛层及位于所述钛层之上的铜层。晶种层可使用例如pvd等来形成。在晶种层上形成光刻胶并将其图案化。光刻胶可通过旋转涂布等来形成且可被暴露于光以进行图案化。光刻胶的图案对应于导通孔。所述图案化形成穿过光刻胶的开口以暴露出晶种层。在光刻胶的开口中及晶种层的被暴露的部分上形成导电材料。所述导电材料可通过例如电镀或无电镀覆等镀覆来形成。导电材料可包括金属,如铜、钛、钨、铝等。移除光刻胶以及晶种层的上面未形成导电材料的部分。光刻胶可通过可接受的灰化工艺或剥除工艺来移除,例如使用氧等离子体等。一旦光刻胶被移除,便例如通过使用可接受的刻蚀工艺(例如通过湿法刻蚀或干法刻蚀)来移除晶种层的被暴露的部分。晶种层的剩余部分及导电材料形成穿孔116。

36.在图5中,通过粘合剂118将集成电路管芯50(例如,第一集成电路管芯50a及第二集成电路管芯50b)粘合到介电层112。期望类型及数量的集成电路管芯50粘合在封装区100a及100b中的每一者中。在所示实施例中,多个集成电路管芯50彼此相邻粘合,包括在第一封装区100a及第二封装区100b中的每一者中的第一集成电路管芯50a及第二集成电路管芯50b。第一集成电路管芯50a可为逻辑装置,例如系统芯片(soc)、中央处理单元(cpu)、图形处理单元(gpu)、微控制器等。第二集成电路管芯50b可为存储器装置,例如动态随机存取存储器(dram)管芯、静态随机存取存储器(sram)管芯、混合存储器立方体(hmc)模块、高带宽存储器(hbm)模块等。在一些实施例中,集成电路管芯50a及50b可为相同类型的管芯,例如soc管芯。第一集成电路管芯50a及第二集成电路管芯50b可在相同技术节点的工艺中形

成,或者可在不同技术节点的工艺中形成。例如,第一集成电路管芯50a可为比第二集成电路管芯50b更先进的工艺节点。集成电路管芯50a及50b可具有不同的大小(例如,不同的高度和/或表面积),或者可具有相同的大小(例如,相同的高度和/或表面积)。第一封装区100a及第二封装区100b中可用于穿孔116的空间可能受到限制,尤其是当集成电路管芯50包括例如soc等具有大覆盖面积的装置时。当第一封装区100a及第二封装区100b具有可用于穿孔116的受限空间时,背侧重布线结构106的使用允许改进的内连线布置。在一些实施例中,相邻集成电路管芯50之间的空间介于约60μm到约100μm的范围内。

37.粘合剂118位于集成电路管芯50的背侧上并将集成电路管芯50粘合到背侧重布线结构106(例如粘合到介电层112)。粘合剂118可为任何合适的粘合剂、环氧树脂、管芯贴合膜(die attach film,daf)等。粘合剂118可被施加到集成电路管芯50的背侧,如果没有利用背侧重布线结构106,则可施加到载体衬底102的表面之上,或者如果适用,则可施加到背侧重布线结构106的上表面。例如,在单体化以分离集成电路管芯50之前,粘合剂118可被施加到集成电路管芯50的背侧。

38.在图6中,在各种组件上及各种组件周围形成包封体(encapsulant)120。在形成之后,包封体120包封穿孔116及集成电路管芯50。包封体120可为模制化合物、环氧树脂等。包封体120可通过压缩模制、转移模塑等施加,且可形成在载体衬底102之上,使得穿孔116和/或集成电路管芯50被掩埋或覆盖。包封体120进一步形成在集成电路管芯50之间的间隙区中。包封体120可以液体或半液体形式施加,且然后固化。

39.在图7中,在包封体120上执行平坦化工艺,以暴露出穿孔116及管芯连接件66。平坦化工艺还可移除穿孔116、介电层68和/或管芯连接件66的材料,直到管芯连接件66及穿孔116被暴露出。在平坦化工艺之后在工艺变化内,穿孔116、管芯连接件66、介电层68及包封体120的顶表面实质上共面(coplanar)。平坦化工艺可为例如化学机械抛光(chemical

‑

mechanical polish,cmp)、研磨工艺等。在一些实施例中,例如如果已暴露出穿孔116和/或管芯连接件66,则可省略所述平坦化。

40.图8示出根据一些实施例的图7的区500的详细视图,其示出包封体120的顶表面中的模制凹坑72的特写视图。在其中平坦化工艺是研磨工艺的一些实施例中,包封体120的顶表面中的模制凹坑72可通过研磨工艺来形成。模制凹坑72可具有介于约15μm到约25μm范围内的宽度w1以及在包封体120的顶表面下方大于约10μm的深度d1。模制凹坑72可在随后形成的重布线层(redistribution layer,rdl)中诱发缺陷,这些缺陷可通过引起例如由于rdl桥接导致的rdl走线断裂等问题来降低生产良率。如下文关于图14a及图14b所述,由聚合物材料形成的前侧重布线结构122可高效地填充模制凹坑72,并降低rdl桥接率(bridge rate),例如降低到约0%的桥接率。

41.在图9到图18中,在包封体120、穿孔116及集成电路管芯50之上形成前侧重布线结构122(参见图17)。前侧重布线结构122包括介电层124、128、132及136;以及金属化图案126、130及134。金属化图案也可称为重布线层或重布线走线。示出前侧重布线结构122作为具有三层金属化图案的实例。可在前侧重布线结构122中形成更多或更少的介电层及金属化图案,例如两个到五个介电层及金属化图案。如果将形成更少的介电层及金属化图案,则可省略以下论述的步骤及工艺。如果将形成更多的介电层及金属化图案,则可重复以下论述的步骤及工艺。

42.现在返回到图9,介电层124形成在包封体120、穿孔116及管芯连接件66上。在一些实施例中,介电层124可由包含溶剂、聚合物前体、交联剂及感光剂的聚合物材料形成。混合物还可包含添加剂。

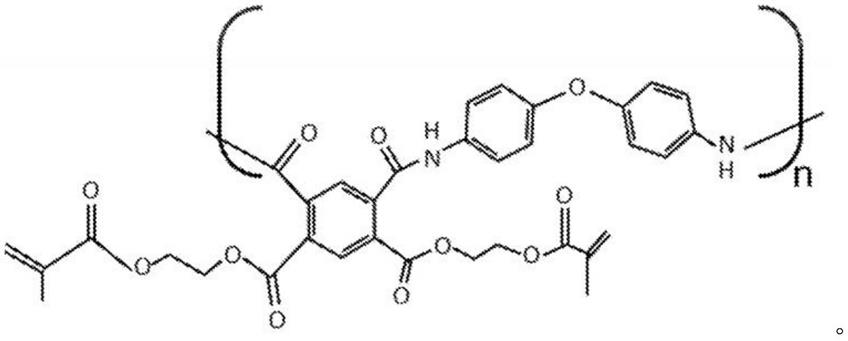

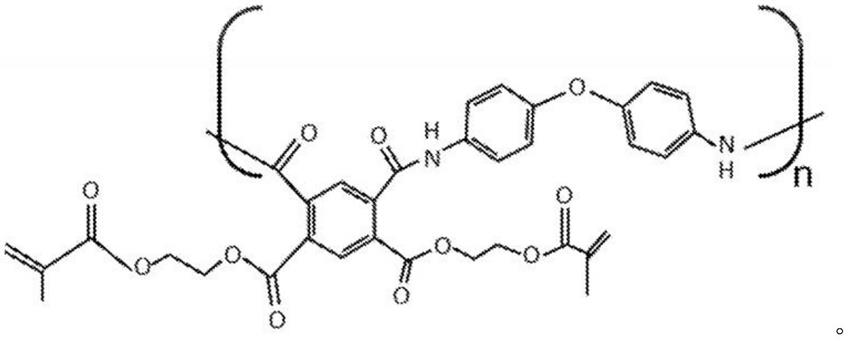

43.在其中对组合物使用低温固化聚酰亚胺的一些实施例中,聚合物材料可包括聚合物前体(例如聚酰胺酸酯)以及放置到溶剂中的感光剂、交联剂及添加剂。在实施例中,聚酰胺酸酯可包含由以下化学式的单体构成的聚合物:

[0044][0045]

此外,尽管聚酰胺酸酯可为如上所述的聚酰亚胺前体的实施例中的一者,但聚酰亚胺前体并不旨在受限于本文所述的具体实例。而是,可利用任何合适的聚酰亚胺前体,且所有此种聚酰亚胺前体均旨在包含于实施例的范围内。例如,聚合物材料可包含约25重量%至35重量%的聚合物前体。

[0046]

在一些实施例中,溶剂包括有机溶剂,其可用于混合、运输及分散聚合物材料的剩余组分。因此,在一些实施例中,有机溶剂可包括γ

‑

丁内酯(gamma

‑

butyrolactone,gbl)、n

‑

甲基

‑2‑

吡咯烷酮(n

‑

methyl

‑2‑

pyrrolidone,nmp)或二甲基乙酰胺(dimethylacetamide,dmac)。然而,可利用任何合适的有机溶剂。

[0047]

在另外的实施例中,另外,溶剂可不仅包括如上所述的有机溶剂,而且还可包括第二溶剂,以实现聚合物前体的良好溶解度。在此种实施例中,溶剂不仅可包括γ

‑

丁内酯(gbl),而且还可包括第二有机溶剂,例如二甲基亚砜(dimethyl sulfoxide,dmso)、乳酸乙酯(ethyl lactate,el)等。然而,任何合适的有机溶剂可用于第二有机溶剂。

[0048]

在一些实施例中,聚合物材料包含约40重量%到约50重量%的gbl。使用约40重量%到约50重量%的gbl可用于实现与聚合物前体的良好溶解度。使用小于约40重量%的gbl可能是不利的,因为其可能导致沉淀。使用超过约50重量%的gbl可能是不利的,因为聚合物前体可能太低,这可能导致随后形成过薄的膜厚度。

[0049]

在一些实施例中,聚合物材料包含约5重量%到约15重量%的dmso。使用约5重量%到约15重量%的dmso可用于实现与聚合物前体的良好溶解度。使用小于约5重量%的dmso可能是不利的,因为其可能导致沉淀。使用超过约15重量%的dmso可能是不利的,因为聚合物前体可能太低,这可能导致随后形成过薄的膜厚度。

[0050]

使用gbl与dmso的混合物作为溶剂可提供优势。gbl与dmso的混合物可被称为绿色混合溶剂,因为其对环境友好。使用gbl及dmso可减少环境污染,因为gbl及dmso比例如n

‑

甲基

‑2‑

吡咯烷酮或n

‑

甲基吡咯烷酮(nmp)、n,n

‑

二甲基甲酰胺或二甲基甲酰胺

(dimethylformamide,dmf)等其他溶剂毒性小。

[0051]

交联剂形成将一个聚合物链键结至另一聚合物链的键。所得组合物可具有比其原本不交联时大的刚性。在一些实施例中,交联剂可包括任何合适的交联剂,例如二甲基丙烯酸四乙二醇酯(丙烯酸酯)。在其他实施例中,混合物中不使用交联剂来形成聚合物材料,并且聚合物材料不包含交联剂。

[0052]

增加交联剂的浓度可有益于降低聚合物材料的固化温度。例如,包含约2重量%到约10重量%的交联剂的聚合物材料可允许更好的光刻图案化。包含小于约2重量%的交联剂的聚合物材料可导致更差的光刻图案化。包含大于约10重量%的交联剂的聚合物材料可导致更差的光刻图案化。

[0053]

还被称为光活化剂或光活化组分(photoactive component,pac)的感光剂可为光活化组分,例如光酸产生剂、光碱产生剂、自由基产生剂等,且感光剂可为正作用(positive

‑

acting)的或负作用(negative

‑

acting)的。在一些实施例中,感光剂包括4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑。使用4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑作为感光剂可用于提高临界尺寸的分辨率及减少显影时间。聚合物材料可包含约0.1重量%到约2.5重量%的4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑,这可有益于实现显影时间的减少及rdl特征的更高分辨率。包含少于约0.1重量%的4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑的聚合物材料可能是不利的,因为这会导致更长的显影时间及更差的rdl特征分辨率。包含大于约2.5重量%的4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑的聚合物材料可能是不利的,因为这会导致更长的显影时间及更差的rdl特征分辨率。

[0054]

图10a示出聚合物材料的转换百分比与曝光能量的关系图。使用4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑作为感光剂可增加聚合物材料相对于曝光能量的转换百分比,使得利用介于约90mj到约110mj范围内的曝光能量可实现介于约33%到约35%范围内的转换百分比。

[0055]

图10b示出可如何实现相对于曝光能量的增强的感光性。例如,通过向由4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑化学式的圆圈部分所示的感光剂化学式中添加硫代苯基,在硫代苯基的曝光期间产生的电子将替代在别处反应并降低总体转换率的电子而与电子反应。如下所述,在相对较低的曝光能量下得到的较高的感光性可允许用低温等离子体电离(low temperature plasma ionization,ltpi)显影程序来生产较高分辨率的rdl特征。

[0056]

除感光剂之外,混合物还可包含添加剂。添加剂有助于降低固化所使用的温度。特别地,添加剂可用于增大混合物的自由体积。添加剂的高极性和/或高位阻(steric hindrance)可用于克服在曝光期间及曝光之后形成的聚合物的极性(例如通过降低偶极矩)。因此,如下所述,可使用较低的曝光能量。聚合物的反应性部分两端的极性减小会使得分子的各分支能够集合在一起以形成环,且因此在较低温度下固化期间改善环化。添加剂可用作反应的催化剂,且因此在固化之前及固化之后保持与聚合物分离,但固化后的最终聚合物层或介电层可包含原始添加剂中的一些或全部。

[0057]

添加剂可包含适合用于增大聚合物材料或聚合物混合物的自由体积的任何分子。为增大混合物的自由体积,可选择添加剂,且所述添加剂可具有与选定感光剂(4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑)相似的结构。例如,在一些实施例中,添加剂包括由以下化学式阐述的化学物质中的一者或多者:

[0058][0059]

其中r包括ch3或c6h

13

,其中a由以下化学式中的一者来阐述:

[0060][0061][0062]

例如,在其中r是ch3的实施例中,添加剂可具有以下化学式:

[0063][0064]

在其中r是c6h

13

的另一实施例中,添加剂可具有以下化学式:

[0065][0066]

在另一实例中,在其中r是ch3的实施例中,添加剂可具有以下化学式:

[0067][0068]

在其中r是c6h

13

的另一实施例中,添加剂可具有以下化学式:

[0069][0070]

在另一实例中,在其中r是ch3的实施例中,添加剂可具有以下化学式:

[0071][0072]

在其中r是c6h

13

的另一实施例中,添加剂可具有以下化学式:

[0073][0074]

在另一实例中,在其中r是ch3的实施例中,添加剂可具有以下化学式:

[0075][0076]

在其中r是c6h

13

的另一实施例中,添加剂可具有以下化学式:

[0077][0078]

在另一实例中,在其中r是ch3的实施例中,添加剂可具有以下化学式:

[0079][0080]

在其中r是c6h

13

的另一实施例中,添加剂可具有以下化学式:

[0081][0082]

在另一实例中,在其中r是ch3的实施例中,添加剂可具有以下化学式:

[0083][0084]

在其中r是c6h

13

的另一实施例中,添加剂可具有以下化学式:

[0085][0086]

在另一实例中,在其中r是ch3的实施例中,添加剂可具有以下化学式:

[0087][0088]

在其中r是c6h

13

的另一实施例中,添加剂可具有以下化学式:

[0089][0090]

在另一实例中,在其中r是ch3的实施例中,添加剂可具有以下化学式:

[0091][0092]

在其中r是c6h

13

的另一实施例中,添加剂可具有以下化学式:

[0093][0094]

在另一实例中,在其中r是ch3的实施例中,添加剂可具有以下化学式:

[0095][0096]

在其中r是c6h

13

的另一实施例中,添加剂可具有以下化学式:

[0097][0098]

在其他实施例中,添加剂包括以下化学物质中的一或多者:2

‑

苯甲基

‑2‑

(二甲氨基)

‑1‑

[4

‑

(吗啉基)苯基]

‑1‑

丁酮、(2

‑

二甲氨基

‑2‑

(4

‑

甲基苯甲基)

‑1‑

(4

‑

吗啉

‑4‑

基苯基)丁烷

‑1‑

酮、1

‑

[4

‑

(苯硫基)苯基]

‑

1,2辛烷二酮

‑

2(邻苯甲酰基肟)、1

‑

[9[乙基

‑6‑

(2

‑

甲基苯甲酰基)

‑

9h

‑

咔唑

‑3‑

基]乙酮邻乙酰基肟或者由以下化学式阐述的化学物质中的一者:

[0099]

[0100][0101]

由正上方的化学式阐述的化学物质也可被称为4,4'

‑

双(二乙氨基)二苯甲酮。

[0102]

然而,如所属领域中的一般技术人员将认识到,本文所列化学化合物仅旨在作为添加剂的所示实例,而并不旨在将实施限制于仅具体阐述的那些添加剂。而是,可利用任何合适的添加剂,且所有此种添加剂均旨在包含在本发明实施例的范围内。在实施例中,聚合物材料包含约5重量%的添加剂。

[0103]

一旦准备好,可通过最初将聚合物材料施加到包封体120、集成电路管芯50及穿孔116上来利用介电层124。介电层124可被施加成使得介电层124涂布包封体120的上部被暴露的表面、集成电路管芯50及穿孔116,且可使用例如旋转涂布工艺、浸涂法、气刀涂布法、帘涂法、丝

‑

杆涂布法、凹版涂布法、叠层法、挤压涂布法、这些的组合等工艺来施加。介电层124可被放置到介于约2μm到约10μm范围内的厚度。在一些实施例中,模制凹坑72被介电层124填充,从而形成如下文关于图13所述的介电特征74。

[0104]

一旦被施加之后,便可对介电层124进行烘烤以在曝光(以下进一步阐述)之前固化及干燥介电层124。固化及干燥介电层124会移除溶剂组分而留下聚酰胺酸酯、感光剂、交联剂及任何其他选定添加剂。在实施例中,预烘烤可在适合蒸发溶剂的温度、例如在介于约40℃与150℃范围内的温度下执行。预烘烤被执行足以固化及干燥介电层124的时间,例如介于约10秒到约5分钟的范围内。

[0105]

在图11中,一旦放置介电层124,便通过例如对介电层124的材料进行曝光及显影来将介电层124图案化以形成暴露出穿孔116及管芯连接件66的部分的开口125。

[0106]

在一些实施例中,能量源向介电层124供应能量(例如光)以引发感光剂的反应,所述感光剂继而与聚酰胺酸酯反应以使介电层124的能量所撞击的那些部分发生化学改变。在实施例中,所述能量可为电磁辐射(例如g

‑

射线(具有约436nm的波长)、i

‑

射线(具有约365nm的波长))、紫外辐射、远紫外辐射、x

‑

射线、电子束等。能量源可为电磁辐射源,且可为krf准分子激光(具有248nm的波长)、arf准分子激光(具有193nm的波长)、f2准分子激光(具有157nm的波长)等,但也可利用任何其他合适的能量源,例如汞蒸气灯、氙灯、碳弧灯等。

[0107]

图案化掩模位于能量源与介电层124之间以在能量实际撞击在介电层124上之前阻挡能量的部分以形成图案化能量。在实施例中,图案化掩模可包括一系列层(例如,衬底、吸收层、抗反射涂层、屏蔽层等)以反射、吸收或以其他方式阻挡能量的部分到达介电层124的不期望被照射的那些部分。可通过以期望的照射形状形成穿过图案化掩模的开口而在图案化掩模中形成期望的图案。

[0108]

在一些实施例中,介电层124被放置在支撑板上。一旦图案已对准至介电层124,能量源便产生期望的能量(例如,光),所述期望的能量穿过图案化掩模而一路到达介电层124。撞击在介电层124的部分上的图案化能量引发介电层124内的感光剂的反应。感光剂吸收图案化能量后的化学反应产物(例如,酸/碱/自由基)接着与聚酰胺酸酯反应,从而使介电层124在通过图案化掩模被照射的那些部分中发生化学改变。如上文关于图10a及图10b所述,通过使用4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑作为感光剂,在曝光能量小于约130mj(例如介于约90mj到约110mj的范围内)的情况下,可实现介于约33%到约35%范围内的转换百分比,这可能是由于在感光剂化学式中具有额外电子的硫代苯基。在相对较低的曝光能量下得到的较高的感光性可允许生产较高分辨率的rdl特征。

[0109]

在一些实施例中,曝光可以介于约2μm与约200μm范围内(例如介于约3μm与约5μm范围内)的底部临界尺寸(bottom critical dimension,bcd)进行。此外,曝光宽容度(exposure latitude,el)可大于约20%或大于约50%,聚焦深度(depth of focus,dof)可介于约8μm与约30μm的范围内。曝光能量可介于约80mj与约300mj的范围内,且聚焦可介于约6μm与约30μm的范围内。

[0110]

在已对介电层124进行曝光之后,可使用第一曝光后烘烤(post

‑

exposure bake,peb)来帮助在曝光期间因能量撞击在感光剂上而产生的酸/碱/自由基的产生、分散及反应。此种帮助有助于形成或增强化学反应,所述化学反应会在被能量撞击的那些区与未被能量撞击的那些区之间产生化学差异及不同极性。这些化学差异也造成被能量撞击的区与未被能量撞击的区之间的溶解度差异。在一些实施例中,介电层124的温度可在介于约70℃与约130℃范围内的时间段内增加到介于约70℃到约130℃的范围内。

[0111]

一旦介电层124已被曝光及烘烤,便可使用显影剂将介电层124显影。在其中介电层124为低温固化聚酰亚胺的实施例中,第一显影剂可为可用来移除介电层124的未曝光于能量且因此保持其原始溶解度的那些部分的例如有机溶剂或临界流体等负型显影剂。可利用的材料的具体实例包括烃溶剂、醇溶剂、醚溶剂、酯溶剂、临界流体、这些的组合等。可用于负型溶剂的材料的具体实例包括环戊酮(a515)、己烷、庚烷、辛烷、甲苯、二甲苯、二氯甲烷、氯仿、四氯化碳、三氯乙烯、甲醇、乙醇、丙醇、丁醇、临界二氧化碳、二乙醚、二丙醚、二丁醚、乙基乙烯醚、二恶烷、环氧丙烷、四氢呋喃、溶纤剂、甲基溶纤剂、丁基溶纤剂、甲基卡必醇、二乙二醇单乙醚、丙酮、甲乙酮、甲基异丁基酮、异佛尔酮、环己酮、乙酸甲酯、乙酸乙酯、乙酸丙酯、乙酸丁酯、吡啶、甲酰胺、n,n

‑

二甲基甲酰胺等。

[0112]

可使用例如旋转涂布工艺对介电层124施加第一显影剂。在此工艺中,在介电层124旋转的同时自介电层124上方对介电层124施加第一显影剂。在实施例中,第一显影剂的温度可介于约20℃与约40℃的范围内,且显影可持续达介于约12秒到约40秒的范围内。

[0113]

然而,尽管本文所述的旋转涂布法为一种适合于在曝光之后对介电层124进行显影的方法,但其旨在为说明性的,而并不旨在限制实施例。相反,可使用用于显影的任何合适的方法,包括浸渍工艺、混拌工艺(puddle process)、喷涂工艺、这些的组合等。所有此种显影工艺均旨在包含在实施例的范围内。

[0114]

一旦介电层124已显影之后,便可冲洗介电层124。在实施例中,可使用冲洗液体(例如丙二醇单甲醚乙酸酯)来冲洗介电层124,但可使用任何合适的冲洗溶液,例如水。

[0115]

在显影后,可利用显影后烘烤工艺来帮助在显影工艺之后使介电层124聚合及稳

定。在实施例中,显影后烘烤工艺可在约80℃与约200℃之间、或约80℃与约170℃之间的温度下执行约60秒与约300秒之间的时间。

[0116]

在显影后烘烤及rdl表面处理之后,可使介电层124固化。在其中介电层124包含低温固化聚酰亚胺的实施例中,固化工艺可在低于约230℃的低温(例如介于约170℃与约230℃范围内的温度)下执行约1小时与约2小时之间的时间。温度可始于约23℃,且以约0.5℃到约10℃的速率(例如以约4.5℃的速率)升高。系统以约0.5℃/分钟到约10℃/分钟(例如约1℃/分钟)的速率冷却。在特定实施例中,固化工艺可在约170℃的温度下执行约1小时,在约180℃的温度下执行约1小时的时间、或在约160℃的温度下执行约2小时的时间。然而,可利用任何合适的温度及时间。

[0117]

在其中介电层124的聚合物材料在约230℃下固化的一些实施例中,在固化工艺之后,介电层124的聚合物材料可具有约85%的收缩率、介于约217℃到约219℃范围内的热机械分析玻璃转变(thermomechanical analysis glass transition,tma

‑

tg)温度、约50ppm/℃的线性热膨胀系数(cte1)、介于约184mpa到约190mpa范围内的拉伸强度、约3gpa的杨氏模量以及介于约72%到约79%范围内的伸长率。介电层124可收缩到介于约5μm到约12μm范围内的厚度。

[0118]

在其中介电层124的聚合物材料在约170℃下固化的一些实施例中,在固化工艺之后,介电层124的聚合物材料可具有约85%的收缩率、约210℃的热机械分析玻璃转变(tma

‑

tg)温度、介于约50ppm/℃到51ppm/℃范围内的线性热膨胀系数(cte1)、介于约175mpa到约190mpa范围内的拉伸强度、约3gpa的杨氏模量以及介于约67%到约79%范围内的伸长率。介电层124可收缩到介于约5μm到约12μm范围内的厚度。

[0119]

图12a及图12b提供质量分析结果,其示出将添加剂的实施例与聚合物材料的实施例包含在一起的结果。在一些实施例中,溶剂包括gbl及dmso,且添加剂包括化学结构700:

[0120][0121]

在包含gbl、dmso及添加剂的聚合物材料固化后,聚合物材料可包含来自dmso的以下化学结构710:

[0122][0123]

且聚合物材料还可包含来自gbl的以下化学结构720:

[0124][0125]

图12a示出根据这些实施例的上述化学结构700、710及720作为标记峰存在于聚合物材料的核磁共振波谱图中。

[0126]

在一些实施例中,溶剂包括dmso,且添加剂包括化学结构700。图12b示出根据这些实施例的上述化学结构700及710作为标记峰存在于聚合物材料的核磁共振波谱图中。

[0127]

图13示出根据一些实施例的图12a及图12b的区500的详细视图,其示出介电层124的介电特征74的特写视图。在一些实施例中,模制凹坑72被介电层124填充,从而形成介电特征74。固化后,介电特征74的顶表面中的凹槽76可具有小于约1.5μm的深度d2。深度d2对宽度w1的比率可小于约0.16,例如介于约0.006到约0.080的范围内。深度d2对深度d1的比率可介于约0.05到约0.15的范围内。如上文关于图9所述形成的介电层124的聚合物材料可填充模制凹坑72,使得介电层124中的剩余凹槽76具有小于约1.5μm的深度。这可将前侧重布线结构122的底层中的桥接缺陷率降低到约0%的桥接率,这可降低例如在随后形成的金属化图案126中的来自断裂rdl走线的良率损失。

[0128]

在图14a中,然后形成金属化图案126。金属化图案126包括沿着介电层124的主表面延伸且延伸穿过介电层124的导电元件,以实体耦合及电耦合到穿孔116及集成电路管芯50。作为形成金属化图案126的实例,在介电层124之上及延伸穿过介电层124的开口中形成晶种层。在一些实施例中,晶种层为金属层,其可为单一层或包括由不同材料形成的多个子层的复合层。在一些实施例中,晶种层包括钛层及位于所述钛层之上的铜层。晶种层可使用例如pvd等来形成。接着在晶种层上形成光刻胶并将其图案化。光刻胶可通过旋转涂布等来形成且可被暴露于光以进行图案化。光刻胶的图案对应于金属化图案126。所述图案化形成穿过光刻胶的开口以暴露出晶种层。然后在光刻胶的开口中及晶种层的被暴露的部分上形成导电材料。所述导电材料可通过例如电镀或无电镀覆等镀覆来形成。导电材料可包括金属,如铜、钛、钨、铝等。导电材料与晶种层的下伏部分的组合形成金属化图案126,金属化图案126包含形成在开口125中的导通孔127。移除光刻胶以及晶种层的上面未形成导电材料的部分。光刻胶可通过可接受的灰化工艺或剥除工艺来移除,例如使用氧等离子体等。一旦光刻胶被移除,便例如通过使用可接受的刻蚀工艺(例如通过湿法刻蚀或干法刻蚀)来移除晶种层的被暴露的部分。

[0129]

图14b示出根据一些实施例的图14a的区600的详细视图,其示出延伸穿过介电层124的导通孔127的特写视图。尽管图14b示出接触穿孔116的顶表面的导通孔127,但导通孔127也可被形成为接触管芯连接件66的顶表面。介电层124的聚合物材料的配方可允许形成金属化图案126的更高分辨率的特征。例如,导通孔127可具有介于约4.7μm到约7.0μm范围内的顶部宽度w2、介于约2.5μm到约4.0μm范围内的底部宽度w3以及在导通孔127的侧壁与介电层124的底表面之间测量的介于约70

°

到约83

°

范围内的通孔角度α。

[0130]

在图15中,在金属化图案126及介电层124上沉积介电层128。介电层128可以与介

电层124类似的方式形成,且可由与介电层124类似的材料形成。然而,可使用任何合适的方法及材料。然后对介电层128进行图案化。所述图案化会形成暴露出金属化图案126的部分的开口。所述图案化可通过可接受的工艺进行,例如当介电层126是感光性材料时,以与上文关于图12a及图12b阐述的介电层124的图案化类似的方式,通过将介电层126曝光及显影来进行。然而,可利用任何合适的图案化工艺。

[0131]

然后形成金属化图案130。金属化图案130包括位于介电层128的主表面上并沿其延伸的部分。金属化图案130还包括延伸穿过介电层128以实体耦合及电耦合金属化图案126的部分。金属化图案130可以与金属化图案126类似的方式且由与金属化图案126类似的材料形成。在一些实施例中,金属化图案130具有与金属化图案126不同的大小。例如,金属化图案130的导电线和/或导通孔可比金属化图案126的导电线和/或导通孔更宽或更厚。此外,金属化图案130可被形成为比金属化图案126更大的节距。

[0132]

在图16中,在金属化图案130及介电层128上沉积介电层132。介电层132可以与介电层124类似的方式形成,且可由与介电层124类似的材料形成。然而,可使用任何合适的方法及材料。

[0133]

然后形成金属化图案134。金属化图案134包括位于介电层132的主表面上并沿其延伸的部分。金属化图案134还包括延伸穿过介电层132以实体耦合及电耦合金属化图案130的部分。金属化图案134可以与金属化图案126类似的方式且由与金属化图案126类似的材料形成。金属化图案134是前侧重布线结构122的最顶部金属化图案。因此,前侧重布线结构122的所有中间金属化图案(例如,金属化图案126及130)均设置在金属化图案134与集成电路管芯50之间。在一些实施例中,金属化图案134具有与金属化图案126及130不同的大小。例如,金属化图案134的导电线和/或导通孔可比金属化图案126及130的导电线和/或导通孔更宽或更厚。此外,金属化图案134可被形成为比金属化图案130更大的节距。

[0134]

在图17中,在金属化图案134及介电层132上沉积介电层136。介电层136可以与介电层124类似的方式形成,且可由与介电层124相同的材料形成。然而,可使用任何合适的方法及材料。介电层136是前侧重布线结构122的最顶部介电层。因此,前侧重布线结构122的所有金属化图案(例如,金属化图案126、130及134)均设置在介电层136与集成电路管芯50之间。因此,前侧重布线结构122的所有中间介电层(例如,介电层124、128、132)均设置在介电层136与集成电路管芯50之间。

[0135]

在图18中,形成用于与前侧重布线结构122外部连接的凸块下金属(under

‑

bump metallurgy,ubm)138。ubm 138具有位于介电层136的主表面上并沿其延伸的凸块部分,并且具有延伸穿过介电层136以实体耦合及电耦合金属化图案134的通孔部分。结果,ubm 138电耦合到穿孔116及集成电路管芯50。ubm 138可由与金属化图案126相同的材料形成。在一些实施例中,ubm 138具有与金属化图案126、130及134不同的大小。

[0136]

在图19中,在ubm 138上形成导电连接件150。导电连接件150可为球栅阵列(ball grid array,bga)连接件、焊料球、金属柱、受控塌陷芯片连接(controlled collapse chip connection,c4)凸块、微凸块、无电镀镍钯浸金技术(electroless nickel

‑

electroless palladium

‑

immersion gold technique,enepig)形成的凸块等。导电连接件150可包含例如焊料、铜、铝、金、镍、银、钯、锡、类似材料或其组合等导电材料。在一些实施例中,导电连接件150通过利用蒸镀、电镀、印刷、焊料转移(solder transfer)、植球(ball placement)

初始地形成焊料层来形成。一旦已在结构上形成焊料层,则可执行回焊以便将所述材料造型成期望的凸块形状。在另一实施例中,导电连接件150包含通过溅镀(sputtering)、印刷、电镀、无电镀覆、cvd等形成的金属柱(例如铜柱)。所述金属柱可不含有焊料且具有实质上垂直的侧壁。在一些实施例中,在金属柱的顶部上形成金属顶盖层(metal cap layer)。金属顶盖层可包含镍、锡、锡

‑

铅、金、银、钯、铟、镍

‑

钯

‑

金、镍

‑

金、类似材料或其组合,且可通过镀覆工艺来形成。

[0137]

在图20中,执行载体衬底剥离(carrier substrate de

‑

bonding)以将载体衬底102从背侧重布线结构106(例如,介电层108)脱离(或“剥离”)。根据一些实施例,所述剥离包括将例如激光或紫外光等光投射在释放层104上以使得释放层104在光的热量下分解,且可移除载体衬底102。接着将所述结构翻转并放置在胶带(未示出)上。

[0138]

在图21中,形成延伸穿过介电层108的导电连接件152以接触金属化图案110。穿过介电层108形成开口以暴露出金属化图案110的部分。所述开口可例如使用激光钻孔(laser drilling)、刻蚀等来形成。导电连接件152形成在开口中。在一些实施例中,导电连接件152包含助焊剂,且在助焊剂浸渍工艺中形成。在一些实施例中,导电连接件152包含导电膏(例如焊料膏、银膏等),且在印刷工艺中被分配。在一些实施例中,导电连接件152以与导电连接件150类似的方式形成,且可由与导电连接件150类似的材料形成。

[0139]

图22及图23示出根据一些实施例的装置堆叠的形成及实现。装置堆叠由在第一封装组件100中形成的集成电路封装形成。装置堆叠也可被称为叠层封装(pop)或晶片上封装(package

‑

on

‑

wafer,pow)结构。

[0140]

在图22中,将第二封装组件200耦合到第一封装组件100。第二封装组件200中的一者在封装区100a及100b中的每一者中耦合,以在第一封装组件100的每一区中形成集成电路装置堆叠。

[0141]

第二封装组件200包括例如衬底202及耦合到衬底202的一个或多个堆叠式管芯210(例如,210a及210b)。尽管示出一组堆叠式管芯210(210a及210b),但在其他实施例中,多个堆叠式管芯210(每一者具有一个或多个堆叠式管芯)可并排设置成耦合到衬底202的相同表面。衬底202可由例如硅、锗、金刚石等半导体材料制成。在一些实施例中,也可使用化合物材料,例如硅锗、碳化硅、镓砷、砷化铟、磷化铟、碳化硅锗、磷化镓砷、磷化镓铟、这些的组合等。另外,衬底202可为绝缘体上硅(silicon

‑

on

‑

insulator,soi)衬底。一般来说,soi衬底包括一层半导体材料,例如外延硅、锗、硅锗、soi、绝缘体上硅锗(silicon germanium on insulator,sgoi)或其组合。在一个替代实施例中,衬底202是基于绝缘芯,例如玻璃纤维强化树脂芯(fiberglass reinforced resin core)。一个示例性芯材料为玻璃纤维树脂(例如,fr4)。所述芯材料的替代形式包括双马来酰亚胺

‑

三嗪(bismaleimide

‑

triazine,bt)树脂,或作为另一选择,包括其他印刷电路板(pcb)材料或膜。可对衬底202使用例如味之素增层膜(ajinomoto build

‑

up film,abf)等增层膜或其他叠层体。

[0142]

衬底202可包括有源装置及无源装置(未示出)。可使用例如晶体管、电容器、电阻器、这些的组合等各种各样的装置来产生用于第二封装组件200的设计的结构性要求及功能性要求。可使用任何合适的方法来形成所述装置。

[0143]

衬底202还可包括金属化层(未示出)及导通孔208。金属化层可形成在有源装置及无源装置之上且被设计成连接各种装置以形成功能性电路系统。金属化层可由交替的介电

材料(例如,低介电常数介电材料)层与导电材料(例如,铜)层以及对导电材料层进行内连的通孔形成,并且可通过任何合适的工艺(例如,沉积、镶嵌、双镶嵌等)来形成。在一些实施例中,衬底202实质上不具有有源装置及无源装置。

[0144]

衬底202可具有位于衬底202的第一侧上以耦合到堆叠式管芯210的接合焊盘204以及位于衬底202的第二侧上以耦合到导电连接件152的接合焊盘206,所述第二侧与衬底202的第一侧相对。在一些实施例中,接合焊盘204及206是通过向衬底202的第一侧及第二侧上的介电层(未示出)中形成凹槽(未示出)而形成。所述凹槽可被形成为允许接合焊盘204及206被嵌入到所述介电层中。在其他实施例中,由于接合焊盘204及206可形成在介电层上,因而所述凹槽被省略。在一些实施例中,接合焊盘204及206包括由铜、钛、镍、金、钯、类似材料或其组合制成的薄晶种层(未示出)。可在薄晶种层之上沉积接合焊盘204及206的导电材料。所述导电材料可通过电化学镀覆工艺、无电镀覆工艺、cvd、原子层沉积(atomic layer deposition,ald)、pvd、类似工艺或其组合来形成。在实施例中,接合焊盘204及206的导电材料是铜、钨、铝、银、金、类似材料或其组合。

[0145]

在一些实施例中,接合焊盘204及接合焊盘206为包括三个导电材料层的ubm,所述三个导电材料层例如为钛层、铜层及镍层。可利用材料及层的其他布置(例如铬/铬

‑

铜合金/铜/金的布置、钛/钛钨/铜的布置或铜/镍/金的布置)来形成接合焊盘204及206。可用于接合焊盘204及206的任何合适的材料或材料层完全旨在包括在当前申请的范围内。在一些实施例中,导通孔208延伸穿过衬底202且将接合焊盘204中的至少一者耦合到接合焊盘206中的至少一者。

[0146]

在所示实施例中,堆叠式管芯210通过丝焊212耦合到衬底202,然而,可使用其他连接,例如导电凸块。在实施例中,堆叠式管芯210是堆叠式存储器管芯。例如,堆叠式管芯210可包括存储器管芯,例如低功率(low

‑

power,lp)双倍数据速率(double data rate,ddr)存储器模块,例如lpddr1、lpddr2、lpddr3、lpddr4或类似存储器模块。

[0147]

堆叠式管芯210及丝焊212可通过模制材料214来包封。模制材料214可例如使用压缩模制被模制在堆叠式管芯210及丝焊212上。在一些实施例中,模制材料214是模制化合物、聚合物、环氧树脂、氧化硅填充材料、类似材料或其组合。可执行固化工艺,以使对模制材料214进行固化;所述固化工艺可为热固化、紫外固化、类似固化或其组合。

[0148]

在一些实施例中,堆叠式管芯210及丝焊212被掩埋入模制材料214中,且在将模制材料214固化之后,执行平坦化步骤(例如研磨),以移除模制材料214的多余部分并为第二封装组件200提供实质上平的表面。

[0149]

在形成第二封装组件200之后,第二封装组件200通过导电连接件152、接合焊盘206及背侧重布线结构106的金属化图案机械接合及电接合到第一封装组件100。在一些实施例中,堆叠式管芯210可通过丝焊212、接合焊盘204及206、导通孔208、导电连接件152、背侧重布线结构106、穿孔116及前侧重布线结构122耦合到集成电路管芯50a及50b。

[0150]

在一些实施例中,在衬底202的与堆叠式管芯210相对的侧上形成阻焊剂(未示出)。导电连接件152可设置在阻焊剂中的开口中,以电耦合及机械耦合到衬底202中的导电特征(例如,接合焊盘206)。阻焊剂可用于保护衬底202的区域免受外部损坏。

[0151]

在一些实施例中,在导电连接件152被回焊之前,导电连接件152上形成有环氧树脂助焊剂(未示出),所述环氧树脂助焊剂的环氧树脂部分中的至少一些在将第二封装组件

200贴合到第一封装组件100之后剩余。

[0152]

在一些实施例中,在第一封装组件100与第二封装组件200之间形成环绕导电连接件152的底部填充胶(未示出)。底部填充胶可减小应力并保护由导电连接件152的回焊而产生的联接部。底部填充胶可在第二封装组件200被贴合之后通过毛细管流动工艺(capillary flow process)来形成,或可在第二封装组件200被贴合之前通过合适的沉积方法来形成。在其中形成环氧树脂助焊剂的实施例中,其可充当底部填充胶。

[0153]

在图23中,通过沿着例如第一封装区100a与第二封装区100b之间的切割道区锯切来执行单体化工艺。锯切将第一封装区100a与第二封装区100b单体化。所得的单体化装置堆叠来自第一封装区100a或第二封装区100b中的一者。在一些实施例中,在第二封装组件200耦合到第一封装组件100之后执行单体化工艺。在其他实施例(未示出)中,在第二封装组件200耦合到第一封装组件100之前,例如在载体衬底102被剥离且形成导电连接件152之后,执行单体化工艺。

[0154]

然后,可使用导电连接件150将每一单体化的第一封装组件100安装到封装衬底300。封装衬底300包括衬底芯302及位于衬底芯302之上的接合焊盘304。衬底芯302可由例如硅、锗、金刚石等半导体材料制成。作为另一选择,也可使用例如硅锗、碳化硅、镓砷、砷化铟、磷化铟、碳化硅锗、磷化镓砷、磷化镓铟、这些的组合等化合物材料。另外,衬底芯302可为soi衬底。一般来说,soi衬底包括例如外延硅、锗、硅锗、soi、sgoi、或其组合等半导体材料层。在一个替代实施例中,衬底芯302是基于绝缘芯,例如玻璃纤维强化树脂芯。一个示例性芯材料为玻璃纤维树脂(例如,fr4)。芯材料的替代形式包括双马来酰亚胺三嗪bt树脂,或作为另一选择,包括其他pcb材料或膜。可对衬底芯302使用例如abf等增层膜或其他叠层体。

[0155]

衬底芯302可包括有源装置及无源装置(未示出)。可使用例如晶体管、电容器、电阻器、这些的组合等各种各样的装置来产生用于装置堆叠的设计的结构性要求及功能性要求。可使用任何合适的方法来形成所述装置。

[0156]

衬底芯302还可包括金属化层及通孔(未示出),接合焊盘304实体耦合和/或电耦合到金属化层及通孔。金属化层可形成在有源装置及无源装置之上且被设计成连接各种装置以形成功能性电路系统。金属化层可由交替的介电材料(例如,低介电常数介电材料)层与导电材料(例如,铜)层以及对导电材料层进行内连的通孔形成,并且可通过任何合适的工艺(例如,沉积、镶嵌、双镶嵌等)来形成。在一些实施例中,衬底芯302实质上不具有有源装置及无源装置。

[0157]

在一些实施例中,导电连接件150被回焊以将第一封装组件100贴合到接合焊盘304。导电连接件150将封装衬底300(包括位于衬底芯302中的金属化层)电耦合和/或实体耦合到第一封装组件100。在一些实施例中,在衬底芯302上形成阻焊剂306。导电连接件150可设置在阻焊剂306中的开口中,以电耦合及机械耦合到接合焊盘304。阻焊剂306可用于保护衬底202的区域免受外部损坏。

[0158]

在导电连接件150被回焊之前,导电连接件150上可形成有环氧树脂助焊剂(未示出),所述环氧树脂助焊剂的环氧树脂部分中的至少一些在将第一封装组件100贴合到封装衬底300之后剩余。此剩余的环氧树脂部分可充当底部填充胶,以减小应力并保护由于对导电连接件150进行回焊而产生的联接部。在一些实施例中,可在第一封装组件100与封装衬

底300之间形成环绕导电连接件150的底部填充胶308。底部填充胶308可在第一封装组件100被贴合之后通过毛细管流动工艺而形成,或可在第一封装组件100被贴合之前通过合适的沉积方法而形成。

[0159]

在一些实施例中,无源装置(例如,表面安装装置(surface mount device,smd),未示出)也可贴合到第一封装组件100(例如,贴合到ubm 138)或封装衬底300(例如,贴合到接合焊盘304)。例如,无源装置可接合到第一封装组件100或封装衬底300的与导电连接件150相同的表面。无源装置可在将第一封装组件100安装在封装衬底300上之前贴合到封装组件100,或者可在将第一封装组件100安装在封装衬底300上之前或之后贴合到封装衬底300。

[0160]

第一封装组件100可在其他装置堆叠中实现。例如,示出pop结构,但第一封装组件100也可在倒装芯片球栅阵列(flip chip ball grid array,fcbga)封装中实现。在此种实施例中,第一封装组件100安装到例如封装衬底300等衬底,但省略第二封装组件200。相反,盖体或散热器可贴合到第一封装组件100。当省略第二封装组件200时,也可省略背侧重布线结构106及穿孔116。

[0161]

尽管聚合物材料形成及图案化工艺被阐述为形成及图案化介电层124的一个可能的实施例,但用于介电层124的聚合物材料形成及图案化工艺的实例旨在为说明性的,而不旨在进行限制。相反,聚合物材料形成及图案化工艺可用于形成和/或图案化的任何合适的介电层,例如,如上文关于图3所述的背侧重布线结构106的介电层108及112。所有此种工艺均旨在包括在实施例的范围内。

[0162]

也可包括其他特征及工艺。举例来说,可包括测试结构,以帮助对三维(three

‑

dimensional,3d)封装或三维集成电路(three

‑

dimensional integrated circuit,3dic)装置进行验证测试。所述测试结构可例如包括在重布线层中或在衬底上形成的测试焊盘,以使得能够对三维封装或三维集成电路进行测试、对探针和/或探针卡(probe card)进行使用等。可对中间结构以及最终结构执行验证测试。另外,本文中所揭露的结构及方法可结合包括对已知良好管芯进行中间验证的测试方法来使用,以提高良率并降低成本。

[0163]

各实施例可实现多个优点。包含作为pi前体的聚酰胺酸酯、作为溶剂的γ

‑

丁内酯(gbl)及二甲基亚砜(dmso)、作为交联剂的二甲基丙烯酸四乙二醇酯及作为感光剂的4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑的配方可用于生产例如集成扇出型(info)封装的重布线层(rdl)的聚酰亚胺(pi)介电材料。通过使用绿色或环境友好型混合溶剂即gbl与dmso可减少环境污染。通过使用所述配方,例如(举例来说)通孔等rdl特征的分辨率可从约8μm增加到约3μm。通过使用所述配方,pi固化温度可降低到约170℃,这可降低热预算并减少由于对例如动态随机存取存储器(dram)单元等装置的损坏而导致的良率损失。所述配方还可提供更短的显影时间及更低的曝光能量,这可分别提高生产通量及装置可靠性。形成pi介电材料可减小模制凹坑凹槽的尺寸,例如由于研磨,这可减少rdl桥接及由rdl走线断裂导致的良率损失。

[0164]

根据实施例,一种制造半导体装置的方法包括:将聚合物材料放置在衬底之上,所述聚合物材料包含聚合物前体、感光剂、交联剂及溶剂,所述感光剂包括4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑;对聚合物材料进行图案化;以及在介于170℃到230℃范围内的温度下对所述聚合物材料进行固化。在实施例中,所述溶剂包括γ

‑

丁内酯(gbl)及二甲基亚砜(dmso)。在实施例中,固化前的所述聚合物材料包含介于40重量%到50重量%范围内的gbl。在实施例

中,固化前的所述聚合物材料包含介于5重量%到15重量%范围内的dmso。在实施例中,固化前的所述聚合物前体包括聚酰胺酸酯。在实施例中,固化前的所述聚合物材料包含介于25重量%到35重量%范围内的聚合物前体。在实施例中,固化前的所述聚合物材料包含介于0.1重量%到2.5重量%范围内的感光剂。在实施例中,固化前的所述聚合物材料还包含添加剂。在实施例中,所述添加剂选自由2

‑

苯甲基

‑2‑

(二甲氨基)

‑1‑

[4

‑

(吗啉基)苯基]

‑1‑

丁酮、(2

‑

二甲氨基

‑2‑

(4

‑

甲基苯甲基)

‑1‑

(4

‑

吗啉

‑4‑

基苯基)丁烷

‑1‑

酮、1

‑

[4

‑

(苯硫基)苯基]

‑

1,2辛烷二酮

‑

2(邻苯甲酰基肟)及1

‑

[9[乙基

‑6‑

(2

‑

甲基苯甲酰基)

‑

9h

‑

咔唑

‑3‑

基]乙酮邻乙酰基肟组成的群组。

[0165]

根据另一实施例,一种制造半导体装置的方法包括:在衬底之上施加聚合物混合物,所述聚合物混合物包含聚合物前体、溶剂、交联剂及感光剂,所述交联剂包括二甲基丙烯酸四乙二醇酯,所述聚合物混合物含2重量%到10重量%的交联剂,所述感光剂包括4

‑

苯基

‑2‑

(哌嗪

‑1‑

基)噻唑;对所述聚合物混合物的至少一部分进行曝光及显影以形成介电层;对所述介电层进行固化;及在所述介电层之上形成金属化图案。在实施例中,所述对所述介电层进行固化是在介于170℃到230℃范围内的温度下执行。在实施例中,所述对所述聚合物混合物的至少所述部分进行曝光及显影是以介于90mj到110mj范围内的曝光能量来执行。在实施例中,溶剂包括二甲基亚砜及γ

‑

丁内酯。在实施例中,聚合物混合物还包含添加剂,所述添加剂包括4,4'

‑

双(二乙氨基)二苯甲酮。在实施例中,在所述对所述介电层进行固化之后,所述介电层具有介于184mpa到190mpa范围内的拉伸强度。在实施例中,所述介电层具有介于72%到79%范围内的伸长百分比。在实施例中,所述介电层具有介于217℃到219℃范围内的热机械分析玻璃转变温度。

[0166]

根据又一实施例,一种半导体封装包括:管芯,位于第一介电层上;包封体,位于所述第一介电层上,所述包封体包封所述管芯;穿孔,延伸穿过所述包封体;以及重布线结构,位于所述包封体、所述管芯及所述穿孔之上,所述重布线结构包括第二介电层以及位于所述第二介电层上的金属化图案,所述第二介电层具有介于175mpa到190mpa范围内的拉伸强度且具有3gpa的杨氏模量,所述金属化图案包括延伸穿过所述第二介电层以实体耦合及电耦合所述管芯的第一导通孔及延伸穿过所述第二介电层以实体耦合及电耦合所述穿孔的第二导通孔。在实施例中,所述第二介电层包含以下化学结构:

[0167]

在实施例中,所述第二介电层还包括延伸到所述包封体中到达大于10μm的深度的介电特征,所述介电特征具有介于15μm到25μm范围内的宽度。

[0168]

以上概述了若干实施例的特征,以使本领域中的技术人员可更好地理解本揭露的各个方面。本领域中的技术人员应理解,其可容易地使用本揭露作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的和/或实现与本文中所介绍的实施例相同的优点。本领域中的技术人员还应认识到,这些等效构造并不背离本揭露的精神及范围,而且他们可在不背离本揭露的精神及范围的条件下在本文中作出各种改变、代替

及变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。