1.本发明属于有源相控阵雷达系统技术领域,特别涉及该领域中的一种用于有源相控阵雷达发射系统的多通道可扩展宽带激励信号产生装置和方法。

背景技术:

2.目前激励信号产生装置的实现途径主要有锁相频率合成技术(pll)和直接数字频率合成技术(dds)等。锁相频率合成技术是通过对输出频率与参考频率在鉴相器中进行比相,再由比相后产生的误差电压控制压控振荡器输出激励信号,这种信号产生过程是一个逐次逼近的过程,输出激励信号的频率稳定需要一定的时间,故而频率转换时间较长,一般需要几个毫秒;并且锁相频率合成技术只能产生离散频率,当对频率分辨率要求比较高、输出通道比较多时,需要采用多环频率合成器,不可避免的要增加额外设备,使系统复杂化。

3.直接数字频率合成技术(dds)是通过控制相位的变化速度来直接产生各种频率的信号。在宽带、频率分辨率、频率转换时间、相位连续性(相位变化连续)、调制输出(对输出信号易实现多种调制)和集成化等方面,都远远超过传统频率合成技术。但是dds技术把频率和相位信息都用数字量表示,这样必然会产生量化精度误差和量化噪声,从而造成输出信号的幅度失真和相位失真,使得dds的输出信号杂散较大;与此同时,dds的输出信号频带有限(最高频率小于0.5fs,更高的fs要求器件的工作频率更高),这是限制dds技术发展和应用的主要问题之一。

4.随着科学技术的飞速发展和自动化程度的不断提高,软件无线电技术得到了快速发展,而数字上变频(duc)作为软件无线电的核心技术,因其全数字化结构,频率分辨率高、频带宽、频率转换时间短、可输出任意波形、易于程控、使用灵活,性价比高、功耗低、体积小、重量轻、可靠性高等优点,在高频信号产生领域已经成为工程应用的首选。

5.有源相控阵雷达系统为了实现空间功率合成和天线波束快速扫描,需要多通道相位精确可控的雷达激励信号产生装置作为支撑,而现代相控阵雷达为了实现预警、跟踪、引导甚至探测等多种功能,对激励信号产生装置提出了很高的要求:一是多通道,能够产生多路相位相关可控的激励信号;二是可扩展,方便系统扩容;三是高频率分辨率,要达到微赫兹量级;四是高相位控制精度;五是能够快速进行空间波束扫描,且波束转换时间短;六是能够依据基带信号产生任意波形;七是能够在宽带范围内进行快速扫频,频率转换时间短。

技术实现要素:

6.本发明所要解决的技术问题就是提供一种应用于短波、超短波有源相控阵雷达系统的多通道可扩展宽带激励产生装置和方法。

7.本发明采用如下技术方案:

8.一种多通道可扩展宽带激励产生装置,其改进之处在于:包括cpci机箱和安装在cpci机箱内的嵌入式主控模块、时钟和同步分配模块、三块以上的激励产生模块;其中嵌入式主控模块与时钟和同步分配模块、各激励产生模块之间的控制信号和数据信号通过cpci

总线传输;时钟和同步分配模块通过射频同轴电缆接收外部输入的时钟信号、时序信号和同步信号,时钟和同步分配模块通过时序连接模块向各激励产生模块传输时钟信号、时序信号和同步信号;嵌入式主控模块按照配置参数控制各模块工作,使各激励产生模块产生激励信号;时钟和同步分配模块包括主时钟同步分配电路、时序控制电路和bit检测电路,用于给各激励产生模块分配时钟信号和同步信号,并产生系统时序信号,各激励产生模块的结构相同,均包括fpga和与fpga电连接的八个激励产生电路、时钟同步分配电路、时序控制电路和bit检测电路。

9.进一步的,嵌入式主控模块为宽温cpci主板。

10.进一步的,时钟和同步分配模块通过ad9516芯片实现时钟和同步信号的分配,系统时序信号由嵌入式主控模块通过pci9054控制fpga产生。

11.进一步的,激励产生模块输出激励信号的频率范围为3mhz~300mhz,输出连续波、脉冲、调幅、调频、2ask和2fsk信号形式。

12.进一步的,激励产生模块的各激励产生电路结构相同,均包括与fpga电连接的ad9788芯片、低通滤波器和运算放大器,产生的激励信号送入射频输出通道,检测信号送入bit检测电路。

13.进一步的,激励产生模块的时钟同步分配电路使用ad9516芯片进行时钟和同步信号的分配,ad9516芯片输出到每片ad9788芯片的时钟和同步信号走线等长,误差小于10mil。

14.进一步的,激励产生模块的bit检测电路采用二极管检波电路检测时钟同步分配电路输出时钟信号和同步信号的幅度,采用fpga计数器检测时钟同步分配电路输出时钟信号和同步信号的频率,采用二极管检波电路检测各激励产生电路输出激励信号的幅度,并由fpga控制电子开关选通各激励产生电路输出的激励信号输入二极管检波电路,最后由fpga判断检测结果并上报嵌入式主控模块。

15.进一步的,通过添加激励产生模块或者级联装置的方式扩展激励通道。

16.一种激励产生方法,使用上述的装置,其改进之处在于,包括如下步骤:

17.步骤1,设备自检:

18.多通道可扩展宽带激励产生装置进行周期自检,自检内容包括各激励产生模块时钟信号和同步信号的幅度与频率、各激励产生电路输出激励信号幅度、时钟和同步分配模块输出时钟信号和同步信号的幅度与频率,自检后若检测信号异常,则会通过嵌入式主控模块显示异常信息;

19.步骤2,调制基带数据产生:

20.将数字调制信号通过数字上变频直接调制到射频工作频率上,首先需要在嵌入式主控模块内产生调制基带数据,产生的调制基带数据包括正弦、方波、半波和三角波等;

21.步骤3:参数设置:

22.嵌入式主控模块发送的控制参数和数据包括:工作频率、工作通道、通道相位和调制基带数据,各激励产生模块按照控制参数通过spi总线配置ad9788芯片,并且将调制基带数据存储在fpga的ram内,时钟和同步分配模块按照调制频率设置调制时序参数;

23.步骤4,工作流程:

24.首先,时钟和同步分配模块输出时序信号至各激励产生模块,并由激励产生模块

同步输出到fpga,当fpga响应第一个时序信号后,同时输出多通道基带数据给各ad9788芯片,基带数据在ad9788芯片内部进行内插滤波后与数字控制振荡器进行混频调制,最终按照寄存器设置的工作频率、幅度和相位同步实现多通道调幅信号输出。

25.进一步的,步骤2输出正弦标准调幅信号,设载波信号v0(t)=v0cosω0t,其中v0为载波信号振幅,ω0为载波信号角频率;调制信号v

ω

(t)=v

ω

cosωt,其中v

ω

为调制信号振幅,ω为调制信号角频率;

26.则标准调幅信号的振幅表达式为:

[0027][0028]

从而得到标准调幅信号的数学表达式:v(t)=v0[1 m

a cosωt]cosω0t,式中调制度0<m

a

≤1,k

d

为比例常数;

[0029]

由标准调幅信号数学表达式可得其离散数学表达式:v(n)=[1 m

a

v

ω

(n)]v0(n),其中v

ω

(n)是调制信号离散序列,v0(n)是载波信号离散序列,从离散表达式可知,调制信号v

ω

(n)先与调制度m

a

相乘,然后再与量化值相加,即在信号上叠加一个直流电平后就能得到标准调幅信号的基带数据,嵌入式主控模块按照上述公式和方法产生调制基带数据并提供给ad9788,调制基带数据再经过内插滤波处理后与ad9788内部数字控制振荡器产生的载波信号进行混频调制,经dac转换最终产生标准调幅信号。

[0030]

本发明的有益效果是:

[0031]

本发明所公开的激励产生装置,为有源相控阵雷达系统的研究提供了强有力的支撑,并在电工技术、工业自动化、智能控制及通讯电子等领域有着巨大的应用潜力,相对于传统的频率合成技术具有以下优势:

[0032]

(1)多通道激励信号输出,单机可同时输出96通道相位相关可控的激励信号,为了实现多个通道间、多个模块间、多个设备间的相位稳定同步,本装置采用了独特的同步算法和同步时序,为其在有源相控阵雷达系统中的应用提供了坚实保障;

[0033]

(2)采用模块化设计,通过添加激励产生模块或者级联装置可扩展激励通道,满足不同相控阵系统要求且维修维护方便;

[0034]

(3)信号形式多样,常规设计输出连续波、脉冲、调幅、调频、2ask、2fsk等信号形式,并具备加载不同基带信号输出任意波形的能力;

[0035]

(4)工作模式多样,具备循环扫频、往返扫频、双频双波束、快速波束扫描以及数据/广播等工作模式;

[0036]

(5)频带宽,采样时钟频率为720mhz,理论输出频率最高可达360mhz;

[0037]

(6)频率分辨率高,参考时钟频率为180mhz时,采样时钟频率为720mhz,理论频率分辨率可达0.167hz;

[0038]

(7)输出相位控制精度高,理论相位控制精度可达0.005度;

[0039]

(8)采用数字上变频技术减少了由于dds的相位截断误差、幅度量化误差和dac的非理想特性等因素引起的杂散,能够实现较高的信号频谱纯度;

[0040]

(9)频率捷变时具有相位连续性,能够快速进行空间波束扫描,其波束转换时间极

短,可达纳秒量级;能够在宽带范围内进行快速扫频,其频率转换时间极短,可达纳秒量级;操作简单,人机界面良好,具备bit告警功能;设备量少,成本低,可靠性高。

[0041]

本发明所公开的激励产生方法,与上述的激励产生装置相配合,可产生多路相位相关可控的激励信号,能够应用于短波、超短波有源相控阵雷达系统。

附图说明

[0042]

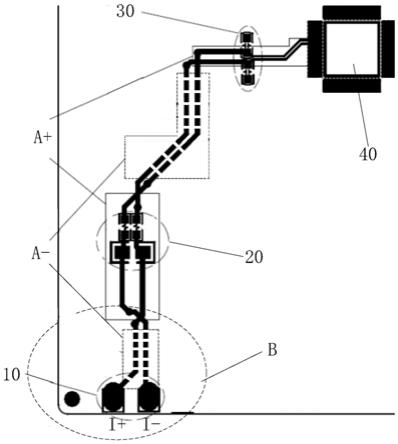

图1是本发明实施例1所公开激励产生装置的组成示意框图;

[0043]

图2是本发明实施例1所公开激励产生装置中时钟和同步分配模块的组成示意框图;

[0044]

图3是本发明实施例1所公开激励产生装置中激励产生模块的组成示意框图;

[0045]

图4是通道扩展级联的结构框图;

[0046]

图5是幅度调制示意图;

[0047]

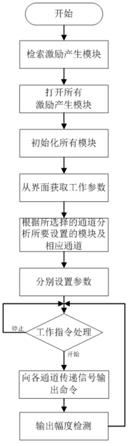

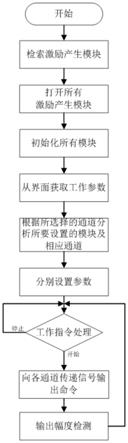

图6是激励控制软件的运行流程图。

具体实施方式

[0048]

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图和实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

[0049]

实施例1,本实施例公开了一种多通道可扩展宽带激励产生装置,采用数字上变频(duc)技术和cpci架构,如图1所示,硬件包括cpci机箱和安装在cpci机箱内的嵌入式主控模块、时钟和同步分配模块、多块激励产生模块。其中嵌入式主控模块与时钟和同步分配模块、各激励产生模块之间的控制信号和数据信号通过cpci总线传输,时钟和同步分配模块通过射频同轴电缆接收外部输入的时钟信号、时序信号和同步信号,时钟和同步分配模块通过时序连接模块向各激励产生模块传输时钟信号、时序信号和同步信号。激励产生装置的电源线和控制信号线使用专用规格线缆和接头连接。软件包括激励控制软件、时序控制软件和激励产生软件。激励控制软件在嵌入式主控模块内运行,提供友好人机界面和配置参数,嵌入式主控模块按照配置参数控制各模块工作,使各激励产生模块产生激励信号,时序控制软件在时钟和同步分配模块的fpga内运行,按照配置参数控制时钟和同步分配模块产生时钟、时序和同步信号;激励产生软件在激励产生模块的fpga内运行,按照配置参数控制激励产生模块产生激励信号。时钟和同步分配模块包括主时钟同步分配电路、时序控制电路和bit检测电路,用于给各激励产生模块分配时钟信号和同步信号,并产生系统时序信号,各激励产生模块的结构相同,均包括fpga和与fpga电连接的八个激励产生电路、时钟同步分配电路、时序控制电路和bit检测电路。

[0050]

嵌入式主控模块是一款宽温6u cpci主板(凌华科技公司的cpci

‑

6210/710q),主要功能是执行激励控制软件指令和总线通信。

[0051]

时钟和同步分配模块主要功能为产生分配出多路参考时钟信号、时序信号和同步信号,并分别提供给各激励产生模块。如图2所示,时钟和同步分配模块通过ad9516芯片实现时钟和同步信号的分配,系统时序信号由嵌入式主控模块通过pci9054控制fpga产生,每个激励产生模块均按照时序信号开始工作。

[0052]

如图3所示,激励产生模块是激励产生装置的核心模块,采用cpci fpga dac架构,各激励产生模块在fpga和dac中进行数字上变频,将基带信号通过数字方式调制到中高频,最后经dac转换成模拟激励信号输出。

[0053]

激励产生模块的各激励产生电路结构相同,均包括与fpga电连接的ad9788芯片、低通滤波器和运算放大器,采用数字上变频技术实现信号产生功能,产生的激励信号送入射频输出通道,检测信号送入bit检测电路。由于fpga具有集成度高、资源丰富、灵活性好和可编程的优点,用来实现数字上变频具有系统集成度高和成本低的优势,激励产生模块的fpga主要实现数字上变频基带数据加载、调用等功能,而数字上变频的内插滤波、混频由ad9788芯片实现。ad9788芯片是adi公司生产的一款双通道、宽动态数模转换器(dac)芯片,提供800ms/s采样速率,具有很高的集成度,内置nco,最高输出频率为400mhz,其频率控制字为32位,当系统时钟为150mhz时,其频率分辨率可达0.167hz,相位控制字为16位,相位控制精度可达0.005度。

[0054]

低通滤波器型号为ldt

‑

450w750,通带dc~400mhz,截止频率440mhz,止带580~750mhz抑制优于20db,止带750~1800mhz抑制优于40db,插损小于0.3db。为了保证多通道激励信号的相位幅度一致性,要求同一批次生产的低通滤波器相位一致性在3

°

之内,幅度一致性在1db之内。

[0055]

运算放大器采用sbf5089进行放大,此款运算放大器宽电压输入、低失真、幅度平坦度好,适合作任意波形发生器的输出驱动。

[0056]

激励产生模块的时钟同步分配电路由多片ad9516芯片实现时钟和同步信号的分配,为了使相控阵雷达发射信号工作时能够在一定的方向上达到最大的辐射功率,实现最好的空间功率合成效果,各通道激励信号的相位同步至关重要,所以为保证每片ad9788芯片能够同步工作,必须保证ad9516芯片输出到每片ad9788芯片的参考时钟信号和同步信号走线严格等长,误差小于10mil。

[0057]

激励产生模块的时序控制电路主要由pci9054和fpga来实现,其主要功能是为激励产生模块提供数据及地址的缓冲和转发并产生各种控制信号。

[0058]

相控阵雷达系统采用duc输出激励信号,若激励信号的参考时钟故障,必然造成duc输出的激励信号不正确,进而有可能损坏发射系统的功率放大部分,所以激励产生模块的bit检测电路必不可少。

[0059]

bit检测电路主要功能为检测时钟同步分配电路输出的时钟信号和同步信号的幅度和频率,检测激励产生电路输出的各通道激励信号的幅度。bit检测电路采用二极管检波电路检测时钟信号和同步信号的幅度;使用fpga计数器检测时钟信号和同步信号的频率,最后由fpga综合判断检测结果并上报嵌入式主控模块激励控制软件。各通道激励信号的幅度也是通过二极管检波电路实现,由fpga控制电子开关选通各通道激励信号输入二极管检波电路,当有激励信号输入时二极管检波电路会输出高电平给fpga。

[0060]

激励产生模块输出激励信号的频率范围为3mhz~300mhz,输出连续波、脉冲、调幅、调频、2ask和2fsk信号形式。采用集成化、模块化、小型化设计,工作稳定可靠,结构设计考虑了抗震性,既可用于船载和车载,也可作为固定站使用。

[0061]

为了使相控阵雷达发射信号工作时能够在一定的方向上达到最大的辐射功率,实现最好的空间功率合成效果,各通道激励信号的相位同步至关重要。如图4所示,多通道可

扩展宽带激励产生装置可以通过添加激励产生模块或者级联装置的方式扩展激励通道,那么怎么保障几百个输出通道信号的相位稳定同步成为该装置成功应用的关键。本装置采用了独特的同步算法和同步时序,完美解决多个通道间、多个模块间、多个设备间的相位同步问题。

[0062]

具体同步过程是由上位控制设备产生参考时钟信号、同步信号和时序信号同时分配各个装置以及各装置内的每个激励产生模块;参考时钟信号保证各级装置和激励产生模块所使用的时钟同步相参,并采用同步校正算法将时钟信号在ad9788芯片中同时倍频到720mhz,保证装置在每次上电启动时各通道间时钟不存在不确定的相位差;而时序信号即设备的工作脉冲信号,由上位控制设备产生,并由各级装置和激励产生模块的参考时钟信号触发传递,保证了所有激励产生模块fpga的数字基带信号同步输出,且与参考时钟信号相位固定,无亚稳定状态;最后的同步措施为使用同步信号同步所有激励产生模块的dac芯片ad9788,ad9788芯片有脉冲和pn码(伪随机噪声码)调制解调两种主从同步信号模式,当同步信号把ad9788芯片内部时钟发生状态机触发到同一状态且nco相位累加器状态相同时,多片dac即彼此完成同步。通过以上方式最终解决了多通道可扩展宽带激励产生装置多个通道间、多个模块间、多个设备间的相位同步问题。

[0063]

本实施例还公开了一种激励产生方法,使用上述的装置,包括如下步骤:

[0064]

步骤1,设备自检:

[0065]

多通道可扩展宽带激励产生装置可进行周期自检,自检内容包括:各激励产生模块时钟信号、同步信号的幅度与频率、各激励产生电路输出激励信号幅度、时钟和同步分配模块输出时钟信号、同步信号的幅度与频率等,自检后若检测信号异常,则会在激励控制软件界面显示;

[0066]

步骤2,调制基带数据产生:

[0067]

传统的模拟调制信号源多采用模拟乘法器等模拟电路实现调幅信号,其信号质量不高,存在着频率不稳定,参数设定不可量化、精度低、可控性差、抗干扰能力弱等缺点。

[0068]

多通道可扩展宽带激励产生装置输出调幅信号采用了数字上变频技术,将数字调制信号通过duc直接调制到射频工作频率上,达到模拟调制的目的,克服了传统模拟调制信号源的缺点。

[0069]

多通道可扩展宽带激励产生装置可输出正弦、方波、半波、三角波等幅度调制信号,本例输出正弦标准调幅信号,幅度调制示意图如图5所示。

[0070]

设载波信号v0(t)=v

0 cosω0t,其中v0为载波信号振幅,ω0为载波信号角频率;调制信号v

ω

(t)=v

ω

cosωt,其中v

ω

为调制信号振幅,ω为调制信号角频率;

[0071]

则标准调幅信号的振幅表达式为:

[0072][0073]

从而得到标准调幅信号的数学表达式:v(t)=v0[1 m

a cosωt]cosω0t,式中称为调制度,是标准调幅的主要参数,它表征着已调波的调制深度,0<m

a

≤1,k

d

为比例常数;

[0074]

由标准调幅信号数学表达式可得其离散数学表达式:v(n)=[1 m

a

v

ω

(n)]v0(n),其中v

ω

(n)是调制信号离散序列,v0(n)是载波信号离散序列,从离散表达式可知,调制信号v

ω

(n)先与调制度m

a

相乘,然后再与量化值相加(即在信号上叠加一个直流电平)后就能得到标准调幅信号的基带数据,嵌入式主控模块按照上述公式和方法产生调制基带数据并提供给ad9788,调制基带数据再经过内插滤波处理后与ad9788内部数字控制振荡器产生的载波信号进行混频调制,经dac转换最终产生标准调幅信号。

[0075]

步骤3:参数设置:

[0076]

激励控制软件发送控制参数和数据,控制参数和数据包括:工作频率、工作通道、通道相位和调制基带数据等,在各激励产生模块内的激励产生软件按照控制参数通过spi总线配置ad9788芯片,并且将调制基带数据存储在fpga的ram内,激励控制软件运行流程如图6所示,时钟和同步分配模块内的时序控制软件按照调制频率设置调制时序参数;

[0077]

步骤4,工作流程:

[0078]

激励控制软件控制开始工作后,首先,时钟和同步分配模块输出时序信号至各激励产生模块,并由激励产生模块同步输出到fpga,当fpga响应第一个时序信号后,同时输出多通道基带数据给各ad9788芯片,基带数据在ad9788芯片内部进行内插滤波后与nco进行混频调制,最终会按照寄存器设置的工作频率、幅度和相位同步实现多通道调幅信号输出的目的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。