一种多路cpu系统中时钟同步控制装置、系统及控制方法

技术领域

1.本发明涉及时钟同步技术领域,尤其涉及一种多路cpu系统中时钟同步控制装置、系统及控制方法。

背景技术:

2.多路cpu系统中,时间系统是多路服务器中的一个重要基础部分,其主要是用于程序运行的任务调度与切换、物理通路的报文超时机制等。系统中各个socket需要保持时间一致,也即为需要保持时钟同步,否则会导致系统硬件初始化以及软件运行异常等。

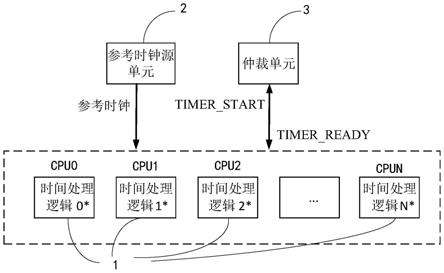

3.cpu的时钟系统的参考源一般是由外部提供,cpu内部的时间处理逻辑获取到该外部参考源后,产生cpu的时间,再派发到各个cpu核上,基于收到的时间,各个cpu核之间理想状态下应当是同步、没有时间差的,这样代码能够在各个核之间进行迁移和运行,单路cpu的时间系统如图1所示。将单路cpu系统扩展为多路cpu系统后,软件层面上不需要关注多个cpu之间的差异,多路cpu只提供硬件资源(核数、缓存、内存、io等)给软件使用,实现更强的计算、io扩展能力。多路cpu系统中,由于每个cpu芯片都有时间处理逻辑,因而在多路系统中会存在多个时间处理逻辑,为了保持多个cpu的时间的一致性,则必须要求多个时间处理逻辑发出的时间是一致的,即确保各cpu的时间处理逻辑是同步的。且为确保多路系统的性能,通常要求各cpu之间能够保持高精度的时间同步。

4.针对于时间/时钟同步,现有技术中大多数都是采用网络协议报文方式进行时间同步,即在两台设备之间,通过网络方式进行时间获取或者时间校准,如图2所示,设备a与设备b之间通过网络方式获取时间或者进行时间校准,实现时间同步。上述网络协议报文方式中,时间校准的流程通常为:网络上传输的网络时间采取特定的报文形式传输,报文中附带发送端的时间信息,接收端收到报文后,解析出时间信息,进行设备时间校准。

5.但是上述传统的采用网络协议报文方式实现时间同步,会存在以下问题:

6.1、效率低、耗时长。

7.由于需要依赖于网络传输来完成设备间时间同步,而网络传输、报文解析等均需要一定的时间,因而完成整个时间同步往往需要耗费较多的时间,导致同步效率低,在芯片在上电后,通常就无法尽快获取到有效的时钟系统,而这会影响芯片初始化时间。

8.2、同步效果难于达到高精度。

9.不仅网络传输需要一定的时间,而且报文的生成和解析产生也会存在一定的时延,因而报文到不同设备的传输时延通常是不同的,导致不同设备最终所获得的时间会存在差异,实际就难以达到高精度的同步,不能满足多路cpu中对于时间系统的高精度要求。

10.3、实现操作复杂且成本高。

11.由于时间校准需要依赖于报文的传输,因而必须构建包含报文发送端、接收端以及传输介质的时间装置,不仅实现复杂,且会增加实现成本。尤其当应用于多路系统中时,由于多路系统之间需要构建大量的时间装置进行报文的收发,会大大增加实现复杂度以及成本。

12.有从业者考虑将时间同步方法放置到芯片设计中,以提高时间同步的效率以及精度,但是这又会导致芯片设计复杂度大大提升,且后续难以针对该时间同步逻辑进行测试。

13.因此,亟需提供一种能够适用于多路系统的时钟同步控制方案,以使得能够兼顾时钟同步实现的效率、精度以及实现成本与复杂程度。

技术实现要素:

14.本发明要解决的技术问题就在于:针对现有技术存在的技术问题,本发明提供一种结构简单、同步效率以及精度高且复杂程度与实现成本低的多路cpu系统中时钟同步控制装置、系统及控制方法。

15.为解决上述技术问题,本发明提出的技术方案为:

16.一种多路cpu系统中时钟同步控制装置,包括:分别与各路cpu系统连接的参考时钟源单元,以及分别与各路cpu系统连接的仲裁单元,所述参考时钟源单元用于为各cpu系统中的所述时间处理逻辑提供统一的参考时钟,所述仲裁单元用于统一控制调度各cpu系统中的所述时间处理逻辑进行时间的推进。

17.进一步的,所述参考时钟源单元通过物理线路与各cpu系统连接。

18.进一步的,所述仲裁单元与各cpu系统中的gpio(general

‑

purpose input/output,通用型输入输出)接口连接,以通过所述gpio接口进行通讯。

19.进一步的,所述仲裁单元包括依次连接的控制信号产生子单元以及控制子单元,所述控制信号产生子单元用于产生开始时间推进控制信号,分别发送给各路cpu系统中的所述时间处理逻辑,所述控制子单元按照所述时间推进开始控制信号,控制各路cpu系统中的所述时间处理逻辑开始进行时间推进。

20.进一步的,各路cpu系统中还设置有与所述仲裁单元连接的就绪信号发送单元,用于发送时间推进准备就绪状态信号给所述仲裁单元。

21.进一步的,所述控制子单元具体当各路cpu系统发送的所述时间推进准备就绪状态信号均为有效状态时,配置使得所述时间推进开始控制信号为有效状态,以控制启动各路cpu系统中的所述时间处理逻辑开始进行时间推进。

22.一种多路cpu系统,各路所述cpu系统包括时间处理逻辑,还包括如上述的时钟同步控制装置,由所述时钟同步控制装置控制各路cpu系统中所述时间处理逻辑进行时钟同步。

23.一种多路cpu系统中时钟同步控制方法,包括:

24.产生参考时钟源,统一提供给各路cpu系统中的所述时间处理逻辑;

25.统一控制调度各cpu系统中的所述时间处理逻辑进行时间的推进。

26.进一步的,所述统一控制调度各cpu系统中的所述时间处理逻辑进行时间的推进包括:

27.产生时间推进开始控制信号,分别发送给各路cpu系统中的所述时间处理逻辑;

28.按照所述时间推进开始控制信号,控制各路cpu系统中的所述时间处理逻辑开始进行时间推进。

29.进一步的,该方法包括:

30.各路cpu系统在配置时间初值后,产生时间推进准备就绪状态信号并发送;

31.当各路cpu系统发送的所述时间推进准备就绪状态信号均为有效状态时,配置使得时间推进开始控制信号为有效状态,控制启动各路cpu系统中的所述时间处理逻辑开始进行时间推进。

32.与现有技术相比,本发明的优点在于:

33.1、本发明在通过为多路cpu系统的时间系统配置参考时钟源单元,以提供统一的参考时钟,同时为配置为多路cpu系统配置仲裁单元,由仲裁单元统一调度控制各时间处理逻辑是否进行时间推进,能够有效确保各路cpu系统的时间处理逻辑的同步精度以及同步效率,实现多路cpu系统快速、精准的时钟同步,且整个同步过程中无需依赖于复杂的网络协议报文,还可以大大降低同步实现的复杂度以及实现成本。

34.2、本发明能够结合多路cpu系统内部机制实现时钟同步,使得时钟同步机制与多路系统结构相匹配,可以确保多路cpu系统实现精准的时钟同步。

附图说明

35.图1是单路cpu的时间系统结构示意图。

36.图2是现有技术中采用网络协议报文方式时间同步的原理示意图。

37.图3是本实施例多路cpu系统中时钟同步控制装置的结构示意图。

38.图4是本实施例中实现时钟同步的结构原理示意图。

39.图5是在具体应用实施例(双路系统)中实现时钟同步的实现流程示意图。

40.图例说明:1、时间处理逻辑;2、参考时钟源单元;3、仲裁单元;31、控制信号产生子单元;32、控制子单元。

具体实施方式

41.以下结合说明书附图和具体优选的实施例对本发明作进一步描述,但并不因此而限制本发明的保护范围。

42.如图3、4所示,本实施例多路cpu系统中时钟同步控制装置包括:分别与各路cpu系统连接的参考时钟源单元2,以及分别与各路cpu系统连接的仲裁单元3,参考时钟源单元2用于为各cpu系统中的时间处理逻辑1提供统一的参考时钟,仲裁单元3用于统一控制调度各cpu系统中的时间处理逻辑1进行时间的推进。每路cpu系统内包含有一个时间处理逻辑1,由该时间处理逻辑1主要用于时间的设置、时间推进、时间的分发等。

43.不同的时钟源存在频偏与相位差,而cpu的时间处理逻辑对时钟的频偏与相位差敏感,因而不同的参考时钟源,可能产生的时间是不一样的。本实施例考虑上述问题,为多路cpu系统的时间系统配置一个参考时钟源单元2,由该参考时钟源单元2为各时间处理逻辑1提供一个统一的时间参考源,使得各时间处理逻辑1保持时钟同源。

44.多路cpu系统的时间处理逻辑1基于参考时钟源单元2能够获取到同一的时钟源,可以确保各路cpu的时钟源的同一性,但是时间的推进是由各个cpu内部的时间处理逻辑来处理,各个cpu的时间推进和停止推进的时间点并不相同,即便使用同一时钟源仍然无法确保各路cpu系统在时间推进时是同步的。本实施例考虑上述问题,在为多路cpu系统的时间系统配置一个参考时钟源单元2的基础上,同时为多路cpu系统的时间处理逻辑1配置一个仲裁单元3,由该仲裁单元3统一调度控制各时间处理逻辑1是否进行时间推进,从而结合参

考时钟源单元2、仲裁单元3共同实现时钟同步,能够有效确保各路cpu系统的时间处理逻辑1的同步精度以及同步效率,实现多路cpu系统快速、精准的时钟同步,在cpu芯片上电即可以快速的获取到时钟信息,且整个同步过程中无需依赖于复杂的网络协议报文,还可以大大降低同步实现的复杂度以及实现成本。

45.在具体应用实施例中,参考时钟源单元2提供的参考时钟的频率具体可以根据cpu的实际设计约束来配置。

46.本实施例中,参考时钟源单元2具体通过物理线路与各cpu系统连接,参考时钟源单元2输出的参考时钟信号通过物理线路传输到各路cpu系统的时间处理逻辑1,参考时钟信号在物理介质中传输。参考时钟源单元2与各cpu系统采用物理线路连接的方式,一方面、由于信号直接通过物理线路传输,传输效率高、时延小,可以大大减少传统如网络协议报文方式的网络传输时延;另一方面、信号通过物理线路传输的抗干扰性能强,参考时钟不易受干扰信号的影响,从而能够进一步提高时钟同步的精度、可靠性。

47.由于不同的物理介质长度会产生不同的延时,在具体应用实施例中,配置参考时钟源单元2与各路cpu系统之间的物理线路时,具体可以根据各cpu的时间精度要求,确定各cpu系统对应的物理介质最大容忍传输长度。

48.本实施例中,仲裁单元3与各cpu系统中的gpio接口连接,以通过gpio接口进行通讯。相比于传统通信接口,gpio接口的传输效率高,且消息传递实现简单,结合gpio接口连接方式,可以进一步提高多路cpu系统时钟同步的效率以及精度。

49.可以理解的是,仲裁单元3与各cpu系统也可以根据实际需求采用其它如i2c、uart等的低速接口连接。

50.如图4所示,本实施例中仲裁单元3包括依次连接的控制信号产生子单元31以及控制子单元32,控制信号产生子单元31用于产生开始时间推进控制信号timer_start,分别发送给各路cpu系统中的时间处理逻辑1,控制子单元32按照开始时间推进控制信号timer_start,控制各路cpu系统中的时间处理逻辑1开始进行时间推进,即控制时间推进的开始时间。由于仲裁单元无法感知cpu系统的时间推进状态,即何时开始进行时间推进,本实施例通过在仲裁单元3中设置控制信号产生子单元31,由控制信号产生子单元31产生控制信号来控制时间推进的开始,使得能够确保各路cpu系统的时间处理逻辑1均是在同一时间点下开始进行时间推进,避免不同cpu系统的时间处理逻辑1时间推进的时间点不同,确保多路系统时钟同步的高精度。

51.本实施例中,各路cpu系统中还设置有与仲裁单元3连接的就绪信号发送单元,用于发送时间推进准备就绪状态信号timer_ready给仲裁单元3。时间推进必须在cpu系统准备就绪的状态下进行,否则无法完成同步,仲裁单元3也无法感知各路cpu系统的时间处理逻辑1是否处于准备就绪状态,本实施例通过由各路cpu系统的就绪信号发送单元,在时间推进准备就绪后,向仲裁单元3发送时间推进准备就绪状态信号timer_ready,以通知仲裁单元3本cpu系统可以准备进行时间推进,避免在存在cpu系统未准确就绪状态下即启动时间推进。

52.在具体应用实施例中,时间推进准备就绪状态信号timer_ready具体在设置时间初值等配置信息后产生,在cpu已经设置好时间初值后,判定cpu系统具备时间推进的条件,即时间推进准确就绪,则置时间推进准备就绪状态信号timer_ready为有效,发送给仲裁单

元3。

53.为实现时间的设置,进一步的cpu系统可以配置可编程接口,以用于设置时间初值、时间推进的起始与截止点等。

54.本实施例中,控制子单元32具体当各路cpu系统发送的时间推进准备就绪状态信号timer_ready均为有效状态时,即表明所有cpu系统均已准确就绪,配置使得时间推进开始控制信号为timer_start有效状态,以控制启动各路cpu系统中的时间处理逻辑1开始进行时间推进,如果存在cpu系统发送的时间推进准备就绪状态信号timer_read为无效状态,则置使得时间推进开始控制信号为timer_start为无效状态以不控制进行时间推进。控制子单元32通过识别各路cpu的时间推进准备就绪状态信号timer_ready是否都有效,以决定timer_start信号是否有效,可以确保在各路cpu系统均处于时间推进准备就绪状态下,按照相同的时间点进行时间推进,从而确保时钟同步的精度以及可靠性。

55.在具体应用实施例中,如表1所示,如果接收到的各路cpu系统发送的timer_ready信号都有效,则置timer_start信号为有效,表明整个系统可以开始执行时间同步,如果timer_ready信号并不是都有效,则判定timer_start无效,表明整个系统不能开始执行时间同步。

56.表1:cpu接口定义。

[0057][0058]

可以理解的是,仲裁单元3还可以根据实际需求产生其他类型的控制信号,或综合使用多种类型的控制信号共同控制cpu系统的时间推进,以进一步提高时钟同步的控制性能。

[0059]

以下以对双路cpu系统(cpu0、cpu1)进行时钟同步控制为例,对本实施例上述时钟同步控制装置进行进一步说明。

[0060]

如图5所示,本实施例中仲裁单元3具体处理timer_ready与timer_start的信号逻辑,该两个信号默认上电都为低电平(无效状态),该部分逻辑配置为系统的上电初始化流程的一部分。对于timer_ready与timer_start两个信号的处理逻辑,如表2所示,当cpu0、cpu1的timer_ready均为高电平(有效状态)时,则timer_start信号为高电平(有效状态),如果cpu0、cpu1的timer_ready均为低电平(无效状态)时,则timer_start信号为低电平(无效状态);如果cpu0、cpu1中timer_ready信号有一个为低电平时,timer_start信号维持不变,即维持当前的时间推进状态不变。

[0061]

表2:仲裁单元时间推进控制逻辑。

[0062]

cpu0_timer_readycpu1_timer_readytimer_start高高高低低低高低电平维持不变低高电平维持不变

[0063]

本实施例还提供多路cpu系统,各路cpu系统包括时间处理逻辑1,还包括如上述的时钟同步控制装置,由时钟同步控制装置控制各路cpu系统中时间处理逻辑1进行时钟同步。

[0064]

本实施例还提供多路cpu系统中时钟同步控制方法,包括:

[0065]

s1.产生参考时钟源,统一提供给各路cpu系统中的时间处理逻辑1;

[0066]

s2.统一控制调度各cpu系统中的时间处理逻辑1进行时间的推进。

[0067]

本实施例中,上述步骤s2具体包括:

[0068]

产生开始时间推进控制信号timer_start,分别发送给各路cpu系统中的时间处理逻辑1;

[0069]

按照开始时间推进控制信号timer_start,控制各路cpu系统中的时间处理逻辑1进行时间推进的开始时间。

[0070]

本实施例中,该方法包括:

[0071]

各路cpu系统在配置时间初值后,产生时间推进准备就绪状态信号timer_ready并发送;

[0072]

当各路cpu系统发送的所述时间推进准备就绪状态信号timer_ready均为有效状态时,配置使得时间推进开始控制信号timer_start为有效状态,控制启动各路cpu系统中的时间处理逻辑1开始进行时间推进。

[0073]

本实施例多路cpu系统中时钟同步控制方法为用于实施上述多路cpu系统中时钟同步控制装置的方法,具有与上述多路cpu系统中时钟同步控制装置相对应的效果,在此不再一一赘述。

[0074]

上述只是本发明的较佳实施例,并非对本发明作任何形式上的限制。虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明。因此,凡是未脱离本发明技术方案的内容,依据本发明技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均应落在本发明技术方案保护的范围内。

再多了解一些

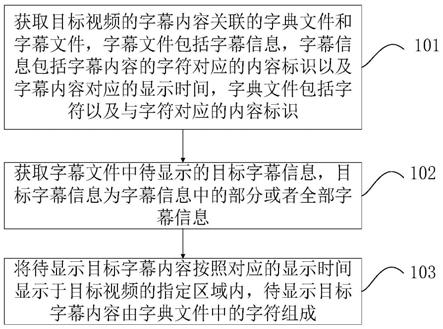

本文用于企业家、创业者技术爱好者查询,结果仅供参考。