1.本发明系有关于对数计算方法。

背景技术:

2.在一般的对数计算电路中,通常是采用坐标旋转数字计算(coordinate rotation digital computer,cordic)方式来实现对数计算,然而,上述方法会需要储存一个很大的参数表,且也需要使用多个电路设计较为复杂的乘法器,因此,会增加电路设计的复杂度及成本。

技术实现要素:

3.因此,本发明的目的之一在于提出一种对数计算方法及相关的电路,其在每次迭代(iteration)运算的过程中仅需要两次加法以及一次移位,因此可以大幅简化电路设计,以解决先前技术中的问题。

4.在本发明的一个实施例中,揭露一种对数计算方法,其用以对一初始输入值进行对数运算,其包含有以下步骤:(a)选择对应到第i次叠代运算的一第一参数、一第二参数、一第三参数以及一第四参数;(b)判断一输入值是大于该第三参数、小于该第四参数、或是位于该第三参数与该第四参数之间,其中该输入值系由该初始输入值所得到;(c)若是该输入值大于该第三参数,透过乘以该第一参数以更新一输入值,透过减去该第一参数的对数值以更新该输出值;若是该输入值小于该第四参数,透过乘以该第二参数以更新该输入值,并减去该第二参数的对数值以更新该输出值;若是该输入值位于该第三参数与该第四参数之间,不改变该输入值与该输出值;(d)将i加上1,并回到步骤(a),直到i等于一预设值;以及(e)当i等于该预设值时,将目前的该输出值作为对该初始输入值进行对数运算的一输出结果。

5.在本发明的另一个实施例中,揭露了一种对数计算电路,其用以对一初始输入值进行对数运算,且包含有一叠代运算电路,且该叠代运算电路用以依序进行多次叠代运算;针对该叠代运算电路所执行的任一次叠代运算,该叠代运算电路执行以下操作:(a)选择对应到之一第一参数、一第二参数、一第三参数以及一第四参数;(b)判断一输入值是大于该第三参数、小于该第四参数、或是位于该第三参数与该第四参数之间,其中该输入值系根据该初始输入值所得到;(c)若是该输入值大于该第三参数,透过乘以该第一参数以更新该输入值,透过减去该第一参数的对数值以更新一输出值;若是该输入小于该第四参数,透过乘以该第二参数以更新该输入值,并减去该第二参数的对数值以更新该输出值;若是该输入值位于该第三参数与该第四参数之间,不改变该输入值与该输出值;(d)将更新后的该输入值及该输出值作为下一次迭带运算的输出值与输入值;其中该叠代运算电路的最后一次叠代运算所产生的该输出值作为对该初始输入值进行对数运算的一计算结果。

附图说明

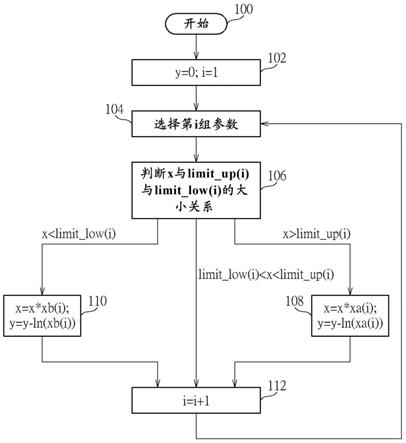

6.图1为根据本发明一实施例的对数计算方法的流程图。

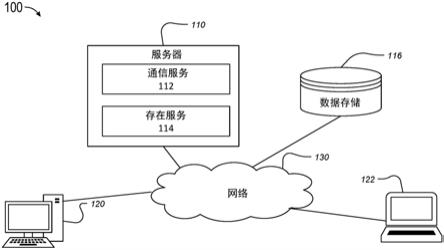

7.图2为根据本发明一实施例的对数计算电路的示意图。

具体实施方式

8.图1为根据本发明一实施例的对数计算方法的流程图。如图1所示,在步骤100中,流程开始,且准备对初始输入值x进行对数运算以得到输出值y,亦即y=ln(x)。在步骤102中,先将输出值y设为0,参数i设为1(亦即,进行第1次叠代运算,并将初始输入值x转换为浮点数表示,亦即将初始输入值x转换为x=m*2^n,其中n为正整数,且m为介于0.5~1之间的数值。在一实施例中,m可以是16位的数字值、且n可以是6位的数字值。在步骤104中,选择第i组参数,其中第i组参数包含了xa(i)、xb(i)、limit_up(i)、limit_low(i),此时,由于一开始计算时i等于1,第1组参数所包含的xa(1)、xb(1)、limit_up(1)、limit_low(1)分别为(1/2)、(3/2)、(4/3)、(4/5)。在步骤106,判断初始输入值x与参数limit_up(1)、limit_low(1)的大小关系,若是初始输入值x大于参数limit_up(1),则流程进入步骤108;若是初始输入值x小于参数limit_low(1),则流程进入步骤110;若是初始输入值x介于参数limit_up(1)与limit_low(1)之间,则流程进入步骤112。在步骤108中,将初始输入值x乘上参数xa(1)以进行更新(后续的x均称为输入值),并将输出值y减去ln(xa(1)),亦即x=x*xa(1),且y=y-ln(xa(1))。在步骤110中,将输入值x乘上参数xb(1),并将输出值y减去ln(xb(1)),亦即x=x*xb(1),且y=y-ln(xb(1))。在步骤112中,将参数i加上1,并回到步骤104开始进行第二次叠代运算。

9.需注意的是,由于在以上的参数xa(1)与xb(1)分别满足1-2^(-1)以及1 2^(-1)的结构,因此,步骤108中的x*xa(1)在电路上可以透过一个移位寄存器以及一个加法器来实现,亦即x*xa(1)=x*(1-2^(-1))=x-x>>1,其中“>>”是移位运算符;同理,步骤110中的x*xb(1)在电路上可以透过一个移位寄存器以及一个加法器来实现,亦即x*xb(1)=x*(1 2^(-1))=x x>>1,其中“>>”是移位运算符。

10.在第二次叠代运算中,在步骤104中所选择的第2组参数所包含的参数xa(2)、xb(2)、limit_up(2)、limit_low(2)分别为(3/4)、(5/4)、(8/7)、(8/9)。在步骤106,判断输入值x与参数limit_up(2)、limit_low(2)的大小关系,若是输入值x大于limit_up(2),则流程进入步骤108;若是输入值x小于参数limit_low(2),则流程进入步骤110;若是输入值x介于参数limit_up(2)与limit_low(2)之间,则流程进入步骤112。在步骤108中,将x乘上xa(2),并将输出值y减去ln(xa(2)),亦即x=x*xa(2),且y=y-ln(xa(2))。在步骤110中,将输入值x乘上xb(2),并将输出值y减去ln(xb(2)),亦即x=x*xb(2),且y=y-ln(xb(2))。

11.由于在以上的参数xa(2)与xb(2)分别满足1-2^(-2)以及1 2^(-2)的结构,因此,步骤108中的x*xa(2)在电路上可以透过一个移位寄存器以及一个加法器来实现,亦即x*xa(2)=x*(1-2^(-2))=x-x>>2;同理,步骤110中的x*xb(2)在电路上可以透过一个移位寄存器以及一个加法器来实现,亦即x*xb(2)=x*(1 2^(-2))=x x>>2。

12.接着,继续进行第三次叠代运算、第四次叠代运算、

…

直到系统的一预设值,例如,当第八次叠代运算完成之后便将所计算出的输出值y输出以作为最后的计算结果,亦即对初始输入值进行对数计算的结果。

13.在一实施例中,每一次叠代运算所使用的参数xa(i)、xb(i)、limit_up(i)、limit_low(i)设计如以下的表一与表二:

14.ixa(i)xb(i)11/23/223/45/437/89/8415/1617/16531/3233/32663/6465/647127/128129/1288255/256257/2569511/512513/512101023/10241025/1024112047/20482049/2048124095/40964097/4096138191/81928193/81921416383/1638416385/163841532767/3276832769/327681665535/6553665537/65536

15.表一

16.ilimit_up(i)limit_low(i)14/34/528/78/9316/1516/17432/3132/33564/6364/656128/127128/1297256/255256/2578512/511512/51391024/10231024/1025102048/20472048/2049114096/40954096/4097128192/81918192/81931316384/1638316384/163851432768/3276732768/327691565536/6553565536/6553716131072/131071131072/131073

17.表二

18.透过上表的参数设计,在第一次叠代运算后的输入值x会介于(2/3)与(4/3)之间,

在第二次叠代运算后的输入值x会介于(5/6)与(8/7)之间,在第三次叠代运算后的输入值x会介于(14/15)与(16/15)之间,在第四次叠代运算后的输入值x会介于(30/31)与(32/31)之间,在第五次叠代运算后的输入值x会介于(62/63)与(64/63)之间,在第六次叠代运算后的输入值x会介于(126/127)与(128/127)之间,

…

,亦即随着叠代运算的次数越多,的输入值x的数值会越来越逼近1,因而使得输出值y也会更逼近理想值。在一范例中,若是进行16次叠代运算操作,输出值y与理想值的误差为7.6*10^(-6)。

19.如以上表所述,由于参数xa(i)与xb(i)分别满足1-2^(-i)以及1 2^(-i)的结构,因此每一次叠代运算中有关于输入值x的计算在电路上可以透过一个移位寄存器以及一个加法器来实现;此外,由于参数xa(i)、xb(i)、limit_up(i)、limit_low(i)都是常数,因此可以事先将这些参数的对数值预先计算出来并建立出一个查找表,以供每一次叠代运算中计算输出值y使用,亦即每一次叠代运算中输出值y的计算在电路上可以仅透过一个加法器来实现。综上所述,每一次叠代运算总共只需要一次移位运算、两次加法运算以及两个比较运算便可以实现,因此可以有效的降低对数计算过程中的复杂度,且也降低了电路的制造及设计成本。

20.图2为根据本发明一实施例的对数计算电路200的示意图。如图2所示,对数计算电路200包含了一叠代运算电路210以及一选择电路220,其中叠代运算电路210系用来执行图1所示的每一次叠代运算,而选择电路220则是根据目前所进行的第i次迭代运算来传送相关的参数至迭代运算电路210,例如上述的i、xa(i)、xb(i)、limit_up(i)、limit_low(i)以及目前的输入值x及输出值y。在本实施例中在叠代运算电路210的操作中,叠代运算电路210包含了移位寄存器202以及两个加法器204、206,其中移位寄存器202以及加法器204系用来执行步骤108、110中有关于输入值x的操作,亦即x=x*xa(i)或是x=x*xb(i),其中图示的x’用来表示下一次叠代运算电路210的输入值x;且加法器206系用来执行步骤108、110中有关于输出值y的操作,亦即y=y-ln(xa(i))或是y=y-ln(xb(i)),其中图示的y’用来表示下一次叠代运算输出值y。由于本领域具有通常知识者再搭配有关于图1所述的流程后应能轻易了解到对数计算电路200的操作,故对数计算电路200的操作细节不再重述。

21.简要归纳本发明,在本发明的对数计算方法及相关的电路中,透过特殊的参数设定以及叠代运算流程,可以让每一个叠代运算仅需要透过一个移位寄存器及两个加法器便可实现,因此,可以有效的降低对数计算过程中的复杂度,且也降低了电路的制造及设计成本。

22.以上所述仅为本发明之较佳实施例,凡依本发明申请专利范围所做之均等变化与修饰,皆应属本发明之涵盖范围。

23.【符号说明】

24.100~112:步骤

25.200:对数计算电路

26.210:叠代运算电路

27.202:移位寄存器

28.204:加法器

29.206:加法器

30.220:选择电路

31.x,x’:输入值

32.xa(i):参数

33.xb(i):参数

34.y,y’:输出值

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。