1.涉及一种连续时间线性均衡电路。

背景技术:

2.有线通信是指通过基于有线的通信技术进行的数据传输。一般来说,有线通信被视为是所有类型的通信服务中最稳定的。宽带有线数据通信系统,例如通用串行总线(usb)、高清多媒体接口(hdmi)、显示端口(dp)、外围组件互连高速(pcie)、thunderbolt、收敛输入输出(cio)和任何其它高速宽带有线通信,需要在其电子电路系统内进行处理的级。

3.宽带数据通信系统电路可包括若干级,所述级包括用于均衡、放大和/或重新驱动每一数据信道的信号的模块。通常一个级无法提供足够的增益或均衡。在此类多级系统中,在每一级之间使用中间缓冲器可能是必要的。然而,时常,与均衡器、放大器和驱动器相比,缓冲器消耗甚至更多的电力,这使得具有更少缓冲块的设计在系统中更有利,尤其在用于低压(即,~1.8v或更低)系统时。所需的是一种高效连续时间线性均衡电路(ctle)。

技术实现要素:

4.在一个实施例中,公开了一种连续时间线性均衡(ctle)电路。所述ctle包括有源ctle电路,所述有源ctle电路包括经由阶数高于一的退化阻抗电路而彼此耦合的差分晶体管对。

5.在另一实施例中,公开了一种连续时间线性均衡(ctle)电路。所述ctle电路包括无源ctle电路和有源ctle电路。所述有源ctle电路包括差分晶体管对。所述无源ctle的输出被配置成驱动所述差分晶体管对的栅极/基极。

6.在一些例子中,所述有源ctle电路包括退化阻抗电路。所述退化阻抗电路为二阶退化阻抗电路,所述二阶退化阻抗电路包括串联耦合的电容器、电阻器和电感器以及与所述串联并联耦合的电阻器。

7.在一些其它实施例中,所述退化阻抗电路为三阶退化阻抗电路,所述三阶退化阻抗电路包括串联耦合的电容器、电阻器和电感器以及与所述串联并联耦合的电阻器。电容器和电阻器并联耦合到所述电感器。

8.在一个例子中,所述无源ctle电路包括一阶阻抗电路或二阶阻抗电路。在一些实施例中,还可使用第三或更高阻抗电路。所述一阶阻抗电路包括并联耦合到第一电阻器并通过第二电阻器耦合到输出的电容器。所述二阶阻抗电路包括第一电容器,所述第一电容器并联耦合到第一电阻器,并且通过第二电阻器耦合到输出且通过电感器和第二电容器耦合到接地。

9.在一些实施例中,所述ctle电路可包括增益级以补偿由所述无源ctle电路引起的dc损耗。所述无源ctle被配置成将极点和零点添加到所述ctle电路的ac响应。

10.在一些实施例中,所述有源ctle包括具有电阻组件的退化阻抗电路,并且所述有源ctle电路被配置成通过调整所述电阻组件来调整dc增益。

11.在另一实施例中,公开了一种ctle电路。所述ctle电路包括无源ctle电路,所述无源ctle电路包括二阶阻抗电路和有源ctle电路,所述有源ctle电路包括差分晶体管对。所述无源ctle的输出被配置成驱动所述差分晶体管对的栅极/基极。所述有源ctle电路包括耦合在差分晶体管对的源极/发射极之间的更高阶退化阻抗电路。所述ctle电路另外包括与所述有源ctle电路耦合的dc增益级,以补偿由所述无源ctle电路引起的dc损耗。在一些例子中,所述更高阶退化阻抗电路包括串联耦合的电容器、电阻器和电感器以及与所述串联并联耦合的电阻器。在另一例子中,所述更高阶退化阻抗电路包括串联耦合的电容器、电阻器和电感器以及与所述串联并联耦合的电阻器,其中电容器和电阻器并联耦合到所述电感器。

附图说明

12.图1示出常规的连续时间线性均衡(ctle)电路。

13.图2示出根据一个或多个实施例的ctle电路的框图。

14.图3描绘根据一个或多个实施例的ctle电路。

15.图4a

‑

4c示出根据一个或多个实施例的用于图3的ctle电路的退化阻抗电路的实施例。

16.图4d

‑

4e示出根据一个或多个实施例的用于图3的ctle电路的无源ctle电路的实施例。

17.图5示出根据一个或多个实施例的图3的ctle电路的增益曲线。

18.在整个描述中,可以使用类似的参考标号来标识类似的元件。

具体实施方式

19.应容易理解,如本文中大体描述且在附图中示出的实施例的组件可以各种各样不同的配置来布置和设计。因此,如图中所表示的各种实施例的具体实施方式并非旨在限制本公开的范围,而仅仅是表示各种实施例。尽管在图式中呈现了实施例的各个方面,但是除非特别地指示,否则图式未必按比例绘制。

20.在不脱离本发明的精神或基本特性的情况下,可以其它具体形式实施本发明。所描述的实施例在所有方面均被视为仅是说明性的而非限制性的。因此,本发明的范围由所附权利要求书而不是由此具体实施方式指示。属于权利要求书等同含义和范围内的所有变化均涵盖在权利要求书的范围内。

21.贯穿本说明书对特征、优点或类似语言的提及并不暗示可通过本发明实现的所有特征和优点应该在或就在本发明的任何单个实施例中。实际上,涉及特征和优点的语言应理解成意指结合实施例描述的具体特征、优点或特性包括在本发明的至少一个实施例中。因此,贯穿本说明书对特征和优点的论述以及类似语言可以(但未必)指代同一实施例。

22.此外,本发明的所描述特征、优点和特性可以任何合适的方式在一个或多个实施例中组合。相关领域的技术人员应认识到,鉴于本文中的描述,本发明可在无具体实施例的特定特征或优点中的一个或多个的情况下实践。在其它情况下,可在某些实施例中识别出可能不存在于本发明的所有实施例中的额外特征和优点。

23.贯穿本说明书对“一个实施例”、“实施例”或类似语言的提及意指结合所指示实施

例描述的特定特征、结构或特性包括在本发明的至少一个实施例中。因此,贯穿本说明书的短语“在一个实施例中”、“在实施例中”和类似语言可以(但未必)全部指同一实施例。

24.本文中所描述的实施例使用“一个”级ctle来提供较高信道损耗补偿。ctle的更多级引起更多功耗。因此,有利的是在一个级中提供较高信道损耗补偿。

25.本文中所描述的一个或多个实施例使用更高阶退化阻抗来提供受控良好的较高信道损耗补偿。另外,更高阶退化升高和滚降ctle频率响应(即,带外衰减同样更快,这抑制更多带外噪声和频带的急剧增加)。

26.退化阻抗可以是2阶、3阶、4阶或任何自定义阶数/形状以实现所需信道损耗补偿。按照定义,更高阶退化阻抗的使用并不影响ctle的最大ac增益,但添加更多低频损耗将增加峰化增益(在奈奎斯特(nyquist)频率下dc增益与ac增益之间的差)。在gb/s数据速率下,传输信道的集肤效应和介电损耗引起频率相关损耗,由此产生符号间干扰(isi)。随着计算系统变得更快,由于符号间干扰(isi)在较慢的传输介质和系统中会快速衰退,因此对于设计者来说,信号完整性也成为一个重要问题。由于所使用的信道有带宽限制,因此在高频率下传输芯片外数据会产生isi。所述isi在高频率下引起显著衰减,因此降低性能且增加误码率(ber)。为了克服这些限制,在高速串行链路中使用均衡器。xu zhang等人的标题为“具有可编程峰化增益的低电源线性均衡器(low supply linear equalizer with programmable peaking gain)的第10,447,507号美国专利描述了一种线性均衡器,所述专利以引用的方式并入本文中。wu的标题为“二阶连续时间线性均衡器(second order continuous time linearequalizer)”的第us20080101450a1号美国专利公开描述了ctle的各种例子,所述专利以引用的方式并入本文中。

27.在接收器(rx)前端处采用ctle以补偿信道损耗且提供均衡的低抖动输出数据。另外,线性均衡器确保前驱均衡以及后驱均衡,而不是像决策反馈均衡(dfe)这样的非线性均衡技术,后者仅实现后驱均衡。印刷电路板(pcb)上的较长电缆或连接路径意味着在一定频率下的更多插入损耗。ctle电路的主要功能是补偿损耗。ctle将补偿损耗且在感兴趣的频率带宽中提供相当平坦的增益。

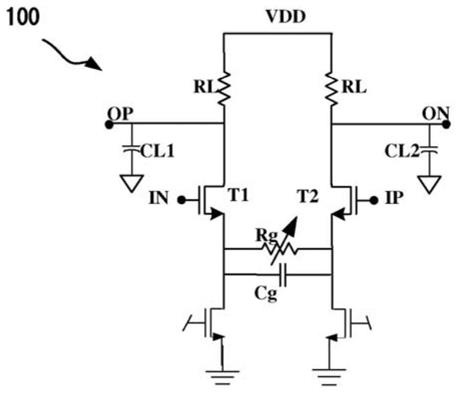

28.图1示出常规的ctle电路100。常规的ctle电路100包括输入端口in、ip和输出端口op、on。输出端口op耦合到电容器cl1,所述电容器cl1耦合到接地。类似地,输出端口on耦合到电容器cl2,所述电容器cl2耦合到接地。输入端口in与晶体管t1的栅极耦合,且输入端口ip与晶体管t2的栅极耦合。晶体管t1的端和晶体管t2经由可变电阻器rg和电容器cg耦合在一起。电阻器rg和电容器cg彼此并联耦合。

29.均衡器实现传递函数,所述传递函数可被调谐以使得其与信道传递函数相反。如果被适当调谐,则均衡器改进接收器性能参数,例如,ber和抖动容限。如图1中所示的具有一个零点和两个极点的常规电容源极退化的一阶ctle提供控制ctle传递函数的形状的有限能力。传递函数的极点和零点为频率,对于所述频率,传递函数的分母和分子的值分别变为零。系统的极点和零点的值确定系统是否稳定,以及系统执行得多好。在常规的ctle中,dc增益、传递函数和最大(峰值)增益可被限定为:

30.adc=2r

l

/(rg 2/g

m

)

ꢀꢀꢀ

(1)

31.h(s)≈adc(1 s rgcg)/((1 s rgcg/(1 g

m rg/2)(1 s r

l

c

l

))

ꢀꢀꢀ

(2)

32.apk=g

m

*r

l

ꢀꢀꢀ

(3)

33.其中g

m

为差分对晶体管t1、t2的跨导。等式1示出rg调整将改变dc增益和零点位置。然而,难以从此常规ctle电路获得高峰化增益和相等增益步长,而不串联添加常规ctle的多个级。然而,添加多个级可能消耗更多电力且在装置上占用更多空间且产生更多噪声。

34.尽管基于cmos的电路在图3中示出,还可使用基于bjt的电路来实施图3的电路。对于常规的ctle电路100,可通过改变不同的用于cmos电路的源极退化电阻器或用于bjt电路的发射极退化电阻器来完成调谐。在峰值增益固定(峰值增益=g

m

*r

l

)时,dc衰减将变化。另外,当退化电阻器被改变时,由于电容器固定时退化rc对产生的零点(ω

zero

=1/rg cg),峰化频率会变化。为了保持峰值频率固定,调谐/调整rg和cg以获得不同峰化增益且维持相同峰化频率。对于高速应用,常规ctle电路100的调谐方法可能会引发问题。由于电路的寄生组件,使用离散调谐步骤,意味着对于每个步骤应存在不同的电阻器和电容器设置。

35.常规ctle 100的有源组件引入寄生电阻和电容。这些寄生电阻和电容无法被很好地控制,并且将引起在低频率下的非预期的峰化或减小预期的调谐范围,因为寄生电阻器和电容器需要被计算为电容和电阻的总量,这可能引起调谐范围的减小。如果使用变容二极管作为调谐电容器,则其将减少电路的寄生。然而,调谐可能是不可预测的,因为变容二极管的准确值是未知的。变容二极管是非线性的。这可降低ctle的总体线性。

36.图2示出为无源ctle 202与有源ctle 204的组合的ctle 200。可在有源ctle 204的输出级处添加增益级206。将无源ctle 202添加到有源ctle 204可能引起低频损耗,但还将向ctle 200的ac响应提供额外的极点和零点,所述ac响应提供额外ac损耗补偿。增益级206补偿dc损耗。在一些实施例中,如果dc损耗在可容许限值内,则增益级206可省略。

37.图3示出ctle电路300,所述ctle电路300包括包含耦合到输入端口i

n

、i

p

的z1和z2的无源ctle 202以及包含差分晶体管对t1、t2的有源ctle 204。有源ctle还包括阻抗z

g

和z

l

。有源ctle包括输出端口o

p

、o

n

。电源v

dd

耦合到阻抗z

l

。z

l

可以是纯电阻阻抗,或还可以是包括电感器的更高阶阻抗。无源ctle的输出驱动晶体管t1、t2的栅极。

38.如等式3所限定的ctle 300的峰值增益不会根据z

g

阻抗而改变,且如等式4所限定的dc增益不会随着阻抗z

g

的ac分量而改变。

39.h(s)~g

m z

l

/(1 g

m

*z

g

)

ꢀꢀꢀ

(4)

40.增加退化阻抗z

g

的电阻部分将减小dc增益,但将增加峰化增益。可按可实现较高带宽的方式调整(多个)极点和零点。可通过调整ctle 300的阻抗组件的值来实现所要带宽中的输入信号的高频频谱与低频频谱之间的已知比率。使z

g

为“更高阶”阻抗增大了ctle曲线的正斜率和负斜率(同样更高的信道损耗补偿和更多带外抑制)。可通过将电感器添加到z

g

来实施更高阶阻抗。

41.图4a、4b、4c示出各种实施例中的z

g

的实际实施方案。图4a示出z

g

的一阶阻抗实施方案400。因此,z

g 400包括串联耦合到电容器c1的电阻器r1和与电阻器r2串联耦合的电容器c1。包括r1、c1和r2的所述串联并联耦合到电阻器r3。图4b提供z

g

的二阶阻抗实施方案402,其中电容器c1被电容器c2、电感器l1和电容器c3的串联代替。图4c示出z

g

的三阶阻抗实施方案404。在三阶阻抗实施方案404中,电感器l1(在图4b中)被并联耦合到电感器l2的电阻器r4、电容器c4和电阻器r5的串联代替。所有阻抗已经以对称形式示出以符合ctle 300的全差分形式。

42.一般来说,ctle电路300的增益可如下限定:

43.增益=g

m

*z

l

/(1 g

m

z

g

),其中z

g

=z(s)限定退化阻抗阶数。如果z(s)=r,则阶数=0。如果z(s)=r||sc或r sc,则阶数=1。如果z(s)=r sl 1/sc=(src s^2lc 1)/sc,则阶数=2。一般来说,z(s)=k(1 a.s b.s^2 c.s^3 ...)限定阻抗的阶数。

44.无源ctle 202实际上执行为具有所要ac响应的无源滤波器。无源ctle的传递函数可表示为:

45.out/in=z2/(z1 z2)

ꢀꢀꢀꢀ

(5)

46.图4d示出在一个实施例中的无源ctle电路406的单端形式。因此,无源ctle电路406包括与电阻器r6并联耦合的电容器c5,以及与输入端口耦合的电容器c5的一个端。电容器c5与电阻器r7耦合,且电阻器r7还与接地耦合。电阻器r7与电阻器r8耦合,且电阻器r8与电容器c6耦合。电容器c6在一端上与接地耦合且在另一端上耦合到输出端口。

47.图4e示出无源ctle电路408,所述无源ctle电路408与无源ctle电路406相比提供更高阶的阻抗。在无源ctle电路408中,电阻器r7被与电感器l3串联耦合的电容器c7代替。在一些其它实施例中,还可将电阻器添加到电容器c7和电感器l3的组合。

48.图4a

‑

4e中所示的阻抗示出许多可能的电路布置中的一种。尽管示出至多3阶的阻抗,但本文中所描述的实施例也适用于比3阶更高阶的阻抗。

49.图5示出增益对频率的图500。图500包括两个曲线502、504。曲线502为具有任选增益级206的ctle 200的响应,且曲线504示出无增益级206的ctle 200的响应。曲线502和曲线504示出类似响应,但曲线502示出增强的dc电平。曲线502包括表示z

g

的阶数的子曲线1、2、3(例如,1=一阶、2=二阶且3=三阶实施方案)。如图所示,曲线502的子曲线3示出与较低阶阻抗实施方案相比频率增益的急剧上升。

50.尽管本文中的方法的操作以特定次序示出和描述,但可更改每个方法的操作次序,使得某些操作可以逆序执行或使得某些操作可至少部分地与其它操作并行执行。在另一实施例中,可以间断和/或交替的方式实施不同操作的指令或子操作。

51.还应注意,本文所描述的方法的操作中的至少一些操作可使用软件指令来实施,所述软件指令存储在计算机可用存储介质上以供计算机执行。作为例子,计算机程序产品的实施例包括用于存储计算机可读程序的计算机可用存储介质。

52.所述计算机可用或计算机可读存储介质可以是电子、磁性、光学、电磁、红外或半导体系统(或设备或装置)。非暂时性计算机可用和计算机可读存储介质的例子包括半导体或固态存储器、磁带、可拆卸计算机磁盘、随机存取存储器(ram)、只读存储器(rom)、硬磁盘和光盘。光盘的当前例子包括具有只读存储器的高密度磁盘(cd

‑

rom)、具有读取/写入的高密度磁盘(cd

‑

r/w)和数字视频光盘(dvd)。

53.可替换的是,本发明的实施例可以完全实施于硬件中或实施于包含硬件和软件元件两者的实施方案中。在使用软件的实施例中,软件可以包括但不限于固件、常驻软件、微码等。

54.虽然已描述和示出本发明的具体实施例,但本发明不限于如此描述和示出的部分的具体形式或布置。本发明的范围将由本文所附权利要求书及其等效物限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。