技术特征:

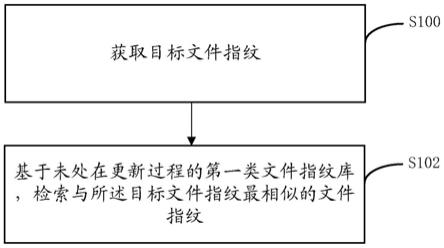

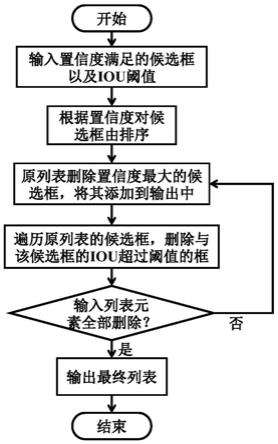

1.一种基于fpga的低延时非极大值抑制方法,其特征在于,该方法包括以下步骤:步骤1:根据当前应用场景下目标检测的数据集,初始化数据集所需输出回归框数上限l、iou阈值iou_th、置信度阈值conf_th,以及串行的候选框;步骤2:根据初始化参数以及资源限制,计算中间缓存的最大候选框数m

max

、算法实际输出回归框数上限l’;步骤3:获取串行的候选框中第一个候选框,并存储至中间缓存中;步骤4:获取串行的候选框中下一个候选框box

i

,根据中间缓存候选框的置信度从大到小依次计算候选框box

i

与中间缓存候选框之间的iou并更新中间缓存,其中,若iou>iou_th,则根据两者置信度大小删去的中间缓存候选框或标记候选框box

i

已覆盖,并根据置信度大小重新排序,得到更新的中间缓存候选框;若iou≤iou_th,则判断候选框box

i

是否已经被缓存或覆盖,并根据置信度大小重新排序,得到更新的中间缓存候选框;直至所有串行的候选框获取完毕;步骤5:输出中间缓存候选框前l’个回归框,作为非极大值抑制计算结果;步骤6:计算在当前应用场景下采用该算法的精度,与精度要求比较,若不满足,降低数据集所需的输出回归框数上限l,返回至步骤2,否则,完成算法以及硬件实现。2.根据权利要求1所述的基于fpga的低延时非极大值抑制方法,其特征在于,所述步骤2计算中间缓存的最大候选框数m

max

、算法实际输出回归框数上限l’,具体步骤如下:步骤2

‑

1:根据串行候选框输入的间隔时钟周期数n,得到该输入条件下允许的中间缓存候选框数最大值m

max

‑

time

=n

‑

5;步骤2

‑

2:根据数据集所需输出回归框数上限l、iou

阈值

、置信度

阈值

,计算数据集所需中间缓存候选框数m

max

‑

dataset

,具体步骤如下:步骤2

‑2‑

1:寻找m个候选框,要求这m个候选框与另一候选框间iou均超过阈值,且这m个候选框间彼此iou未超过iou阈值,计算m的最大值m

max

‑

single

,步骤2

‑2‑

2:计算数据集所需中间缓存候选框数m

max

‑

dataset

=1 (l

‑

1)

×

m

max

‑

single

;步骤2

‑

3:计算过程中间缓存候选框数取数据集所需中间缓存候选框数与输入条件下允许的中间缓存候选框数最大值中较小值,即m

max

=min(m

max

‑

dataset

,m

max

‑

time

);步骤2

‑

4:单张图最终输出回归框数上限选择该应用场景下的输出回归框数上限与计算过程中间缓存候选框数中较小值,即l’=min(m

max

,l)。3.根据权利要求1所述的基于fpga的低延时非极大值抑制方法,其特征在于,具体是:步骤4

‑

1:设定目前比较的中间缓存候选框地址为0,将输入候选框已缓存、输入候选框已被覆盖的标志置为0;步骤4

‑

2:计算输入候选框与对应地址的中间缓存候选框间的iou,判断是否超过iou阈值;步骤4

‑

3:若iou超过阈值,比较输入候选框与对应地址的中间缓存候选框置信度大小,更新中间缓存候选框,具体步骤如下:步骤4

‑3‑

1:若输入候选框置信度超过对应地址的中间缓存候选框,则判断输入候选框状态,更新中间缓存候选框,具体步骤如下:

步骤4

‑3‑1‑

1:若输入候选框已缓存或已被覆盖,则直接删去该中间缓存候选框,将之后地址的中间缓存候选框前移,最后一个中间缓存候选框置为0;步骤4

‑3‑1‑

2:否则用输入候选框替换该中间缓存候选框,将输入候选框已缓存标志置为1;步骤4

‑3‑

2:若输入候选框置信度未超过对应地址的中间缓存候选框,则输入候选框已被覆盖的标志置为1;步骤4

‑

4:若iou未超过阈值,比较输入候选框与对应地址的中间缓存候选框置信度大小,更新中间缓存候选框,具体步骤如下:步骤4

‑4‑

1:若输入候选框置信度超过对应地址的中间缓存候选框,则判断输入候选框状态,更新中间缓存候选框,具体步骤如下:步骤4

‑4‑1‑

1:若输入候选框已缓存或已被覆盖,则无需操作;步骤4

‑4‑1‑

2:否则将输入候选框插入到该候选框之前,将之后地址的中间缓存候选框后移,若缓存候选框数量已达到上限则删去置信度最小的候选框,将输入候选框已缓存标志置为1;步骤4

‑4‑

2:若输入候选框置信度未超过对应地址的中间缓存候选框,则无需操作;步骤4

‑

5:若中间缓存候选框地址已经到达底部,则跳转至步骤5;否则中间缓存候选框地址加一,跳转至步骤4

‑

2。4.一种基于fpga的低延时非极大值抑制装置,其特征在于,包括:中间候选框缓存模块、iou计算模块、中间缓存更新逻辑模块与地址控制模块;地址控制模块,负责产生输入候选框的计数信号与当前正在比较的中间缓存候选框地址信号,将其传递至中间候选框缓存模块与中间缓存更新逻辑模块;中间候选框缓存模块,负责缓存中间候选框、根据地址控制模块的当前正在比较的中间缓存候选框地址信号将该候选框信息传递至iou计算模块、根据中间缓存更新逻辑模块产生的更新指令以及当前输入候选框box

i

更新中间缓存候选框;iou计算模块,负责计算中间候选框缓存模块传递的候选框与当前输入候选框box

i

的iou与置信度大小关系,将其传递至中间缓存更新逻辑模块;中间缓存更新逻辑模块,负责根据iou计算模块产生的iou与置信度大小关系以及当前输入候选框box

i

的状态信号,产生更新控制信号与当前输入候选框box

i

的状态信号。5.根据权利要求4所述的基于fpga的低延时非极大值抑制装置,其特征在于,所述的更新控制信号包括是否缓存当前输入候选框box

i

、是否删除当前正在比较的中间缓存框;状态信号包括当前输入候选框box

i

是否已经覆盖、是否已经缓存。6.根据权利要求4或5所述的基于fpga的低延时非极大值抑制装置,其特征在于,所述的装置的输入为串行候选框,同一时间最多仅有一个候选框输入,输出为回归框,其中,中间候选框缓存数量等参数根据权利要求2确定,对于单个应用不再更改。

技术总结

一种基于FPGA的低延时非极大值抑制方法与装置,省去现有各NMS算法均需要的整体排序步骤,降低启动延时,且其可通过灵活的参数配置满足不同的计算速度与精度要求。采用流水线架构,可与流水线架构的神经网络加速器兼容,缩短了目标检测算法整体延迟。缩短了目标检测算法整体延迟。缩短了目标检测算法整体延迟。

技术研发人员:贺光辉 余希 李杰 张津铭 蒋剑飞 王琴 景乃锋 毛志刚

受保护的技术使用者:上海航天测控通信研究所

技术研发日:2021.08.12

技术公布日:2021/11/24

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。