1.本技术涉及半导体电路设计领域,特别涉及一种交错信号产生电路。

背景技术:

2.在半导体电路设计中,经常会用到等间距交错(stagger)信号,等间距交错信号指每间隔固定延迟产生的信号。

3.对于同步信号而言,通常借助时钟信号来产生等间距交错信号;对于异步信号而言,通过插入延时单元(delay cell)来产生所需的等间距交错信号,信号之间的延迟可以根据需求插入相应的延时单元实现。

4.然而申请人发现,采用同步信号产生等间距交错信号的方式,等间距交错信号之间的延迟必须是时钟周期的整数倍,等间距交错信号之间延迟大小的可控性差;采用异步信号产生等间距交错信号的方式,虽然信号之间的延迟可控性好,但会明显增大形成的电路版图的面积和电路的功耗。

技术实现要素:

5.本技术实施例提供一种交错信号产生电路,以产生周期可调整的第一脉冲信号和第二脉冲信号,并根据第一脉冲信号和第二脉冲信号产生延时可控的延时信号,且电路版图的面积小,电路的功耗小。

6.为解决上述技术问题,本技术实施例提供了一种交错信号产生电路,包括:交错脉冲产生电路,用于根据第一控制信号生成第一脉冲信号,并根据第二控制信号生成第二脉冲信号,第一控制信号与第二控制信号为反相信号,第一脉冲信号与第二脉冲信号为交错脉冲信号;延时信号输出电路,包括g个信号输出电路,g为大于等于2的整数,信号输出电路用于接收输入信号、第一脉冲信号和第二脉冲信号,输出延时输出信号;其中,非第一级信号输出电路均接收前一级信号输出电路输出的延时输出信号作为当前级信号输出电路的输入信号,第一级信号输出电路接收初始输入信号作为第一级信号输出电路的输入信号;信号输出电路生成的延时输出信号的上升沿,与接收的前一级信号输出电路输出的延时输出信号或所述初始输入信号的上升沿,具有第一延迟;信号输出电路生成的延时输出信号的下降沿,与接收的前一级信号输出电路输出的延时输出信号或所述初始输入信号的下降沿,具有第二延迟。

7.与相关技术相比,根据控制信号产生第一振荡信号,即控制信号在处于有效电平时,产生周期一定的第一振荡信号;根据倍率选择信号,基于第一振荡信号产生第二振荡信号,即基于倍率选择信号,改变第一振荡信号的周期,以产生相应的第二振荡信号;然后将第二振荡信号作为信号源产生脉冲信号,产生的脉冲信号的脉冲周期与第二振荡信号的振荡周期相同;在产生脉冲信号的过程中,若倍率选择信号改变,调整第一振荡信号的周期的幅度改变,以使产生的第二振荡信号的周期变化,从而产生周期可调整的第一脉冲信号和第二脉冲信号;并且根据第一脉冲信号和第二脉冲信号产生延时可控的延时信号,延时信

号相对于输入信号而言,上升沿存在第一延时,下降沿存在第二延时;第一延时为第一脉冲信号的脉冲周期,第二延时为第二脉冲信号的脉冲周期,因此可以通过调整第一脉冲信号和第二脉冲信号脉冲周期的方式,调整延时信号的延时时间;同时,调整延时信号的延时时间无需接入更多延时单元,从而简化电路结构,使得电路版图的面积小,电路的功耗小。

8.另外,第一脉冲信号和第二脉冲信号的脉冲周期相等。通过控制第一脉冲信号的脉冲周期和第二脉冲信号的脉冲周期一致,保证产生的延时信号的上升沿和下降沿的延时时间一致,从而保证延时信号是对输入信号的延时。

9.另外,交错脉冲产生电路包括:信号产生模块,用于根据激活信号生成第一控制信号和第二控制信号;第一脉冲产生单元,用于根据第一控制信号生成第一脉冲信号;第二脉冲产生单元,用于根据第二控制信号生成第二脉冲信号。

10.另外,信号产生模块包括:复位单元,接收第一复位信号以及激活信号,并基于第一复位信号和激活信号生成第一控制信号;反向单元,接收第一控制信号,并基于第一控制信号生成第二控制信号。

11.另外,信号产生模块还包括:复位信号产生单元,用于根据第一复位信号和第一控制信号生成第二复位信号,以使当第一复位信号为复位状态时,第二复位信号也处于复位状态,当第一复位信号为非复位状态时,第二复位信号基于第一控制信号的变化沿产生复位窄脉冲。

12.另外,第一脉冲产生单元,包括:振荡模块,接收第一控制信号,且根据第一控制信号生成第一振荡信号;周期调整模块,接收第一振荡信号以及倍率选择信号,并输出第二振荡信号,且第二振荡信号的周期为基于倍率选择信号调整第一振荡信号后的周期;脉冲转换模块,接收第二振荡信号,并输出脉冲信号,第一脉冲信号的脉冲基于第二振荡信号的信号变化沿产生,且第一脉冲信号的脉冲周期与第二振荡信号的振荡周期相同。

13.另外,第二脉冲产生单元与第一脉冲产生单元具有相同的电路结构。

14.另外,周期调整模块包括:延时单元,接收第一振荡信号,并基于第一振荡信号生成振荡调整信号,振荡调整信号的周期与第一振荡信号周期的不同;选择单元,接收倍率选择信号,并基于倍率选择信号选择第一振荡信号或振荡调整信号作为第二振荡信号。

15.另外,延时单元包括e个串联的延时子单元,振荡调整信号包括e个延时信号,e为正整数;第一级延时子单元,用于根据第一振荡信号生成第一延时信号,并将第一延时信号输入到第二级延时子单元中;第f级延时子单元,用于根据第f

‑

1延时信号生成第f延时信号,f小于等于e,且大于等于2的正整数。

16.另外,选择单元包括:倍率选择器,倍率选择器包括第一选择输入端、第二选择输入端、选择信号端和选择输出端,第一选择输入端和第二选择输入端分别用于接收振荡调整信号中的一个信号或第一振荡信号,选择信号端用于接收倍率选择信号,选择输出端用于输出第二振荡信号。

17.另外,振荡模块包括:振荡单元以及连接在振荡单元中的触发单元;触发单元,用于接收复位信号以及第一控制信号,并基于复位信号和第一控制信号触发振荡单元;振荡单元触发后,用于根据第一控制信号生成第一振荡信号。

18.另外,振荡单元包括:a个反相器串联形成的环形振荡器,a为正奇数。

19.另外,振荡模块还包括:第一反相器组,包括串联的b个反相器,b为正偶数;第一选

择单元,用于接收第一选择信号,并基于第一选择信号,将第一反相器组串接在环形振荡器中的相邻反相器之间。

20.另外,脉冲转换模块包括:脉冲转换器,用于接收第二振荡信号,且基于第二振荡信号生成第一脉冲信号。

21.另外,信号输出电路包括:第一控制模块,接收第一脉冲信号和输入信号,并输出第一调整信号,第一调整信号的第一预设沿相对于输入信号的上升沿具有第一延时,第一延时为第一脉冲信号的脉冲周期;第二控制模块,接收第二脉冲信号和输入信号,并输出第二调整信号,第二调整信号的第二预设沿相对于输入信号的下降沿具有第二延时,第二延时为第二脉冲信号的脉冲周期;信号输出模块,接收第一调整信号和第二调整信号,并输出延时输出信号,延时输出信号的上升沿基于第一调整信号的第一预设沿产生,延时输出信号的下降沿基于第二调整信号的第二预设沿产生。

22.另外,信号输出模块包括:第一接收单元,接收第一脉冲信号和第一调整信号,并在第一调整信号为有效电平期间,生成第一脉冲控制信号,第一脉冲控制信号的脉冲相位与第一脉冲信号的脉冲相位相同;第二接收单元,接收第二脉冲信号和第二调整信号,并在第二调整信号为有效电平期间,生成第二脉冲控制信号,第二脉冲控制信号的脉冲相位与第二脉冲信号的脉冲相位相同;锁存单元,接收第一脉冲控制信号和第二脉冲控制信号,并生成延时输出信号。

23.另外,第一接收单元还用于接收第一控制信号,第一接收单元用于在第一调整信号和第一控制信号为有效电平期间,根据第一脉冲信号生成第一脉冲控制信号。

24.另外,第二接收单元还用于接收第二控制信号,第二接收单元用于在第二调整信号和第二控制信号为有效电平期间,根据第二脉冲信号生成第二脉冲控制信号。

25.另外,延时信号输出电路还包括:初始信号输出电路,包括第一控制模块、第二控制模块和信号输出模块;所述第一控制模块,用于接收第一脉冲信号和第一电源信号,并根据所述第一脉冲信号和所述第一电源信号,生成所述第一调整信号;所述第二控制模块,用于接收第二脉冲信号和第二电源信号,并根据所述第二脉冲信号和所述第二电源信号,生成所述第二调整信号;所述信号输出模块,用于根据所述第一调整信号和所述第二调整信号,生成所述初始输入信号。

附图说明

26.图1和图2为本技术实施例提供的交错脉冲产生电路的结构示意图;

27.图3为本技术实施例提供的信号产生模块的具体电路示意图;

28.图4和图5为本技术实施例提供的脉冲产生电路的结构示意图;

29.图6为本技术实施例提供的振荡模块的具体电路示意图;

30.图7为本技术实施例提供的延时单元的结构示意图;

31.图8为本技术实施例提供的选择单元的结构示意图;

32.图9和图10为本技术实施例提供的周期调整模块的电路示意图;

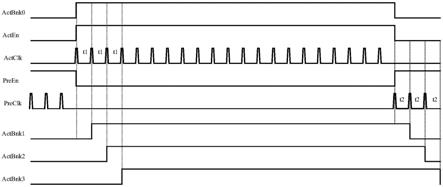

33.图11为本技术实施例提供的脉冲产生电路中信号的时序示意图;

34.图12为本技术实施例提供的交错脉冲产生电路中信号的时序示意图;

35.图13为本技术实施例提供的信号输出电路的结构示意图;

36.图14为本技术实施例提供的第一控制模块的具体电路示意图;

37.图15为本技术实施例提供的第二控制模块的具体电路示意图;

38.图16为本技术实施例提供的信号输出模块的结构示意图;

39.图17和图18为本技术实施例提供的信号输出模块的具体电路示意图;

40.图19为本技术实施例提供的信号输出电路中信号的时序示意图;

41.图20和图21为本技术实施例提供的延时信号输出电路的结构示意图;

42.图22为本技术实施例提供的延时信号输出电路的具体电路示意图;

43.图23为本技术实施例提供的延时信号输出电路中信号输出电路的具体电路示意图;

44.图24为本技术实施例提供的延时信号输出电路中信号的时序示意图。

具体实施方式

45.采用同步信号产生等间距交错信号的方式,等间距交错信号之间的延迟必须是时钟周期的整数倍,等间距交错信号之间延迟大小的可控性差;采用异步信号产生等间距交错信号的方式,虽然信号之间的延迟可控性好,但会明显增大形成的电路版图的面积和电路的功耗。

46.为解决上述问题,本技术实施例提供了一种交错信号产生电路,包括:交错脉冲产生电路,用于根据第一控制信号生成第一脉冲信号,并根据第二控制信号生成第二脉冲信号,第一控制信号与第二控制信号为反相信号,第一脉冲信号与第二脉冲信号为交错脉冲信号;延时信号输出电路,包括g个信号输出电路,g为大于等于2的整数,信号输出电路用于接收输入信号、第一脉冲信号和第二脉冲信号,输出延时输出信号;其中,非第一级信号输出电路均接收前一级信号输出电路输出的延时输出信号作为当前级信号输出电路的输入信号,第一级信号输出电路接收初始输入信号作为第一级信号输出电路的输入信号;信号输出电路生成的延时输出信号的上升沿,与接收的前一级信号输出电路输出的延时输出信号或所述初始输入信号的上升沿,具有第一延迟;信号输出电路生成的延时输出信号的下降沿,与接收的前一级信号输出电路输出的延时输出信号或所述初始输入信号的下降沿,具有第二延迟。

47.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合附图对本技术的各实施例进行详细的阐述。然而,本领域的普通技术人员可以理解,在本技术各实施例中,为了使读者更好地理解本技术而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本技术所要求保护的技术方案。以下各个实施例的划分是为了描述方便,不应对本技术的具体实现方式构成任何限定,各个实施例在不矛盾的前提下可以相互结合,相互引用。

48.图1和图2为本技术实施例提供的交错脉冲产生电路的结构示意图,图3为本技术实施例提供的信号产生模块的具体电路示意图,图4和图5为本技术实施例提供的脉冲产生电路的结构示意图,图6为本技术实施例提供的振荡模块的具体电路示意图,图7为本技术实施例提供的延时单元的结构示意图,图8为本技术实施例提供的选择单元的结构示意图,图9和图10为本技术实施例提供的周期调整模块的电路示意图,图11为本技术实施例提供的脉冲产生电路中信号的时序示意图,图12为本技术实施例提供的交错脉冲产生电路中信

号的时序示意图,图13为本技术实施例提供的信号输出电路的结构示意图,图14为本技术实施例提供的第一控制模块的具体电路示意图,图15为本技术实施例提供的第二控制模块的具体电路示意图,图16为本技术实施例提供的信号输出模块的结构示意图,图17和图18为本技术实施例提供的信号输出模块的具体电路示意图,图19为本技术实施例提供的信号输出电路中信号的时序示意图,图20和图21为本技术实施例提供的延时信号输出电路的结构示意图,图22为本技术实施例提供的延时信号输出电路的具体电路示意图,图23为本实施例提供的延时信号输出电路中信号输出电路的具体电路示意图,图24为本技术实施例提供的延时信号输出电路中信号的时序示意图,以下结合附图对本实施例提供的交错信号产生电路作进一步详细说明。

49.交错信号产生电路,包括:

50.交错脉冲产生电路,用于根据第一控制信号acten生成第一脉冲信号actclk,并根据第二控制信号preen生成第二脉冲信号preclk,第一控制信号acten和第二控制信号preen为反相信号,第一脉冲信号actclk和第二脉冲信号preclk为交错脉冲信号。本实施例所称交错脉冲信号表示根据反相的信号(第一控制信号acten和第二控制信号preen)产生的脉冲信号(第一脉冲信号actclk和第二脉冲信号preclk),也可以为在不同期间分别有效的脉冲信号。

51.延时信号输出电路,包括g个信号输出电路,g为大于等于2的整数,信号输出电路用于接收输入信号、第一脉冲信号actclk和第二脉冲信号preclk,输出延时输出信号。

52.其中,非第一级信号输出电路均接收前一级信号输出电路输出的延时输出信号作为当前级信号输出电路的输入信号,第一级信号输出电路接收初始输入信号作为第一级信号输出电路的输入信号;信号输出电路生成的延时输出信号的上升沿,与接收的前一级信号输出电路输出的延时输出信号的上升沿,具有第一延迟;信号输出电路生成的延时输出信号的下降沿,与接收的前一级信号输出电路输出的延时输出信号的下降沿,具有第二延迟。

53.在本实施例中,第一脉冲信号actclk的脉冲周期为t1,第二脉冲信号preclk的脉冲周期为t2,第一脉冲信号actclk的脉冲周期和第二脉冲信号preclk的脉冲周期相等;在其他实施例中,第一脉冲信号和第二脉冲信号的脉冲周期可以不同。

54.具体地,参考图1,交错脉冲产生电路300,包括:信号产生模块303,用于根据激活信号active生成第一控制信号acten和第二控制信号preen,第一控制信号acten和第二控制信号preen为反相信号。其中,激活信号active即外部输入的激活指令,信号产生模块303用于根据外部激活指令生成互为反向信号的第一控制信号acten和第二控制信号preen。

55.更具体地,参考图2,信号产生模块303包括:

56.复位单元313,接收第一复位信号fnacten以及激活信号active,并基于第一复位信号fnacten和激活信号active生成第一控制信号acten。

57.第一复位信号fnacten即外部输入的复位指令,用于对复位单元313进行复位;具体地,当复位单元313复位后,若复位单元313接收的激活信号active为有效电平,复位单元313产生第一控制信号acten。

58.反向单元323,接收第一控制信号acten,并基于第一控制信号acten生成第二控制信号preen。

59.在本实施例中,信号产生模块303还包括:复位信号产生单元333,用于根据第一复位信号fnacten和第一控制信号acten生成第二复位信号fnpreen,以使当第一复位信号fnacten为复位状态时,第二复位信号fnpreen也处于复位状态,当第一复位信号fnacten为非复位状态时,第二复位信号fnpreen基于第一控制信号acten的变化沿产生复位窄脉冲。

60.在本实施例中,信号产生模块303还包括:选择信号产生单元343,用于接接受选择信号fnadjdly,并基于选择信号fnadjdly生成选择信号组,选择信号组包括选择信号fnadjdly和反相选择信号fnadjdlyn,选择信号fnadjdly与反相选择信号fnadjdlyn为反相信号。

61.需要说明的是,在本实施例中选择信号fnadjdly包括用于调控脉冲产生电路100的倍率选择信号fnadjdlyx、第一选择信号fnadjdly1和第二选择信号fnadjdly2。

62.在一个例子中,参考图3,复位单元313包括复位与非门403和复位反向器404,复位反相器404连接复位与非门403的输出端,复位与非门403用于接接收第一复位信号fnacten和激活信号active。

63.反向单元323包括连接复位单元313的输出反相器405,用于根据第一控制信号acten生成第二控制信号preen。

64.复位信号产生单元333包括脉冲转换装置406,用于检测第一控制信号acten的变化沿(如上升沿),产生脉冲控制信号;输出与非门407和输出反相器408,输出与非门407还用于接收第一复位信号fnacten,此时输出反相器408输出第二复位信号fnpreen。

65.选择信号产生单元343包括:串联的第一选择反相器401和第二选择反相器402,第一选择反相器401的输出端连接第二选择反相器402的输入端,用于光根据选择信号fnadjdly生成选择信号组。

66.继续参考图2,交错脉冲产生电路300,还包括:第一脉冲产生单元301和第二脉冲产生单元302;第一脉冲产生单元301具体包括脉冲产生电路,用于根据第一控制信号acten生成第一脉冲信号actclk;第二脉冲产生单元302具体包括脉冲产生电路,用于根据第二控制信号preen生成第二脉冲信号preclk;第一脉冲信号actclk与第二脉冲信号preclk为交错脉冲信号。

67.在本实施例中,第二脉冲产生单元302与第一脉冲产生单元301具有相同的电路结构。本实施例以第一脉冲产生单元301的脉冲产生电路100进行介绍,其中,第一控制信号acten和第二控制信号preen属于控制信号rasen;第一复位信号fnacten和第二复位信号fnpreen属于复位信号fnrasen。

68.参考图4,第一脉冲产生单元301包括脉冲单元电路100,包括:振荡模块101,接收控制信号rasen,且根据控制信号rasen生成第一振荡信号osc1;具体地,当控制信号rasen处于有效电平时,振荡模块101生成第一振荡信号osc1;在本实施例中,假设第一振荡信号osc1的周期为t。

69.在一个例子中,当接收到控制信号rasen,且控制信号rasen为有效电平时,振荡模块101起振以产生第一振荡信号osc1。

70.进一步地,参考图5,振荡模块101包括振荡单元111以及连接在振荡单元111中的触发单元121;触发单元121用于接收复位信号fnrasen以及控制信号rasen,并基于复位信号fnrasen和控制信号rasen触发振荡单元111;振荡单元111触发后,根据控制信号rasen生

成第一振荡信号osc1。

71.需要注意的是,此处描述的“基于复位信号fnrasen和控制信号rasen触发振荡单元111”中,“基于”的含义包括但不限定于:当复位信号fnrasen处于非复位状态,且控制信号rasen为有效电平,触发单元121触发振荡单元111。

72.复位信号fnrasen即外部输入的复位指令,用于对触发单元121进行复位;具体地,当触发单元121复位后,若触发单元121接收的控制信号rasen为有效电平,触发单元121触发振荡单元111,以使振荡单元111产生第一振荡信号osc1。

73.在一个例子中,参考图6,振荡单元111包括a个反相器串联形成的环形振荡器,a为正奇数;a可以为5、7、9、11等,在本实施例中以a=7,即7个反相器串联形成的环形振荡器为例进行举例说明,并不构成对本实施例的限定,在具体应用中,可以根据实际需求选择环形振荡器中反相器的数量。触发单元121包括第一与非门211和第二与非门212,第一与非门211的输出端连接至第二与非门212的一输入端,第一与非门211的一输入端和第二与非门212的输出端用于接入环形振荡器;第一与非门211与第二与非门212中,其中一者用于接收控制信号rasen,另一者用于接收复位信号fnrasen;需要说明的是,图3中给定的第一与非门211用于接收控制信号rasen,第二与非门212用于接收复位信号fnrasen并不构成对本实施例的限定,在其他实施例中也可以采用第二与非门接收控制信号,第一与非门接收复位信号。

74.在本实施例中,振荡模块101还包括:第一反相器组215,包括串联的b个反相器,b为正偶数;b可以为2、4、6等,在本实施例中以b=2,即2个反相器串联形成的第一反相器组215为例进行举例说明,并不构成对本实施例的限定,在具体应用中,可以根据实际需求选择第一反相器组215中反相器的数量。第一选择单元(未图示),用于接收第一选择信号fnadjdly1,并基于第一选择信号fnadjdly1,将第一反相器组215串接在环形振荡器中的相邻反相器之间。

75.具体地,第一反相器组215中反相器为b个的目的在于:保证环形振荡器中反相器的总数为奇数个;具体地,第一选择单元(未图示)包括第一选择器214,用于根据第一选择信号fnadjdly1和反向第一选择信号fnadjdly1n选通第一支路或第二支路;其中,第一支路作为环形振荡器中相邻反相器的连接电路,第二支路将第一反相器组215串接至环形振荡器相邻反相器的连接电路中;将第一反相器组215接入环形振荡器的目的是:增加环形振荡器中反相器的个数,从而增大振荡单元111产生的第一振荡信号osc1的周期,在本实施例中假设增加第一反相器组215的反相器后,生成的第一振荡信号osc1为1.2t;由于第一反相器组215接入环形振荡器是通过第一选择信号fnadjdly1控制,即可通过外部输入的第一选择信号fnadjdly1调整振荡单元111生成的第一振荡信号osc1的周期。

76.在本实施例中,振荡模块101还包括:第二反相器组217,包括串联的c个反相器,c为正偶数;c可以为2、4、6等,在本实施例中以c=4,即4个反相器串联形成的第二反相器组217为例进行举例说明,并不构成对本实施例的限定,在具体应用中,可以根据实际需求选择第二反相器组217中反相器的数量。第二选择单元(未图示),用于接收第二选择信号fnadjdly2,并基于第二选择信号fnadjdly2,将第二反相器组217串接在环形振荡器中的相邻反相器之间。

77.具体地,第二反相器组217中反相器为c个的目的在于:保证环形振荡器中反相器

的总数为奇数个;具体地,第二选择单元(未图示)包括第二选择器216,用于根据第二选择信号fnadjdly2和反向第二选择信号fnadjdly2n选通第三支路或第四支路;其中,第三支路作为环形振荡器中相邻反相器的连接电路,第四之路将第二反相器组217串接至环形振荡器相邻反相器的连接电路中;将第二反相器组217接入环形振荡器的目的是:增加环形振荡器中反相器的个数,从而增大振荡单元111产生的第一振荡信号osc1的周期,在本实施例中假设增加第二反相器组217的反相器后,生成的第一振荡信号osc1为1.4t;由于第二反相器组217接入环形振荡器是通过第二选择信号fnadjdly2控制,即可通过外部输入的第二选择信号fnadjdly2调整振荡单元111生成的第一振荡信号osc1的周期。

78.在本实施例中b和c可以设置为任意正偶数,在具体应用于可以根据振荡单元111产生的第一振荡信号osc1所需的变化,合理设置b和c的值;另外,本实施例中说明了两个反相器组的实现方式,在本实施例的基础上继续加入第三反相器组、第四反相器组的实现方案,都应该属于本技术的保护范围。

79.另外,通过第一反相器组215和第二反向器组217同时接入环形振荡器,可以实现不同幅度的改变第一振荡信号osc1的周期;此时根据第一选择信号fnadjdly1和第二选择信号fnadjdly2的不同生成的第一振荡信号osc1的周期表1所示:

80.表1 osc1周期表

[0081][0082][0083]

继续参考图4,脉冲产生电路100包括:周期调整模块102,接收第一振荡信号osc1以及倍率选择信号fnadjdlyx,并输出第二振荡信号osc2,第二振荡信号osc2的周期为第一振荡信号osc1基于倍率选择信号fnadjdlyx调整后的周期,倍率选择信号fnadjdlyx为外部输入的选择指令,用于调整第二振荡信号osc2的周期,即脉冲产生电路可通过外部输入的倍率选择信号fnadjdlyx调整周期调整模块102生成的第二振荡信号osc2的周期。

[0084]

在一个例子中,可以利用第一振荡信号osc1生成振荡调整信号osct,然后根据倍率选择信号fnadjdlyx选择第一振荡信号osc1作为第二振荡信号osc2输出,或选择振荡调整信号osct作为第二振荡信号osc2输出。也可以根据倍率选择信号fnadjdlyx判断是否需要生成振荡调整信号osct,即采用先判断再生成的方式,输出第二振荡信号osc2。

[0085]

参考图5,周期调整模块102包括:延时单元112,接收第一振荡信号osc1,并基于第一振荡信号osc1生成振荡调整信号osct,振荡调整信号osct的周期与第一振荡信号osc1的周期不同;选择单元122,接收倍率选择信号fnadjdlyx,并基于倍率选择信号fnadjdlyx选择第一振荡信号osc1或振荡调整信号osct作为第二振荡信号osc2。

[0086]

在一个例子中,参考图7,延时单元112包括:d触发器201,d触发器包括输入端d、时钟端clk和clkn、复位端rn和输出端q,时钟端clk和clkn用于接收第一振荡信号osc1和反向

第一振荡信号osc1n,复位端rn用于接收复位信号fnrasen,输出端q用于串联触发反相器202并连接至输入端d,且用于输出振荡调整信号osct。本领域技术人员可知,此时输出的振荡调整信号osct的周期是第一振荡信号osc1周期的两倍。

[0087]

参考图8,选择单元122包括倍率选择器203,倍率选择器203包括第一选择输入端、第二选择输入端、选择信号端和选择输出端,第一选择输入端和第二选择输入端分别用于接收第一振荡信号osc1和振荡调整信号osct,选择信号端用于接收倍率选择信号fnadjdlyx和反向倍率选择信号fnadjdlyxn,选择输出端用于输出第二振荡信号osc2,通过倍率选择信号fnadjdlyx可以大幅度的改变振荡信号的周期;在本实施例中,采用第一选择输入端接收第一振荡信号osc1,第二选择输入端接收振荡调整信号osct;在其他实施例中,也可以是第一选择输入端接收振荡调整信号osct,第二选择输入端接收第一振荡信号osc1。

[0088]

此时,根据第一选择信号fnadjdly1、第二选择信号fnadjdly2和倍率选择信号fnadjdlyx的不同生成的第二振荡信号osc2的周期如表2所示:

[0089]

表2 osc2的周期表

[0090]

fnadjdlyxfnadjdly1fnadjdly2osc2的周期000t0101.2t0011.4t0111.6t1002t1102.4t1012.8t1113.2t

[0091]

在本实施例中,延时单元112包括e个串联的延时子单元,振荡调整信号osct包括e个延时信号,e为正整数;第一级延时子单元,用于根据第一振荡信号osc1生成第一延时信号osc11,并将第一延时信号osc11输入到第二级延时子单元中;第f级延时子单元,用于根据第f

‑

1级延时信号osc1f

‑

1生成第f延时信号osc1f,f为小于等于e,且大于等于2正整数。

[0092]

具体地,第f级延时子单元包括:d触发器,d触发器包括输入端、时钟端和、复位端和输出端,时钟端和用于接收第f

‑

1延时信号osc1f

‑

1和反向第f

‑

1延时信号osc1f

‑

1n,复位端用于接收复位信号,输出端用于串联触发反相器并连接至输入端,且用于输出第f延时信号osc1f。本领域技术人员可知,此时输出的第f延时信号osc1f的周期是第f

‑

1延时信号osc1f

‑

1周期的两倍。

[0093]

参考图9,延时单元112包括3个串联的延时子单元,分别为第一级延时子单元221、第二级延时子单元223和第三级延时子单元225;其中,第一级延时子单元221用于根据第一振荡信号osc1生成第一延时信号osc11,第一延时信号osc11的周期是第一振荡信号osc1周期的两倍;第二级延时子单元223用于根据第一延时信号osc11生成第二延时信号osc12,第二延时信号osc12的周期是第一延时信号osc11周期的两倍;第三级延时子单元225用于根据第二延时信号osc12生成第三延时信号osc13,第三延时信号osc13的周期是第二延时信号osc12周期的两倍。

[0094]

在一个例子中,选择单元122基于倍率选择信号fnadjdlyx选择第一振荡信号osc1或振荡调整信号osct作为第二振荡信号osc2,包括:基于倍率选择信号fnadjdlyx选择第e

‑

1延时信号osc1e

‑

1或第e延时信号osc1e作为第二振荡信号osc2。

[0095]

在本实施例中,选择单元122基于倍率选择信号fnadjdlyx选择第一振荡信号osc1或振荡调整信号osct作为第二振荡信号osc2,包括:基于倍率选择信号fnadjdlyx选择第二延时信号osc12或第三延时信号osc13第二振荡信号osc2。其中,第一级延时单元221和第二级延时子单元223用于扩大输出的第二振荡信号osc2的周期。

[0096]

此时根据第一选择信号fnadjdly1、第二选择信号fnadjdly2和倍率选择信号fnadjdlyx的不同生成的第二振荡信号osc2的周期如表3所示:

[0097]

表3 osc2的周期表

[0098][0099][0100]

在另一个例子中,选择单元122包括e个串联的选择子单元,倍率选择信号fnadjdlyx包括对应于每个选择子单元的子倍率选择信号;第一级选择子单元,用于根据对应的子倍率选择信号,选择第一振荡信号osc1或第一延时信号osc11输入到第二级选择子单元中;第f级选择子单元,用于根据对应的子倍率选择信号,选择第f

‑

1级选择子单元的输出信号或第f延时信号osc1f输入到第f 1级选择子单元中;第e级选择子单元,用于根据对应的子倍率选择信号,选择第e

‑

1级选择子单元的输出信号或振荡调整信号osct作为第二振荡信号osc2,f为小于e,且大于等于2的正整数,即选择单元122的第一选择输入端和第二选择输入端分别用于接收振荡调整信号(第1延时信号osc11、第2延时信号osc12

……

第f延时信号osc1f)中的一个信号或第一振荡信号osc1,并根据倍率选择信号选择振荡调整信号(第1延时信号osc11、第2延时信号osc12

……

第f延时信号osc1f)中的一个信号或第一振荡信号osc1中的一个信号作为第二振荡信号osc2。

[0101]

具体地,第f级选择子单元包括:倍率选择器,倍率选择器包括第一选择输入端、第二选择输入端、选择信号端和选择输出端、第一选择输入端和第二选择输入端分别用于接收第f

‑

1级选择子单元的输出信号和第f延时信号osc1f,选择信号端用于接收对应的子倍率选择信号,选择输出端用于输出第f

‑

1级选择子单元的输出信号或第f延时信号osc1f;在

本实施例中,采用第一选择输入端接收第f

‑

1级选择子单元的输出信号,第二选择输入端接收第f延时信号osc1f;在其他实施例中,也可以是第一选择输入端接收第f延时信号osc1f,第二选择输入端接收第f

‑

1级选择子单元的输出信号。

[0102]

参考图10,选择单元122包括3个串联的选择子单元,分别为第一级选择子单元227、第二级选择子单元228和第三级选择子单元229;其中,第一级选择子单元227用于选择第一振荡信号osc1或第一延时信号osc11输入到第二级选择子单元228,第二级选择子单元228用于选择第一级选择子单元227的输出信号或第二延时信号osc12输入到第三级选择子单元229,第三级选择子单元229用于选择第二级选择子单元228的输出信号或第三延时信号osc13作为振荡调整信号osct。通过多个选择子单元的串联,实现了第二振荡信号osc2周期更多的变化选择。

[0103]

需要说明的是,在具体应用过程中,倍率选择信号fnadjdlyx、第一选择信号fnadjdly1和第二选择信号fnadjdly2可以通过多位二进制数实现,即选择信号是一个多位二进制数,其中一位作为倍率选择信号fnadjdlyx,一位作为第一选择信号fnadjdly1,一位作为第二选择信号fnadjdly2。

[0104]

继续参考图4,脉冲产生电路100包括:脉冲转换模块103,接收第二振荡信号osc2,并输出脉冲信号oscclk,脉冲信号oscclk的脉冲基于第二振荡信号的上升沿或下加沿产生,且脉冲信号oscclk的脉冲周期与第二振荡信号的振荡周期相同。

[0105]

具体地,参考图5,脉冲转换模块103包括:脉冲转换器113,用于接收第二振荡信号osc2,且基于第二振荡信号osc2生成脉冲信号oscclk。

[0106]

在一个例子中,当脉冲转换器113检测到第二振荡信号osc2的上升沿后输出一个向上的窄脉冲,脉冲转换器113的输出端还可以通过串联反相器,以输出一个向下的窄脉冲。在另一个例子中,当脉冲转换器113检测到第二振荡信号osc2的上升沿后输出一个向下的窄脉冲,脉冲转换器113的输出端还可以通过串联反相器,以输出一个向上的窄脉冲。另外,本实施例中脉冲转换器113是基于第二振荡信号osc2的上升沿工作,在其他实施例中,脉冲转换器还可以基于第二振荡信号的下降沿工作。

[0107]

需要注意的是,此处描述的“基于第二振荡信号osc2生成脉冲信号oscclk”中,“基于”的含义包括但不限定于:检测到第二振荡信号osc2的上升沿,或者检测到第二振荡信号osc2由低电平变为高电平(高电平变为低电平)后产生脉冲信号oscclk的窄脉冲。

[0108]

需要说明的是,在本实施例中,脉冲信号oscclk是基于第二振荡信号osc2的上升沿产生,在其他实施例中,脉冲信号还可以根据第二振荡信号的下降沿产生。

[0109]

参考图11,在控制信号rasen为有效电平期间,振荡模块101产生周期为t的第一振荡信号osc1,周期调整模块102根据倍率选择信号fnadjdlyx调整第二振荡信号osc2(osc2

′

)的周期。

[0110]

具体地,若在控制信号rasen为有效电平期间改变倍率选择信号fnadjdlyx,此时产生的第二振荡信号osc2存在周期变化,假设由周期t变为周期2t,此时产生的脉冲信号oscclk中脉冲周期也由周期t变为周期2t;若在控制信号rasen为有效电平之前改变倍率选择信号fnadjdlyx,此时产生的第二振荡信号osc2

′

不存在周期变化,产生的脉冲信号oscclk

′

中脉冲周期也不存在脉冲周期的变化。

[0111]

参考图12,当激活信号active为有效电平时,产生的第一控制信号acten为有效电

平;第一脉冲产生单元301用于根据第一控制信号acten产生周期为t第一振荡信号osc1和周期为2t的第二振荡信号osc2;在本实施例中,第二振荡信号osc2与第一振荡信号osc1的周期一致,第一脉冲信号actclk基于第二振荡信号osc2的上升沿产生。第二脉冲产生单元302用于格局第二控制信号preen产生周期为t的第一振荡信号osc1〃和周期为2t的第二振荡信号osc2〃;在本实施例中,第二振荡信号osc2〃与第一振荡信号osc1〃的周期一致,第二脉冲信号preclk基于第二振荡信号osc2〃的上升沿产生。此时产生的第一脉冲信号actclk与第二脉冲信号preclk为交错脉冲信号。

[0112]

具体地,延时信号输出电路,包括:g个信号输出电路500,g为大于等于2的整数,信号输出电路用于接收输入信号、第一脉冲信号actclk和第二脉冲信号preclk,输出延时输出信号;其中,非第一级信号输出电路均接收前一级信号输出电路输出的延时输出信号作为当前级信号输出电路的输入信号,第一级信号输出电路接收初始输入信号作为第一级信号输出电路的输入信号;信号输出电路生成的延时输出信号的上升沿,与接收的前一级信号输出电路输出的延时输出信号或所述初始输入信号的上升沿,具有第一延迟;信号输出电路生成的延时输出信号的下降延,与接收的前一级信号输出电路输出的延时输出信号或所述初始输入信号的下降沿,具有第二延迟。

[0113]

具体地,参考图13,信号输出电路500包括:第一控制模块501,接收第一脉冲信号actclk和输入信号actbnk0,并输出第一调整信号actlat,第一调整信号actlat的第一预设沿相对于输入信号actbnk0的上升延具有第一延迟,第一延迟为第一脉冲信号actclk的脉冲周期。

[0114]

在一个例子中,可以利用第一脉冲信号actclk的上升沿或下降沿去采样输入信号actbnk0,然后输出第一调整信号actlat;或检测到第一脉冲信号actclk的上升沿或下降沿后延迟输出输入信号actbnk0,从而获取第一调整信号actlat。

[0115]

在本实施例中,以第一预设沿为上升沿为例进行举例说明;具体地,输入信号actbnk0为外部输入信号(相比信号输出电路500来说),信号输出电路500用于根据输入信号actbnk0产生延时输出信号actbnk1;其中,延时输出信号actbnk1的上升沿基于第一调整信号actlat的上升沿产生,第一调整信号actlat的上升沿与输入信号actbnk0的上升沿具有第一延迟;即延时输出信号actbnk1的上升沿与输入信号actbnk0的上升沿具有第一延迟,第一延迟为第一脉冲信号actclk的脉冲周期,由此可知,外部输入的第一脉冲信号actclk用于调整延时输出信号actbnk1的上升沿的延迟。需要说明的是,在其他实施例中,第一预设沿还可以为下降沿。

[0116]

需要注意的是,此处描述的“延时输出信号actbnk1的上升沿基于第一调整信号actlat的第一预设沿产生”中,“基于”的含义包括但不限定于:检测到第一调整信号actlat的第一预设沿即产生延时输出信号actbnk1的上升沿,或者检测到第一调整信号actlat由低电平变为高电平(高电平变为低电平)后产生延时输出信号actbnk1的上升沿。

[0117]

在一个例子中,参考图14,第一控制模块501包括第一d触发器511,时钟端用于接收第一脉冲信号actclk,复位端用于接收第一复位信号fnacten,输入端用于接收输入信号actbnk0,输出端用于输出第一调整信号actlat。

[0118]

继续参考图13,信号输出电路500还包括:第二控制模块502,接收第二脉冲信号preclk和输入信号actbnk0,并输出第二调整信号prelat,第二调整信号prelat的第二预设

沿相对于输入信号actbnk0的下降沿具有第二延迟,第二延迟为第二脉冲信号preclk的脉冲周期。

[0119]

在本实施例中,以第二预设沿为上升沿为例进行举例说明;具体地,延时输出信号actbnk1的下降沿基于第二调整信号prelat的上升沿产生,第二调整信号prelat的上升沿与输入信号actbnk0的下降沿具有第二延迟;即延时输出信号actbnk1的下降沿与输入信号actbnk0的下降沿具有第二延迟,第二延迟为第二脉冲信号preclk的脉冲周期,由此可知,外部输入的第二脉冲信号preclk用于调整延时输出信号actbnk1的下降沿的延迟。需要说明的是,在其他实施例中,第二预设沿还可以为下降沿。

[0120]

需要注意的是,此处描述的“延时输出信号actbnk1的下降沿基于第二调整信号prelat的第二预设沿产生”中,“基于”的含义包括但不限定于:检测到第二调整信号prelat的第二预设沿即产生延时输出信号actbnk1的下降沿,或者检测到第二调整信号prelat由低电平变为高电平(高电平变为低电平)后产生延时输出信号actbnk1的下降沿。

[0121]

在一个例子中,参考图15,第二控制模块502包括第二d触发器512,时钟端用于接收第二脉冲信号preclk,复位端用于接收第二复位信号fnpreen,输入端用于接收输入信号actbnk0,输出端串联反相器后输出第二调整信号prelat。

[0122]

另外,在本实施例中,第一脉冲信号actclk的其中一个脉冲与输入信号actbnk0的上升沿对齐,第二脉冲信号preclk的其中一个脉冲与输入信号actbnk0的下降沿对齐。需要说明的是,此处描述的“对齐”并不一定是理想情况下的完全对齐,可以包括由于电路延迟等因素导致的上升沿/下降沿存在细微差别。通过第一脉冲信号actclk的其中一个脉冲与输入信号actbnk0的上升沿对齐,以保证对第一调整信号actlat的第一信号沿与输入信号actbnk0的上升沿的第一延迟的准确性;通过第二脉冲信号preclk的其中一个脉冲与输入信号actbnk0的下降沿对齐,以保证对第二调整信号prelat的第二信号沿与输入信号actbnk0的下降沿的第二延迟的准确性。

[0123]

继续参考图13,信号输出电路500还包括:信号输出模块503,接收第一调整信号actlat和第二调整信号prelat,并输出延时输出信号actbnk1,延时输出信号actbnk1的上升沿基于第一调整信号actlat的第一预设沿产生,延时输出信号actbnk1的下降沿基于第二调整信号prelat的第二预设沿产生。

[0124]

具体地,参考图16,信号输出模块503包括:第一接收单元513,接收第一脉冲信号actclk和第一调整信号actlat,并在第一调整信号actlat为有效电平期间,生成第一脉冲控制信号actn,第一脉冲控制信号actn的脉冲相位与第一脉冲信号actclk的脉冲相位相同第二接收单元523,接收第二脉冲信号preclk和第二调整信号prelat,并在第二调整信号prelat为有效电平期间,生成第二脉冲控制信号pren,第二脉冲控制信号pren的脉冲相位与第二脉冲信号preclk的脉冲相位相同。锁存单元533,接收第一脉冲控制信号actn和第二脉冲控制信号pren,并延时输出信号actbnk1。

[0125]

在一个例子中,当检测到第一调整信号actlat为有效电平,基于反相器通过第一脉冲信号actclk生成第一脉冲控制信号actn;当检测到第二调整信号prelat为有效电平,基于反相器通过第二脉冲信号preclk生成第二脉冲控制信号pren。

[0126]

在一个例子中,参考图17,第一接收单元513包括第一接收与非门601,第一接收与非门601包括第一输入端、第二输入端和第一输出端,第一输入端用于接收第一调整信号

actlat,第二输入端用于接收第一脉冲信号actclk,第一输出端用于输出第一脉冲控制信号actn。第二接收单元523包括第二接收与非门602,第二接收与非门602包括第三输入端、第四输入端和第二输出端,第三输入端用于接收第二调整信号prelat,第四输入端用于接收第二脉冲信号preclk,第二输出端用于输出第二脉冲控制信号pren。锁存单元533包括锁存器603,锁存器603包括第五输入端、第六输入端和第三输出端,第五输入端用于接收第一脉冲控制信号actn,第六输入端用于接收第二脉冲控制信号pren,第三输出端用于输出延时输出信号actbnk1。

[0127]

锁存单元603被配置为:第一脉冲控制信号actn和第二脉冲控制信号pren为不同电平时,延时输出信号actbnk1与第二脉冲控制信号pren为相同电平;第一脉冲控制信号actn和第二脉冲控制信号pren为高电平时,锁存单元603保持状态。

[0128]

具体地,第一脉冲信号actn和第二脉冲控制信号pren为高电平时,锁存单元603保持状态;当第一脉冲控制信号actn为高电平,第二脉冲信号控制信号pren为低电平时,锁存单元603为低电平;当第一脉冲控制信号actn为低电平,第二脉冲信号控制信号pren为高电平时,锁存单元603为高电平。

[0129]

在另一例子中,第一接收单元513还用于接收第一控制信号acten,第一接收单元513用于在第一调整信号actlat和第一控制信号acten为有效电平期间,根据第一脉冲信号actclk生成第一脉冲控制信号actn。第二接收单元523还用于接收第二控制信号preen,第二接收单元523用于在第二调整信号prelat和第二控制信号preen为有效电平期间,根据第二脉冲信号preclk生成第二脉冲控制信号pren。

[0130]

参考图18,第一接收与非门601还用于接收第一控制信号acten,第一接收与非门601根据第一时钟信号actclk、第一控制信号acten和第一调整信号actlat生成第一脉冲控制信号actn。第二接收与非门602还用于接收第二控制信号preen,第二接收与非门602根据第二时钟信号preclk、第二控制信号preen和第二调整信号prelat生成第二脉冲控制信号pren。其中,第一控制信号acten和第二控制信号preen为反相信号,第一脉冲信号actclk在第一控制信号acten为有效电平期间存在,第二脉冲信号preclk在第二控制信号preen为有效电平期间存在。通过第一接收与非门601和第二接收与非门分别接收第一控制信号acten和第二控制信号preen,保证第一接收与非门601和第二接收与非门602输出的稳定性。

[0131]

进一步地,第一脉冲信号actclk和第二脉冲信号preclk为交错脉冲信号,交错脉冲信号即根据反相的信号产生的脉冲信号;在本实施例中,第一脉冲信号actclk在第一控制信号acten为有效电平期间存在,且第一脉冲信号actclk的起始脉冲与第一控制信号acten的上升沿对齐;第二脉冲信号preclk在第二控制信号preen为有效电平期间存在,且第二脉冲信号preclk的起始脉冲与第二控制信号preen的上升沿对齐;需要说明的是,此处描述的“对齐”并不一定是理想情况下的完全对齐,可以包括由于电路延迟等因素导致的上升沿/下降沿存在细微差别。

[0132]

在一个例子中,参考图19,输入信号actbnk0、第一脉冲信号actclk和第二脉冲信号preclk为外部输入信号;假设第一脉冲信号actclk的周期为t1,第二脉冲信号preclk的周期为t2。结合图15,第一调整信号actlat基于输入信号actbnk0和第一脉冲信号actclk产生,当第一脉冲信号actclk为高电平时,第一调整信号actlat的次态为输入信号actbnk0的当前状态,造成第一调整信号actlat的上升沿与输入信号actbnk0的上升沿存在第一延迟,

第一延迟为第一脉冲信号actclk的周期,即第一调整信号actlat的上升沿与输入信号actbnk0的上升沿的延迟为t1。结合图16,第二调整信号prelat基于输入信号actbnk0和第二脉冲信号preclk产生,当第二脉冲信号preclk为高电平时,第二调整信号prelat的次态为输入信号actbnk0的当前状态,造成第二调整信号prelat的上升沿与输入信号actbnk0的下降沿存在第二延迟,第二延迟为第二脉冲信号preclk的周期,即第二调整信号prelat的上升沿与输入信号actbnk0的下降沿的延迟为t2。结合图18,为了保证第一接收与非门601和第二接收与非门602输出的稳定性,第一接收与非门601还用于接收第一控制信号acten,第二接收与非门602还用于接收第二控制信号preen,第一控制信号acten和第二控制信号preen为反相信号。此时第一接收与非门601和第二接收与非门602分别产生的第一脉冲控制信号actn和第二脉冲控制信号pren。锁存单元603根据第一脉冲控制信号actn和第二脉冲控制信号pren产生延时输出信号actbnk1,延时输出信号actbnk1的上升沿与输入信号actbnk0的上升沿具有第一延迟,第一延迟为第一脉冲信号actclk的脉冲周期t1;延时输出信号actbnk1的下降沿与输入信号actbnk0的下降沿具有第二延迟,第二延迟为第二脉冲信号preclk的脉冲周期t2。在本实施例中,第一脉冲信号actclk和第二脉冲信号preclk的脉冲周期相等,即延时输出信号actbnk1信号变化沿相对于输入信号actbnk0的信号变化沿存在相等时间的延迟。

[0133]

需要说明的是,图7给出的各信号的时序图,仅用于对本实施例提供的信号输出电路500的电路功能进行解读,并不构成对本实施例的限定;在其他实施例中,可以根据其他输入信号生成对应的延时输入信号;另外,输入信号也可能和第一控制信号不一致。

[0134]

需要说明的是,在其他实施例中,信号输出电路还包括偶数个反相器,反相器与信号输出模块的输出端串联,以增强信号输出电路的驱动能力。

[0135]

参考图20,在本实施例中,以延时信号输出电路700包括7个上述信号输出电路500为例进行具体说明,并不构成对本实施例的限定,具体为第一级信号输出电路701、第二级信号输出电路702、第三级信号输出电路703、第四级信号输出电路704、第五级信号输出电路705、第六级信号输出电路706和第七级信号输出电路707。在其他实施例中,延时信号输出电路包括大于等于2个信号输出电路即可。

[0136]

具体地,第一级信号输出电路701根据初始输入信号actbnk0、第一脉冲信号actclk和第二脉冲信号preclk生成第一级延时输出信号actbnk1,第一级延时输出信号actbnk1的上升沿相对于初始输入信号actbnk0的上升沿存在第一延迟,第一延迟为第一脉冲信号actclk的脉冲周期t1;第一级延时输出信号actbnk1的下降沿相对于初始输入信号actbnk0的下降沿存在第二延迟,第二延迟为第二脉冲信号preclk的脉冲周期t2。

[0137]

第二级信号输出电路702根据第一级延时输出信号actbnk1、第一脉冲信号actclk和第二脉冲信号preclk生成第二级延时输出信号actbnk2,第二级延时输出信号actbnk2的上升沿相对于第一级延时输出信号actbnk1存在第一延迟;第二级延时输出信号actbnk2的下降沿相对于第一级延时输出信号actbnk1存在第二延时。

[0138]

第三级信号输出电路703根据第二级延时输出信号actbnk2、第一脉冲信号actclk和第二脉冲信号preclk生成第三级延时输出信号actbnk3,第三级延时输出信号actbnk3的上升沿相对于第二级延时输出信号actbnk2存在第一延迟;第三级延时输出信号actbnk3的下降沿相对于第二级延时输出信号actbnk2存在第二延时。

[0139]

第四级信号输出电路704根据第三级延时输出信号actbnk3、第一脉冲信号actclk和第二脉冲信号preclk生成第四级延时输出信号actbnk4,第四级延时输出信号actbnk4的上升沿相对于第三级延时输出信号actbnk3存在第一延迟;第四级延时输出信号actbnk4的下降沿相对于第三级延时输出信号actbnk3存在第二延时。

[0140]

第五级信号输出电路705根据第四级延时输出信号actbnk4、第一脉冲信号actclk和第二脉冲信号preclk生成第五级延时输出信号actbnk5,第五级延时输出信号actbnk5的上升沿相对于第四级延时输出信号actbnk4存在第一延迟;第五级延时输出信号actbnk5的下降沿相对于第四级延时输出信号actbnk4存在第二延时。

[0141]

第六级信号输出电路706根据第五级延时输出信号actbnk5、第一脉冲信号actclk和第二脉冲信号preclk生成第六级延时输出信号actbnk6,第六级延时输出信号actbnk6的上升沿相对于第五级延时输出信号actbnk5存在第一延迟;第六级延时输出信号actbnk6的下降沿相对于第五级延时输出信号actbnk5存在第二延时。

[0142]

第七级信号输出电路707根据第六级延时输出信号actbnk6、第一脉冲信号actclk和第二脉冲信号preclk生成第七级延时输出信号actbnk7,第七级延时输出信号actbnk7的上升沿相对于第六级延时输出信号actbnk6存在第一延迟;第七级延时输出信号actbnk7的下降沿相对于第六级延时输出信号actbnk6存在第二延时。

[0143]

参考图21,更具体地,在本实施例中,信号输出电路的第一控制模块还用于接收第一控制信号acten,信号输出电路的第二控制模块还用于接收第二控制信号preen,其中,第一脉冲信号actclk和第二脉冲信号preclk为反相信号;每一级信号输出电路用于根据第一控制信号acten、第二控制信号preen、第一脉冲信号actclk、第二脉冲信号preclk和前一级信号输出电路输出的延时输出信号生成当前级的延时输出信号,通过接收第一控制信号acten和第二控制信号preen,保证信号输出电路输出的稳定性。

[0144]

继续参考图21,本实施例中,延时信号输出电路700还包括:初始信号输出电路710,包括第一控制模块、第二控制模块和信号输出模块;第一控制模块,用于接收第一脉冲信号actclk和第一电源信号vdd,并根据第一脉冲信号actclk和第一电源信号vdd生成第一调整信号(未图示);输出信号输出电路的第二控制模块,用于接收第二脉冲信号preclk和第二电源信号vss并根据第二脉冲信号preclk和第二电源信号vss生成第二调整信号(未图示);信号输出模块,用于根据第一调整信号(未图示)和第二调整信号(未图示)生成初始输入信号。根据第一电源信号vdd和第二电源信号vss生成的初始信号输出电路的延时输出信号,即根据初始信号初始输出电路710输出的初始输入信号actbnk0相比于外部直接输入的输入信号actbnk0可以避免信号输出电路的电路元件造成的延迟。这里的初始信号输出电路710的电路可以与前文描述的信号输出电路一致,在此不再赘述,但本实施例也不限于此。

[0145]

在一个例子中,参考图22和图23,该图以4个信号输出电路构成的延时信号输出电路700为例进行介绍。信号输出电路的第一时钟端actclk用于接收第一脉冲信号actclk;信号输出电路的第二时钟端preclk用于接收第二脉冲信号preclk;信号输出电路的第一控制端acten用于接收第一控制信号acten;信号输出电路的第二控制端preen用于接收第二控制信号preen;信号输出电路的信号输出端actbnk用于输出当前级的延时输出信号;信号输出电路还包括第一信号端actenpre和第二信号端preenpre(信号输出电路的信号输入端),

结合图23,初始信号输出电路的第一信号端actenpre用于接收第一电源信号vdd,初始信号输出电路的第二信号端preenpre用于接收第二电源信号vss;其他信号输出电路的第一信号端actenpre和第二信号端preenpre,用于接收前一级信号输出电路输出的延时输出信号。

[0146]

参考图21和图24,第一级信号输出电路701根据初始输入信号actbnk0生成第一级延时输出信号actbnk1,第二级信号输出电路702根据第一级延时输出信号actbnk1生成第二级延时输出信号actbnk2,第三级信号输出电路703根据第二级延时输出信号actbnk2生成第三级延时输出信号actbnk3,第四级信号输出电路704根据第三级延时输出信号actbnk3生成第四级延时输出信号actbnk4(未图示),第五级信号输出电路705根据第四级延时输出信号actbnk4生成第五级延时输出信号actbnk5(未图示),第六级信号输出电路706根据第五级延时输出信号actbnk5生成第六级延时输出信号actbnk6(未图示),第七级信号输出电路707根据第六级延时输出信号actbnk6生成第七级延时输出信号actbnk7(未图示)。

[0147]

相对于相关技术而言,根据控制信号产生第一振荡信号,即控制信号在处于有效电平时,产生周期一定的第一振荡信号;根据倍率选择信号,基于第一振荡信号产生第二振荡信号,即基于倍率选择信号,改变第一振荡信号的周期,以产生相应的第二振荡信号;然后将第二振荡信号作为信号源产生脉冲信号,产生的脉冲信号的脉冲周期与第二振荡信号的振荡周期相同;在产生脉冲信号的过程中,若倍率选择信号改变,调整第一振荡信号的周期的幅度改变,以使产生的第二振荡信号的周期变化,从而产生周期可调整的第一脉冲信号和第二脉冲信号;并且根据第一脉冲信号和第二脉冲信号产生延时可控的延时信号,延时信号相对于输入信号而言,上升沿存在第一延时,下降沿存在第二延时;第一延时为第一脉冲信号的脉冲周期,第二延时为第二脉冲信号的脉冲周期,因此可以通过调整第一脉冲信号和第二脉冲信号脉冲周期的方式,调整延时信号的延时时间;同时,调整延时信号的延时时间无需接入更多延时单元,从而简化电路结构,使得电路版图的面积小,电路的功耗小。

[0148]

值得一提的是,本实施例中所涉及到的各单元均为逻辑单元,在实际应用中,一个逻辑单元可以是一个物理单元,也可以是一个物理单元的一部分,还可以以多个物理单元的组合实现。此外,为了突出本技术的创新部分,本实施例中并没有将与解决本技术所提出的技术问题关系不太密切的单元引入,但这并不表明本实施例中不存在其它的单元。

[0149]

本领域的普通技术人员可以理解,上述各实施例是实现本技术的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本技术的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。