一种基于像素分享的pwm驱动电路及驱动方法

技术领域

1.本发明涉及micro led pwm驱动,具体为基于像素分享的pwm驱动电路及驱动方法。

背景技术:

2.对于像素阵列,传统驱动方法是通过外围电路实现驱动信号的生成,通过wordline和bitline直接将信号加在发光单元阵列上,实现对发光单元的驱动。不同于传统的驱动电路,像素驱动电路是通过与每个像素发光单元(如led)集成在一起的驱动电路实现对外围信号的处理,从而实现对发光单元的驱动的。由于信号处理模块与发光单元很近,这种方式得到的驱动信号质量更高。

3.当前的像素驱动电路,对于每个发光单元都需要一个信号处理模块,这就导致一个很大的劣势:对于高密度像素阵列,驱动电路需要很大的集成度,晶体管数量庞大,直接导致制造成本更高、对工艺稳定性和质量要求更高。

技术实现要素:

4.发明目的:本发明的目的在于提供一种基于像素分享的低晶体管密度的pwm像素驱动电路;本发明的第二目的在于提供上述pwm像素驱动电路的驱动运行方法。

5.技术方案:本发明的一种基于像素分享的pwm驱动电路,包括若干呈阵列排列的发光单元,对应每一列发光单元,还包括用于提供pwm驱动信号的信号处理模块,每一列中任一个发光单元与信号处理模块信号连接;对应每一行发光单元,还包括用于提供开关信号的第一信号发射器,每一行中任一个发光单元与第一信号发射器信号连接。

6.进一步的,所述发光单元包括用于控制像素开关的选通晶体管、用于提供电流脉冲信号的驱动晶体管以及用于显示发光的micro led,所述选通晶体管的栅极与第一信号发射器连接,选通晶体管的源极与驱动晶体管的栅极连接,所述驱动晶体管的源极与micro led的正极连接,micro led的负极接地。

7.进一步的,所述信号处理模块包括于输出恒定电压的比较器和用于调节电流恒定的电流镜,所述电流镜与比较器信号连接。

8.进一步的,所述比较器包括差分输入级、电平转换级和放大级;所述差分输入级包括第一nmos管m1、第二nmos管m2、第三nmos管m3和第四nmos管m4;所述第一nmos管m1和第二nmos管m2的栅极与选通晶体管连接;所述第一nmos管m1和第二nmos管m2的漏极分别与第三nmos管m3和第四nmos管m4的源极连接;所述第三nmos管m3和第四nmos管m4的栅极与自身的漏极连接,第三nmos管m3和第四nmos管m4的漏极与驱动电源连接;所述电平转换级包括第五nmos管m5,所述第五nmos管m5的栅极与第四nmos管m4的源极连接;所述第五nmos管m5的漏极与驱动电源连接;所述放大级包括第六nmos管m6和第七nmos管m7,所述第七nmos管m7的栅极与第五

nmos管m5的源极连接,所述第七nmos管m7的漏极分别与第六nmos管m6的源极和驱动晶体管连接;所述第六nmos管m6的栅极与自身的漏极连接,所述第六nmos管m6的漏极与驱动电源连接。

9.进一步的,所述电流镜包括电流源i

b

、第八nmos管m8、第九nmos管m9和第十nmos管m10;所述第八nmos管m8的漏极与第一nmos管m1和第二nmos管的源级连接,所述第九nmos管m9的漏极与第五nmos管m5的源级连接,所述第十nmos管m10的漏极与电流源i

b

的一端连接,电流源i

b

的另一端与驱动电源连接;所述第九nmos管m9的栅极、第八nmos管m8的栅极分别与第十nmos管m10的栅极连接,第十nmos管m10的栅极与自身的漏极连接;所述第八nmos管m8、第九nmos管m9和第十nmos管m10的源极接地。

10.进一步的,第一nmos管m1、第二nmos管m2、第三nmos管m3、第四nmos管m4、第五nmos管m5、第六nmos管m6、第七nmos管m7、第八nmos管m8、第九nmos管m9和第十nmos管m10均采用薄膜晶体管。

11.进一步的,对应每一列发光单元,还包括用于提供时分复用信号的第二信号发射器,所述第二信号发射器的输出端与分别信号处理模块的第一nmos管m1的栅极和第二nmos管m2的栅极连接。

12.本发明还保护一种基于像素分享的pwm驱动电路的驱动方法,包括以下步骤:步骤一、提供一种如权利要求1

‑

7任一项所述的基于nmos管的pwm像素电路;步骤二、在一个运行周期内,第一信号发射器将信号分配给位于同一行的发光单元;步骤三、发光单元的选通晶体管被激活,每一列的第二信号发射器将信号分配给对应的信号处理模块;步骤四、信号处理模块将接收的信号转变为pwm电压信号,该信号流经激活的选通晶体管后进入驱动晶体管,驱动晶体管产生pwm电流信号并控制micro led发光;步骤五、第一信号发射器将信号分配给位于另一行的发光单元,并重复步骤三至步骤四,实现对阵列排布的micro led的像素驱动。

13.进一步的,所述步骤四的具体过程为:信号处理模块的差分输入级对接收的信号进行运算并输出至电平转换级,电平转换级对信号的直流电平进行转换,并匹配输出至放大级,放大级将电路电压进行增益放大,并将电压脉冲信号以方波形式输出。

14.进一步的,信号处理模块接收的信号包括电平信号和三角波信号,电平信号和三角波信号分别通过第一nmos管m1和第二nmos管m2传输至差分输入级,电平信号和三角波信号由第二信号发射器提供。

15.本发明的工作原理为:针对阵列排布的micro led,将每一列的发光单元共用一个信号处理模块,实现了低晶体管密度的像素驱动;对于每一列,通过第二信号发射器提供时分复用信号给信号处理模块,并控制对应的发光单元工作;对于每一行,通过第一信号发射器提供开关信号,实现不同行发光单元的独立的开启和关闭,以显著减少的晶体管来达到与现有像素驱动电路几乎相同的驱动效果。

16.有益效果:本发明和现有技术相比,具有如下显著性特点:本发明基于像素共享原理,将多个发光单元共用一个信号处理模块,每个驱动电路的平均晶体管数目显著下降,大幅降低了集成难度以及制备成本,实现了低晶体管密度的像素驱动;采用pwm的信号输出,

对于micro led的驱动能力强,驱动面积与分辨率不受限制,micro led的亮度均匀性强,减少了micro led光色漂移等问题。

附图说明

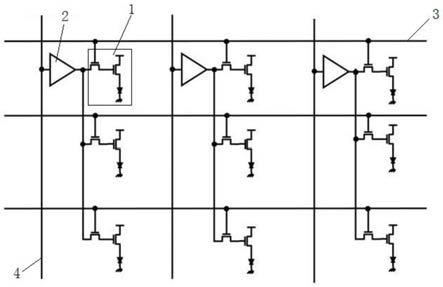

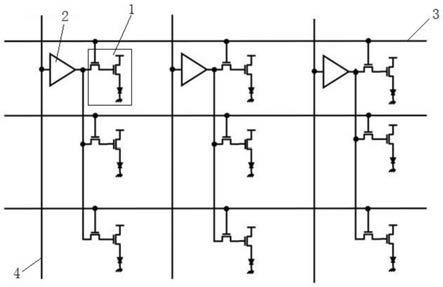

17.图1为本发明的pwm像素电路示意图;图2为本发明发光单元的电路示意图;图3为本发明信号处理模块的电路示意图;图4为实施例中2

×

2的pwm像素阵列示意图;图5为传统2

×

2的pwm像素阵列示意图。

具体实施方式

18.下面结合实施例和附图对本发明作进一步说明。

19.参见图1所示的一种基于像素分享的pwm驱动电路,包括呈矩形阵列方式排列的发光单元1;对应每一列发光单元1,还包括信号处理模块2,以及与信号处理模块2信号连接的第二信号发射器4,每一列中任一个发光单元1与信号处理模块2信号连接;对应每一行发光单元1,还包括第一信号发射器3,每一行中任一个发光单元1与第一信号发射器1信号连接。

20.其中,信号处理模块2为列共用的模块,第二信号发射器4为信号处理模块2提供信号,信号处理模块2可以为同一列的所有发光单元1提供驱动信号;而对于每一行而言,每个发光单元1是并存的,通过第一信号发射器1提供开启或关闭的信号,每一行均设置第一信号发射器1,相互独立的控制每一行发光单元1的开关。

21.参见图2,发光单元1包括用于控制像素开关的选通晶体管11、用于提供电流脉冲信号的驱动晶体管12以及用于显示发光的micro led13,选通晶体管11和驱动晶体管12均采用常规的薄膜晶体管结构,选通晶体管11的源极与驱动晶体管12的栅极连接,驱动晶体管12的源极与micro led13的正极连接,micro led13的负极接地。

22.参加图3,信号处理模块包括于输出恒定电压的比较器和用于调节电流恒定的电流镜,电流镜与比较器信号连接,通过比较器和电流镜的设置可以实现pwm的传递;其中,差分输入级包括第一nmos管m1、第二nmos管m2、第三nmos管m3和第四nmos管m4;第一nmos管m1和第二nmos管m2的栅极与选通晶体管连接;第一nmos管m1和第二nmos管m2的漏极分别与第三nmos管m3和第四nmos管m4的源极连接;第三nmos管m3和第四nmos管m4的栅极与自身的漏极连接,第三nmos管m3和第四nmos管m4的漏极与驱动电源连接;电平转换级包括第五nmos管m5,第五nmos管m5的栅极与第四nmos管m4的源极连接;第五nmos管m5的漏极与驱动电源连接;放大级包括第六nmos管m6和第七nmos管m7,第七nmos管m7的栅极与第五nmos管m5的源极连接,第七nmos管m7的漏极分别与第六nmos管m6的源极和驱动晶体管连接;第六nmos管m6的栅极与自身的漏极连接,第六nmos管m6的漏极与驱动电源连接。具体设计过程中,第一nmos管m1、第二nmos管m2、第三nmos管m3、第四nmos管m4、第五nmos管m5、第六nmos管m6、第七nmos管m7采用薄膜晶体管;第一nmos管m1、第二nmos管m2和第七nmos管m7的沟道长宽比相同;第三nmos管m3、第四nmos管m4、第五nmos管m5、第六nmos管m6的沟道长宽比相同。薄膜晶体管沟道的尺寸设计与差模增益、共模抑制比有关,主要用于控制差分驱动晶体管m1、m2和差分负载晶体管m3、m4的沟道宽长比之比。

23.电流镜包括电流源i

b

、第八nmos管m8、第九nmos管m9和第十nmos管m10;第八nmos管m8的漏极与第一nmos管m1和第二nmos管的源级连接,第九nmos管m9的漏极与第五nmos管m5的源级连接,第十nmos管m10的漏极与电流源i

b

的一端连接,电流源i

b

的另一端与驱动电源连接;第九nmos管m9的栅极、第八nmos管m8的栅极分别与第十nmos管m10的栅极连接,第十nmos管m10的栅极与自身的漏极连接;第八nmos管m8、第九nmos管m9和第十nmos管m10的源极接地。电流源i

b

的输出电流为3.5μa,在驱动电源的作用下,电流源i

b

的输出电流先通过第十nmos管m10,此时第十nmos管m10、第八nmos管m8、第九nmos管m9均处于饱和状态,且三个nmos管的栅极相连,即v

gs10

=v

gs8

=v

gs9

,由晶体管饱和区电流公式i

ds

=0.5μ

n

c

ox

(w/l)(v

gs

‑

v

th

)2,其中μ

n

为载流子的迁移速率,c

ox

为单位面积栅氧化层电容,v

th

为阈值电压,可得通过控制各nmos管w/l大小的方式,可以为差分输入级、电平转换级提供稳定的电流输入。第八nmos管m8、第九nmos管m9和第十nmos管m10均采用薄膜晶体管。

24.本发明中,第二信号发射器4的输出端与第一nmos管m1的栅极和第二nmos管m2的栅极连接,第二信号发射器4的主要作用在于提供时分复用信号,在一个处理周期内,使平均分配到每一行的处理时间相同,以时间作为信号分割的参量,使各行信号在时间轴上互不重叠,达到多路传输控制的目的。其中,第二信号发射器4分别提供电平信号和三角波信号,电平信号通过第一nmos管m1输入,三角波信号通过第二nmos管m2输入;第一信号发射器3的主要作用是控制每一行的选通晶体管11的开关,第一信号发射器3也是每一行启动的开始点。

25.该基于像素分享的pwm驱动电路的驱动过程为:初始阶段,在一个运行周期内,第一信号发射器3将信号分配给位于同一行的发光单元1;然后发光单元的选通晶体管11被激活,每一列的第二信号发射器4将信号分配给对应的信号处理模块2;比较器、电流镜和驱动晶体管与驱动电源连接,电流源i

b

分别通过第八nmos管m8、第九nmos管m9和第十nmos管m10为差分输入级、电平转换级和放大级提供恒定电流;第二信号发射器4将电平信号和三角波信号分别通过第一nmos管m1和第二nmos管m2传输至差分输入级;运行阶段,当电平信号和三角波信号传输到差分级后,此时由于差分对的两个反相器与同一个等效电流源相连,一端的输入信号扰动会影响分配到另一端的电流,从而控制另一端的工作情况,当三角波信号增加时,右端反相器的工作电流增加,相对的,左端反相器分得的电流减小,体现为总体的输出电压out1变大,即差分级对于这两个信号做一个运算,即该级的输出,其中为第一级的电压放大增益;该级输出信号传入电平转换级;在第电平转换级中,信号的直流电平进行转换,此时构成一个共漏极放大器,即m5处于饱和区,m5栅极输入信号的变化会影响m5的输出电导,实现控制输出直流电平的目的,使其能与放大级的直流放大电平相匹配,该级的输出,其中为该级的放大增益,,该级输出信号传入放大级;放大级为电路提供主要增益,该级的结构为反相器,反相器输入输出曲线的斜率越大,该反相器的增益越大,该级的输出即为比较器的输出,其中为该级的电压增益;由于第一级的输入为大信号,信号经电路放大后,必然很快达到饱和,故电路的总体输出为方波信号,即vin2>vin1时输出为高电平,否则为低电平vss。

26.在发光阶段,信号处理模块2输出pwm电压信号,该信号流经激活的选通晶体管11

后进入驱动晶体管12驱动晶体管12产生pwm电流信号并控制micro led13发光;当该行的处理时间完成后,第一信号发射器3控制关闭信号,另一行的第一信号发射器3启动激活选通晶体管11并重复上述的各个阶段,从而完成另一行的发光,以此往复实现对阵列排布的micro led的像素驱动。

27.由于采用pwm的信号输出,可以实现更高的驱动频率,从而保证了每一行micro led亮度的均匀性。

28.参见图4,以2

×

2的pwm像素阵列为例,in1、tri、in2均由第二信号发射器4提供信号,vsw1和vsw2是第一信号发射器3提供信号,在整个共享过程中,所有信号的模式都没有发生变化。第二信号发射器4的信号是时分复用信号;在一个运行周期内,前1/2周期为第一行提供信号,后1/2周期为第二行提供信号;第一信号发射器3的信号为开关信号;在一个运行周期内,前1/2周期vsw1为高,vsw2为低,第一行开启;后1/2周期vsw1低,vsw2高,第二行开启。

29.运行过程:前1/2周期,第二信号发射器4给出第一行的电平信号和三角波信号,vsw1高,vsw2低,第一行的选通晶体管打开,第二行关闭,第一行像素单元被激活。信号经信号处理模块2处理后,转变为pwm电压信号,该信号流经开启的第一行的选通晶体管加在驱动晶体管的栅极,控制驱动晶体管产生pwm电流信号,控制第一行micro led发光,每个micro led的亮暗程度受到in1和in2的具体电压大小控制;后1/2周期同理,第二信号发射器4给出第二行的电平信号和三角波信号,vsw1低,vsw2高;以相同的方式控制第二行micro led发光。

30.本实施例中实际采用的晶体管数量为28个,参加图5,传统驱动电路中实际使用的晶体管数量为52个,本实施例的晶体管数量远小于传统的驱动电路,且随着阵列规模的增大,本发明像素共享方式采用的晶体管数目将更低。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。