1.本技术属于电子设备技术领域,具体涉及一种图像传感器、控制方法、控制装置、电子设备和存储介质。

背景技术:

2.目前,由发光二极管(light emitting diode,led)显示技术启发的五像素的彩色滤光片阵列(color filter array,cfa),即rgbw3.0,其解决了柯达rgbw cfa、拜耳rgb cfa等传统cfa架构在应用上的诸多弊病(例如色彩分辨率下降等)。然而,rgbw3.0的结构相比于传统cfa架构发生了较大的变化,目前没有对应的像素阵列的像素信号处理电路方案,导致无法对rgbw3.0进行精准控制。

技术实现要素:

3.本技术实施例的目的是提供一种图像传感器、控制方法、控制装置、电子设备和存储介质,能够解决相关技术中没有对应的像素阵列的像素信号处理电路方案导致无法对彩色滤光片阵列进行精准控制的问题。

4.第一方面,本技术实施例提供了一种图像传感器,该图像传感器包括:

5.像素电路阵列,像素电路阵列包括多个像素团电路,每个像素团电路包括一个白色像素电路和至少两个彩色像素电路,至少两个彩色像素电路围绕白色像素电路设置,像素电路阵列包括至少两行像素电路行和至少两列像素电路列,至少两个像素电路行共用一个控制信号线,至少两个像素电路列共用一个输出信号线,其中,像素电路行包括白色像素电路或彩色像素电路,像素电路列包括白色像素电路或彩色像素电路;

6.像素信号处理模块,像素信号处理模块与输出信号线相连接。

7.第二方面,本技术实施例提供了一种电子设备,该电子设备包括:如第一方面的图像传感器。

8.第三方面,本技术实施例提供了一种图像传感器的控制方法,图像传感器包括像素电路阵列和像素信号处理模块,像素电路阵列包括多个像素团电路,每个像素团电路包括一个白色像素电路和多个彩色像素电路,多个彩色像素电路围绕白色像素电路设置,像素电路阵列的每个像素电路行共用一个控制信号线,像素电路阵列的每个像素电路列共用一个输出信号线,像素信号处理模块与输出信号线相连接;在像素电路行包括白色像素电路或彩色像素电路,像素电路列包括白色像素电路或彩色像素电路的情况下,像素信号处理模块包括选择模块、第一子处理模块、第二子处理模块以及第一处理缓存模块;该控制方法包括:

9.控制选择模块将第一目标信号传输至第一子处理模块;

10.控制第一子处理模块对第一目标信号进行放大及模数转换处理,并控制第二子处理模块对第三输出信号线的第三输出信号进行放大处理,以及对放大处理后的第三输出信号进行模数转换处理;

11.控制第一处理缓存模块对第一目标信号和第三输出信号进行存储,以及对第一目标信号和第三输出信号进行图像处理;

12.其中,第一目标信号包括第一输出信号线的第一输出信号或第二输出信号线的第二输出信号,第一输出信号线为白色像素电路列对应的输出信号线,第二输出信号线为与白色像素电路列相邻的一个彩色像素电路列对应的输出信号线,第三输出信号线为与白色像素电路列相邻的另一个彩色像素电路列对应的输出信号线,白色像素电路列为包括白色像素电路的像素电路列,彩色像素电路列为包括彩色像素电路的像素电路列。

13.第四方面,本技术实施例提供了一种图像传感器的控制装置,图像传感器包括像素电路阵列和像素信号处理模块,像素电路阵列包括多个像素团电路,每个像素团电路包括一个白色像素电路和多个彩色像素电路,多个彩色像素电路围绕白色像素电路设置,像素电路阵列的每个像素电路行共用一个控制信号线,像素电路阵列的每个像素电路列共用一个输出信号线,像素信号处理模块与输出信号线相连接;在像素电路行包括白色像素电路或彩色像素电路,像素电路列包括白色像素电路或彩色像素电路的情况下,像素信号处理模块包括选择模块、第一子处理模块、第二子处理模块以及第一处理缓存模块;该控制装置包括:

14.控制选择模块将第一目标信号传输至第一子处理模块;

15.控制第一子处理模块对第一目标信号进行放大及模数转换处理,以及控制第二子处理模块对第三输出信号线的第三输出信号进行放大处理,以及对放大处理后的第三输出信号进行模数转换处理;

16.控制第一处理缓存模块对第一目标信号和第三输出信号进行存储,以及对第一目标信号和第三输出信号进行图像处理;

17.其中,第一目标信号包括第一输出信号线的第一输出信号或第二输出信号线的第二输出信号,第一输出信号线为白色像素电路列对应的输出信号线,第二输出信号线为与白色像素电路列相邻的一个彩色像素电路列对应的输出信号线,第三输出信号线为与白色像素电路列相邻的另一个彩色像素电路列对应的输出信号线,白色像素电路列为包括白色像素电路的像素电路列,彩色像素电路列为包括彩色像素电路的像素电路列。

18.第五方面,本技术实施例提供了一种电子设备,该电子设备包括处理器、存储器及存储在存储器上并可在处理器上运行的程序或指令,程序或指令被处理器执行时实现如第二方面的方法的步骤。

19.第六方面,本技术实施例提供了一种可读存储介质,可读存储介质上存储程序或指令,程序或指令被处理器执行时实现如第二方面的方法的步骤。

20.第七方面,本技术实施例提供了一种芯片,芯片包括处理器和通信接口,通信接口和处理器耦合,处理器用于运行程序或指令,实现如第二方面的方法。

21.在本技术实施例中,像素电路阵列由多个像素团电路构成。像素电路阵列的每个像素电路行共用一个控制信号线路,像素电路阵列的每个像素电路列共用一个输出信号线路,具体包括:每一行的彩色像素电路共用一个控制信号线,每一行的白色像素电路共用一个像素控制信号;每一列的彩色像素电路共用一个输出信号线,每一列的白色像素电路共用一个输出信号线。每一行白色像素电路共用的像素控制信号与每一行彩色像素电路共用的像素控制信号相互独立,彩色像素电路的输出信号线与白色像素电路的输出信号线相互

独立。

22.本技术实施例提供了一种rgbw的像素电路阵列架构,相对于传统的像素电路阵列,实现了对像素电路阵列的重新布局。一方面,此像素电路阵列架构适用于cfa类型(例如,rgbw3.0 cfa),解决了cfa无法使用传统的像素电路阵列的问题,为cfa在互补金属氧化半导体图像传感器(complementary metal

‑

oxide semiconductor image sensor,cis)上的广泛应用提供基础;另一方面,实现了彩色像素与白色像素之间信号的独立处理,在适配采用cfa像素结构的同时,有效地避免了彩色像素与白色像素间信号的串扰,提高了图像传感器的灵敏度。

附图说明

23.图1是本技术实施例的互补金属氧化半导体图像传感器像素阵列排布以及像素团排布示意图;

24.图2是本技术实施例的互补金属氧化半导体图像传感器的像素的结构示意图之一;

25.图3是本技术实施例的互补金属氧化半导体图像传感器的像素的结构示意图之二;

26.图4是本技术实施例的互补金属氧化半导体图像传感器的像素电路阵列架构示意图;

27.图5是本技术实施例的像素电路阵列的结构示意图之一;

28.图6是本技术实施例的像素信号处理模块的结构示意图之一;

29.图7是本技术实施例的模拟数据选择器的结构示意图;

30.图8是本技术实施例的数字数据分用器的结构示意图;

31.图9是本技术实施例的像素电路阵列的结构示意图之二;

32.图10是本技术实施例的像素信号处理模块的结构示意图之二;

33.图11是本技术实施例的加法器的结构示意图之一;

34.图12是本技术实施例的加法器的结构示意图之二;

35.图13是本技术实施例的图像传感器的控制方法的流程示意图;

36.图14是本技术实施例的图像传感器的控制装置的示意框图;

37.图15是本技术实施例的电子设备的示意框图之一;

38.图16是本技术实施例的电子设备的示意框图之二。

具体实施方式

39.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员获得的所有其他实施例,都属于本技术保护的范围。

40.本技术的说明书和权利要求书中的术语“第一”、“第二”等是用于区别类似的对象,而不用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便本技术的实施例能够以除了在这里图示或描述的那些以外的顺序实施。此外,说明书以及权利要求中“和/或”表示所连接对象的至少其中之一,字符“/”,一般表示前后关联

对象是一种“或”的关系。

41.采用rgbw3.0的cis的像素阵列(pixel array)是由像素团构成的。如图1所示,每一个像素团100拥有5个像素(pixel),其中4个有色像素(即彩色像素),包括红色像素102、蓝色像素104和两个绿色像素106,均为“l”形状,而无色透明的白色像素108则仍为正方形,白色像素108位于像素团100的正中心,由4个“l”型的有色像素包裹环绕。在每一个有色像素的彩色滤光片下为感光元件,例如光电二极管,其作用为将彩色滤光片滤出的光线转换为用于后端处理的电学信号,例如电流、电压、电势能等。

42.而在现代的cis制造工艺中,异形像素(即“l”型)由于其工艺和良率问题,目前仍然无法大规模应用在消费类cis产品中。为了成功实践,rgbw3.0中的“l”型有色像素被拆分为多个矩形像素。如图2和图3所示,为两种方案。如图2所示,在方案1中,红区域202、蓝区域204、绿色区域206均由3个像素构成。而中间的白色区域208则由4个像素构成,每个像素的大小均一致。如图3所示,在方案2中,每个有色区域则由5个像素构成,而中心的白色区域208则由16个像素构成。不论上述何种方法,绿色像素,红色像素,蓝色像素的个数比值不变,始终为2:1:1。然而由于白色像素的个数变化,使得白色区域在像素团区域的占比改变,方法1中白色像素与有色像素的比值为1:3,方法2中白色像素与有色像素的比值为4:5。

43.采用rgbw3.0的cis像素电路阵列架构如图4所示,每一行像素均共享一组像素控制信号,像素控制信号包括:像素重置信号用于控制像素的重置时间,电荷转移开关信号用于控制像素的曝光时间,以及像素信号读取开关信号用于控制像素的读取时间,像素控制信号由像素控制信号生成模块402生成。每一列像素共用一个像素输出信号(v

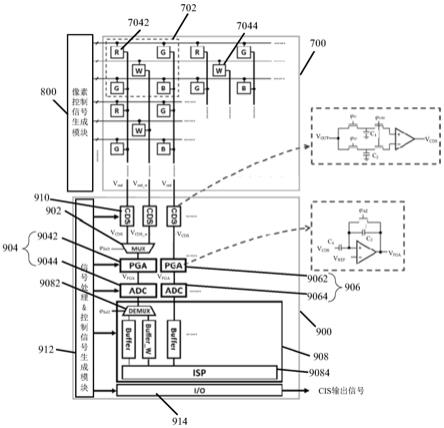

out

)传输线路,每一行像素将轮流使用此共享的传输线路传输v

out

至后端信号处理电路。

44.对于每一个像素,都包含了一个像素电路。如图4所示,像素电路404包括4晶体管有源像素感应(active pixel sensor,aps)电路,其中感光的光电二极管(photodiode,pd)将光线转换成电子后通过电荷转移晶体管(由控制其开关)转移至浮动扩散(floating diffusion,fd)区域。当像素被选择读取时(电平拉高),fd中的电荷量被由m

sf

以及m

sel

组成的源跟随器(source follower)读为电压信号并输出为v

out

。

45.采用rgbw3.0 cfa后,由于其与拜耳rgb以及柯达rgbw等传统cfa形式相比,结构发生了较大改变,因此无法适用传统的像素阵列对应的像素信号处理电路。而本技术提供的图像传感器和电子设备即可解决上述问题。

46.下面结合附图,通过具体的实施例及其应用场景对本技术实施例提供的图像传感器、控制方法、控制装置、电子设备和存储介质进行详细地说明。

47.本技术实施例提供了一种图像传感器,该图像传感器包括:

48.像素电路阵列,像素电路阵列包括多个像素团电路,每个像素团电路包括一个白色像素电路和至少两个彩色像素电路,至少两个彩色像素电路围绕白色像素电路设置,像素电路阵列包括至少两行像素电路行和至少两列像素电路列,至少两个像素电路行共用一个控制信号线,至少两个像素电路列共用一个输出信号线,其中,像素电路行包括白色像素电路或彩色像素电路,像素电路列包括白色像素电路或彩色像素电路;

49.像素信号处理模块,像素信号处理模块与输出信号线相连接。

50.在该实施例中,对于“l”型像素结构的方案,像素层的cfa采用了图1所示的布局,每个像素团包括4个彩色像素和1个白色像素,其中4个彩色像素包括红色像素(r)、蓝色像素(b)和两个绿色像素(g),均为“l”形状,而无色透明的白色像素(w)则为正方形,白色像素位于像素团的正中心,由4个“l”型的彩色像素包裹环绕。

51.像素阵列600以及像素阵列600对应的像素电路阵列700的电路结构,如图5所示,像素电路阵列700由多个像素团电路702构成,一个像素团电路702由多个像素电路704构成(像素阵列600中的一个像素团602对应一个像素团电路604,像素阵列600中的一个像素对应一个像素电路704),每一行像素电路均由像素控制信号生成模块800进行控制。

52.像素电路行中包括白色像素电路或彩色像素电路,且像素电路列中包括白色像素电路或彩色像素电路,相当于,像素电路阵列的每个像素电路行共用一个控制信号线路,像素电路阵列的每个像素电路列共用一个输出信号线路,具体包括:每一行的彩色像素电路共用一个像素控制信号(也即控制信号线路),每一行的白色像素电路共用一个像素控制信号;每一列的彩色像素电路共用一个输出信号线,每一列的白色像素电路共用一个输出信号线。每一行白色像素电路共用的像素控制信号与每一行彩色像素电路共用的像素控制信号相互独立,彩色像素电路的输出信号线与白色像素电路的输出信号线相互独立。每一列彩色像素电路的输出电压信号为v

out

,每一列白色像素电路输出的电压信号为v

out_w

,信号传输线路将每列的输出信号(v

out

和v

out_w

)传输至像素信号处理模块900,由像素信号处理模块900进行处理。

53.本技术实施例提供了一种rgbw的像素电路阵列架构,相对于传统的像素电路阵列,实现了对像素电路阵列的重新布局。一方面,此像素电路阵列架构适用于cfa类型(例如,rgbw3.0 cfa),解决了cfa无法使用传统的像素电路阵列的问题,为cfa在cis上的广泛应用提供基础;另一方面,实现了彩色像素与白色像素之间信号的独立处理,在适配采用cfa像素结构的同时,有效地避免了彩色像素与白色像素间信号的串扰,提高了图像传感器的灵敏度。

54.进一步地,在本技术的一个实施例中,像素信号处理模块包括:多个选择模块,选择模块与第一输出信号线、第二输出信号线连接,其中第一输出信号线为白色像素电路列对应的输出信号线,第二输出信号线为与白色像素电路列相邻的一个彩色像素电路列对应的输出信号线,白色像素电路列为包括白色像素电路的像素电路列,彩色像素电路列为包括彩色像素电路的像素电路列;第一处理模块,第一处理模块包括:多个第一子处理模块,第一子处理模块与选择模块连接;以及多个第二子处理模块,第二子处理模块与第三输出信号线连接,第三输出信号线为与白色像素电路列相邻的另一个彩色像素电路列对应的输出信号线;第一处理缓存模块,与第一处理模块连接。

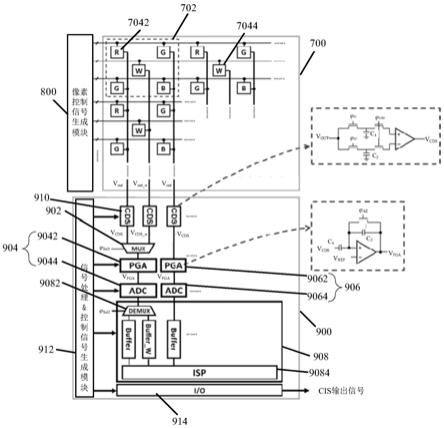

55.其中,选择模块将第一输出信号线的第一输出信号或第二输出信号线的第二输出信号传输至第一子处理模块,第一子处理模块对第一输出信号或第二输出信号进行放大处理,以及对放大处理后的第一输出信号或第二输出信号进行模数转换处理;第二子处理模块用于对第三输出信号线的第三输出信号进行放大处理,以及对放大处理后的第三输出信号进行模数转换处理。第一处理缓存模块用于对第一输出信号、第二输出信号和第三输出信号进行存储,并对存储的第一输出信号、第二输出信号和第三输出信号进行图像处理,以提高第一输出信号、第二输出信号和第三输出信号的信号质量,图像处理具体包括线性纠

正、坏点去除、内插、白平衡、自动曝光控制等后期处理。

56.在该实施例中,像素信号处理模块包括多个选择模块、第一处理模块以及第一处理缓存模块,第一处理模块包括多个第一子处理模块和多个第二子处理模块。白色像素电路列对应的输出信号线(即第一输出信号线)的输出信号和与其相邻的一个彩色像素电路列对应的输出信号线(即第二输出信号线)的输出信号,通过一个选择模块复用同一个第一子处理模块。而与第一输出信号线相邻的另一个彩色像素电路列对应的输出信号线(即第三输出信号线)的输出信号使用第二子处理模块。

57.第一处理缓存模块与所有的第一子处理模块、所有的第二子处理模块连接,用于对进行放大处理和模数转换处理后的第一输出信号、第二输出信号和第三输出信号依次进行存储和图像处理。

58.示例性地,如图6所示,像素信号处理模块900包括模拟数据选择器(analog data multiplexer,mux)902、第一子处理模块904、第二子处理模块906以及第一处理缓存模块908。每一列彩色像素电路7042的输出信号为v

out

、每一列白色像素电路7044的输出信号为v

out_w

,一个输出信号v

out

和一个输出信号v

out_w

通过一个mux 902后,复用一个第一子处理模块904,其中,mux即为上述选择模块,第一子处理模块904包括一个可调增益放大器(programmable gain amplifier,pga)电路9042和一个模数转换器(analog

‑

to

‑

digital convertor,adc)电路9044,第二子处理模块906包括一个pga电路9062和一个adc电路9064。pga电路用于对信号进行放大处理,其输出的信号v

pga

再输入至adc电路,adc电路用于对信号v

pga

进行模数转换处理。第一处理缓存模块908即为isp和图像缓存器,用于对信号进行存储和图像处理。

59.需要说明的是,如图6所示,mux902的两个输入信号分别为一列像素团电路中的一个白色像素电路列的输出信号v

out_w

,以及该列像素团电路中的任一个彩色像素电路列的输出信号v

out

。

60.在按照逐行扫描的方式读取像素电路的信号的情况下,首先读取第一行像素,例如读取彩色像素r的信号和彩色像素g的信号,彩色像素r的信号传输至mux 902中,再传输至pga电路、adc电路中进行处理,彩色像素g的信号直接传输至pga电路、adc电路中进行处理。然后读取第二行像素,例如读取白色像素w的信号,白色像素w的信号传输至mux902中,再传输至pga电路、adc电路,且与彩色像素r的信号共用的相同的pga电路、adc电路。由于第一行像素和第二行像素不同时读取,所以不会出现pga电路、adc电路的处理冲突。

61.本技术的实施例中,由于白色像素与彩色像素的数量不同且在不同横行,因此白色像素的信号处理链路与彩色像素处理链路有部分子模块可以复用,从而节省空间和能耗。

62.进一步地,在本技术的一个实施例中,第一处理缓存模块包括:多个第一分用模块,第一分用模块与第一子处理模块连接;多个第一缓存模块,第一缓存模块与第一分用模块连接;多个第二缓存模块,第二缓存模块与第一分用模块连接或者第二缓存模块与第二子处理模块连接;第一图像处理模块,与第一缓存模块和第二缓存模块连接。

63.其中,第一缓存模块,用于对第一输出信号进行存储,第二缓存模块在与第一分用模块连接的情况下,用于对第二输出信号进行存储,第二缓存模块在与第二子处理模块连接的情况下,用于对第三输出信号进行存储,第一图像处理模块,用于对第一输出信号、第

二输出信号和第三输出信号进行图像处理。

64.在该实施例中,第一处理缓存模块包括多个第一分用模块、多个第一缓存模块、多个第二缓存模块以及第一图像处理模块。第一分用模块用于将第一子处理模块输出的第一输出信号和第二输出信号分别传输至不同的缓存模块。具体地,第一输出信号传输至第一缓存模块,第二输出信号传输至第二缓存模块,第三输出信号传输至第二缓存模块,也就是说,第一缓存模块中存储白色像素电路列的输出信号,第二缓存模块中存储彩色像素电路列的输出信号。

65.第一图像处理模块再对第一缓存模块和第二缓存模块内存储的信号进行图像处理。

66.需要说明的是,多个第一分用模块的数量与选择模块的数量相等。

67.示例性地,如图6所示,在进入第一处理缓存模块908后,通过第一处理缓存模块908的数字数据分用器(digital data demultiplexer,demux)9082将第一输出信号和第二输出信号存储至不同的缓存模块(buffer和buffer_w),demux即为上述第一分用模块。具体地,第二输出信号和第三输出信号(即彩色像素列的输出信号)缓存在buffer,而第一输出信号(即白色像素列的输出信号)缓存在buffer_w。缓存后的信号进而进入isp 9084进行数字图像处理相关的步骤。

68.通过上述方式,对彩色像素列的输出信号和白色像素列的输出信号进行了独立的缓存,第一图像处理模块可以任意地点选彩色像素列的输出信号或白色像素列的输出信号进行后期处理,极大的丰富了图像信号处理种类。

69.需要说明的是,demux 9082的电路结构如图8所示,demux 9082由信号进行控制,将adc的输出信号分别输入至buffer和buffer_w。

70.常见的缓存模块有动态随机存取存储器(dynamic random accessmemory,dram)、静态随机存取存储器(static random access memory,sram)等。

71.图6中数据分用器也可放在adc前,此时数据分用器则必须使用模拟数据分用器而非数字数据分用器。

72.进一步地,在本技术的一个实施例中,像素信号处理模块还包括:多个第一采样模块,第一采样模块与输出信号线的输出端相连接。

73.第一采样模块用于对输出信号线的输出信号进行消噪音处理。

74.在该实施例中,像素信号处理模块还包括多个第一采样模块,第一采样模块的一端与输出信号线的输出端相连接,第一采样模块的另一端与选择模块或第二子处理模块相连接,第一采样模块用于对输出信号线的输出信号进行消噪音处理。

75.示例性地,如图6所示,每一列彩色像素电路的输出信号为v

out

、每一列白色像素电路的输出信号为v

out_w

,输出信号v

out

和输出信号v

out_w

均通过独立的相关双采样(corrolated double sampling,cds)电路910(即第一采样模块)进行消噪音处理。具体地,通过两次采样(采样信号存储在电容c1与电容c2),使用运算放大器a

cds

进行信号减法得到两次采样信号的差值,即v

cds

信号。cds电路910输出的v

cds

信号会输入至pga电路进行可调信号放大操作。

76.如图7所示,mux包括开启s1、开关s2以及运算放大器,mux由信号进行控制,cds输出的v

cds

与v

cds_w

信号进入mux进行信号合成。

77.通过上述方式,实现对彩色像素电路列的输出信号和白色像素电路列的输出信号进行消噪音处理,提高信号的准确性。

78.需要说明的是,如图6所示,在像素信号处理模块900中每一条像素信号处理链路上的子模块均需要由信号处理&控制信号模块912提供时序与控制信号。当像素信号走完所有链路上子模块且缓存至buffer或buffer_w上后,信号将进入isp 9084进行数字图像处理相关的步骤。处理完成后由i/o 914输出最后的图像信号至cis芯片外。

79.进一步地,在本技术的一个实施例中,在白色像素电路包括多个子白色像素电路、彩色像素电路包括多个子彩色像素电路的情况下,像素电路行包括子彩色像素电路,或包括子白色像素电路和子彩色像素电路;像素电路列包括子彩色像素电路,或包括子白色像素电路和子彩色像素电路。

80.在该实施例中,对于将白色像素拆分为多个矩形子白色像素、将彩色像素拆分为多个矩形子彩色像素的合成像素方案(如图2和图3所示)。以如图2中所示的结构为例,像素阵列600的每个像素团602中含有16个子像素,因此如图9所示,像素电路阵列700的每个像素团电路702中含有16个子像素电路706,具体为4个子白色像素电路和12个子彩色像素电路。每一行子像素电路均由像素控制信号生成模块800进行控制,每一列子像素电路的输出信号传输至像素信号处理模块900,由像素信号处理模块900进行处理。

81.像素电路阵列中,每一行中的子像素电路包括两种情况,一种为每一行中仅包括子彩色像素电路,另一种为每一行中包括子白色像素电路和子彩色像素电路;每一列中的子像素电路包括两种情况,一种为每一列中仅包括子彩色像素电路,另一种为每一列中包括子白色像素电路和子彩色像素电路。

82.每一行的所有子像素电路(不论是子彩色像素电路还是子白色像素电路)均由像素控制信号生成模块进行控制,也即,每一行的所有子像素电路共用一个像素控制信号(也即控制信号线)。每一列的所有子像素电路(不论是子彩色像素电路还是子白色像素电路)输出的信号共用一条信号传输线路(也即输出信号线)至像素信号处理模块。

83.本技术实施例提供了一种rgbw的像素电路阵列架构,一方面,此像素电路阵列架构适用于cfa类型(例如,rgbw3.0 cfa)的合成像素方案,解决了cfa的合成像素方案无法使用传统的像素电路阵列的问题,为cfa在cis上的广泛应用提供基础;另一方面,像素电路阵列中每一个像素电路均可进行信号处理与读出,在适配采用cfa像素结构的同时,有效地避免了像素间信号的串扰。

84.进一步地,在本技术的一个实施例中,像素信号处理模块包括:多个第二处理模块,第二处理模块与输出信号线连接;第二处理缓存模块,第二处理缓存模块包括:多个第二分用模块,第二分用模块与第一目标处理模块连接,其中第一目标处理模块为与第一目标像素电路列对应的输出信号线相连接的第二处理模块,第一目标像素电路列为包括子白色像素电路和子彩色像素电路的像素电路列;多个第三缓存模块,第三缓存模块与第二分用模块连接;多个第四缓存模块,第四缓存模块与第二分用模块连接,或第四缓存模块与第二目标处理模块连接,第二目标处理模块为与第二目标像素电路列对应的输出信号线相连接的第二处理模块,第二目标像素电路列为包括子彩色像素电路的像素电路列;以及第二图像处理模块,与第三缓存模块和第四缓存模块连接。

85.其中,第二处理模块,用于对输出信号线的输出信号进行放大处理,并对进行放大

处理后的输出信号进行模数转换处理;第三缓存模块,用于对第四输出信号进行存储,第四输出信号为第一目标像素电路列对应的输出信号线输出的子白色像素电路的信号;第四缓存模块在与第二分用模块连接的情况下,用于对第五输出信号进行存储,第五输出信号为第一目标像素电路列对应的输出信号线输出的子彩色像素电路的信号,第四缓存模块在与第二目标处理模块连接的情况下,用于对第二目标处理模块的第六输出信号进行存储;第二图像处理模块,用于对第四输出信号、第五输出信号和第六输出信号进行图像处理,以提高第四输出信号、第五输出信号和第六输出信号的信号质量,图像处理具体包括线性纠正、坏点去除、内插、白平衡、自动曝光控制等后期处理。

86.在该实施例中,对于合成像素方案,像素信号处理模块包括多个第二处理模块和一个第二处理缓存模块,第二处理缓存模块包括多个第二分用模块、多个第三缓存模块、多个第四缓存模块和一个第二图像处理模块。第二处理模块用于对输出信号线的输出信号进行放大处理和模数转换处理,第二分用模块将进行了放大处理和模数转换处理后的第一目标像素电路列的输出信号分别传输至不同的缓存模块(即第三缓存模块和第四缓存模块)中进行存储。具体地,第一目标像素电路列的输出信号包括子白色像素电路的信号(即第四输出信号)和子彩像素电路的信号(即第五输出信号),利用第二分用模块将第四输出信号传输至第三缓存模块进行存储,利用第二分用模块将第五输出信号传输至第四缓存模块进行存储。

87.另外,第二目标像素电路列的输出信号仅包括子彩色像素电路的信号(即第六输出信号),则将第二目标像素电路列的输出信号在利用第二目标处理模块进行放大处理和模数转换处理后,直接传输至第四缓存模块进行存储。

88.第二图像处理模块再对第三缓存模块和第四缓存模块内存储的信号进行图像处理。

89.其中,第一目标处理模块和第二目标处理模块均包括一个pga电路和一个adc电路。pga电路用于对信号进行放大处理,其输出的信号v

pga

或信号v

pga/w

再输入至adc电路,adc电路用于对信号v

pga

或信号v

pga/w

进行模数转换处理。

90.示例性地,如图10所示,像素信号处理模块900包括第一目标处理模块916、第二目标处理模块918以及第二处理缓存模块920。每一个子彩色像素电路列的输出信号为v

out

、每一个包括子白色像素电路和子彩色像素电路的像素电路列的输出信号为v

out/w

,输出信号v

out

通过第二目标处理模块918,输出信号v

out/w

通过第一目标处理模块916,进入isp和图像缓存器(即第二处理缓存模块920)。第一目标处理模块916包括一个pga电路9162和一个adc电路9164,第二目标处理模块918包括一个pga电路9182和一个adc电路9184。

91.由于在一个像素团中,子白色像素只存在于中间两列,因此在有子白色像素存在的列链路上设置一个demux 9202,在输出信号v

out/w

通过demux9202后,将子彩色像素信息(即上述第五输出信号)与子白色像素信息(即上述第四输出信号)分别缓存至对不同的缓存模块(buffer或buffer_w)。具体地,第五输出信号缓存在buffer,而第四输出信号缓存在buffer_w。另外,仅包括子彩色像素电路的像素电路列的输出信号v

out

(即上述第六输出信号)缓存在buffer。

92.在按照逐行扫描的方式读取像素电路的信号的情况下,首先读取第一行像素,例如读取子彩色像素r1、r2、g1、g2的信号,子彩色像素r1、g2的信号传输至对应的pga电路、adc

电路后,再存储至对应的buffer,子彩色像素r2、g1的信号传输至对应的pga电路、adc电路后,被demux分配至对应的buffer中进行存储。然后读取第二行像素,例如读取子彩色像素r3、g3的信号以及子白色像素w1、w2的信号,子彩色像素r3、g3的信号传输至对应的pga电路、adc电路后,再存储至对应的buffer,子白色像素w1、w2的信号传输至对应的pga电路、adc电路后,被demux分配至对应的buffer_w中进行存储。

93.通过上述方式,像素信号处理模块适配采用合成像素方案的像素阵列,通过使用不同的缓存模块将子彩色像素电路的信号与子白色像素电路的信号进行独立缓存,避免了信号之间的混乱与杂揉,为isp进行后期处理提供了方便。

94.需要说明的是,常见的缓存模块有dram、sram等。demux的电路结构如图8所示。图10中数据分用器也可放在adc前,此时数据分用器则必须使用模拟数据分用器而非数字数据分用器。

95.进一步地,在本技术的一个实施例中,第二处理缓存模块还包括:多个信号合成模块,信号合成模块与第二图像处理模块、第一目标缓存模块和第二目标缓存模块相连接,第一目标缓存模块和第二目标缓存模块为分别存储目标像素团电路中相邻行的两个子白色像素电路的信号的第三缓存模块。

96.其中,信号合成模块用于将第一目标缓存模块的输出信号和第二目标缓存模块的输出信号进行融合,也即增强第一目标缓存模块的输出信号和第二目标缓存模块的输出信号。

97.在该实施例中,由于合成像素方案,可能需要进行同色像素信号融合的情况,子彩色像素的同色像素合成一般发生在像素阵列中,而子白色像素的信号合成则在像素阵列中较难实现。

98.对此,本技术实施例提供了子白色像素的信号融合方案,在采用了子彩色像素信号融合的情况下,利用信号合成模块使对应的子白色像素信号进行信号融合。具体地,第二处理缓存模块包括多个信号合成模块,信号合成模块用于目标像素团电路中相邻行的两个子白色像素电路的信号,而相邻行的两个子白色像素电路的信号是分别存储在第一目标缓存模块和第二目标缓存模块中的信号,目标像素团电路为像素电路阵列中的任一个像素团电路。

99.示例性地,如图10所示,在两个相邻的buffer_w的输出端设置一个加法器9206(即上述信号合成模块),即可轻易地实现子白色像素(例如,子白色像素w1和子白色像素w2,或者子白色像素w3和子白色像素w4)的信号融合。需要说明的是,如图10所示,由于加法器9206是在adc后,因此是进行数字信号合成。

100.加法器的电路结构如图11所示,加法器有多个全加器构成,全加器的的电路结构如图12所示。n位二进制数字信号a1、a2、

……

、a

n

与n位二进制数字信号b1、b2、

……

、b

n

在通过加法器后将分别生成n位二进制数字信号s1、s2、

……

、s

n

。c1、c2、

……

、c

n

为加法中的进位。

101.通过上述方式,实现相邻的两个子白色像素信号的融合,为isp进行后期处理提供了方便。

102.进一步地,在本技术的一个实施例中,像素信号处理模块还包括:多个第二采样模块,第二采样模块连接于第二处理模块与输出信号线之间。其中,第二采样模块用于对输出信号线的输出信号进行消噪音处理。

103.在该实施例中,像素信号处理模块还包括多个第二采样模块,第二采样模块的一端与输出信号线的输出端相连接,第二采样模块的另一端与第二处理模块相连接,第二采样模块用于对输出信号线的输出信号进行消噪音处理。

104.示例性地,如图10所示,每一个仅包括子彩色像素电路的像素电路列的输出信号为v

out

、每一个包括子彩色像素电路和子白色像素电路的像素电路列的输出信号为v

out/w

,输出信号v

out

和输出信号v

out/w

均通过独立的cds 922(即第二采样模块)进行消噪音处理。

105.通过上述方式,实现对输出信号线的输出信号进行消噪音处理,提高信号的准确性。

106.需要说明的是,如图10所示,在像素信号处理模块中每一条像素信号处理链路上的子模块均需要由信号处理&控制信号模块912提供时序与控制信号。当像素信号走完所有链路上子模块且缓存至buffer或buffer_w上后,信号将进入isp 9204进行数字图像处理相关的步骤。处理完成后由i/o914输出最后的图像信号至cis芯片外。

107.本技术实施例提供了一种电子设备,该电子设备包括如上述实施例的图像传感器。

108.在该实施例中,图像传感器的像素电路阵列由多个像素团电路构成。像素电路阵列的每个像素电路行共用一个控制信号线路,像素电路阵列的每个像素电路列共用一个输出信号线路,具体包括:每一行的彩色像素电路共用一个控制信号线,每一行的白色像素电路共用一个像素控制信号;每一列的彩色像素电路共用一个输出信号线,每一列的白色像素电路共用一个输出信号线。每一行白色像素电路共用的像素控制信号与每一行彩色像素电路共用的像素控制信号相互独立,彩色像素电路的输出信号线与白色像素电路的输出信号线相互独立。

109.本技术实施例提供了一种rgbw的像素电路阵列架构,相对于传统的像素电路阵列,实现了对像素电路阵列的重新布局。一方面,此像素电路阵列架构适用于cfa类型(例如,rgbw3.0 cfa),解决了cfa无法使用传统的像素电路阵列的问题,为cfa在cis上的广泛应用提供基础;另一方面,实现了彩色像素与白色像素之间信号的独立处理,在适配采用cfa像素结构的同时,有效地避免了彩色像素与白色像素间信号的串扰,提高了图像传感器的灵敏度。

110.该电子设备可以是移动电子设备,也可以为非移动电子设备。示例性的,移动电子设备可以为手机、平板电脑、笔记本电脑、掌上电脑、车载电子设备、可穿戴设备、超级移动个人计算机(ultra

‑

mobile personal computer,umpc)、上网本或者个人数字助理(personal digital assistant,pda)等,非移动电子设备可以为服务器、网络附属存储器(network attached storage,nas)、个人计算机(personal computer,pc)、电视机(television,tv)、柜员机或者自助机等,本技术实施例不作具体限定。

111.本技术实施例中的电子设备可以为具有操作系统的装置。该操作系统可以为安卓(android)操作系统,可以为ios操作系统,还可以为其他可能的操作系统,本技术实施例不作具体限定。

112.本技术实施例提供一种图像传感器的控制方法,图像传感器包括像素电路阵列和像素信号处理模块,像素电路阵列包括多个像素团电路,每个像素团电路包括一个白色像素电路和多个彩色像素电路,多个彩色像素电路围绕白色像素电路设置,像素电路阵列的

每个像素电路行共用一个控制信号线,像素电路阵列的每个像素电路列共用一个输出信号线,像素信号处理模块与输出信号线相连接;在像素电路行包括白色像素电路或彩色像素电路,像素电路列包括白色像素电路或彩色像素电路的情况下,像素信号处理模块包括选择模块、第一子处理模块、第二子处理模块以及第一处理缓存模块;如图13所示,控制方法包括:

113.步骤1302,控制选择模块将第一目标信号传输至第一子处理模块;

114.步骤1304,控制第一子处理模块对第一目标信号进行放大及模数转换处理,并控制第二子处理模块对第三输出信号线的第三输出信号进行放大处理,以及对放大处理后的第三输出信号进行模数转换处理;

115.步骤1306,控制第一处理缓存模块对第一目标信号和第三输出信号进行存储,以及对第一目标信号和第三输出信号进行图像处理。

116.其中,第一目标信号包括第一输出信号线的第一输出信号或第二输出信号线的第二输出信号,第一输出信号线为白色像素电路列对应的输出信号线,第二输出信号线为与白色像素电路列相邻的一个彩色像素电路列对应的输出信号线,第三输出信号线为与白色像素电路列相邻的另一个彩色像素电路列对应的输出信号线,白色像素电路列为包括白色像素电路的像素电路列,彩色像素电路列为包括彩色像素电路的像素电路列。

117.在该实施例中,像素信号处理模块包括多个选择模块、第一处理模块以及第一处理缓存模块,第一处理模块包括多个第一子处理模块和多个第二子处理模块。白色像素电路列对应的输出信号线(即第一输出信号线)的输出信号和与其相邻的一个彩色像素电路列对应的输出信号线(即第二输出信号线)的输出信号,通过一个选择模块复用同一个第一子处理模块。而与第一输出信号线相邻的另一个彩色像素电路列对应的输出信号线(即第三输出信号线)的输出信号使用第二子处理模块。

118.第一处理缓存模块与所有的第一子处理模块、所有的第二子处理模块连接,用于对进行了放大处理和模数转换处理后的第一输出信号、第二输出信号和第三输出信号依次进行存储和图像处理,其中,图像处理具体包括线性纠正、坏点去除、内插、白平衡、自动曝光控制等后期处理。

119.本技术的实施例中,由于白色像素与彩色像素的数量不同且在不同横行,因此白色像素的信号处理链路与彩色像素处理链路有部分子模块可以复用,从而节省空间和能耗。

120.进一步地,在本技术的一个实施例中,第一处理缓存模块包括第一分用模块、第一缓存模块、第二缓存模块以及第一图像处理模块;控制第一处理缓存模块对第一目标信号和第三输出信号依次进行存储处理和图像处理,包括:控制第一分用模块将第一输出信号存储至第一缓存模块,以及将第二输出信号存储至第二缓存模块;控制第二缓存模块对第三输出信号进行存储;控制第一图像处理模块对第一缓存模块存储的第一输出信号进行图像处理,以提高第一输出信号的信号质量,以及对第二缓存模块存储的第二输出信号和第三输出信号进行图像处理,以提高第二输出信号和第三输出信号的信号质量。

121.在该实施例中,第一处理缓存模块包括多个第一分用模块、多个第一缓存模块、多个第二缓存模块以及第一图像处理模块。第一分用模块用于将第一子处理模块输出的第一输出信号和第二输出信号分别传输至不同的缓存模块。具体地,第一输出信号传输至第一

缓存模块,第二输出信号传输至第二缓存模块,第三输出信号传输至第二缓存模块,也就是说,第一缓存模块中存储白色像素电路列的输出信号,第二缓存模块中存储彩色像素电路列的输出信号。

122.第一图像处理模块再对第一缓存模块和第二缓存模块内存储的信号进行图像处理,其中图像处理具体包括线性纠正、坏点去除、内插、白平衡、自动曝光控制等后期处理。

123.通过上述方式,对彩色像素列的输出信号和白色像素列的输出信号进行了独立的缓存,第一图像处理模块可以任意地点选彩色像素列的输出信号或白色像素列的输出信号进行后期处理,极大的丰富了图像信号处理种类。

124.进一步地,在本技术的一个实施例中,在白色像素电路包括多个子白色像素电路、彩色像素电路包括多个子彩色像素电路的情况下,像素电路行包括子彩色像素电路,或包括子白色像素电路和子彩色像素电路,像素电路列包括子彩色像素电路,或包括子白色像素电路和子彩色像素电路,像素信号处理模块包括第二处理模块和第二处理缓存模块,第二处理缓存模块包括第二分用模块、第三缓存模块、第四缓存模块以及第二图像处理模块;该控制方法还包括:控制第二处理模块对输出信号线的输出信号进行放大处理,以及对放大处理后的输出信号线的输出信号进行模数转换处理;控制第二分用模块将第四输出信号存储至第三缓存模块,以及将第五输出信号存储至第四缓存模块;控制第四缓存模块对第二目标处理模块的第六输出信号进行存储;控制第二图像处理模块对第三缓存模块存储的第四输出信号进行图像处理,以提高第四输出信号的信号质量,以及对第四缓存模块存储的第五输出信号和第六输出信号进行图像处理,以提高第五输出信号和第六输出信号的信号质量;其中,第四输出信号为第一目标像素电路列对应的输出信号线输出的子白色像素电路的信号,第一目标像素电路列为包括子白色像素电路和子彩色像素电路的像素电路列,第五输出信号为第一目标像素电路列对应的输出信号线输出的子彩色像素电路的信号,第二目标处理模块为与第二目标像素电路列对应的输出信号线相连接的第二处理模块,第二目标像素电路列为包括子彩色像素电路的像素电路列。

125.在该实施例中,对于合成像素方案,像素信号处理模块包括多个第二处理模块和一个第二处理缓存模块,第二处理缓存模块包括多个第二分用模块、多个第三缓存模块、多个第四缓存模块和一个第二图像处理模块。第二处理模块用于对输出信号线的输出信号进行放大处理和模数转换处理,第二分用模块将进行了放大处理和模数转换处理后的第一目标像素电路列的输出信号分别传输至不同的缓存模块(即第三缓存模块和第四缓存模块)中进行存储。具体地,第一目标像素电路列的输出信号包括子白色像素电路的信号(即第四输出信号)和子彩像素电路的信号(即第五输出信号),利用第二分用模块将第四输出信号传输至第三缓存模块进行存储,利用第二分用模块将第五输出信号传输至第四缓存模块进行存储。

126.另外,第二目标像素电路列的输出信号仅包括子彩色像素电路的信号(即第六输出信号),则将第二目标像素电路列的输出信号在利用第二目标处理模块进行放大处理和模数转换处理后,直接传输至第四缓存模块进行存储。

127.第二图像处理模块再对第三缓存模块和第四缓存模块内存储的信号进行图像处理,其中图像处理具体包括线性纠正、坏点去除、内插、白平衡、自动曝光控制等后期处理。

128.通过上述方式,像素信号处理模块适配采用合成像素方案的像素阵列,通过使用

不同的缓存模块将子彩色像素电路的信号与子白色像素电路的信号进行独立缓存,避免了信号之间的混乱与杂揉,为isp进行后期处理提供了方便。

129.进一步地,在本技术的一个实施例中,第二处理缓存模块还包括信号合成模块;该控制方法还包括:控制信号合成模块将第一目标缓存模块的输出信号与第二目标缓存模块的输出信号进行融合,第一目标缓存模块和第二目标缓存模块为分别存储目标像素团电路中相邻行的两个子白色像素电路的信号的第三缓存模块。

130.在该实施例中,由于合成像素方案,可能需要进行同色像素信号融合的情况,子彩色像素的同色像素合成一般发生在像素阵列中,而子白色像素的信号合成则在像素阵列中较难实现。

131.对此,本技术实施例提供了子白色像素的信号融合方案,在采用了子彩色像素信号融合的情况下,利用信号合成模块使对应的子白色像素信号进行信号融合。具体地,第二处理缓存模块包括多个信号合成模块,信号合成模块用于目标像素团电路中相邻行的两个子白色像素电路的信号,而相邻行的两个子白色像素电路的信号是分别存储在第一目标缓存模块和第二目标缓存模块中的信号,目标像素团电路为像素电路阵列中的任一个像素团电路。

132.通过上述方式,实现相邻的两个子白色像素信号的融合,为isp进行后期处理提供了方便。

133.进一步地,在本技术的一个实施例中,该控制方法还包括:控制第二图像处理模块将信号合成模块的输出信号与第二目标信号进行融合,以增强第二目标信号,第二目标信号为目标像素团电路中的子彩色像素电路的信号。

134.在该实施例中,在子彩色像素信号相互进行了信号融合,以及子白色像素信号也相互进行了信号整合的情况下,使在同一个像素团中的融成后的子白色像素信号与融成后的子彩色像素信号配对,也就是说,利用第二图像处理模块实现同一个像素团中的子白色像素信号与子彩色像素信号的信号融合,以增强子彩色像素的感光程度。

135.通过上述方式,为isp进行后期处理提供了方便,同时也极大的丰富了图像信号处理种类。

136.需要说明的是,本技术实施例提供的图像传感器的控制方法,执行主体可以为图像传感器的控制装置,或者,该图像传感器的控制装置中的用于执行图像传感器的控制方法的控制模块。本技术实施例中以图像传感器的控制装置执行图像传感器的控制方法为例,说明本技术实施例提供的图像传感器的控制装置。

137.本技术实施例提供一种图像传感器的控制装置,图像传感器包括像素电路阵列和像素信号处理模块,像素电路阵列包括多个像素团电路,每个像素团电路包括一个白色像素电路和多个彩色像素电路,多个彩色像素电路围绕白色像素电路设置,像素电路阵列的每个像素电路行共用一个控制信号线,像素电路阵列的每个像素电路列共用一个输出信号线,像素信号处理模块与输出信号线相连接;在像素电路行包括白色像素电路或彩色像素电路,像素电路列包括白色像素电路或彩色像素电路的情况下,像素信号处理模块包括选择模块、第一子处理模块、第二子处理模块以及第一处理缓存模块;如图14所示,该控制装置包括控制模块1402,该控制模块1402用于:

138.控制选择模块将第一目标信号传输至第一子处理模块;

139.控制第一子处理模块对第一目标信号进行放大及模数转换处理,并控制第二子处理模块对第三输出信号线的第三输出信号进行放大处理,以及对放大处理后的第三输出信号进行模数转换处理;

140.控制第一处理缓存模块对第一目标信号和第三输出信号进行存储,以及对第一目标信号和第三输出信号进行图像处理;

141.其中,第一目标信号包括第一输出信号线的第一输出信号或第二输出信号线的第二输出信号,第一输出信号线为白色像素电路列对应的输出信号线,第二输出信号线为与白色像素电路列相邻的一个彩色像素电路列对应的输出信号线,第三输出信号线为与白色像素电路列相邻的另一个彩色像素电路列对应的输出信号线,白色像素电路列为包括白色像素电路的像素电路列,彩色像素电路列为包括彩色像素电路的像素电路列。

142.在该实施例中,像素信号处理模块包括多个选择模块、第一处理模块以及第一处理缓存模块,第一处理模块包括多个第一子处理模块和多个第二子处理模块。白色像素电路列对应的输出信号线(即第一输出信号线)的输出信号和与其相邻的一个彩色像素电路列对应的输出信号线(即第二输出信号线)的输出信号,通过一个选择模块复用同一个第一子处理模块。而与第一输出信号线相邻的另一个彩色像素电路列对应的输出信号线(即第三输出信号线)的输出信号使用第二子处理模块。

143.第一处理缓存模块与所有的第一子处理模块、所有的第二子处理模块连接,用于对进行了放大处理和模数转换处理后的第一输出信号、第二输出信号和第三输出信号依次进行存储和图像处理,其中,图像处理具体包括线性纠正、坏点去除、内插、白平衡、自动曝光控制等后期处理。

144.本技术的实施例中,由于白色像素与彩色像素的数量不同且在不同横行,因此白色像素的信号处理链路与彩色像素处理链路有部分子模块可以复用,从而节省空间和能耗。

145.进一步地,在本技术的一个实施例中,第一处理缓存模块包括第一分用模块、第一缓存模块、第二缓存模块以及第一图像处理模块;控制模块1402,还用于:控制第一分用模块将第一输出信号存储至第一缓存模块,以及将第二输出信号存储至第二缓存模块;控制第二缓存模块对第三输出信号进行存储;控制第一图像处理模块对第一缓存模块存储的第一输出信号进行图像处理,以提高第一输出信号的信号质量,以及对第二缓存模块存储的第二输出信号和第三输出信号进行图像处理,以提高第二输出信号和第三输出信号的信号质量。

146.进一步地,在本技术的一个实施例中,在白色像素电路包括多个子白色像素电路、彩色像素电路包括多个子彩色像素电路的情况下,像素电路行包括子彩色像素电路,或包括子白色像素电路和子彩色像素电路,像素电路列包括子彩色像素电路,或包括子白色像素电路和子彩色像素电路,像素信号处理模块包括第二处理模块和第二处理缓存模块,第二处理缓存模块包括第二分用模块、第三缓存模块、第四缓存模块以及第二图像处理模块;控制模块1402,还用于:控制第二处理模块对输出信号线的输出信号进行放大处理,以及对放大处理后的输出信号线的输出信号进行模数转换处理;控制第二分用模块将第四输出信号存储至第三缓存模块,以及将第五输出信号存储至第四缓存模块;控制第四缓存模块对第二目标处理模块的第六输出信号进行存储;控制第二图像处理模块对第三缓存模块存储

的第四输出信号进行图像处理,以提高第四输出信号的信号质量,以及对第四缓存模块存储的第五输出信号和第六输出信号进行图像处理,以提高第五输出信号和第六输出信号的信号质量;其中,第四输出信号为第一目标像素电路列对应的输出信号线输出的子白色像素电路的信号,第一目标像素电路列为包括子白色像素电路和子彩色像素电路的像素电路列,第五输出信号为第一目标像素电路列对应的输出信号线输出的子彩色像素电路的信号,第二目标处理模块为与第二目标像素电路列对应的输出信号线相连接的第二处理模块,第二目标像素电路列为包括子彩色像素电路的像素电路列。

147.进一步地,在本技术的一个实施例中,第二处理缓存模块还包括信号合成模块;控制模块1402,还用于控制信号合成模块将第一目标缓存模块的输出信号与第二目标缓存模块的输出信号进行融合,第一目标缓存模块和第二目标缓存模块为分别存储目标像素团电路中相邻行的两个子白色像素电路的信号的第三缓存模块。

148.进一步地,在本技术的一个实施例中,控制模块1402,还用于控制第二图像处理模块将信号合成模块的输出信号与第二目标信号进行融合,以增强第二目标信号,第二目标信号为目标像素团电路中的子彩色像素电路的信号。

149.本技术实施例中的图像传感器的控制装置1400可以是装置,也可以是终端中的部件、集成电路或芯片。该装置可以是移动电子设备,也可以为非移动电子设备。示例性的,移动电子设备可以为手机、平板电脑、笔记本电脑、掌上电脑、车载电子设备、可穿戴设备、超级移动个人计算机(ultra

‑

mobilepersonal computer,umpc)、上网本或者个人数字助理(personal digitalassistant,pda)等,非移动电子设备可以为服务器、网络附属存储器(networkattached storage,nas)、个人计算机(personal computer,pc)、电视机(television,tv)、柜员机或者自助机等,本技术实施例不作具体限定。

150.本技术实施例中的图像传感器的控制装置1400可以为具有操作系统的装置。该操作系统可以为安卓(android)操作系统,可以为ios操作系统,还可以为其他可能的操作系统,本技术实施例不作具体限定。

151.本技术实施例提供的图像传感器的控制装置1400能够实现图13的方法实施例中实现的各个过程,为避免重复,这里不再赘述。

152.可选的,如图15所示,本技术实施例还提供一种电子设备1500,包括处理器1502,存储器1504,存储在存储器1504上并可在处理器1502上运行的程序或指令,该程序或指令被处理器1502执行时实现上述像素阵列的控制方法实施例的各个过程,且能达到相同的技术效果,为避免重复,这里不再赘述。

153.需要注意的是,本技术实施例中的电子设备包括上述的移动电子设备和非移动电子设备。

154.图16为实现本技术实施例的一种电子设备的硬件结构示意图。

155.该电子设备1600包括但不限于:射频单元1602、网络模块1604、音频输出单元1606、输入单元1608、传感器1610、显示单元1612、用户输入单元1614、接口单元1616、存储器1618、以及处理器1620等部件。

156.本领域技术人员可以理解,电子设备1600还可以包括给各个部件供电的电源(比如电池),电源可以通过电源管理系统与处理器1620逻辑相连,从而通过电源管理系统实现管理充电、放电、以及功耗管理等功能。图16中示出的电子设备结构并不构成对电子设备的

限定,电子设备可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置,在此不再赘述。

157.其中,电子设备1600的传感器1610包括图像传感器,图像传感器包括像素电路阵列和像素信号处理模块,像素电路阵列包括多个像素团电路,每个像素团电路包括一个白色像素电路和多个彩色像素电路,多个彩色像素电路围绕白色像素电路设置,像素电路阵列的每个像素电路行共用一个控制信号线,像素电路阵列的每个像素电路列共用一个输出信号线,像素信号处理模块与输出信号线相连接;在像素电路行包括白色像素电路或彩色像素电路,像素电路列包括白色像素电路或彩色像素电路的情况下,像素信号处理模块包括选择模块、第一子处理模块、第二子处理模块以及第一处理缓存模块。处理器1620用于:

158.控制选择模块将第一目标信号传输至第一子处理模块;

159.控制第一子处理模块对第一目标信号进行放大及模数转换处理,并控制第二子处理模块对第三输出信号线的第三输出信号进行放大处理,以及对放大处理后的第三输出信号进行模数转换处理;

160.控制第一处理缓存模块对第一目标信号和第三输出信号进行存储,以及对第一目标信号和第三输出信号进行图像处理;

161.其中,第一目标信号包括第一输出信号线的第一输出信号或第二输出信号线的第二输出信号,第一输出信号线为白色像素电路列对应的输出信号线,第二输出信号线为与白色像素电路列相邻的一个彩色像素电路列对应的输出信号线,第三输出信号线为与白色像素电路列相邻的另一个彩色像素电路列对应的输出信号线,白色像素电路列为包括白色像素电路的像素电路列,彩色像素电路列为包括彩色像素电路的像素电路列。

162.在该实施例中,像素信号处理模块包括多个选择模块、第一处理模块以及第一处理缓存模块,第一处理模块包括多个第一子处理模块和多个第二子处理模块。白色像素电路列对应的输出信号线(即第一输出信号线)的输出信号和与其相邻的一个彩色像素电路列对应的输出信号线(即第二输出信号线)的输出信号,通过一个选择模块复用同一个第一子处理模块。而与第一输出信号线相邻的另一个彩色像素电路列对应的输出信号线(即第三输出信号线)的输出信号使用第二子处理模块。

163.第一处理缓存模块与所有的第一子处理模块、所有的第二子处理模块连接,用于对进行了放大处理和模数转换处理后的第一输出信号、第二输出信号和第三输出信号依次进行存储和图像处理,其中,图像处理具体包括线性纠正、坏点去除、内插、白平衡、自动曝光控制等后期处理。

164.本技术的实施例中,由于白色像素与彩色像素的数量不同且在不同横行,因此白色像素的信号处理链路与彩色像素处理链路有部分子模块可以复用,从而节省空间和能耗。

165.进一步地,在本技术的一个实施例中,第一处理缓存模块包括第一分用模块、第一缓存模块、第二缓存模块以及第一图像处理模块;处理器1620,还用于:控制第一分用模块将第一输出信号存储至第一缓存模块,以及将第二输出信号存储至第二缓存模块;控制第二缓存模块对第三输出信号进行存储;控制第一图像处理模块对第一缓存模块存储的第一输出信号进行图像处理,以提高第一输出信号的信号质量,以及对第二缓存模块存储的第二输出信号和第三输出信号进行图像处理,以提高第二输出信号和第三输出信号的信号质

量。

166.进一步地,在本技术的一个实施例中,在白色像素电路包括多个子白色像素电路、彩色像素电路包括多个子彩色像素电路的情况下,像素电路行包括子彩色像素电路,或包括子白色像素电路和子彩色像素电路,像素电路列包括子彩色像素电路,或包括子白色像素电路和子彩色像素电路,像素信号处理模块包括第二处理模块和第二处理缓存模块,第二处理缓存模块包括第二分用模块、第三缓存模块、第四缓存模块以及第二图像处理模块;处理器1620,还用于:控制第二处理模块对输出信号线的输出信号进行放大处理,以及对放大处理后的输出信号线的输出信号进行模数转换处理;控制第二分用模块将第四输出信号存储至第三缓存模块,以及将第五输出信号存储至第四缓存模块;控制第四缓存模块对第二目标处理模块的第六输出信号进行存储;控制第二图像处理模块对第三缓存模块存储的第四输出信号进行图像处理,以提高第四输出信号的信号质量,以及对第四缓存模块存储的第五输出信号和第六输出信号进行图像处理,以提高第五输出信号和第六输出信号的信号质量;其中,第四输出信号为第一目标像素电路列对应的输出信号线输出的子白色像素电路的信号,第一目标像素电路列为包括子白色像素电路和子彩色像素电路的像素电路列,第五输出信号为第一目标像素电路列对应的输出信号线输出的子彩色像素电路的信号,第二目标处理模块为与第二目标像素电路列对应的输出信号线相连接的第二处理模块,第二目标像素电路列为包括子彩色像素电路的像素电路列。

167.进一步地,在本技术的一个实施例中,第二处理缓存模块还包括信号合成模块;处理器1620,还用于控制信号合成模块将第一目标缓存模块的输出信号和第二目标缓存模块的输出信号进行融合,第一目标缓存模块和第二目标缓存模块为分别存储目标像素团电路中相邻行的两个子白色像素电路的信号的第三缓存模块。

168.进一步地,在本技术的一个实施例中,处理器1620,还用于控制第二图像处理模块将信号合成模块的输出信号与第二目标信号进行融合,以增强第二目标信号,第二目标信号为目标像素团电路中的子彩色像素电路的信号。

169.应理解的是,本技术实施例中,射频单元1602可用于收发信息或收发通话过程中的信号,具体的,接收基站的下行数据或向基站发送上行数据。射频单元1602包括但不限于天线、至少一个放大器、收发信机、耦合器、低噪声放大器、双工器等。

170.网络模块1604为用户提供了无线的宽带互联网访问,如帮助用户收发电子邮件、浏览网页和访问流式媒体等。

171.音频输出单元1606可以将射频单元1602或网络模块1604接收的或者在存储器1618中存储的音频数据转换成音频信号并且输出为声音。而且,音频输出单元1606还可以提供与电子设备1600执行的特定功能相关的音频输出(例如,呼叫信号接收声音、消息接收声音等等)。音频输出单元1606包括扬声器、蜂鸣器以及受话器等。

172.输入单元1608用于接收音频或视频信号。输入单元1608可以包括图形处理器(graphics processing unit,gpu)16082和麦克风16084,图形处理器16082对在视频捕获模式或图像捕获模式中由图像捕获装置(如摄像头)获得的静态图片或视频的图像数据进行处理。处理后的图像帧可以显示在显示单元1612上,或者存储在存储器1618(或其它存储介质)中,或者经由射频单元1602或网络模块1604发送。麦克风16084可以接收声音,并且能够将声音处理为音频数据,处理后的音频数据可以在电话通话模式的情况下转换为可经由

射频单元1602发送到移动通信基站的格式输出。

173.电子设备1600还包括至少一种传感器1610,比如指纹传感器、压力传感器、虹膜传感器、分子传感器、陀螺仪、气压计、湿度计、温度计、红外线传感器、光传感器、运动传感器以及其他传感器。

174.显示单元1612用于显示由用户输入的信息或提供给用户的信息。显示单元1612可包括显示面板16122,可以采用液晶显示器、有机发光二极管等形式来配置显示面板16122。

175.用户输入单元1614可用于接收输入的数字或字符信息,以及产生与电子设备的用户设置以及功能控制有关的键信号输入。具体地,用户输入单元1614包括触控面板16142以及其他输入设备16144。触控面板16142也称为触摸屏,可收集用户在其上或附近的触摸操作。触控面板16142可包括触摸检测装置和触摸控制器两个部分。其中,触摸检测装置检测用户的触摸方位,并检测触摸操作带来的信号,将信号传送给触摸控制器;触摸控制器从触摸检测装置上接收触摸信息,并将它转换成触点坐标,再送给处理器1620,接收处理器1620发来的命令并加以执行。其他输入设备16144可以包括但不限于物理键盘、功能键(比如音量控制按键、开关按键等)、轨迹球、鼠标、操作杆,在此不再赘述。

176.进一步的,触控面板16142可覆盖在显示面板16122上,当触控面板16142检测到在其上或附近的触摸操作后,传送给处理器1620以确定触摸事件的类型,随后处理器1620根据触摸事件的类型在显示面板16122上提供相应的视觉输出。触控面板16142与显示面板16122可作为两个独立的部件,也可以集成为一个部件。

177.接口单元1616为外部装置与电子设备1600连接的接口。例如,外部装置可以包括有线或无线头戴式耳机端口、外部电源(或电池充电器)端口、有线或无线数据端口、存储卡端口、用于连接具有识别模块的装置的端口、音频输入/输出(i/o)端口、视频i/o端口、耳机端口等等。接口单元1616可以用于接收来自外部装置的输入(例如,数据信息、电力等等)并且将接收到的输入传输到电子设备1600内的一个或多个元件或者可以用于在电子设备1600和外部装置之间传输数据。

178.存储器1618可用于存储软件程序以及各种数据。存储器1618可主要包括存储程序区和存储数据区,其中,存储程序区可存储操作系统、至少一个功能所需的应用程序(比如声音播放功能、图像播放功能等)等;存储数据区可存储根据移动终端的使用所创建的数据(比如音频数据、电话本等)等。此外,存储器1618可以包括高速随机存取存储器,还可以包括非易失性存储器,例如至少一个磁盘存储器件、闪存器件、或其他易失性固态存储器件。

179.处理器1620通过运行或执行存储在存储器1618内的软件程序和/或模块,以及调用存储在存储器1618内的数据,执行电子设备1600的各种功能和处理数据,从而对电子设备1600进行整体监控。处理器1620可包括一个或多个处理单元;优选的,处理器1620可集成应用处理器和调制解调处理器,其中,应用处理器主要处理操作系统、用户界面和应用程序等,调制解调处理器主要处理无线通信。

180.需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。此外,需要指出的是,本技术实

施方式中的方法和装置的范围不限按示出或讨论的顺序来执行功能,还可包括根据所涉及的功能按基本同时的方式或按相反的顺序来执行功能,例如,可以按不同于所描述的次序来执行所描述的方法,并且还可以添加、省去、或组合各种步骤。另外,参照某些示例所描述的特征可在其他示例中被组合。

181.通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到上述实施例方法可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件,但很多情况下前者是更佳的实施方式。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分可以以计算机软件产品的形式体现出来,该计算机软件产品存储在一个存储介质(如rom/ram、磁碟、光盘)中,包括若干指令用以使得一台终端(可以是手机,计算机,服务器,或者网络设备等)执行本技术各个实施例所述的方法。

182.上面结合附图对本技术的实施例进行了描述,但是本技术并不局限于上述的具体实施方式,上述的具体实施方式仅仅是示意性的,而不是限制性的,本领域的普通技术人员在本技术的启示下,在不脱离本技术宗旨和权利要求所保护的范围情况下,还可做出很多形式,均属于本技术的保护之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。