1.本发明涉及索引源数组中的元素。

背景技术:

2.索引数组中的数据元素是计算硬件的运算中普遍存在的任务。例如,它是内插运算的关键启用过程。

3.通常,待索引的数据元素的数组被存储在存储器中。为了从数组中检索特定期望的数据元素,该期望的数据元素的索引通常用于计算存储器地址,然后通过访问所计算的存储器地址来检索数据元素。计算存储器地址的需要强加计算负担。计算大量任意索引的地址可能是效率低的—尤其对某些类型的硬件来说如此。然而,迄今,没有其他替代方案。

技术实现要素:

4.提供本发明内容是为了以简化的形式介绍下文在具体实施方式中进一步描述的一系列概念。本发明内容不旨在标识所要求保护的主题的关键特征或必要特征,也不旨在用于限制所要求保护的主题的范围。

5.提供了一种索引源数组中的数据元素的硬件实现的方法。所述方法包括:生成大量移位副本数组;接收用于索引所述源数组的索引;以及根据接收到的索引,从所述移位副本数组中检索一个或多个数据元素。还公开了一种相关处理系统,所述相关处理系统包括存储器和用于索引所述存储器中的源数组中的数据元素的硬件。

6.根据一个方面,提供了一种索引存储器中的源数组中的数据元素的硬件实现的方法,所述方法包括:

7.基于所述源数组生成大量移位副本数组,每个移位副本数组在相应的移位位置处包括所述源数组的数据元素;

8.接收用于索引所述源数组的多个索引,所述多个索引中的每个索引指示所述源数组中的目标位置;以及

9.对于所述多个索引中的每个索引:

10.从相应的一个或多个移位副本数组中检索一个或多个数据元素,其中所述一个或多个移位副本数组根据所述索引来选择。

11.对于每个索引,所述检索到的一个或多个数据元素可以包括所述源数组的在所述目标位置周围的有限邻域中的数据元素。此类数据元素将被表示“邻域数据元素”。在一些实施方案中,邻域数据元素可以是在源数组的一个或多个维度上最接近于目标位置的数据元素(例如,相对于目标位置在左边/在右边/在上方/在下方的数据元素)。在其他示例中,邻域可以更广泛,并且可以在目标位置周围包括数组的更大部分。

12.在一些实施方案中,邻域可以与用于在目标位置处生成数据值的采样/内插内核的范围一致。

13.通常,从数组中检索任意元素可能是效率低的任务—特别是当使用某些类型的硬

件来实现时。本方法取代在将数据扩展成多个移位版本情况下索引单个源数组、随后访问与每个期望的索引相对应的(一个或多个)移位版本的任务。在某些情况下,此方法能够优于常规“直接”索引方法提供性能增益。例如,此方法在需要以变化的位置偏移访问许多数据元素时可以是特别有益的,其中位置偏移位于有限范围内。此方法还可以更好地适合于在某些类型的硬件—例如,被适配用于实现神经网络的硬件上实现。

14.由于每个移位副本数组涉及源数组的相应的移位位置,所以移位副本数组的数量等于所考虑的移位位置的数量。移位位置可以包括在一个、两个或更多个维度上的移位。移位可以是整数移位。如果移位例如由在一个维度上 1和

‑

1的移位构成,则存在两个移位副本数组。如果移位例如由在两个维度上介于 1与

‑

1之间的移位的所有组合构成,则存在与( 1,0)、( 1, 1)、(0, 1)、(

‑

1, 1)、(

‑

1,0)、(

‑

1,

‑

1)、(0,

‑

1)和( 1,

‑

1)的(x,y)移位相对应的八个移位副本数组。在这里,应理解,“移位”(0,0)是源数组。

15.从被访问的每个移位副本数组中检索一个数据元素(不论一个移位副本数组或不止一个移位副本数组是否被访问)。

16.在一些实施方案中,所述方法可以包括输出一个或多个检索到的数据元素。在一些实施方案中,所述方法可以包括输出根据一个或多个检索到的数据元素内插的值。

17.生成移位副本数组可以包括用一组滤波器内核对源数组进行卷积,每个滤波器内核生成移位副本数组中的相应一个。滤波器内核可以是稀疏滤波器内核。每个稀疏滤波器内核可以包括由多个零值滤波器系数和单个非零滤波器系数构成的δ函数。非零系数可以等于1。

18.对于多个索引中的每个索引,检索相应的一个或多个数据元素可以包括从移位副本数组中的每一个中检索数据元素,所述方法任选地包括基于索引选通所检索到的元素,以从而选择数据元素和/或生成内插数据元素。

19.选通所检索到的元素可以包括定义所检索到的元素中的每一个的选通系数,其中针对除在目标位置周围的有限邻域中的邻域数据元素以外的数据元素的选通系数是零。选通可以包括将所检索到的数据元素乘以它们相应的选通系数,并且计算结果的总和。由于除邻域数据元素以外的数据元素的选通系数是零,所以这将导致乘以零。乘以零的结果总是为零。在某些硬件实现方式中,能够利用这来提高效率。能够检测零值被乘数(和/或乘数),并且作为响应,能够抑制乘法运算。乘法的输出被设定为零,而无需执行实际计算。这能够导致节能。

20.定义选通系数可以包括计算选通系数,其中计算包括线性求和,随后是非线性激活函数。这镜像神经网络中的过程并且特别很好地适合于在神经网络加速器硬件上实现。线性求和可以是加权线性求和。当被用于内插和/或(重新)采样时,以这种方式计算选通系数能够允许方便地实现采样或内插内核。选通能够实现对相关数据元素的选择和根据内核对那些数据元素的加权两者。

21.计算选通系数可以包括,对于多个索引中的索引在一个维度上:形式的第一求和,其中b=[n,n

‑

1,...,0,...,

‑

n 1,

‑

n],和s是在一个维度上的移位次数;定义激活函数,其在输入值介于0与1之间的情况下返回输入给其的值,否则返回0;激活函数的第一运算,在输入(y 1)情况下,给出输出y1;激活函数的第二运

算,在输入(y)情况下,给出输出y2;以及对y2的至少一个值运算的第二求和,其返回z2=w2y2 b2,其中w2=

‑

1并且b2=1,其中选通系数基于激活函数的第一运算的结果y1和第二求和的结果z2。

[0022]

在这里x是标量值,而b是矢量。因此,可以使用逐元素加法来实现第一求和。第二求和原则上还能通过逐元素加法来实现;然而,由于y2的仅一个元素是非零,所以能够将任务约简为标量求和。

[0023]

y1的非零值可以至少部分地定义至少一个数据元素的选通系数,并且z2(对其来说y2为非零)的值可以至少部分地定义至少一个其他数据元素的选通系数。任何其他选通系数是零。

[0024]

如上概述的,选通可以包括将移位数据元素乘以它们相应的选通系数,并且计算结果的总和。当移位是一维的时,y1的非零值可以定义一个数据元素的选通系数,并且z2(对其来说y2为非零)的值可以定义另一数据元素的选通系数。

[0025]

以上概述的计算选通系数的方式能够使得选通系数能够实现双线性内插。通过将计算用公式表示为线性求和和非线性激活函数的组合,所述方法适于在神经网络加速器硬件上实现。能够设计选通系数的其他公式化,其将实现其他形式的内插,诸如双三次内插。

[0026]

移位位置可以包括在多个维度上的移位位置,并且每个索引可以是在相应的多个维度上的索引并且计算选通系数任选地包括针对多个维度中的每个维度重复以上概述的计算,并且计算结果的外积。这可使得选通系数能够在两个或更多个维度上实现双线性内插。再次,选通系数的其他公式化能够允许在两个或更多个维度上进行其他形式的内插(诸如双三次内插)。

[0027]

目标数据元素中的至少一个的选通系数可以是浮点值。也就是说,选通系数不必是整数。

[0028]

多个索引可以包括浮点索引。换句话说,索引可以是非整数值。

[0029]

所述方法可以包括在源数组的数据元素之间内插,其中索引方法用于检索数据元素以进行内插。内插可以包括线性内插或双线性内插或双三次内插。

[0030]

可以在基于运动矢量场使图像或特征图扭曲的方法中使用如上概述的方法。例如,这在数组包括图像或特征映射时可以是特别有用的。运动矢量场可以包括多个运动矢量,例如在两个维度上。多个索引可以包括多个运动矢量,由多个运动矢量构成,或者基于多个运动矢量。

[0031]

所述方法可以由被适配成实现神经网络的硬件逻辑实现。例如,硬件逻辑可以是神经网络加速器装置的一部分。它可以包括专门地适配成执行加权线性求和的第一逻辑。它可以包括专门地适配成实现非线性激活函数的第二逻辑。

[0032]

另外提供了一种处理系统,所述处理系统包括存储器和用于索引所述存储器中的源数组中的数据元素的硬件,所述系统包括:

[0033]

移位生成器块,其被配置成基于所述源数组生成大量移位副本数组,每个移位副本数组在相应的移位位置处包括所述源数组的数据元素;以及

[0034]

索引块,其被配置成接收用于索引所述源数组的多个索引,所述多个索引中的每个索引指示所述源数组中的目标位置;并且

[0035]

对于所述多个索引中的每个索引:

[0036]

从相应的一个或多个移位副本数组中检索一个或多个数据元素,其中所述一个或多个移位副本数组根据所述索引来选择。

[0037]

所述移位生成器块可以包括多个数字滤波器,其中每个数字滤波器被配置成通过用相应的滤波器内核对所述源数组进行卷积来生成所述移位副本数组中的相应一个。

[0038]

所述索引块可以被配置成从所述移位副本数组中的每一个中检索数据元素,并且所述索引块可以包括选通单元,所述选通单元被配置成选通所述检索到的元素,从而选择数据元素和/或生成内插数据元素。

[0039]

还提供一种处理系统,该处理系统被配置为执行如上概述的方法。

[0040]

该处理系统可以在集成电路上的硬件中体现。该处理系统可以是图形处理系统。或者,它可以是神经网络加速器系统。

[0041]

一种使用集成电路制造系统来制造如权利要求15至19中任一项所述的处理系统的方法。

[0042]

还提供了一种使用集成电路制造系统来制造如上概述的处理系统的方法,所述方法包括:

[0043]

使用布局处理系统来处理该处理系统的计算机可读描述以便生成体现该处理系统的集成电路的电路布局描述;以及

[0044]

使用集成电路生成系统来根据电路布局描述制造处理系统。

[0045]

还提供了一种计算机可读代码,该计算机可读代码被配置成使得当代码被运行时执行如上概述的方法。还提供了一种计算机可读存储介质,在其上编码有计算机可读代码。

[0046]

根据另一示例,提供了一种集成电路定义数据集,当在集成电路制造系统中被处理时,该集成电路定义数据集将集成电路制造系统配置成制造如上概述的处理系统。

[0047]

还提供了一种非暂时性计算机可读存储介质,在其上存储有如上概述的处理系统的计算机可读描述,当在集成电路制造系统中被处理时,该计算机可读描述使集成电路制造系统制造体现该处理系统的集成电路。

[0048]

更进一步提供了一种非暂时性计算机可读存储介质,在其上存储有如上概述的处理系统的计算机可读描述,当在集成电路制造系统中被处理时,该计算机可读描述使集成电路制造系统:

[0049]

使用布局处理系统来处理该处理系统的计算机可读描述以便生成体现该处理系统的集成电路的电路布局描述;以及

[0050]

使用集成电路生成系统,根据所述电路布局描述来制造所述图形处理系统。

[0051]

还提供了一种集成电路制造系统,该集成电路制造系统被配置成制造如上概述的处理系统。

[0052]

还提供了一种集成电路制造系统,该集成电路制造系统包括:

[0053]

非暂时性计算机可读存储介质,在其上存储有如上所概述的处理系统的计算机可读描述;

[0054]

布局处理系统,该布局处理系统被配置成处理计算机可读描述以便生成体现处理系统的集成电路的电路布局描述;和

[0055]

集成电路生成系统,该集成电路生成系统被配置成根据所述电路布局描述来制造所述处理系统,

[0056]

其中该处理系统包括:

[0057]

存储器,用于存储数据元素的源数组;

[0058]

移位生成器块,其被配置成基于所述源数组生成大量移位副本数组,每个移位副本数组在相应的移位位置处包括所述源数组的数据元素,由此移位副本数组的数量等于移位位置的数量;以及

[0059]

索引块,其被配置成接收用于索引所述源数组的多个索引,所述多个索引中的每个索引指示所述源数组中的目标位置;并且

[0060]

被配置成,对于所述多个索引中的每个索引:

[0061]

根据所述索引来访问所述移位副本数组中的一个或多个,并且

[0062]

从所述相应的一个或多个移位副本数组中检索一个或多个目标数据元素。

[0063]

布局处理系统可被配置为确定从集成电路描述导出的电路的逻辑部件的位置信息,以生成体现该处理系统的集成电路的电路布局描述。

[0064]

可提供用于执行本文中描述的任一方法的计算机程序码。可提供非暂时性计算机可读存储介质,在其上存储有计算机可读指令,所述计算机可读指令在计算机系统处执行时使所述计算机系统执行本文中描述的任何方法。

[0065]

如对本领域的技术人员显而易见的,上述特征可以适当地组合,并且可以与本文所述的示例的任何方面组合。

附图说明

[0066]

现在将参考附图详细描述示例,在附图中:

[0067]

图1示出了根据一个示例的处理系统的框图,包括用于索引源数组中的数据元素的硬件;

[0068]

图1a更详细地图示了图1的选通单元;

[0069]

图2是图示了索引数据元素的方法的流程图;

[0070]

图3图示了根据另一示例的索引数据元素的方法;

[0071]

图3a图示了针对图3的方法计算选通系数的方法;

[0072]

图4图示了根据一个示例的索引方法的运算的原理;

[0073]

图5a示出了根据一个示例的可用于计算选通系数的激活函数;

[0074]

图5b示出了根据另一示例的可用于计算选通系数的激活函数;

[0075]

图6是能够在上面实现索引和/或内插的方法的示例性nna的框图;

[0076]

图7示出了在其中实现根据一个示例的处理系统的计算机系统;以及

[0077]

图8示出用于生成体现图形处理系统的集成电路的集成电路制造系统。

[0078]

附图示出各种示例。技术人员将理解,附图中所示的元件边界(例如,框、框的组,或其他形状)表示边界的一个示例。在一些示例中,情况可能是一个元件可以被设计为多个元件,或者多个元件可以被设计为一个元件。在适当的情况下,贯穿各附图使用共同附图标记来指示相似特征。

具体实施方式

[0079]

通过示例的方式给出以下描述,以使本领域的技术人员能够制造和使用本发明。

本发明不限于本文中描述的实施方案,并且对所公开的实施方案的各种修改对于所属领域的技术人员而言将是显而易见的。

[0080]

现在仅通过示例的方式来描述实施方案。

[0081]

定义:如本文所使用的内插是指估计方法,其包括在已知数据点的离散集的范围内构建新数据点。

[0082]

本发明人已认识到内插—以及,特别是密集内插—不管其普遍存在,都可能是效率低且计算密集的任务。问题对于被优化来实现诸如神经网络加速器(nna)的机器学习算法的硬件来说可能是特别严重的。这种硬件通常不很好地适于计算数组中的偏移并且从存储器中的该数组中检索任意期望的数据元素。

[0083]

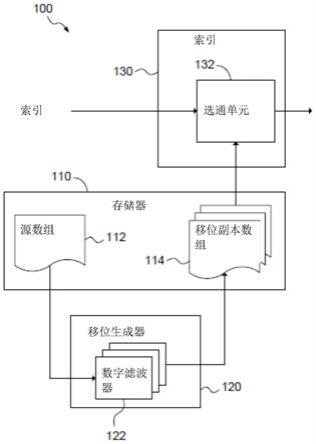

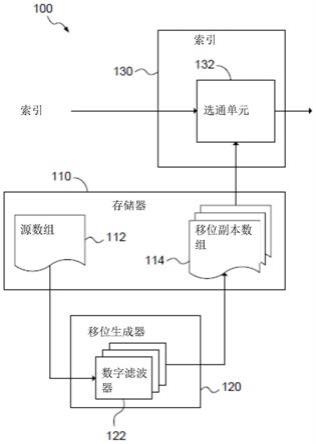

图1是根据一个示例的处理系统100的框图。处理系统包括存储器110,其存储待索引的源数组112。系统还包括用于索引源数组的数据元素的硬件,此硬件包括移位生成器块120和索引块130。移位生成器块120包括一组数字滤波器122。索引块130包括选通单元132。

[0084]

图2是图示了根据一个示例的由图1的处理系统100执行的方法的流程图。在步骤210中,移位生成器块120基于源数组112生成大量移位副本数组114。每个移位副本数组114在相应的移位位置处包括源数组的数据元素。移位副本数组由移位生成器块120输出到存储器110。

[0085]

在此示例中,移位副本数组114由数字滤波器122生成。每个数字滤波器被配置成用稀疏滤波器内核对源数组112进行卷积,以生成移位副本数组114中的相应一个。例如,取一维数组的简单示例,稀疏滤波器内核[1 0 0]将使源数组的数据元素向右移位一个地方。稀疏滤波器内核[0 0 1]使数据元素向左移位一个地方。应理解,不必要借助于数字滤波生成移位副本数组;然而,以这种方式实现运算可以是有利的—特别是当使用被优化用于高效地执行内积和/或数字滤波运算的硬件时。这可以包括诸如图形处理单元(gpu)或nna的加速器硬件。

[0086]

在步骤220中,索引块130接收用于索引源数组的多个索引。每个索引指示源数组中的目标位置。注意,通常,索引可以指示数组中的整数或非整数目标位置。然而,仅对于本示例,将假定索引是整数。在步骤230中,对于多个索引中的每个索引,索引块从移位副本数组之一中检索至少一个数据元素。从中检索数据元素的移位副本数组是根据索引选择的。

[0087]

在此示例中,不是计算与原始源数组中的每个目标位置相对应的存储器位置,而是处理系统替代地从适当的移位副本数组中检索所期望的数据元素。本质上,索引到源数组中的任务用选择移位副本数组中的哪一个包含所期望的数据元素的任务替换。此方法可以特别地本身适用于需要进行大量索引运算的应用。例如,在一些应用中,可能有必要产生密集输出数组,其中输出数组的每个元素是从源数组中位于有限距离远处的元素导出的。这是用于重新采样、内插和扭曲运算等的情况。

[0088]

能够以若干方式执行选择要检索哪一个(或哪些)数据元素—即,选择从中检索数据元素的移位副本数组—的任务。在一些示例中,索引块130可以选择性地访问移位副本数组114,以仅检索感兴趣的数据元素。然而,在许多情况下,访问所有移位副本数组114并且从每个移位副本数组中检索数据元素可能是更高效的。这些检索到的数据元素然后由选通单元132选通,以选择相关的数据元素并且忽略不相关的数据元素。当索引是整数值时,如在图2的示例中一样,选通单元的任务是选择与每个索引相对应的一个唯一数据元素,并且

拒绝所检索到的源自其他移位副本数组的数据元素。可以例如通过将所期望的数据元素乘以等于1的值、将其他元素乘以等于0的值、并且计算结果的总和来实现这个。也就是说,选通单元132可以用为0或1的选通系数实现内积计算。常常能够在硬件中非常高效地实现此类积计算—例如,在gpu或nna的情况下。

[0089]

在索引不是整数值的情况下(特别地,在索引是浮点值的情况下),能够采用选通单元132以特别受益。非整数索引意味着处理系统需要估计位于源数组中的离散数据元素之间的数据值。换句话说,某种形式的内插是必需的。在这些情况下,选通单元132能够用于既选择要在内插中使用的相关检索到的数据元素,然后又用于进行内插所必需的计算。现在将参考图1a和图3描述这样的示例。

[0090]

图1a是选通单元132的框图。如图所示,选通单元包括:系数计算块134,其被配置成计算选通系数;以及內积块136,其被配置成用从移位副本数组114中检索到的数据元素来计算选通系数的内积。

[0091]

图3中的步骤210(生成移位副本数组)与图2中的步骤210相同。除了所接收到的索引是浮点值之外,图3中的步骤220a(接收索引)与图2中的步骤220相同。在步骤232中,索引单元130从移位副本数组中的每一个中检索数据元素。在步骤234中,选通单元132计算选通系数。这由系数计算块134完成。在步骤236中,每个检索到的数据元素被乘以相应的选通系数;并且在步骤238中计算这些乘法的结果的总和。步骤236和238由内积块136进行。

[0092]

通过对选通系数进行适当的计算,处理系统能够实现各种不同种类的内插。将针对计算选通系数以便实现双线性内插的示例在下面提供详细描述。然而,选通系数能够实现最近邻内插、双三次内插或任何其他类型的内插。

[0093]

能够参考图4说明处理系统100的运算的原理。这示意性地图示了针对在其中生成并在索引方法中使用四个移位副本数组的简化一维示例的源数组和移位副本数组。实心黑色圆圈表示源数组i(x)的八个数据元素i(0)

…

i(7)。无阴影圆圈表示移位副本数组。i(x

‑

1)表示源数组的数据元素向右移位了一个地方的移位副本数组。同样地,i(x 1)表示源数组的数据元素向左移位了一个地方的移位副本数组,依此类推。移位副本数组的范围由图4中的垂直虚线指示。在本示例中,在此范围外移位的数据元素被丢弃。因此,在每个移位副本数组中,至少一个数据元素被从数组的左端或右端丢弃。灰色阴影圆圈表示填充元素。这些被使用代替源数组中的未定义数据元素。能够根据诸如将为技术人员所公知的填充算法(零填充、镜像对称等)的任何合适的填充算法来定义填充值。例如:在移位副本数组i(x 2)中,从数组的左手侧丢弃两个数据元素i(0)和i(1),并且在右手侧添加两个填充数据元素(对应于源数组的未定义数据元素i(8)和i(9))。同样地,在移位副本数组i(x

‑

1)中,从数组的右手侧丢弃一个数据元素i(7),并且在左手侧添加一个填充数据元素(对应于源数组的未定义数据元素i(

‑

1))。

[0094]

让我们假定正在生成具有八个数据元素的密集输出数组。为了生成第四输出数据元素o(3),索引单元从每个数组(包括源数组和移位副本数组)中检索第四数据元素。通过访问移位副本数组中的每一个中的相同位置,系统能够检索源数组的给定局部区域中的所有数据元素。在图4所示的示例中,选通单元132被提供有i(1)、i(2)、i(3)、i(4)和i(5)。这些是i(3)的区域中的数据元素。从这些检索到的数据元素中,选通单元能够选择和/或内插适当的值。例如,如果输出o(3)的输入索引是1.5,并且内插方法是双线性内插,则选通单元

132能够将0.5的选通系数应用于i(1)和i(2)中的每一个,并且能够将0的选通系数应用于其他检索到的数据元素中的每一个。这将导致为i(1)和i(2)的加权平均值的内内插“i(1.5)”。换句话说,选通单元132能够同时地选择适当的邻域i(1)和i(2)以用于内插,并且通过适当地对这些数据元素进行加权来进行内插。

[0095]

现在将描述针对双线性内插的情况的选通系数的计算的更详细描述。在本示例中,选通系数的计算是以使它变得特别适合于在nna硬件中实现的方式构造的。

[0096]

将首先参考图3a描述用于一维双线性内插的选通系数的计算。然后能够容易地将这扩展到更多维度。

[0097]

为了在一个维度上计算索引的选通值,系数计算块134计算形式的第一求和(步骤310),其中b=[n,n

‑

1,...,0,...,

‑

n 1,

‑

n],和s是在一个维度上的移位次数。然后定义以下激活函数:f(x)=max(0,sign(

‑

x 1 ε))max(0,x),其中ε是硬件能够表示的最小正数。此激活函数是非线性函数。有效地,当x介于零与一之间时,它返回输入值x。对于在范围0至1外的x的值,激活函数返回零。此激活函数被图示在图5a中。如将由本领域的技术人员所理解的,nna的硬件将通常包括用于高效地实现激活函数的硬件。

[0098]

激活函数被应用两次(用于在一个维度上进行线性内插)。这两个应用将在下面被称为“流”。一个选通系数经由每个流计算。对于最近邻插插,将存在仅单个流。对于双线性内插(如在下面进一步讨论的),将存在四个流。

[0099]

在第一流中,将激活函数应用(步骤320a)于输入(y 1)。也就是说,第一流返回y1=f(y 1)。在第二流中,将激活函数应用(步骤320b)于输入y。也就是说,第二流返回y2=f(y)。

[0100]

接下来,系数计算块134计算返回z1=w1y1 b1的求和330a,其中w1=1并且b1=0;以及返回z2=w2y2 b2的另一个求和330b,其中w2=

‑

1并且b2=1。

[0101]

注意,在以上示例中,x是标量值,而b是矢量。因此,可以使用逐元素加法来实现第一求和310。附加求和330a、330b原则上还能通过逐元素加法来实现;然而,由于y1的一个元素和y2的一个元素是非零,所以能将任务约简为标量求和。附加地,由于一个求和330a返回z1=y1,所以能在没有实际求和运算的情况下实现它。然而,在本示例中,所有求和都以全矢量形式进行。这是出于对称的原因而做的,并且另外因为当使用nna硬件来实现方法时可以是有利的。

[0102]

此时,z1包含用于一维线性内插的选通系数中的一个;并且y2包含另一个。由系数计算块134进行的剩余步骤目的旨在从这些矢量中选择相关值并进行组合。值使用形式z1οσ

′

(y1) z2οσ

′

(y2)的计算来组合(步骤340)。在这里,σ

′

=1

‑

σ,其中σ是在输入为0情况下返回1否则返回0的函数(例如,狄拉克δ函数(dirac delta function))。因此,函数σ

′

在输入为0时返回值0,否则返回1。符号

°

表示其两个运算数之间的逐元素乘法。

[0103]

这些计算的结果是被提供给內积块136的选通系数的矢量。內积块136用从移位副本数组114中检索到的数据元素的矢量来计算选通系数的矢量的内积。

[0104]

考虑两个简单的数值示例来应用以上计算可以是有益的。在两个示例中,移位次数是s=3,并且b=[1,0,

‑

1]。

[0105]

在示例a中,假定输入索引x=

‑

0.62。我们然后具有:y=[0.38,

‑

0.62,

‑

1.62];然后y1=[0,0.38,0];以及y2=[0.38,0,0];z1=[0,0.38,0];并且z2=[0.62,1,1]。最后,σ

′

(y1)=[0,1,0]并且σ

′

(y2)=[1,0,0]并且z1σ

′

(y1) z2σ

′

(y2)=[0,0.38,0]ο[0,1,0] [0.62,1,1]ο[1,0,0]=[0.62,0.38,0]。

[0106]

在示例b中,索引x=0.24。我们然后具有:y=[1.24,0.24,

‑

0.76];然后y1=[0,0,0.24];以及y2=[0,0.24,0];z1=[0,0,0.24];并且z2=[1,0.76,1]。最后,σ

′

(y1)=[0,0,1]并且σ

′

(y2)=[0,1,0]并且z1σ

′

(y1) z2σ

′

(y2)=[0,0,0.24]ο[0,0,1] [1,0.76,1]ο[0,1,0]=[0,0.76,0.24]。

[0107]

如能够从这些示例中看到的,选通系数被计算以在一个维度上正确地实现线性内插。对于双线性内插(例如在两个维度上),能够根据针对各个维度的选通系数的相应矢量的外积来计算选通系数。

[0108]

应理解,以上阐述的计算的序列仅仅是正确地计算用于线性内插或双线性内插的选通系数的一个方式。它们能同样地由运算的替代序列计算。然而,据信以上序列可以特别适用于在nna硬件上实现,因为计算是主要以线性求和和非线性激活函数的形式构造的。nna硬件被通常很好地适配并且专用于执行此类运算。

[0109]

图5b示出了能够在双线性内插的替代实现方式中使用的另一激活函数f’(x)的示例。此激活函数用实现三角激活函数的单个块替换图3a的块320a、320b、330a、330b和340。换句话说,能够以稍微更复杂的激活函数为代价减少块的数量。在数学上,能够将三角激活函数定义为f

′

(x)=max(0,1

‑

|x|)。能够借助于查找表(lut)实现这个。使用lut来实现激活函数的一个优点是它可以使在软件中重新配置内插变得更容易。

[0110]

现在将描述用于在nna中实现(双线性)内插的一般框架。等式是按扭曲运算抛出的,其中密集运动场用于使目标帧朝向参考帧扭曲。

[0111]

运动场描述像素如何从参考帧i

r

(x,y)移动到目标帧i

t

(x,y),并且由分别通过u(x,y)由v(x,y)表示的水平位移和垂直位置组成。扭曲意在计算i

t

(x u,y v)。基于由jaderberg等人提出的技术(max jaderberg,karen simonyan,andrew zisserman,koray kavukcuoglu,“spatial transformer networks”,advances in neural information processing systems 28(nips 2015)),能够通过以下等式来计算基于密集运动场的目标帧的扭曲版本:

[0112][0113]

其中x

s

=x u,y

s

=y v。此公式表明扭曲运算由索引i

t

(m,n)和双线性内插运算max(0,1

‑

|x

s

‑

m|)max(0,1

‑

|y

s

‑

n|)组成。换言之,

[0114][0115]

其中并且

[0116]

在下文中,将首先在一维情况下描述扭曲方法,然后将其扩展到更一般的二维情况。基于以上等式,定义在一维离散信号的情况下,

[0117][0118]

能够将此公式重写为两个矢量a和i

t

的点积,

[0119][0120]

如上先前讨论的,能够通过用一组稀疏(“独热”)滤波器对输入信号进行卷积来计算其所有条目除一个外都为零,以提供信号的一组移位版本。这些移位的程度能够由用户在通过m表示为移位次数的预定义区域之上定义。

[0121]

矢量a表示选通系数,并且能够由相当于感知器的两个层的硬件来实现,给定x

s

,所述两个层计算a。在第一层中每个单元m

i

计算α=x

s

‑

m

i

(若m

i

≤x

s

<m

i 1

的话),否则为0。在第二层中,α然后被从函数传y(x)=1

‑

x递以计算在前述等式中使用的1

‑

α。以这种方式,每个单元m

i 1

计算1

‑

α,若m

i

≤x

s

<m

i 1

的话。对于每个输入,这两个层中的每一个的仅一个单元计算非零值。

[0122]

如上先前所讨论的,感知器的激活函数被定义如下:

[0123][0124]

a是通过添加两个感知器的输出来计算的。

[0125]

此一维线性内插方案是直接了当的以扩展到两个维度。选通系数矩阵能够根据a

u

的外积计算,根据u和a

v

计算,根据v计算:

[0126][0127]

能够以与一维情况类似的方式生成移位副本i,但是移位现在是在均匀二维网格之上。

[0128]

现在参考图6,其图示了示例神经网络加速器(nna)2000,其可以被配置成根据以上阐述的示例的一个来实现索引的方法。

[0129]

图6的nna 2000被配置成通过一系列硬件遍次(其也可以被称为处理遍次)来计算深度神经网络(dnn)的输出。在每个遍次期间,硬件实现方式接收用于dnn的层的输入数据的至少一部分并且依照该层(并且任选地依照一个或多个后续层)处理所接收到的输入数据以产生处理后的数据。处理后的数据要么输出到存储器用作随后的硬件过程的输入数据,要么输出为dnn的输出。硬件实现方式能够在单个硬件遍次期间处理的层数可以基于数据的大小、硬件实现方式和层的次序。例如,在硬件实现方式包括执行每种可能的层类型的硬件的情况下,包括第一卷积层、第一激活层、第二卷积层、第二激活层和池化层的dnn可以能够接收初始dnn输入数据,并且根据第一硬件遍次中的第一卷积层和第一激活层来处理该输入数据,然后将激活层的输出输出到存储器中,接着在第二硬件遍次中从存储器接收该数据作为输入,并且根据第二卷积层、第二激活层和池化层来处理该数据,以产生dnn的输出数据。

[0130]

图6的示例nna 2000包括输入模块2001、卷积引擎2002、累积缓冲器2004、逐元素运算模块2006、激活模块2008、归一化模块2010、池化模块2012、输出交织模块2014和输出模块2015。每个模块或引擎实现或处理一种或多种类型的层的全部或一部分。具体地,卷积引擎2002和累积缓冲器2004一起实现或处理卷积层或全连接层。激活模块2006处理或实现激活层。归一化模块2010处理或实现归一化层。池化模块2012实现池化层,并且输出交织模

块2014处理或实现交织层。

[0131]

输入模块2001被配置成接收当前硬件遍次的输入数据并且将其提供给下游模块以进行处理。接收输入数据的下游模块取决于当前硬件遍次中要处理的层。

[0132]

卷积引擎2002被配置为使用与特定卷积层相关联的权重对所接收的输入数据执行卷积运算。dnn的每个卷积层的权重可以被存储在如图6所示的系数缓冲器2016中,并且当特定卷积层正在由卷积引擎2002处理时,可以向卷积引擎2002提供该特定卷积层的权重。如果硬件实现方式支持可变权重格式,则卷积引擎2002可以被配置成接收指示正在处理的当前卷积层的权重的一种或多种格式的信息,以允许卷积引擎2002适当地解释和处理所接收到的权重。

[0133]

卷积引擎2002可以包括多个乘法器(例如,128个乘法器)和多个加法器,所述多个加法器将乘法器的结果相加以产生单个和。尽管在图6中示出了单个卷积引擎2002,但是在其他示例中,可以存在多个(例如,8个)卷积引擎,使得能够同时地处理多个窗口。

[0134]

卷积引擎专用于执行积求和计算。因此,它能够用于计算数据元素与选通系数的矢量之间的內积(图1中的內积块136)。它还能够用于实现在计算选通系数时涉及的线性总和(图1中的系数计算块134)。

[0135]

卷积引擎2002的输出被馈送到累积缓冲器2004。累积缓冲器2004被配置为接收卷积引擎的输出并且将其添加到累积缓冲器2004的当前内容中。以这种方式,累积缓冲器2004累积卷积引擎2002的结果。尽管在图6中示出了单个累积缓冲器2004,但是在其他示例中,可以存在多个(例如,8个,每卷积引擎一个)累积缓冲器。累积缓冲器2004将累积结果输出到逐元素运算模块2006,该逐元素运算模块根据在当前硬件过程期间是否要处理逐元素层,可能或可能不对累积结果进行运算。

[0136]

逐元素运算模块2006被配置成接收当前硬件过程的输入数据(例如,当在当前硬件过程中未处理卷积层时)或来自累积缓冲器2004的累积结果(例如,当在当前硬件过程中处理卷积层时)。逐元素运算模块2006可以取决于在当前硬件遍次中是否处理逐元素层以及/或者取决于是否要在逐元素层之前处理激活层而处理所接收到的输入数据或者将所接收到的输入数据传递到另一模块(例如,激活模块2008和/或归一化模块2010)。当逐元素运算模块2006被配置成处理所接收到的输入数据时,逐元素运算模块2006对所接收到的数据执行逐元素运算(任选地与可以从外部存储器获得的另一数据集一起)。逐元素运算模块2006可以被配置成执行任何合适的逐元素运算,诸如但不限于:相加、相乘、最大值和最小值。逐元素运算可以包括标量值与矢量(或矩阵或张量)中的每个值之间的代数运算。对矢量/矩阵/张量的每个元素执行相同的代数运算。例如,标量值[a]与矢量[b c d]之间的逐元素加法的结果是矢量[a b a c a d]。例如,逐元素运算模块2006可以被配置成执行逐元素加法以实现图3a的第一求和310。然后,根据是否要在逐元素层之后处理激活层,将逐元素运算的结果提供给激活模块2008或归一化模块2010。

[0137]

激活模块2008被配置成接收下列中的一者作为输入数据:(例如,当在当前硬件遍次中未处理卷积层时)(经由逐元素运算模块2006)对硬件遍次的原始输入;(例如,当在当前硬件遍次中处理卷积层并且在当前硬件遍次中未处理逐元素层或者在当前硬件遍次中处理逐元素层但是在激活层之后时)(经由逐元素运算模块2006)累积数据。激活模块2008被配置为将激活函数应用于输入数据,并且将输出数据提供回逐元素运算模块2006,其中

该输出数据被直接或者在逐元素运算模块2006对其进行处理之后转发到归一化模块2010。在一些情况下,应用于由激活模块2008接收的数据的激活函数可在每个激活层变化。在这些情况下,可以(例如,在存储器中)存储指定要应用于每个激活层的激活函数的一个或多个属性的信息,并且可以将在特定硬件遍次中处理的激活层的相关信息在该硬件遍次期间提供给激活模块2008。

[0138]

已经在上面描述了激活函数在选通系数的计算中的使用。在一些情况下,激活模块2008可被配置为在查找表的条目中存储表示激活函数的数据。在这些情况下,输入数据可用于查找查找表中的一个或多个条目以及表示激活函数的输出的输出值。例如,激活模块2008可被配置为通过在从查找表读取的两个或更多个条目之间进行内插来计算输出值。

[0139]

归一化模块2010被配置成接收下列中的一者作为输入数据:(例如,当在当前硬件遍次未处理卷积层并且在当前硬件遍次中未处理逐层元素层和激活层两者时)(经由逐元素运算模块2006)硬件遍次的原始输入数据;(例如,当在当前硬件遍次中处理卷积层并且在当前硬件遍次中未处理逐元素层和激活层两者时)(经由逐元素运算模块2006)累积输出;以及逐元素运算模块和/或激活模块的输出数据。然后,归一化模块2010对所接收的输入数据执行归一化函数以产生归一化数据。在一些情况下,归一化模块2010可被配置为执行局部响应归一化(lrn)函数和/或局部对比度归一化(lcn)函数。然而,对于本领域的技术人员将显而易见的是,这些仅是示例,并且归一化模块2010可被配置为实现任何合适的一个或多个归一化函数。不同的归一化层可被配置为应用不同的归一化函数。

[0140]

池化模块2012可接收来自归一化模块2010的归一化数据,或者可经由归一化模块2010接收到归一化模块2010的输入数据。在一些情况下,可以经由xbar 2018在归一化模块2010与池化模块2012之间传输数据。在本文中,术语“xbar”用于指包含路由逻辑的简单硬件模块,该路由逻辑以动态方式将多个模块连接在一起。在此示例中,xbar可以取决于在当前硬件遍次中将处理哪些层而动态地连接归一化模块2010、池化模块2012和/或输出交织模块2014。因此,xbar可以在每个硬件遍次中接收指示要连接哪些模块2010、2012、2014的信息。

[0141]

池化模块2012被配置为对所接收的数据执行池化函数,诸如但不限于max函数或mean函数,以产生池化数据。池化层的目的是减小表示的空间大小,以减少网络中参数和计算的数量,并且因此也控制过度拟合。在一些示例中,在每个池化层定义的滑动窗口上执行池化运算。

[0142]

输出交织模块2014可接收来自归一化模块2010的归一化数据、(经由归一化模块2010)对归一化函数的输入数据,或者来自池化模块2012的池化数据。在一些情况下,可以经由xbar 2018在归一化模块2010、池化模块2012和输出交织模块2014之间传输数据。输出交织模块2014被配置为执行重新排列运算以产生处于预先确定的顺序的数据。这可包括对所接收的数据进行排序和/或转置。由最后一层生成的数据被提供给输出模块2015,其中该数据被转换为对当前硬件过程的期望的输出格式。

[0143]

归一化模块2010、池化模块2012和输出交织模块2014可各自访问共享缓冲器2020,这些模块2010、2012和2014可使用该共享缓冲器向其中写入数据并且从中检索数据。例如,这些模块2010、2012、2014可使用共享缓冲器2020来重新排列所接收的数据或所生成的数据的顺序。例如,这些模块2010、2012、2014中的一个或多个模块可被配置为将数据写

入共享缓冲器2020并且以不同的顺序读出相同的数据。在一些情况下,尽管归一化模块2010、池化模块2012和输出交织模块2014中的每一者都可以访问共享缓冲器2020,但是归一化模块2010、池化模块2012和输出交织模块2014中的每一者可被分配共享缓冲器2020的仅它们自身可访问的一部分。在这些情况下,归一化模块2010、池化模块2012和输出交织模块2014中的每一个均可以仅能够从共享缓冲器2020读取它们已写入共享缓冲器2020中的数据。

[0144]

如上所述,硬件实现方式2000的在任何硬件遍次期间使用或活动的模块基于在该硬件遍次期间处理的层。特别地,仅与在当前硬件过程期间处理的层相关的模块或部件被使用或者是活动的。如上所述,基于dnn中层的顺序以及可选地基于一个或多个其他因素(诸如数据的大小)来(通常预先通过例如软件工具)确定在特定的硬件过程期间处理的层。例如,在一些情况下除非能够在不将数据写入到层之间的存储器的情况下处理多个层,否则硬件实现方式可以被配置成每硬件遍次执行单个层的处理。例如,如果第一卷积层后面紧接有第二卷积层,则将必须在单独的硬件遍次中执行每个卷积层,因为来自第一硬件卷积的输出数据需要被先写出到存储器才能够被用作第二硬件卷积的输入。在这些硬件遍次中的每一个中,仅与卷积层相关的模块、部件或引擎,诸如卷积引擎2002和累积缓冲器2004,可以被使用或者是活动的。

[0145]

如现在将显而易见的,前述示例的各种修改是可能的。尽管图6的硬件实现方式2000图示了模块、引擎等的特定布置次序,并且因此图示了数据的处理如何流经处理模块,但是应领会,这仅是示例,并且在其他示例中,模块、引擎可以以不同的方式布置。此外,其他nna可以支持附加或替代类型的神经网络层并且因此可以包括不同的模块、引擎等。

[0146]

尽管前面的描述已通过示例集中于线性内插和双线性内插,但是可以根据其他示例实现其他内插方法。特别地,通过在被索引的目标位置周围选取不同的邻域,并且计算不同的选通系数,可以提供其他类型的内插。对于最近邻内插,邻域将由单个数据元素构成,并且除了此数据元素(对其来说选通系数将等于1)之外,选通系数将等于0。对于在一个维度上的线性内插,邻域由两个数据元素构成。对于在两个维度上的双线性内插,邻域由四个数据元素(2x 2)构成。对于更高阶内插(例如,对于双三次内插),邻域可能更大。各种类型的常规内插的内插内核将为本领域技术人员公知。同样地,以上示例中描述的方法通常将适用于仍待在将来开发的内插内核。

[0147]

应注意,前面的描述集中于以相对形式—即,作为在中央数据元素周围的区域中的偏移提供的索引。然而,如经由本领域技术人员所理解的,能够利用等式的合适的重新公式化以绝对形式等效地提供索引。

[0148]

图7示出了可以在其中实现本文描述的图形处理系统的计算机系统。计算机系统包括cpu 902、nna 904、存储器906和其他装置914,诸如显示器916、扬声器918,以及相机919。在nna 904上实现处理块910(对应于处理块100)。在其他示例中,处理块910可以在cpu 902上实现。计算机系统的部件可经由通信总线920彼此进行通信。暂存器912(与存储器110相对应)被实现为存储器906的一部分。

[0149]

图1的处理系统被示出为包括许多功能块。这仅是示意性的,并不旨在限定此类实体的不同逻辑元件之间的严格划分。每个功能块可以任何合适的方式提供。应理解,本文中描述为由处理系统形成的中间值不需要由处理系统在任何时间点物理地生成,并且可以只

表示方便描述由处理系统在其输入与输出之间执行的处理的逻辑值。

[0150]

本文中所描述的处理系统可体现在集成电路上的硬件中。本文中所描述的处理系统可配置成执行本文所描述的任一种方法。通常,能够在软件、固件、硬件(例如,固定逻辑电路系统)或其任何组合中实现以上描述的功能、方法、技术或部件中的任一个。本文可以使用术语“模块”、“功能”、“部件”、“元件”、“单元”、“块”和“逻辑”来概括地表示软件、固件、硬件或其任何组合。在软件实现方式的情况下,模块、功能、部件、元件、单元、块或逻辑表示程序码,所述程序码在处理器上执行时执行指定任务。本文中所描述的算法和方法可以由执行码的一个或多个处理器执行,所述码使处理器执行算法/方法。计算机可读存储介质的示例包括随机存取存储器(ram)、只读存储器(rom)、光盘、闪存存储器、硬盘存储器以及可以使用磁性、光学和其他技术来存储指令或其他数据并且可以由机器存取的其他存储器装置。

[0151]

如本文中所使用的术语计算机程序码和计算机可读指令是指供处理器执行的任何种类的可执行码,包含以机器语言、解释语言或脚本语言表达的码。可执行码包含二进制码、机器码、字节码、定义集成电路的码(例如硬件描述语言或网表),以及用例如c、java或opencl等编程语言码表达的码。可执行码可以是例如任何种类的软件、固件、脚本、模块或库,当在虚拟机或其他软件环境中被适当地执行、处理、解释、编译、运行时,这些软件、固件、脚本、模块或库使支持可执行码的计算机系统的处理器执行由所述码指定的任务。

[0152]

处理器、计算机或计算机系统可以是任何种类的装置、机器或专用电路,或其集合或一部分,它具有处理能力使得可以执行指令。处理器可以是任何种类的通用或专用处理器,例如cpu、gpu、nna、片上系统、状态机、媒体处理器、专用集成电路(asic)、可编程逻辑阵列、现场可编程门阵列(fpga)等。计算机或计算机系统可以包括一个或多个处理器。

[0153]

本发明还意图涵盖限定如本文中所描述的硬件的配置的软件,例如硬件描述语言(hdl)软件,用于设计集成电路或用于配置可编程芯片以执行所要功能。也就是说,可以提供一种在其上编码有形式为集成电路定义数据集的计算机可读程序代码的计算机可读存储介质,当在集成电路制造系统中被处理(即运行)时,该计算机可读程序代码将该系统配置成制造被配置成执行本文描述的任何方法的处理系统,或者制造包括本文描述的任何设备的处理系统。集成电路定义数据集可以是例如集成电路描述。

[0154]

因此,可以提供一种在集成电路制造系统处制造如本文所描述的处理系统的方法。此外,可以提供一种集成电路定义数据集,该集成电路定义数据集当在集成电路制造系统中被处理时,使制造处理系统的方法被执行。

[0155]

集成电路定义数据集可以是计算机代码的形式,例如作为网表,用于配置可编程芯片的代码,作为定义适合于在集成电路中以任何级别制造的硬件描述语言,包括作为寄存器传输级(rtl)代码,作为高级电路表示法(诸如verilog或vhdl),以及作为低级电路表示法(诸如oasis(rtm)和gdsii)。在逻辑上定义适合于在集成电路中制造的硬件的更高级表示法(诸如rtl)可以在计算机系统上处理,该计算机系统被配置用于在软件环境的上下文中生成集成电路的制造定义,该软件环境包括电路元件的定义和用于组合这些元件以生成由该表示法定义的集成电路的制造定义的规则。如通常软件在计算机系统处执行以便定义机器的情况一样,可能需要一个或多个中间用户步骤(例如,提供命令、变量等),以便将计算机系统配置为生成集成电路的制造定义,以执行定义集成电路以便生成该集成电路的

制造定义的代码。

[0156]

现在将参考图8描述在集成电路制造系统处处理集成电路定义数据集以便将该系统配置成制造处理系统的示例。图8示出集成电路(ic)制造系统1002的示例,该ic制造系统被配置成制造如本文任何示例中描述的处理系统。具体来说,ic制造系统1002包括布局处理系统1004和集成电路生成系统1006。ic制造系统1002被配置成接收ic定义数据集(例如,定义如本文任何示例中描述的处理系统),处理ic定义数据集,并且根据ic定义数据集来生成ic(例如,其体现如本文任何示例中描述的处理系统)。对ic定义数据集的处理将ic制造系统1002配置成制造体现如本文任何示例中描述的处理系统的集成电路。

[0157]

布局处理系统1004被配置成接收和处理ic定义数据集以确定电路布局。根据ic定义数据集确定电路布局的方法在本领域中是已知的,并且例如可以涉及合成rtl代码以确定要生成的电路的门级表示,例如就逻辑部件(例如nand、nor、and、or、mux和flip

‑

flop部件)而言。通过确定逻辑部件的位置信息,可以根据电路的门级表示来确定电路布局。这可以自动完成或者在用户参与下完成,以便优化电路布局。当布局处理系统1004已经确定电路布局时,其可将电路布局定义输出到ic生成系统1006。电路布局定义可以是例如电路布局描述。如本领域已知的,ic生成系统1006根据电路布局定义来生成ic。举例来讲,ic生成系统1006可实现生成ic的半导体装置制造工艺,其可涉及光刻和化学处理步骤的多步骤序列,在此期间,在由半导体材料制成的晶片上逐渐形成电子电路。电路布局定义可呈掩模的形式,其可以在光刻工艺中用于根据电路定义来生成ic。替代地,提供给ic生成系统1006的电路布局定义可呈计算机可读代码的形式,ic生成系统1006可使用所述计算机可读代码来形成用于生成ic的合适掩模。

[0158]

由ic制造系统1002执行的不同过程可全部在一个位置例如由一方来实施。替代地,ic制造系统1002可以是分布式系统,使得一些过程可在不同位置执行,并且可由不同方来执行。例如,以下阶段中的一些可以在不同位置和/或由不同方来执行:(i)合成表示ic定义数据集的rtl代码,以形成要生成的电路的门级表示;(ii)基于门级表示来生成电路布局;(iii)根据电路布局来形成掩模;以及(iv)使用掩模来制造集成电路。

[0159]

在其他示例中,在集成电路制造系统处对集成电路定义数据集的处理可以将该系统配置成在不处理ic定义数据集以便确定电路布局的情况下制造处理系统。举例来说,集成电路定义数据集可以定义例如fpga的可重新配置的处理器的配置,并且对所述数据集进行的处理可以将ic制造系统配置成(例如,通过将配置数据加载到fpga)生成具有所述定义的配置的可重新配置的处理器。

[0160]

在一些实施例中,当在集成电路制造系统中被处理时,集成电路制造定义数据集可以使集成电路制造系统生成如本文中描述的装置。例如,由集成电路制造定义数据集以上文参考图8描述的方式对集成电路制造系统进行配置,可以制造出如本文所述的装置。

[0161]

在一些示例中,集成电路定义数据集可以包括在数据集处定义的硬件上运行的软件,或者与在数据集处定义的硬件组合运行的软件。在图8所示的实例中,ic生成系统可以进一步由集成电路定义数据集配置成在制造集成电路时根据在集成电路定义数据集中定义的程序代码将固件加载到所述集成电路上,或者以其它方式向集成电路提供与集成电路一起使用的程序代码。

[0162]

与已知的实现方式相比,在本技术中阐述的概念在装置、设备、模块和/或系统中

(以及在本文中实现的方法中)的实现方式可以引起性能改进。性能改进可以包含计算性能提高、等待时间缩短、处理量增大和/或功耗降低中的一个或多个。在制造此类装置、设备、模块和系统(例如在集成电路中)期间,可以在性能改进与物理实施方案之间进行权衡,从而改进制造方法。例如,可以在性能改进与布局面积之间进行权衡,从而匹配已知实现方式的性能,但使用更少的硅。例如,这可以通过以串行方式重复使用功能块或在装置、设备、模块和/或系统的元件之间共享功能块来完成。相反,在本技术中阐述的引起装置、设备、模块和系统的物理实现方式的改进(诸如硅面积减小)的概念可以针对性能提高进行权衡。例如,这可以通过在预定义面积预算内制造模块的多个实例来完成。

[0163]

申请人据此独立地公开了本文中所描述的每个单独的特征以及两个或更多个此类特征的任意组合,到达的程度使得此类特征或组合能够根据本领域的技术人员的普通常识基于本说明书整体来实行,而不管此类特征或特征的组合是否解决本文中所公开的任何问题。鉴于前文描述,本领域的技术人员将清楚,可以在本发明的范围内进行各种修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。