1.本发明是有关于一种图像处理方法,且特别是有关于一种可提高处理效率的图像处理装置与图像处理方法。

背景技术:

2.随着显示技术的进步,画质更佳、色彩更丰富、效果更好的图像播放装置不断地推陈出新。具体而言,各式图像播放装置的尺寸越来越大,图像品质的要求也越来越高。例如,具备超高画质(uhd)解析度(例如4k、8k解析度)的显示器已经逐渐开始普遍。对应的,当播放图像的尺寸或解析度提高时,用以产生图像的图像处理晶片必须提高处理效能,才可即时支援每秒30帧(30fps)、60帧(60fps)或其他更高帧率。然而,图像处理晶片的处理效能此往往受限于制程技术,且处理功耗也伴随着处理效能增加而提高。因此,如何在有限的硬件条件下,提高图像处理晶片所支援的输出画面品质,是本领域技术人员相当关心的议题。

技术实现要素:

3.有鉴于此,本发明提出一种图像处理装置与图像处理方法,其可提高图像处理效能并具有良好显示品质。

4.本发明实施例提供一种图像处理装置,其包括图像分割器以及多核处理电路。图像分割器将一原始图帧分割为多个分割区块。多核处理电路耦述图像分割器,并包括多个处理器核心以及图像拼接电路。多个处理器核心对上述多个分割区块进行图像处理而产生多个经处理图像区块。图像拼接电路耦接上述处理器核心,依据上述多个经处理图像区块进行拼接处理而产生一经处理图帧。处理器核心取分割区块以及自分割区块向外扩展的多个扩展像素点进行图像处理,且扩展像素点的列数依据图像处理的窗口算法所要求的窗口尺寸而决定。

5.本发明实施例提供一种图像处理方法,其包括下列步骤。将一原始图帧分割为多个分割区块。藉由多个处理器核心分别取所述分割区块以及自分割区块向外扩展的多个扩展像素点进行图像处理而产生多个经处理图像区块。扩展像素点的列数依据图像处理的窗口算法所要求的窗口尺寸而决定。依据经处理图像区块进行拼接处理而产生经处理图帧。

6.基于上述,于本发明的实施例中,原始图帧会被分割为多个分割区块。藉由多个处理核心分别对多个分割区块并行进行图像处理,可在硬件制程条件受限的情况下明显提升图像处理效率。此外,在对分割区块进行图像处理之前,可依据图像处理的一或多个窗口算法所规范的窗口尺寸弹性配置扩展像素点的数量,使这些处理核心可依据精确的像素信息而分别对分割区块完成图像处理。藉此,本发明实施例的图像处理方法与图像处理装置可更弹性支援不同的窗口算法,且有利各式窗口算法的升级。

7.为让本发明之上述特征和优点能更明显易懂,下文特举实施例,并配合所附图式作详细说明如下。

附图说明

8.图1是依照本发明一实施例所绘示的图像处理装置的示意图。

9.图2a至图2c是依照本发明一实施例所绘示的取扩展像素点的示意图。

10.图3是依照本发明一实施例所绘示的图像处理装置的示意图。

11.图4是依照本发明一实施例所绘示的图像处理方法的示意图。

12.图5是依照本发明一实施例所绘示的图像处理方法的流程图。

13.附图标记说明

14.10:图像处理装置

15.110:图像分割器

16.120:存储器

17.130:多核心电路

18.140:图像合成电路

19.150:显示输出单元

20.131_1~131_m:处理器核心

21.132:图像拼接电路

22.133_1~133_m:数据读取电路

23.subi_1~subi_n:分割区块

24.ep_l1、ep_r1、ep_l2、ep_r2、ep_z1:扩展像素点

25.pi_1~pi_n:经处理图像区块

26.ff:输出图帧

27.f1、f2:经处理图帧

28.i1:原始图帧

29.mi_1~mi_4:待拼接图像区块

30.p1:有效像素点

31.p2:无效像素点

32.s501~s503:步骤

具体实施方式

33.本发明的部分实施例接下来将会配合附图来详细描述,以下的描述所引用的元件符号,当不同附图出现相同的元件符号将视为相同或相似的元件。这些实施例只是本发明的一部分,并未揭示所有本发明的可实施方式。更确切的说,这些实施例只是本发明的权利要求中的装置与方法的范例。

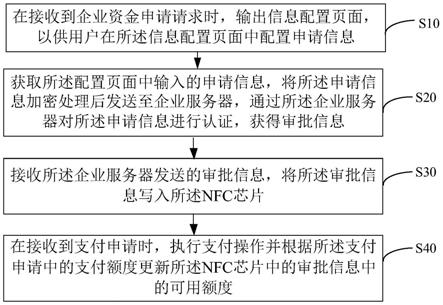

34.图1是依照本发明一实施例所绘示的图像处理装置的示意图。请参照图1,图像处理装置10可包括图像分割器110、存储器120,以及多核处理电路130。

35.图像分割器110将原始图帧分割为多个分割区块,并将这些分割区块记录至存储器120。存储器120用以缓存图像数据,可以是静态随机存取存储器(static random-access memory,sram)或同步动态随机存取存储器(synchronous dynamic random access memory,sdram),但不以此为限制。于一实施例中,原始图帧可以为解码一视频或是一网络流视频而产生的图帧。一般而言,这些视频解码后的原始图帧在播放前还需要进行一些图

像处理,以提升显示品质。需说明的是,于一实施例中,图像分割器110可将原始图帧分割为多个垂直条状区块。然而,本发明对于分割区块的数量与分割方式并不限制,其可视实际需求而配置。此外,每个分割区块的尺寸可以相同或不同。此外,于一实施例中,原始图帧可为包括多个显示画面的多宫格画面、并排画面或子母画面等等。亦即,原始图帧的各个分割区块可能包括一或多个显示画面的像素区块。举例而言,假设原始图帧为包括4个子画面的四宫格画面且原始图帧平均分割为4个垂直条状区块,则每一个垂直条状区块将包括分别对应至2个子画面的2个画面区块。

36.多核处理电路130耦接存储器120,并包括m个处理器核心131_1~131_m(m为大于1的整数)以及图像拼接电路132。部分或全部的处理器核心131_1~131_m可依据直接存储器存取(direct memory access,dma)技术分别自存储器120读取对应的分割区块subi_1~subi_n(n为大于1且小于等于m的整数)。需说明的是,图1系以n=m为范例进行绘示,但本发明不限制于此。

37.举例而言,假设m=n=4。处理器核心131_1可自存储器120取得分割区块subi_1;处理器核心131_2可自存储器120取得分割区块subi_2;处理器核心131_3可自存储器120取得分割区块subi_3;处理器核心131_4可自存储器120取得分割区块subi_4。换言之,每一个处理器核心131_1~131_4将各自取得一个对应的分割区块subi_1~subi_4以进行后续图像处理,而每一个分割区块subi_1~subi_4将各自被一个对应的处理核心131_1~131_4负责处理。

38.于一实施例中,处理器核心131_1~131_m对多个分割区块subi_1~subi_n进行图像处理而产生多个经处理图像区块pi_1~pi_n,像是处理器核心131_1~131_m将分别对分割区块subi_1~subi_n进行去除杂讯、调整色差、增加锐利度、调整尺寸等图像处理程序。换言之,图像处理可包括图像缩放处理、图像去噪处理、高动态范围调整处理、图像对比度调整处理、图像色调度调整处理、图像锐利度调整处理、色彩空间转换或其组合。值得一提的是,处理器核心131_1~131_m会取分割区块subi_1~subi_n以及自分割区块subi_1~subi_n向外扩展的多个扩展像素点进行图像处理。于此,扩展像素点的列数(column number)是依据图像处理的窗口算法所要求的窗口尺寸而决定。

39.详细而言,基于图像处理所应用的窗口算法原理,处理器核心131_1~131_m需要取原始图帧中的多个邻近像素点来进行计算而产生输出像素点。例如,高品质缩放演算法就需要取输入像素点的左右两侧一个以上的邻近像素点进行运算。此外,不同的窗口算法可能需要不同数量的邻近像素点,亦即不同窗口算法所要求的窗口尺寸可能不同。于一些窗口算法中,可透过拷贝图像边缘的第一列边缘像素点来产生施行窗口算法所需的邻近像素点。于是,于一实施例中,由于处理器核心131_1~131_m各自负责不同的分割区块subi_1~subi_n的图像处理,因此除了分割区块subi_1~subi_n中的像素点之外,各个处理器核心131_1~131_m还需要从存储器120取自分割区块subi_1~subi_n向外扩展的多个扩展像素点进行图像处理。

40.于一实施例中,处理器核心131_1~131_m执行的图像处理可包括应用第一窗口算法的第一图像处理以及应用第二窗口算法的第二图像处理。第一窗口算法的窗口尺寸为第一值,第二窗口算法的窗口尺寸为第二值。扩展像素点的需求量是基于图像处理的窗口尺寸而决定。因此,扩展像素点的列数可依据第一值与/或第二值来决定。于一实施例中,处理

器核心131_1~131_m依序执行第一图像处理与第二图像处理。在此情况下,扩展像素点的列数依据第一窗口算法的第一值与第二窗口算法的第二值的总和来决定。像是,假设第一窗口算法的执行需要x列的扩展像素点且第二窗口算法的执行需要y的扩展像素点,则处理器核心131_1~131_m总计将取(x y)列的扩展像素点。举例而言,处理器131_1~131_m执行依序执行多种图像处理的过程中,处理器核心131_1~131_m可取16(或16的倍数)列的扩展像素点。此外,于另一实施例中,扩展像素点的列数依据第一窗口算法的第一值与第二窗口算法的第二值中的最大值来决定。由此可见,本发明实施例可依据一或多个图像处理的窗口尺寸来弹性配置扩展像素点的列数,使其应用范围更为弹性与广泛。

41.举例而言,图2a至图2c是依照本发明一实施例所绘示的取扩展像素点的示意图。为了方便说明,假设原始图帧包括16列像素且被分割为左右两个分割区块,但本发明并不限制于此。本领域具有通常知识者应当可以在参照图2a至图2c及上述例举的内容后,轻易地推演/类推出原始图帧为其他不同尺寸的实施方式。

42.请先参照图2a,处理器核心131_1与处理器核心131_2分别负责对分割区块subi_1与分割区块subi_2进行图像处理。处理器核心131_1可自存储器120取得分割区块subi_1以及自分割区块subi_1向外扩展的多个扩展像素点ep_l1、ep_r1。于此,假设扩展像素点ep_l1、ep_r1的列数经配置为4,则处理器核心131_1至少需要分别取分割区块subi_1左边4列的多个扩展像素点ep_l1以及右边4列的多个扩展像素点ep_r1。由于分割区块subi_1包括原始图帧中第1~8列的像素点,因此自分割区块subi_1向外扩展的多个扩展像素点ep_r1可包括原始图帧中第9~12列的像素点,而自分割区块subi_1向外扩展的多个扩展像素点ep_l1可包括原始图帧中第1列的像素点。需说明的是,由于分割区块subi_1位于原始图帧的边缘,因此处理器核心131_1可重复取原始图帧中第1列的像素点来作为位于分割区块subi_1左边的4列扩展像素点ep_l1。

43.相似的,处理器核心131_2可自存储器120取得分割区块subi_2以及自分割区块subi_2向外扩展的多个扩展像素点ep_l2、ep_r2。于此假设扩展像素点的列数经配置为4,则处理器核心131_2至少需要分别取分割区块subi_2左边4列与右边4列的多个扩展像素点ep_l2、ep_r2。由于分割区块subi_2包括原始图帧中第9~16列的像素点,因此自分割区块subi_2向外扩展的多个扩展像素点ep_l2、ep_r2可包括原始图帧中第5~8列的像素点以及原始图帧中第16列(即最后一列)的像素点。由于分割区块subi_2位于原始图帧的边缘,因此处理器核心131_1可重复取原始图帧中第16列的像素点来作为位于分割区块subi_2右边的4列扩展像素点ep_r2。

44.基此,处理器核心131_1可依据分割区块subi_1以及自分割区块subi_1向外扩展的多个扩展像素点ep_l1、ep_r1进行图像处理,且处理器核心131_2可依据分割区块subi_2以及自分割区块subi_2向外扩展的多个扩展像素点ep_l2、ep_r2进行图像处理,以正确计算出输出像素点。

45.需说明的是,于图2a的范例中,处理器核心131_1~131_2是读取相同数量的像素点来进行图像处理,亦即分割区块subi_1、subi_2的尺寸相同。然而,本发明并不限制于此,于其他实施例中,处理器核心131_1~131_2可读取相异数量的像素点来进行图像处理,亦即分割区块subi_1、subi_2的尺寸可不相同。

46.请参照图2b,处理器核心131_1与处理器核心131_2分别负责对分割区块subi_1与

分割区块subi_2进行图像处理。于图2b的范例中,分割区块subi_1包括12列像素,而分割区块subi_2包括4列像素。在此情况下,由于分割区块subi_1包括原始图帧中第1~12列的像素点,因此自分割区块subi_1向外扩展的多个扩展像素点ep_l1、ep_r1可包括原始图帧中第13~16列的像素点以及原始图帧中第1列的像素点。处理器核心131_1需要依据20列像素进行图像处理。另外,由于分割区块subi_2包括原始图帧中第13~16列的像素点,因此自分割区块subi_2向外扩展的多个扩展像素点ep_l2、ep_r2可包括原始图帧中第9~12列的像素点以及原始图帧中第16列的像素点。此外,在处理器核心131_2被设计为处理16列像素的条件中,可设计处理器核心131_2拷贝原始图帧中第9列的像素点来产生其余的扩展像素点ep_z1。

47.同理,请参照图2c,分割区块subi_1包括4列像素,而分割区块subi_2包括12列像素。在此情况下,由于分割区块subi_1包括原始图帧中第1~4列的像素点,因此自分割区块subi_2向外扩展的多个扩展像素点ep_l1、ep_r1可包括原始图帧中第5~8列的像素点以及原始图帧中第1列的像素点。此外,在处理器核心131_1被设计为处理16列像素的条件中,可设计处理器核心131_1拷贝原始图帧中第8列的像素点来产生其余的扩展像素点ep_z1。另外,由于分割区块subi_2包括原始图帧中第5~16列的像素点,因此自分割区块subi_2向外扩展的多个扩展像素点ep_l2、ep_r2可包括原始图帧中第1~4列的像素点以及原始图帧中第16列的像素点。

48.图像拼接电路132耦接处理器核心131_1~131_m,可接收处理器核心131_1~131_m进行图像处理后产生的pi_1~pi_n,并依据多个经处理图像区块pi_1~pi_n进行拼接处理而产生经处理图帧f1。具体而言,在分别对分割区块subi_1~subi_n进行图像处理之后,由于处理器核心131_1~131_m有使用扩展像素点进行图像处理,因此图像拼接电路132需要从经处理图像区块pi_1~pi_n取出适合的像素点并舍弃不需要的像素点,以拼接为完整的经处理图帧f1。也就是说,图像拼接电路132需要从经处理图像区块pi_1~pi_n分别取出部分像素点来进行拼接处理。关于图像拼接的具体实施细节将于后方实施例详细描述。

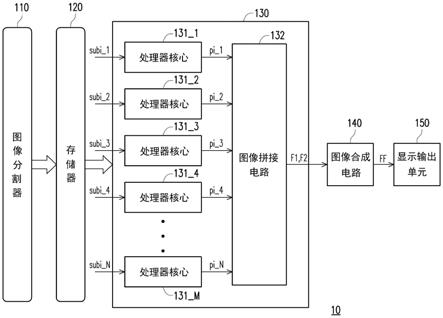

49.图3是依照本发明一实施例所绘示的图像处理装置的示意图。请参照图3,于一实施例中,除了图像分割器110、存储器120,以及多核处理电路130,图像处理装置10可更包括图像合成电路140以及显示输出单元150。

50.图像合成电路140耦接多核处理电路130,合成属于第一图层的经处理图帧f1以及属于第二图层的另一经处理图帧f2,以产生输出图帧ff。另一经处理图帧f2也是由多核处理电路130依据相似的原理产生。换言之,图像合成电路140可迭合经处理图帧f1与另一经处理图帧f2来产生输出图帧ff,以实现多层图像的画面。接着,显示输出单元150输出输出图帧ff。

51.于一实施例中,多核处理电路130可更包括多个数据读取电路133_1~133_m。数据读取电路133_1~133_m一对一耦接至处理器核心131_1~131_m,用以自存储器120读取像素数据。数据读取电路133_1~133_m可以为dma电路。换言之,数据读取电路133_1~133_m经配置以依据扩展像素点的列数自存储器120读取扩展像素点以及分割区块subi_1~subi_n。

52.基于前述可知,数据读取电路133_1~133_m所读取的扩展像素点可包括多个拷贝像素点与/或多个非拷贝像素点。详细而言,于一实施例中,图像分割器110产生的多个分割

区块subi_1~subi_n包括第一分割区块以及第二分割区块。第一分割区块位于原始图帧的垂直边界,则第一分割区块的扩展像素点会包括多个拷贝像素点以及多个非拷贝像素点。数据读取电路133_1~133_m其中之一读取第一分割区块的第一列像素点作为拷贝像素点,数据读取电路133_1~133_m其中之一读取与所述第一分割区块相邻的第二分割区块的多列像素点作为非拷贝像素点。举图2a为例,分割区块subi_1(即第一分割区块)位于原始图帧的垂直边界,则分割区块subi_1的扩展像素点ep_l1包括多个拷贝像素点,且分割区块subi_1的扩展像素点ep_r1包括多个非拷贝像素点。数据读取电路133_1读取分割区块subi_1的第一列像素点作为拷贝像素点,数据读取电路133_1读取分割区块subi_2(即第二分割区块)的多列像素点作为非拷贝像素点。

53.此外,于一实施例中,多核处理电路130依据原始图帧的图像尺寸与图像处理装置10的图像输出格式决定处理器核心131_1~131_m的启用数量。于此,处理器核心131_1~131_m的启用数量会等于分割区块subi_1~subi_n的数量n。举例而言,假设图像处理装置10的图像输出格式为每秒60帧且图像解析度8k(8k@p60),且假设处理器核心131_1~131_m分别支援为每秒60帧且图像解析度4k(4k@p60)的处理效能,则多核处理电路130至少需要启用4个处理器核心131_1~131_4。在硬件受限的情况下,图像处理装置10可选择打开或关闭处理器核心131_1~131_m,以提升处理效能并节约功耗。像是,于一实施例中,图像处理装置10可选择启用至少2个处理器核心131_1~131_2,即可产生符合图像输出格式的输出结果并节约功耗。

54.表1为一实施例中决定处理器核心131_1~131_m的启用数量的范例。然而,表1仅为一示范性说明,并非用以限定本发明。于表1范例中,考量到为处理器核心131_1~131_m开设的数据行缓冲器(line buffer)的尺寸支援解析度2k的数据量,多核处理电路130可基于表1来决定处理器核心131_1~131_m的启用数量。

[0055][0056]

表1

[0057]

需特别说明的是,于一实施例中,处理器核心131_1~131_m执行的图像处理包括图像缩放处理,且处理器核心131_1~131_m依据多相位插值法(polyphase interpolation)进行图像缩放处理,例如4阶(4-tap)或8阶(8-tap)的三次卷积插值法(cubic convolution interpolation)。于多相位插值法的运算中,各输出像素点的相位信息会先被计算出来。处理器核心131_1~131_m需要依据输出像素点的相位信息来获取对应的权重信息,以依据取得的权重信息与输入像素点计算出输出像素点的像素值。于一实施例中,处理器核心131_1~131_m可实现为分别包括多相位插值滤波器,而滤波器系数是依

据输出像素点的相位信息而决定。举例而言,处理器核心131_1~131_m可依据输出像素点的相位信息查表而获取对应的滤波器系数,从而计算出输出像素点的像素值。以4阶(4-tap)的多相位插值滤波器为例,处理器核心131_1~131_m需要取4个输入像素点以及关联于相位信息的4个权重值来进行加权运算,从而产生输出像素点。

[0058]

由此可知,于一实施例中,处理器核心131_1~131_m将根据原始图帧的尺寸与经处理图帧f1的尺寸计算出经处理图像区块pi_1~pi_n中的多个像素点的相位信息。处理器核心131_1~131_m进行图像缩放处理后产生的经处理图像区块pi_1~pi_n中的多个像素点(即图像缩放处理的输出像素点)将分别具有关联于多相位插值法的相位信息。处理器核心131_1~131_m依据经处理图像区块pi_1~pi_n中的像素点的相位信息计算经处理图像区块pi_1~pi_n中的像素点pi_1~pi_n的像素值。需注意的是,图像拼接电路132依据经处理图像区块pi_1~pi_n中的像素点的相位信息从经处理图像区块pi_1~pi_n取出多个待拼接图像区块,并拼接待拼接图像区块而产生经处理图帧f1。

[0059]

于一实施例中,经处理图像区块pi_1~pi_n可包括第一经处理图像区块以及第二经处理图像区块。图像拼接电路132从第一经处理图像区块取出待拼接图像区块中的第一待拼接图像区块,并从第二经处理图像区块取出待拼接图像区块中的第二待拼接图像区块。需注意的是,第一待拼接图像区块中的外侧有效像素点的相位信息相同于第二经处理图像区块中相邻于第二待拼接图像区块的无效像素点的相位信息。举例而言,于水平放大2倍的范例中,像素点之间的位置步进值将从1改为0.5,因此放大后像素的自左至右的相位信息将转换为1、1.5、2、2.5

…

.。对应的,每一个处理器核心131_1~131_m所产生的经处理图像区块中的像素点也都具有对应的相位信息。因此,图像拼接电路132可依据第一待拼接图像区块中的外侧有效像素点的相位信息自第二经处理图像区块取出第二待拼接图像区块进行拼接。基此,待拼接图像区组成的经处理图帧f1中的像素点的相位信息是连续的。

[0060]

于一实施例中,图像拼接电路132可依据图像缩放处理的缩放倍率以及扩展像素点的列数而从第一经处理图像区块取出第一待拼接图像区块。接着,图像拼接电路132可再依据第一待拼接图像区块中的外侧有效像素点的相位信息自第二经处理图像区块取出第二待拼接图像区块。藉此,由于图像拼接电路132是在考量到经处理图像区块pi_1~pi_n中的像素点的相位信息来取出适合像素点进行拼接,因此拼接处理后产生的经处理图帧f1不会有异常的拼接瑕疵。

[0061]

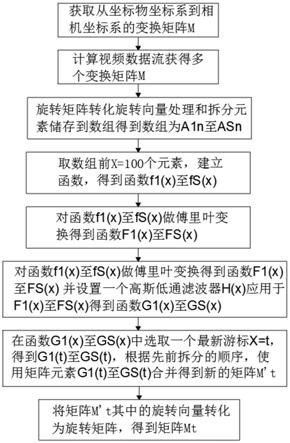

详细而言,图4是依照本发明一实施例所绘示的图像处理方法的示意图。于此,假设分割区块的数量为4,各分割区块取扩展像素点的列数为4,且原始图帧的尺寸(或称为解析度)为p*q。请参照图4,尺寸p*q的原始图帧i1被图像分割器130分割为4个分割区块subi_1~subi_4。每一个分割区块subi_1~subi_4的尺寸为p/4*q。接着,4个处理器核心131_1~131_4可分别取分割区块subi_1~subi_4与左右各4列的扩展像素点进行图像缩放处理与其他图像处理,以产生经处理图像区块pi_1~pi_4。假设垂直缩放倍率与水平缩放倍率皆假设为1.5倍,则经处理图像区块pi_1~pi_4的尺寸为a*b。其中,a等于(p/4 8)乘上1.5,而b等于q乘上1.5。最后,图像拼接电路132自经处理图像区块pi_1~pi_4分别取出四个待拼接图像区块mi_1~mi_4,以拼接出图像输出尺寸为s*b经处理图帧f1。待拼接图像区块mi_1~mi_4的尺寸为s/4*b,亦即,图像拼接电路132自经处理图像区块pi_1~pi_4的a列像素取出s/4列像素作为待拼接图像区块mi_1~mi_4。于此,待拼接图像区块mi_1中的外侧有效像

素点p1的相位信息相同于经处理图像区块pi_2中相邻于待拼接图像区块mi_2的无效像素点p2的相位信息。

[0062]

更具体而言,于此范例中,由于扩展像素点的列数为4且缩放倍率为1.5,图像拼接电路132可得知经处理图像区块pi_1中包括6列的拷贝像素信息。因此,图像拼接电路132可自经处理图像区块pi_1的第七列像素取出尺寸为s/4*b的待拼接图像区块mi_1。接着,图像拼接电路132可依据待拼接图像区块mi_1里最后一列的有效像素点p1的相位信息从经处理图像区块pi_2搜寻出相位信息相同的无效像素点p2,并从经处理图像区块pi_2中无效像素点p2旁边一列取出尺寸为s/4*b的待拼接图像区块mi_2。

[0063]

值得注意的是,在不同的实施例中,上述图像分割器110、多核心处理电路130、图像合成电路140、及/或显示输出单元150的相关功能可以利用一般的编程语言(programming languages,例如c或c )、硬件描述语言(hardware description languages,例如verilog hdl或vhdl)或其他合适的编程语言来实现为软件、固件或硬件。可执行所述相关功能的软件(或固件)可以被布置为任何已知的计算机可存取媒体(computer-accessible medias),例如磁带(magnetic tapes)、半导体(semiconductors)存储器、磁盘(magnetic disks)或光盘(compact disks,例如cd-rom或dvd-rom)。所述软件(或固件)可以被存放在计算机的可存取媒体(例如存储器)中,以便于由计算机的处理器来存取/执行所述软件(或固件)的编程码(programming codes),以执行所述相关功能。

[0064]

图5是依照本发明一实施例所绘示的图像处理方法的流程图。此外,本实施例的图像处理方法的相关实施细节以及相关装置特征可由上述关于图1至图4的各实施例的叙述当中,获得足够的教示、建议以及实施方式,在此不再加以赘述。

[0065]

于步骤s501,将一原始图帧分割为多个分割区块。于步骤s502,藉由多个处理器核心分别取分割区块以及自分割区块向外扩展的多个扩展像素点进行图像处理而产生多个经处理图像区块。扩展像素点的列数依据图像处理的窗口算法所要求的窗口尺寸而决定。于步骤s503,依据经处理图像区块进行拼接处理而产生经处理图帧。

[0066]

综上所述,于本发明的实施例中,在制程条件受限的情况下,可透过多个处理器核心并行对多个分割区块进行图像处理来提升处理效能。藉此,可因应显示器的高显示规格来开启多个处理器核心,以提供良好的显示效能。此外,透过依据图像处理算法的窗口算法所要求的窗口尺寸来决定弹性配置像素点的列数,不仅可正确计算出分割边界的像素信息,更有利于这些窗口算法的升级,且可应用范围更为广泛。此外,透过相位对齐的图像拼接方式,可产生显示效果良好且没有瑕疵的输出图像,以达到无缝拼接的显示效果。

[0067]

虽然本发明已以实施例揭露如上,然其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,当可作些许的更动与润饰,故本发明的保护范围当视后附的权利要求所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。