1.本发明涉及驱动电路内置型功率模块,特别地涉及内置有马达驱动用逆变器等电力变换用半导体开关元件和驱动该开关元件的驱动电路的驱动电路内置型功率模块。

背景技术:

2.对于马达驱动用逆变器使用智能功率模块(intelligent power module)。在该智能功率模块中存在下述结构:具备有多组将两个开关元件串联连接而得的半桥电路、以及驱动开关元件导通、截止的驱动电路。

3.图7是表示用于三相马达驱动用逆变器的智能功率模块的整体的构成例的电路图,图8是表示智能功率模块的一相的构成例的电路图,图9是规定了开关时间的时序图,图10是表示高侧关断时间的电流依赖特性的图。

4.图7所示的智能功率模块100是向三相马达200供给交流电的电力变换装置。因此,该智能功率模块100具有用于u相、v相以及w相的三个半桥电路。u相的半桥电路由开关元件101、102所构成,v相的半桥电路由开关元件103、104所构成,w相的半桥电路由开关元件105、106所构成。此处,使用电压控制型的igbt(insulated gate bipolar transistor:绝缘栅双极型晶体管)和反向并联地连接于该igbt的集电极与发射极端子的续流二极管作为开关元件101

‑

106。应予说明,作为开关元件101

‑

106,有时使用相同的电压控制型的功率mosfet(metal

‑

oxide

‑

semiconductor field

‑

effect transistor:金属氧化物半导体场效应晶体管)。

5.构成u相、v相以及w相的半桥电路的高侧的开关元件101、103、105的集电极端子介由智能功率模块100的p端子与直流电源的正极端子vdc( )连接。开关元件101、103、105的发射极端子介由智能功率模块100的u端子、v端子以及w端子与三相马达200的u相端子、v相端子以及w相端子连接。另外,开关元件101、103、105的发射极端子分别与高侧驱动电路111、112、113的vs端子连接。开关元件101、103、105的栅极端子分别与高侧驱动电路111、112、113的out端子连接。

6.构成u相、v相以及w相的半桥电路的低侧的开关元件102、104、106的集电极端子分别与高侧的开关元件101、103、105的发射极端子连接。开关元件102、104、106的发射极端子分别与智能功率模块100的nu端子、nv端子以及nw端子连接。nu端子、nv端子以及nw端子与电流检测用的分流电阻121的一个端子连接,分流电阻121的另一个端子与直流电源的负极端子vdc(

‑

)连接。开关元件102、104、106的栅极端子分别与低侧驱动电路114的uout端子、vout端子以及wout端子连接。

7.高侧驱动电路111、112、113具有与智能功率模块100的in(hu)端子、in(hv)端子以及in(hw)端子连接的in端子。低侧驱动电路114具有与智能功率模块100的in(lu)端子、in(lv)端子、in(lw)端子以及is端子连接的uin端子、vin端子、win端子以及is端子。

8.高侧驱动电路111、112、113以及低侧驱动电路114分别具有与智能功率模块100的com端子连接的gnd端子。智能功率模块100的com端子与分流电阻121的另一个端子连接。智

能功率模块100的is端子介由电阻122、以及包含电容器123和保护二极管124的滤波器而与分流电阻121的一个端子连接。

9.智能功率模块100的in(hu)端子、in(hv)端子、in(hw)端子、in(lu)端子、in(lv)端子以及in(lw)端子与未图示的上位控制装置连接,并从上位控制装置接收控制信号。如果高侧驱动电路111、112、113在in(hu)端子、in(hv)端子以及in(hw)端子接收到控制信号,则驱动开关元件101、103、105导通、截止。如果低侧驱动电路114在in(lu)端子、in(lv)端子以及in(lw)端子接收到控制信号,则驱动开关元件102、104、106导通、截止。在低侧的开关元件102、104、106中流通的电流通过分流电阻121变换为电压信号,低侧驱动电路114接收该电压信号并进行过电流保护以及短路保护。

10.由于智能功率模块100的u相、v相以及w相的电路分别具有相同电路构成以及功能,所以在图8中代表性地示出与u相相关的电路构成。智能功率模块100的与u相相关的电路具备高侧驱动电路111以及开关元件101、低侧驱动电路114以及开关元件102。

11.高侧驱动电路111具有电平移位电路131、延迟电路132、驱动电路133以及输出电路134,输出电路134具有串联连接的p沟道mosfet 135以及n沟道mosfet 136。电平移位电路131在in端子接收将gnd端子的电位作为基准的高侧用的输入信号而电平移位为将vs端子的电位作为基准的信号。电平移位而得的信号通过延迟电路132延迟预定时间并输入到驱动电路133。驱动电路133基于延迟了的信号驱动输出电路134的mosfet 135、136导通、截止。输出电路134产生将高侧的控制电源电压vb作为开关元件101的栅极驱动电压的信号并从out端子输出。

12.低侧驱动电路114具有延迟电路141、驱动电路142以及输出电路143,输出电路143具有串联连接的p沟道mosfet 144以及n沟道mosfet 145。延迟电路141在uin端子接收低侧用的输入信号而延迟预定时间,并输入到驱动电路142。驱动电路142基于延迟了的信号驱动输出电路143的mosfet144、145导通、截止。输出电路143产生将低侧的控制电源电压vcc作为开关元件102的栅极驱动电压的信号并从uout端子输出。

13.此处,关于根据在智能功率模块100的in(hu)端子以及in(lu)端子所接收的输入信号进行接通或关断的开关元件101、102的动作,参照图9进行说明。应予说明,在图9中从上至下表示in(hu)端子的电压vin(hu)、开关元件101的栅极与发射极间电压vge(hu)、集电极电流ic(hu)以及集电极与发射极间电压vce(hu)。进一步地,在图9中表示in(lu)端子的电压vin(lu)、开关元件102的栅极与发射极间电压vge(lu)、集电极电流ic(lu)以及集电极与发射极间电压vce(lu)。另外,在该图9中表示下述的状态:高侧的开关元件101从接通状态转换为关断状态,且低侧的开关元件102从关断状态转换为接通状态。

14.对in(hu)端子以及in(lu)端子输入有输入信号时的开关时间是输入信号的延迟时间与开关元件101、102的栅极充放电时间之和。输入信号的延迟时间是输入信号被输入之后驱动开关元件101、102的栅极所花费的时间,并且由高侧驱动电路111以及低侧驱动电路114的内部的延迟电路132、141的时间常数所决定。栅极充放电时间是直接驱动开关元件101、102的栅极的时间,并且栅极充放电时间由输出电路134、143的mosfet 135、136、144、145的工作电阻值等决定。

15.根据图9,高侧的关断时间toff是从指示开关元件101的关断的输入信号被输入起直到开关元件101的集电极电流ic(hu)变为零为止的时间。延迟时间是从指示开关元件101

的关断起直到输出电路134的p沟道mosfet135截止且n沟道mosfet 136导通为止。栅极放电时间是从n沟道mosfet136导通而开关元件101的栅极电容开始放电起直到集电极电流ic(hu)实际上变为零为止。

16.在指示高侧的开关元件101的关断之后,经过预先所确定的死区时间tdead(in)的时间后,指示低侧的开关元件102的接通的输入信号被输入。

17.低侧的接通时间ton是从指示开关元件102的接通的输入信号被输入起直到开关元件102的栅极电容的充电结束为止的时间。延迟时间是从指示开关元件102的接通起直到输出电路143的p沟道mosfet 144导通且n沟道mosfet 145截止为止。栅极充电时间是从p沟道mosfet 144导通且开关元件102的栅极电容开始充电起直到栅极电容的充电结束且密勒电容开始充电为止。

18.应予说明,图9示出高侧的开关元件101关断而低侧的开关元件102接通的情况。但是,低侧的开关元件102关断而高侧的开关元件101接通的情况也一样。在该情况下,高侧的vin(hu)、vge(hu)、ic(hu)以及vce(hu)的符号与低侧的vin(lu)、vge(lu)、ic(lu)以及vce(lu)的符号成为交换改写的符号。

19.死区时间tdead(in)是为了防止开关元件101、102同时成为接通状态从而u相的半桥电路短路这一情况而设定。该死区时间tdead(in)考虑开关元件101、102的关断时间toff以及接通时间ton的偏差等,设计为满足规格所需的最小死区时间。

20.为了确保死区时间裕度,高侧的关断时间toff的偏差最大值与低侧的接通时间ton的偏差最小值之差需要满足规格所需的最小死区时间。

21.为了满足最小死区时间而调整开关时间,但是一般提出有调整栅极放电时间而调整开关时间的发明(例如,参照专利文献1)。

22.关于专利文献1的发明,在驱动电路使igbt关断时,在经过延迟时间后使栅极电容在最开始高速放电,之后分阶段地使放电速度变化为低速,由此调整栅极放电时间。

23.现有技术文献

24.专利文献

25.专利文献1:日本特开2015

‑

204659号公报

技术实现要素:

26.技术问题

27.对于电压控制型的开关元件,确认了关断时间toff依赖于集电极电流而变化的行为。图10表示作为高侧的开关元件的igbt的关断时间toff存在集电极电流依赖这一情况。根据图10,示出igbt的关断时间toff在集电极电流的低电流域增加的趋势。例如,集电极电流为75安培(a)时的关断时间toff是3.8微秒(μs),但是集电极电流为2a时,关断时间toff成为4.8μs。这是因igbt芯片引起的动作,是耗尽层依赖于漂移层浓度并在低集电极电流域中难以扩展的电压控制型的器件中的特有的现象。

28.如果出现本现象,则由于关断时间变长,所以难以确保期望的死区时间裕度。作为缩短栅极充放电时间的一般性的方法,已知有提升高侧驱动电路的驱动能力的方法。但是,如果提升高侧驱动电路的驱动能力,则由于开关元件截断大电流时的集电极电流的变化率变得急剧,所以由于布线电感而产生的反向电压即关断跳变电压增大,并且有可能超过耐

压而导致绝缘破坏。

29.本发明是鉴于这样的点而完成的,目的在于提供改善了开关元件的关断时间的电流依赖特性的驱动电路内置型功率模块。

30.技术方案

31.关于本发明,为了解决上述的课题,在一个方案中,提供驱动电路内置型功率模块,其具备有以构成半桥电路的方式连接的高侧开关元件以及低侧开关元件、驱动高侧开关元件的高侧驱动电路、以及驱动低侧开关元件的低侧驱动电路。该驱动电路内置型功率模块还具备检测高侧开关元件的电流的高侧电流检测电路,高侧驱动电路具有高侧可变延迟电路,所述高侧可变延迟电路根据高侧电流检测电路的检测值来调整从信号输入于高侧驱动电路起直到高侧开关元件被驱动为止的高侧延迟时间的长度。

32.技术效果

33.上述构成的驱动电路内置型功率模块由于以延迟时间来调整开关元件的开关时间,所以关断时的在低电流域增加的关断时间的增加量由调整了的延迟时间抵消,从而能够确保死区时间裕度。

附图说明

34.图1是表示第一实施方式的智能功率模块的构成例的电路图。

35.图2是表示高侧的关断时间的电流依赖特性的图。

36.图3是表示高侧的主要构成部分的电路图。

37.图4是表示低侧的主要构成部分的电路图。

38.图5是表示第二实施方式的智能功率模块的高侧的主要构成部分的电路图。

39.图6是表示第二实施方式的智能功率模块的低侧的主要构成部分的电路图。

40.图7是表示用于三相马达驱动用逆变器的智能功率模块的整体的构成例的电路图。

41.图8是表示智能功率模块的一相的构成例的电路图。

42.图9是规定了开关时间的时序图。

43.图10是表示高侧关断时间的电流依赖特性的图。

44.符号说明

45.10 智能功率模块

46.20 高侧驱动电路

47.21 电平移位电路

48.22、22a 可变延迟电路

49.22a、22b 电阻

50.22c 电容器

51.22d 开关

52.22e 电阻

53.22f、22g 电容器

54.22h 开关

55.23 驱动电路

56.24 输出电路

57.25、25a 电流检测电路

58.25a、25b 电阻

59.25c 比较器

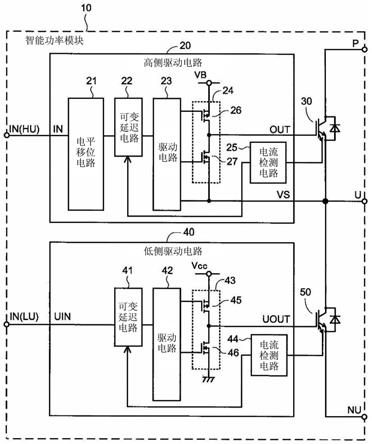

60.25d 基准电压源

61.26、27 mosfet

62.30 开关元件

63.40 低侧驱动电路

64.41、41a 可变延迟电路

65.41a、41b 电阻

66.41c 电容器

67.41d 开关

68.41e 电阻

69.41f、41g 电容器

70.41h 开关

71.42 驱动电路

72.43 输出电路

73.44、44a 电流检测电路

74.44a、44b 电阻

75.44c 比较器

76.44d 基准电压源

77.45、46 mosfet

78.50 开关元件

具体实施方式

79.以下,关于本发明的实施方式,以适用于被三相马达驱动用逆变器所用的智能功率模块的情况为例参照附图进行详述,但是,此处为了避免附图的复杂,仅说明与u相相关的电路构成。图中,由相同的符号所示的部分表示相同的构成要素。另外,各实施方式在不矛盾的范围中能够将多个实施方式部分地组合而实施。

80.图1是表示第一实施方式的智能功率模块的构成例的电路图,图2是表示高侧的关断时间的电流依赖特性的图,图3是表示高侧的主要构成部分的电路图,图4是表示低侧的主要构成部分的电路图。

81.第一实施方式的智能功率模块10具备高侧驱动电路20以及开关元件30、低侧驱动电路40以及开关元件50。开关元件30、50设为相互反向并联地连接的igbt以及续流二极管,并且igbt具有主igbt和用于检测在该主igbt中流通的电流的电流感测元件即感测igbt。

82.高侧驱动电路20具有电平移位电路21、可变延迟电路22、驱动电路23、输出电路24以及电流检测电路25,输出电路24具有串联连接的p沟道mosfet 26以及n沟道mosfet 27。

83.高侧驱动电路20具有in端子,并且该in端子连接于智能功率模块10的接收高侧用的输入信号的in(hu)端子和电平移位电路21的输入端子。电平移位电路21的输出端子与可

变延迟电路22的输入端子连接,可变延迟电路22的输出端子与驱动电路23的输入端子连接。驱动电路23具有与输出电路24连接的第一输出端子以及第二输出端子、和与高侧驱动电路20的vs端子连接的高侧基准电位端子。驱动电路23的第一输出端子与p沟道mosfet 26的栅极端子连接,mosfet 26的源极端子与高侧的控制电源电压vb的导线连接。驱动电路23的第二输出端子与n沟道mosfet 27的栅极端子连接,mosfet 27的源极端子与高侧驱动电路20的vs端子连接。p沟道mosfet 26的漏极端子与n沟道mosfet 27的漏极端子以及高侧驱动电路20的out端子连接。高侧驱动电路20的out端子与开关元件30的栅极端子连接,开关元件30的集电极端子与智能功率模块10的p端子连接,该p端子连接外部的直流电源的正极端子。开关元件30的发射极端子与高侧驱动电路20的vs端子、低侧的开关元件50的集电极端子、以及智能功率模块10的u端子连接。开关元件30内置的感测igbt的感测发射极端子与电流检测电路25的输入端子连接,电流检测电路25的输出端子与可变延迟电路22的控制输入端子连接。应予说明,电流检测电路25可以内置于高侧驱动电路20,也可以设置于高侧驱动电路20的外部。

84.低侧驱动电路40具有可变延迟电路41、驱动电路42、输出电路43以及电流检测电路44,输出电路43具有串联连接的p沟道mosfet 45以及n沟道mosfet 46。

85.低侧驱动电路40具有uin端子,并且该uin端子连接于智能功率模块10的接收低侧用的输入信号的in(lu)端子和可变延迟电路41的输入端子。可变延迟电路41的输出端子与驱动电路42的输入端子连接。驱动电路42具有与输出电路43连接的第一输出端子以及第二输出端子。驱动电路42的第一输出端子与p沟道mosfet 45的栅极端子连接,mosfet 45的源极端子与低侧的控制电源电压vcc的导线连接。驱动电路42的第二输出端子与n沟道mosfet 46的栅极端子连接,mosfet 46的源极端子与低侧驱动电路40的接地端连接。p沟道mosfet 45的漏极端子与n沟道mosfet46的漏极端子以及低侧驱动电路40的uout端子连接,低侧驱动电路40的uout端子与开关元件50的栅极端子连接。开关元件50的集电极端子与智能功率模块10的u端子连接,开关元件50的发射极端子与智能功率模块10的nu端子连接,该nu端子连接外部的直流电源的负极端子。开关元件50的感测发射极端子与电流检测电路44的输入端子连接,电流检测电路44的输出端子与可变延迟电路41的控制输入端子连接。应予说明,电流检测电路44可以内置于低侧驱动电路40,也可以设置于低侧驱动电路40的外部。

86.在该智能功率模块10中,如果高侧驱动电路20在in端子接收到使开关元件30接通的输入信号,则电平移位电路21将该输入信号的基准电位从接地端电位电平移位为vs端子的电位。电平移位而得的信号输入到可变延迟电路22。可变延迟电路22具有延迟时间不同的两个延迟电路,并且具有下述功能:与电流检测电路25检测出的开关元件30的集电极电流的电流值相应地将延迟时间切换为已有的延迟电路设定的延迟时间和比已有的延迟电路设定的延迟时间短的延迟时间。电流检测电路25接收来自开关元件30的感测发射极端子的电流检测信号,并且判断集电极电流是否大于预先所设定的电流值。作为预先所设定的电流值,例如设为集电极电流的绝对最大额定的1/10。

87.通过可变延迟电路22延迟后的信号输入到驱动电路23。驱动电路23通过使输出电路24的p沟道mosfet 26导通并且使n沟道mosfet 27截止,从而使开关元件30接通。由此,开关元件30的集电极电流增加。如果集电极电流超过预先所设定的电流值,则电流检测电路25将可变延迟电路22切换为延迟时间短的延迟电路。

88.此处,如果高侧驱动电路20接收到使开关元件30关断的输入信号,则该输入信号通过电平移位电路21进行电平移位,并在可变延迟电路22中通过延迟时间短的延迟电路而延迟。由于预先使开关元件30被关断时的由可变延迟电路22产生的延迟时间短于使开关元件30接通时的延迟时间,所以成为高侧的关断时间的一部分的延迟时间抵消在集电极电流的低电流域中增加的时间。由此,如图2所示,由于高侧的关断时间的在低电流域中的电流依赖得到抑制,所以能够确保期望的死区时间裕度。

89.另外,智能功率模块10的低侧驱动电路40也具有在开关元件50关断时切换可变延迟电路41的延迟时间的构成。该低侧驱动电路40也与高侧驱动电路20同样地,电流检测电路44接收来自开关元件50的感测发射极端子的电流检测信号而检测集电极电流,并且根据该电流值切换可变延迟电路41的延迟时间。由此,由于在低侧也能够缩短开关元件50的关断时间的延迟时间,所以能够确保期望的死区时间裕度。

90.接着,关于高侧驱动电路20的可变延迟电路22以及电流检测电路25、和低侧驱动电路40的可变延迟电路41以及电流检测电路44的具体的构成例进行说明。

91.关于高侧,如图3所示,高侧驱动电路20的可变延迟电路22具备两个电阻22a、22b、电容器22c和开关22d。可变延迟电路22的输入端子与电阻22a的一个端子连接,电阻22a的另一个端子与电阻22b的一个端子连接,电阻22b的另一个端子与电容器22c的一个端子和该可变延迟电路22的输出端子连接。电容器22c的另一个端子与作为高侧驱动电路20的基准电位的vs端子的导线连接。可变延迟电路22的输入端子还与开关22d的一个端子连接,开关22d的另一个端子与电阻22a、22b的共同连接部连接,开关22d的控制输入端子与电流检测电路25的输出端子连接。

92.电流检测电路25具备两个电阻25a、25b、比较器25c和基准电压源25d。电流检测电路25的连接着开关元件30的感测发射极端子的输入端子与电阻25a的一个端子连接,电阻25a的另一个端子与电阻25b的一个端子连接,电阻25b的另一个端子与vs端子的导线连接。电阻25a、25b的共同连接部与比较器25c的非反相输入端子连接,比较器25c的反相输入端子与基准电压源25d的正极端子连接,基准电压源25d的负极端子与vs端子的导线连接。比较器25c的输出端子构成电流检测电路25的输出端子,并且与可变延迟电路22的开关22d的控制输入端子连接。应予说明,基准电压源25d输出与该电流检测电路25要检测出的预先所设定的集电极电流的电流值相当的电压。

93.可变延迟电路22通过电阻22a、22b以及电容器22c构成rc电路,并且依开关22d是否将电阻22a短路而具有两个时间常数。即,开关22d断开(非导通)时的时间常数由电阻22a以及电阻22b的电阻值之和与电容器的电容值的积表示,该值是与已有的延迟电路相同的值,延迟时间也与已有的延迟电路的延迟时间相同。开关22d闭合(导通)时的时间常数由电阻22b的电阻值与电容器的电容值之积表示,该值小于已有的延迟电路的时间常数,并且延迟时间也短于已有的延迟电路的延迟时间。

94.电流检测电路25从开关元件30的感测发射极端子接收与开关元件30的集电极电流成比例的电流检测信号。如果电流检测信号供给于串联连接的电阻25a、25b,则电流检测信号通过电阻25b转换为电压信号,转换后的电压信号施加于比较器25c的非反相输入端子。

95.比较器25c将与电流检测信号相当的电压信号和基准电压源25d的电压进行比较,

并且在开关元件30关断等而集电极电流小时,比较器25c输出低电平的输出信号。由此,在可变延迟电路22中,开关22d被断开,可变延迟电路22的时间常数大并设定长的延迟时间。

96.如果开关元件30接通而集电极电流变大,并且该集电极电流超过与基准电压源25d的电压相当的电流,则比较器25c输出高电平的输出信号。由此,在可变延迟电路22中,开关22d被闭合,可变延迟电路22的时间常数变小,并且设定短的延迟时间。由此,开关元件30接下来关断而集电极电流降低,成为低电流域时的延迟时间的增加量被由可变延迟电路22所设定的延迟时间的缩短量抵消。由于包含栅极放电时间在内的总的高侧的关断时间没有变长,所以能够确保期望的死区时间裕度。

97.关于低侧,如图4所示,低侧驱动电路40的可变延迟电路41具备有两个电阻41a、41b、电容器41c和开关41d,具有与高侧驱动电路20的可变延迟电路22相同的构成。但是,电容器41c的另一个端子与接地端连接。

98.电流检测电路44也具有与高侧驱动电路20的电流检测电路25同样的构成,具备两个电阻44a、44b、比较器44c和基准电压源44d。但是,电阻44b的另一个端子以及基准电压源44d的负极端子与接地端连接。

99.电流检测电路44从开关元件50的感测发射极端子接收与开关元件50的集电极电流成比例的电流检测信号。如果电流检测信号供给于串联连接的电阻44a、44b,则电流检测信号通过电阻44b转换为电压信号,转换后的电压信号施加于比较器44c的非反相输入端子。

100.比较器44c将与电流检测信号相当的电压信号和基准电压源44d的电压进行比较,并且在开关元件50关断等而集电极电流小时,比较器44c输出低电平的输出信号。由此,在可变延迟电路41中,开关41d被断开,可变延迟电路41的时间常数大并设定长的延迟时间。

101.如果开关元件50接通而集电极电流变大,并且该集电极电流超过与基准电压源44d的电压相当的电流,则比较器44c输出高电平的输出信号。由此,在可变延迟电路41中,开关41d被闭合,可变延迟电路41的时间常数变小并且设定短的延迟时间。由此,在开关元件50接下来关断时,由于可变延迟电路41的延迟时间设定得短,所以包含栅极放电时间在内的总的低侧的关断时间没有变长。因此,低侧的关断时间不会超过最小死区时间裕度。

102.图5是表示第二实施方式的智能功率模块的高侧的主要构成部分的电路图,图6是表示第二实施方式的智能功率模块的低侧的主要构成部分的电路图。

103.关于第二实施方式,如图5所示,高侧驱动电路20具备可变延迟电路22a以及电流检测电路25a。可变延迟电路22a具备电阻22e、两个电容器22f、22g、和开关22h。可变延迟电路22a的输入端子与电阻22e的一个端子连接,电阻22e的另一个端子与电容器22f的一个端子、开关22h的一个端子以及该可变延迟电路22a的输出端子连接。开关22h的另一个端子与电容器22g的一个端子连接。电容器22f、22g的另一个端子与作为高侧驱动电路20的基准电位的vs端子的导线连接。开关22h的控制输入端子与电流检测电路25a的输出端子连接。

104.电流检测电路25a与第一实施方式的电流检测电路25同样,具备两个电阻25a、25b、比较器25c和基准电压源25d,具有与第一实施方式的电流检测电路25相同的电路构成。但是,将比较器25c的反相输入端子以及非反相输入端子与第一实施方式的电流检测电路25的比较器25c的反相输入端子以及非反相输入端子相反地进行连接。

105.根据该可变延迟电路22a以及电流检测电路25a,在开关元件30关断等而集电极电

流小时,电流检测电路25a输出高电平的输出信号。由此,在可变延迟电路22a中,开关22h被断开而rc电路的电容值变大,由此可变延迟电路22a的时间常数大并设定长的延迟时间。

106.如果开关元件30接通而集电极电流变大,并且该集电极电流超过与基准电压源25d的电压相当的电流,则比较器25c输出低电平的输出信号。由此,在可变延迟电路22a中,开关22h被断开,可变延迟电路22a的时间常数变小并且设定短的延迟时间。由此,在开关元件30接下来关断时,由于可变延迟电路22a的延迟时间设定得短,所以能够使包含栅极放电时间在内的总的高侧的关断时间变短。

107.如图6所示,第二实施方式的低侧驱动电路40具备可变延迟电路41a以及电流检测电路44a。可变延迟电路41a具备电阻41e、两个电容器41f、41g、和开关41h。可变延迟电路41a具有与高侧的可变延迟电路22a相同的构成。

108.电流检测电路44a具备两个电阻44a、44b、比较器44c和基准电压源44d,具有与高侧的电流检测电路25a相同的电路构成。

109.根据该可变延迟电路41a以及电流检测电路44a,在开关元件50关断等而集电极电流小时,电流检测电路44a输出高电平的输出信号。由此,在可变延迟电路41a中,开关41h被闭合而rc电路的电容值变大,由此可变延迟电路41a的时间常数大并设定长的延迟时间。

110.如果开关元件50接通而集电极电流变大,并且该集电极电流超过与基准电压源44d的电压相当的电流,则比较器44c输出低电平的输出信号。由此,在可变延迟电路41a中,开关41h被断开,可变延迟电路41a的时间常数小并且设定短的延迟时间。由此,在开关元件50接下来关断时,由于可变延迟电路41a的延迟时间设定得短,所以能够使包含栅极放电时间在内的总的低侧的关断时间变短。

111.应予说明,关于上述的实施方式,是对于具有关断时间在低电流域变长的电流依赖的开关元件的实施方式。但是,在使用了具有关断时间在大电流域中变长的电流依赖的开关元件的智能功率模块中,上述的实施方式也能够同样地适用。在该情况下,仅使电流检测电路的比较器的输入端子的连接反转即可。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。