1.本发明涉及时间测量技术领域,尤其涉及用于测量时间的方法和装置以及用于量子通信设备的可编程控制器。

背景技术:

2.在相关技术中,主要采用tdc(time to digital convert,时间数字转换器)模块或基于fpga的tdc模块来测量光子的到达时间,tdc模块通常通过在其内部设置的多个延时链来实现上述测量。然而,由于延时链会随着温度的变化而导致测量的时间结果发生偏移,因此,tdc模块需要随着温度的变化实时地对测量的结果进行修正,这样不仅会占用大量的计算资源(诸如,fpga资源、dsp资源等),而且很难满足系统(诸如,但不限于,量子通信系统)的高速运行要求。

技术实现要素:

3.本发明的目的在于提供用于测量时间的方法和装置以及用于量子通信设备的可编程控制器。

4.根据本发明的一方面,提供一种用于测量时间的方法,所述方法包括:接收start信号和stop信号;使用同一时钟对所述信号进行采样,以产生与所述start信号对应的start比特串以及与所述stop信号对应的stop比特串,在所述比特串中以第一比特指示所述信号中的高电平,以第二比特指示所述信号中的低电平;从所述start比特串中提取所述start信号的上升沿,从所述stop比特串中提取所述stop信号的上升沿,其中,所述start信号的上升沿对应于所述start比特串中的由第二比特跳变至第一比特的比特位,所述stop信号的上升沿对应于所述stop比特串中的由第二比特跳变至第一比特的比特位;基于所述start信号的上升沿与所述stop信号的上升沿之间的比特位的计数以及所述时钟的周期来确定所述start信号与所述stop信号之间的时间间隔。

5.根据本发明的一个实施例,从所述start比特串中提取所述start信号的上升沿,从所述stop比特串中提取所述stop信号的上升沿的步骤包括:将所述start比特串和所述stop比特串从串行数据转换成并行数据;将所述并行数据中的连续相邻的多个第一比特处理成独热码,所述独热码对应于所述比特串中的由第二比特跳变至第一比特的比特位;根据所述独热码从所述start比特串中提取所述start信号的上升沿并且从所述stop比特串中提取所述stop信号的上升沿。

6.根据本发明的一个实施例,基于所述start信号的上升沿与所述stop信号的上升沿之间的比特位的计数以及所述时钟的周期来确定所述start信号与所述stop信号之间的时间间隔的步骤包括:根据在所述start信号的上升沿所在的并行数据与所述stop信号的上升沿所在的并行数据之间包括的并行数据中的比特位的计数以及所述时钟的周期来计算所述start信号与所述stop信号之间的粗测时间间隔;根据所述start信号的上升沿所在的比特位以及所述时钟的周期来计算针对所述start信号的上升沿的第一细测时间间隔;

根据所述stop信号的上升沿所在的比特位以及所述时钟的周期来计算针对所述stop信号的上升沿的第二细测时间间隔;将所述粗测时间间隔、所述第一细测时间间隔和所述第二细测时间间隔汇总求和,以得到所述start信号与所述stop信号之间的时间间隔。

7.根据本发明的一个实施例,所述并行数据的位宽为8位、16位、32位和64位中的一者。

8.根据本发明的一个实施例,所述第一比特为1,所述第二比特为0。

9.根据本发明的另一方面,提供一种用于测量时间的装置,所述装置包括:信号输入单元,被配置为接收start信号和stop信号;比特串产生单元,被配置为使用同一时钟对所述信号进行采样,以产生与所述start信号对应的start比特串以及与所述stop信号对应的stop比特串,在所述比特串中以第一比特指示所述信号中的高电平,以第二比特指示所述信号中的低电平;上升沿提取单元,被配置为从所述start比特串中提取所述start信号的上升沿,从所述stop比特串中提取所述stop信号的上升沿,其中,所述start信号的上升沿对应于所述start比特串中的由第二比特跳变至第一比特的比特位,所述stop信号的上升沿对应于所述stop比特串中的由第二比特跳变至第一比特的比特位;时间测量单元,被配置为基于所述start信号的上升沿与所述stop信号的上升沿之间的比特位的计数以及所述时钟的周期来确定所述start信号与所述stop信号之间的时间间隔。

10.根据本发明的一个实施例,所述上升沿提取单元包括:串并转换单元,被配置为将所述start比特串和所述stop比特串从串行数据转换成并行数据;独热码处理单元,被配置为将所述并行数据中的连续相邻的多个第一比特处理成独热码,所述独热码对应于所述比特串中的由第二比特跳变至第一比特的比特位;独热码提取单元,被配置为根据所述独热码从所述start比特串中提取所述start信号的上升沿并且从所述stop比特串中提取所述stop信号的上升沿。

11.根据本发明的一个实施例,所述时间测量单元包括:时间粗测单元,被配置为根据在所述start信号的上升沿所在的并行数据与所述stop信号的上升沿所在的并行数据之间包括的并行数据中的比特位的计数以及所述时钟的周期来计算所述start信号与所述stop信号之间的粗测时间间隔;第一时间细测单元,被配置为根据所述start信号的上升沿所在的比特位以及所述时钟的周期来计算针对所述start信号的上升沿的第一细测时间间隔;第二时间细测单元,被配置为根据所述stop信号的上升沿所在的比特位以及所述时钟的周期来计算针对所述stop信号的上升沿的第二细测时间间隔;汇总求和单元,被配置为将所述粗测时间间隔、所述第一细测时间间隔和所述第二细测时间间隔汇总求和,以得到所述start信号与所述stop信号之间的时间间隔。

12.根据本发明的一个实施例,所述并行数据的位宽为8位、16位、32位和64位中的一者。

13.根据本发明的一个实施例,所述第一比特为1,所述第二比特为0。

14.根据本发明的另一方面,提供一种用于量子通信设备的可编程控制器,所述可编程控制器被配置为执行如前面所述的用于测量时间的方法。

15.本发明所提供的用于测量时间的方法和装置以及用于量子通信设备的可编程控制器无需设置延时链以及复杂的运算即可实现对诸如,但不限于,光子到达信号的时间测量,这样不仅能够省去了针对外部tdc模块所使用的硬件电路和芯片,提升设备的集成化和

小型化,而且还能够满足系统(诸如,但不限于,量子通信系统)的高速运行要求。

附图说明

16.通过下面结合附图进行的描述,本发明的上述目的和特点将会变得更加清楚。

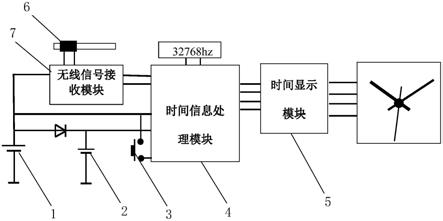

17.图1示出了根据本发明的示例性实施例的用于测量时间的方法的流程图。

18.图2示出了根据本发明的示例性实施例的用于从比特串中提取start信号的上升沿和stop信号的上升沿的示意图。

19.图3示出了根据本发明的示例性实施例的用于测量时间的装置的结构框图。

20.图4示出了根据本发明的示例性实施例的在量子通信设备中经由可编程控制器测量光子到达时间的示意图。

21.图5示出了根据本发明的示例性实施例的在量子通信设备中经由可编程控制器产生的比特串的示意图。

具体实施方式

22.下面,将参照附图来详细说明本发明的实施例。

23.图1示出了根据本发明的示例性实施例的用于测量时间的方法的流程图。

24.参照图1,根据本发明的示例性实施例的用于测量时间的方法可包括以下步骤。

25.在步骤110,可接收start信号和stop信号。

26.例如,在量子通信设备(诸如,量子密钥分发系统中的接收端)中,可将由同步光触发的电脉冲信号作为start信号接收,将由信号光触发的电脉冲信号作为stop信号接收。然而,本发明并不限于此。根据需要,也可将其他光信号触发的电脉冲信号或其他的电脉冲信号作为start信号接收,将其他光信号触发的电脉冲信号或其他的电脉冲信号作为stop信号接收。

27.在步骤120,可使用同一时钟对上述信号进行采样,以产生与start信号对应的start比特串以及与stop信号对应的stop比特串,在比特串中以第一比特指示上述信号中的高电平,以第二比特指示上述信号中的低电平。

28.例如,可以以比特“1”指示上述信号中的高电平,以比特“0”指示上述信号中的低电平。然而,本发明并不限于此,例如,根据需要,也可以以比特“0”指示上述信号中的高电平,以比特“1”指示上述信号中的低电平。

29.在步骤130,可从start比特串中提取start信号的上升沿,从stop比特串中提取stop信号的上升沿,该start信号的上升沿对应于start比特串中的由第二比特跳变至第一比特的比特位,该stop信号的上升沿对应于stop比特串中的由第二比特跳变至第一比特的比特位。

30.在示例中,可将start比特串和stop比特串从串行数据转换成并行数据;将并行数据中的连续相邻的多个第一比特处理成独热码,该独热码对应于比特串中的由第二比特跳变至第一比特的比特位;根据独热码从start比特串中提取start信号的上升沿并且从stop比特串中提取stop信号的上升沿。

31.图2示出了根据本发明的示例性实施例的用于从比特串中提取start信号的上升沿和stop信号的上升沿的示意图。

32.参照图2,第一行示出的信号为start信号1010,第二行示出的信号为stop信号1020,第三行示出的信号为时钟1030,第四行和第五行示出的比特串分别为通过时钟1030的上升沿对start信号1010进行采样(即,与操作)而产生的与start信号1010对应的串行数据1040以及通过时钟1030的上升沿对stop信号1020进行采样而产生的与stop信号1020对应的串行数据1050,第六行和第七行示出的比特串分别为按照8 位位宽对串行数据1040进行串并转换而产生的并行数据1060以及按照8位位宽对串行数据1050进行串并转换而产生的并行数据1070,第八行和第九行示出的比特串分别为通过将并行数据1060中的连续相邻的多个比特“1”处理成独热码bit1而产生的并行数据1080以及通过将并行数据1070中的连续相邻的多个比特“1”处理成独热码bit2而产生的并行数据1090(即,保持并行数据中的由比特“0”跳变至比特“1”的比特位bit1和bit2上的比特值不变而将并行数据中的其他比特位上的比特值“1”置为“0”),基于上述串并转换和独热码处理,可从并行数据1080中提取独热码bit1作为start信号的上升沿,从并行数据1090中提取独热码bit2作为stop信号的上升沿。

33.应当理解,尽管图2示出了按照8 位位宽将比特串从串行数据转换成并行数据的示例,但是该示例仅仅示意性的,本发明并不限于此。根据需要,也可按照16位、32位或64位等位宽将比特串从串行数据转换成并行数据。

34.在步骤140,可基于start信号的上升沿与stop信号的上升沿之间的比特位的计数以及时钟的周期来确定start信号与stop信号之间的时间间隔。

35.在示例中,可根据在start信号的上升沿所在的并行数据与stop信号的上升沿所在的并行数据之间包括的并行数据中的比特位的计数以及时钟的周期来计算start信号与stop信号之间的粗测时间间隔;根据start信号的上升沿所在的比特位以及时钟的周期来计算针对start信号的上升沿的第一细测时间间隔;根据stop信号的上升沿所在的比特位以及时钟的周期来计算针对stop信号的上升沿的第二细测时间间隔;将粗测时间间隔、第一细测时间间隔和第二细测时间间隔汇总求和,以得到start信号与stop信号之间的时间间隔。

36.再次参照图2,t0为start信号与stop信号之间的粗测时间间隔t0,t1为针对start信号的上升沿的第一细测时间间隔,t2为针对stop信号的上升沿的第二细测时间间隔。

37.在图2示出的示例中,在start信号的上升沿所在的并行数据与stop信号的上升沿所在的并行数据之间包括2个并行数据,由于一个并行数据中存在8个比特位,因此在start信号的上升沿所在的并行数据与stop信号的上升沿所在的并行数据之间包括的比特位的计数为16,根据该计数可将start信号与stop信号之间的粗测时间间隔t0计算为16

×

τ,该τ为时钟周期。

38.另外,在图2示出的示例中,start信号的上升沿所在的比特位bit1位于其所在并行数据中的第二个比特位,换言之,在start信号的上升沿与其所在并行数据的末端之间包括的比特位的计数为7,根据该计数可将针对start信号的上升沿的第一细测时间间隔t1计算为7

×

τ,该τ为时钟周期。

39.另外,在图2示出的示例中, stop信号的上升沿所在的比特位bit2位于其所在并行数据中的第三个比特位,换言之,在stop信号的上升沿与其所在并行数据的首端之间包括的比特位的计数为3,根据该计数可将针对stop信号的上升沿的第二细测时间间隔t2计

算为3

×

τ,该τ为时钟周期。

40.因此,在图2示出的示例中,start信号与stop信号之间的时间间隔可计算为16

×

τ+7

×

τ+3

×

τ。

41.应当理解,尽管图2还示出了用于测量start信号与stop信号之间的时间间隔的示例,但是该示例仅仅是示意性的,本发明并不限于此。例如,也可通过直接地统计start信号的上升沿与stop信号的上升沿之间的比特位的计数来计算start信号与stop信号之间的时间间隔。

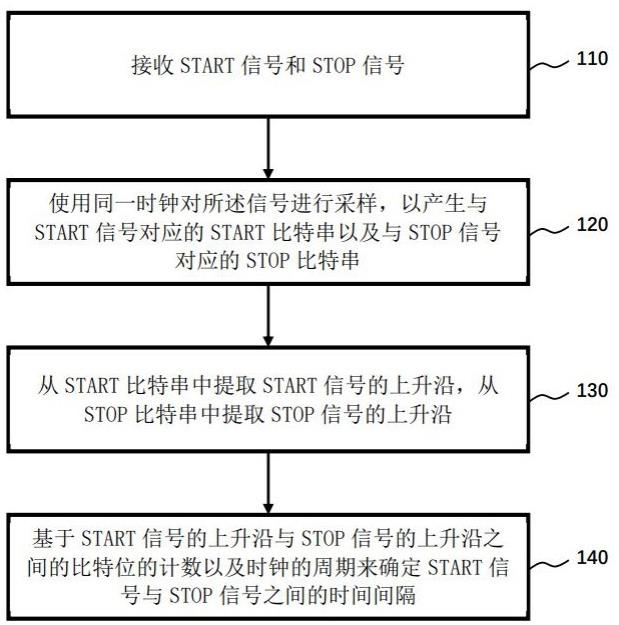

42.图3示出了根据本发明的示例性实施例的用于测量时间的装置的结构框图。

43.参照图3,根据本发明的示例性的用于测量时间的装置至少可包括信号接收单元310、比特串产生单元320、上升沿提取单元330和时间测量单元340,其中,信号接收单元310可被配置为接收start信号和stop信号;比特串产生单元320可被配置为使用同一时钟对上述信号进行采样,以产生与start信号对应的start比特串以及与stop信号对应的stop比特串,在比特串中以第一比特指示上述信号中的高电平,以第二比特指示上述信号中的低电平;上升沿提取单元330可被配置为从start比特串中提取start信号的上升沿,从stop比特串中提取stop信号的上升沿,该start信号的上升沿对应于start比特串中的由第二比特跳变至第一比特的比特位,该stop信号的上升沿对应于stop比特串中的由第二比特跳变至第一比特的比特位;时间测量单元340可被配置为基于start信号的上升沿与stop信号的上升沿之间的比特位的计数以及时钟的周期来确定start信号与stop信号之间的时间间隔。

44.在图3所示的装置中,上升沿提取单元330可进一步包括串并转换单元、独热码处理单元和独热码提取单元(未示出),其中,串并转换单元可被配置为将start比特串和stop比特串从串行数据转换成并行数据;独热码处理单元可被配置为将并行数据中的连续相邻的多个第一比特处理成独热码,独热码可对应于比特串中的由第二比特跳变至第一比特的比特位;独热码提取单元可被配置为根据独热码从start比特串中提取start信号的上升沿并且从stop比特串中提取stop信号的上升沿。另外,在示例中,并行数据的位宽可以是8位,也可以是16位、32位或64位。根据需要,可选择合适的位宽来进行上述串并转换和独热码处理。

45.在图3所示的装置中,时间测量单元340可进一步包括时间粗测单元、第一时间细测单元、第二时间细测单元和汇总求和单元(未示出),其中,时间粗测单元可被配置为根据在start信号的上升沿所在的并行数据与stop信号的上升沿所在的并行数据之间包括的并行数据中的比特位的计数以及时钟的周期来计算start信号与stop信号之间的粗测时间间隔;第一时间细测单元可被配置为根据start信号的上升沿所在的比特位以及时钟的周期来计算针对start信号的上升沿的第一细测时间间隔;第二时间细测单元可被配置为根据stop信号的上升沿所在的比特位以及时钟的周期来计算针对stop信号的上升沿的第二细测时间间隔;汇总求和单元可被配置为将粗测时间间隔、第一细测时间间隔和第二细测时间间隔汇总求和,以得到start信号与stop信号之间的时间间隔。

46.下面,将参照图4和图5进一步地详细地描述上述用于测量时间的方法和装置在量子通信设备中的应用。

47.图4示出了根据本发明的示例性实施例的在量子通信设备(诸如,量子通信系统中的接收端或bob端)中经由可编程控制器测量光子到达时间的示意图。图5示出了根据本发

明的示例性实施例的在量子通信设备中经由可编程控制器产生的比特串的示意图。

48.在图4和图5示出的量子通信设备中,单光子探测器d0可将同步光到达时所产生的电脉冲信号作为start信号传送给可编程控制器fpga,单光子探测器d1可将信号光到达时所产生的电脉冲信号作为stop信号传送给可编程控制器fpga,此外,单光子探测器d2还可将信号光到达时所产生的电脉冲信号作为stop信号传送给可编程控制器fpga。可编程控制器fpga可被配置为经由设置在其内部的收发器接收start信号和stop信号,然后通过收发器中的串并转换模块sipo(未示出)使用同一时钟clock对上述信号进行采样,以产生与start信号对应的比特串start以及与stop信号对应的比特串stop0和stop1,在比特串中以比特“1”指示上述信号中的高电平,以比特“0”指示上述信号中的低电平,并且将产生的上述比特串从串行数据转换成并行数据。进一步地,可编程控制器fpga还可被配置为将并行数据中的连续相邻的多个比特“1”处理成独热码,以从上述比特串中分别提取出start信号的上升沿以及各路stop信号的上升沿,然后按照如前所述的方法基于start信号的上升沿与各路stop信号的上升沿之间的比特位的计数以及时钟clock的周期来确定start信号与各路stop信号之间的时间间隔。

49.应当理解,尽管图4和图5示出了在量子通信设备中对光子到达时间进行测量的示例,但是本发明并不限于于此,也可使用上述用于测量时间的方法和装置在其他设备或系统中进行信号之间的时间测量。

50.可以看出,根据本发明的示例性实施例的用于测量时间的方法和装置无需设置延时链以及复杂的运算即可实现对诸如但不限于光子到达信号的时间测量,这样不仅能够省去了针对外部tdc模块所使用的硬件电路和芯片,提升设备的集成化和小型化,而且还能够满足系统(诸如,但不限于,量子通信系统)的高速运行要求。

51.尽管已参照优选实施例表示和描述了本技术,但本领域技术人员应该理解,在不脱离由权利要求限定的本技术的精神和范围的情况下,可以对这些实施例进行各种修改和变换。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。