1.本发明涉及摄像机领域,特别是涉及一种单光源全彩摄像机。

背景技术:

2.在摄像机领域,由于全天候监控的需求,会根据光照环境,对摄像机进行功能性的设定,比如宽动态、强光抑制、星光级超低照度等。在白天光照充足的时候,摄像机的isp系统可以将sensor输入的原始图像恢复成清晰度高,色彩鲜艳的srgb图像。但是,在夜晚微光条件下,sensor输入的原始图像,由于光强微弱,导致原始图像的信噪比急剧降低,图像有效信息大多被淹没在各种噪声中,如果只依赖于简单的isp处理,其恢复出来的srgb图像不仅图像模糊不清,而且色彩单调。

3.为此,业界推出了一种全彩黑光相机的方案,例如杭州萤石软件有限公司发明的《黑光全彩实现方法和黑光全彩摄像机》,该发明采用两颗星光级图像传感器,其中一颗星光级图像传感器通过红外补光采集图像亮度信息和物体轮廓,另外一颗星光级图像传感器采集色彩信息。然后通过图像融合算法将两颗星光级图像传感器采集到的图像信息进行融合,输出明亮全彩的图像。在夜晚微光环境下,黑光摄像机也必须依赖于红外补光灯进行补光。在一些无法补光的微光场景中,黑光相机受制于成像原理,无法有效的工作,输出图像的质量也差强人意。

技术实现要素:

4.本发明的目的是提供一种单光源全彩摄像机,以解决现有的摄像机在夜晚微光环境下,输出的图像质量低的问题。

5.为实现上述目的,本发明提供了如下方案:

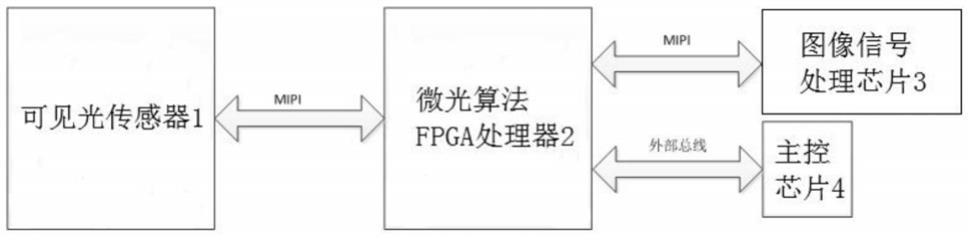

6.一种单光源全彩摄像机,包括:可见光传感器、微光算法fpga处理器、图像信号处理芯片以及主控芯片;

7.所述可见光传感器与所述微光算法fpga处理器的一端连接;所述图像信号处理芯片以及所述主控芯片分别与所述微光算法fpga处理器的另一端连接;

8.所述可见光传感器用于采集原始图像,并将所述原始图像输入到所述微光算法fpga处理器;所述微光算法fpga处理器用于将所述原始图像进行去噪处理,并将去噪后的图像输入到所述图像信号处理芯片;所述图像信号处理芯片用于对所述去噪后的图像进行处理得到srgb图像;所述主控芯片用于对所述微光算法fpga处理器进行参数配置,以及用于生成缓存地址。

9.可选的,所述微光算法fpga处理器还用于对所述去噪后的图像进行去马赛克处理,得到srgb图像。

10.可选的,还包括双倍速率同步动态随机存储器;

11.所述双倍速率同步动态随机存储器与所述微光算法fpga处理器连接;所述双倍速率同步动态随机存储器用于存储所述原始图像、所述去噪后的图像以及所述srgb图像。

12.可选的,所述微光算法fpga处理器具体包括:图像接口模块、算法处理模块以及内部总线;

13.所述图像接口模块与所述可见光传感器连接,用于接收所述原始图像,并将所述原始图像传输至所述双倍速率同步动态随机存储器中;

14.所述算法处理模块与所述双倍速率同步动态随机存储器连接,用于对所述原始图像进行噪声估计、去噪处理以及去马赛克处理,并将去噪后的图像以及srgb图像传输至所述双倍速率同步动态随机存储器中。

15.可选的,所述微光算法fpga处理器还包括:内部总线;

16.所述图像接口模块、所述算法处理模块以及所述双倍速率同步动态随机存储器之间通过所述内部总线进行通信。

17.可选的,所述图像接口模块具体包括:mipi

‑

csi接口、mipi

‑

isp接口和hdmi接口;

18.所述mipi

‑

csi接口的一端与所述可见光传感器连接,所述mipi

‑

csi接口的另一端通过所述内部总线与所述双倍速率同步动态随机存储器连接;所述mipi

‑

csi接口用于接收所述原始图像,并将所述原始图像输入到所述双倍速率同步动态随机存储器;

19.所述mipi

‑

isp接口的一端与所述图像信号处理芯片连接;所述mipi

‑

isp接口的另一端通过所述内部总线与所述双倍速率同步动态随机存储器连接;所述mipi

‑

isp接口用于根据所述缓存地址提取所述去噪后的图像,将所述去噪后的图像数据输入到所述图像信号处理芯片;

20.所述hdmi接口的一端通过所述内部总线分别与所述算法处理模块和所述双倍速率同步动态随机存储器连接;所述hdmi接口的另一端与显示设备连接;所述hdmi接口用于输出所述srgb图像。

21.可选的,所述图像信号处理芯片用于对所述去噪后的图像进行处理具体包括:自动曝光控制、自动增益控制、自动白平衡、色彩校正、镜头明暗处理、gamma校正和祛除坏点。

22.可选的,所述算法处理模块具体包括:noisees子模块、denoise子模块和demosic子模块;所述noisees子模块、所述denoise子模块和所述demosic子模块依次连接;

23.所述noisees子模块与所述双倍速率同步动态随机存储器连接;所述noisees子模块用于根据所述缓存地址提取所述原始图像,对所述原始图像进行噪声估计,确定所述原始图像的噪声程度;

24.所述denoise子模块用于根据所述噪声程度对所述原始图像进行去噪处理;

25.所述demosic子模块用于对所述去噪后的图像进行去马赛克处理,输出srgb图像。

26.可选的,所述噪声程度包括:噪声轻微、噪声中等以及噪声严重。

27.根据本发明提供的具体实施例,本发明公开了以下技术效果:

28.本发明通过可见光传感器采集原始图像,微光算法fpga处理器对原始图像进行去噪处理,图像信号处理芯片对去噪后的图像进行图像处理,输出srgb图像。在夜晚光线微弱的环境下,通过可见光传感器就可以完成对图像的亮度信息、物体轮廓以及色彩信息的采集,输出明亮全彩的图像,不需要额外的补光灯进行补光,提高了图片输出的质量。

附图说明

29.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所

需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

30.图1为本发明提供的一种单光源全彩摄像机的结构图;

31.图2为本发明提供的一种单光源全彩摄像机的微光算法fpga处理器内部逻辑框图。

32.符号说明:1

‑

可见光传感器;2

‑

微光算法fpga处理器;3

‑

图像信号处理芯片;4

‑

主控芯片;5

‑

图像接口模块;6

‑

算法处理模块;7

‑

双倍速率同步动态随机存储器;8

‑

内部总线。

具体实施方式

33.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

34.本发明的目的是提供一种单光源全彩摄像机,以解决现有的摄像机在夜晚微光环境下,输出的图像质量低的问题。本发明适用于各种光照条件下(包括白天光照充足与夜晚微光环境),只需要一个可见光传感器,不需要红外传感器,且微光场景下,不需要使能额外的补光灯,摄像机就能够输出清晰的全彩视频图像,更加适用于一些无法补光的场景。

35.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

36.图1为本发明提供的一种单光源全彩摄像机的结构图,如图1所示,一种单光源全彩摄像机,包括:可见光传感器1、微光算法fpga处理器2、图像信号处理芯片3以及主控芯片4。

37.所述可见光传感器1与所述微光算法fpga处理器2的一端连接;所述图像信号处理芯片3以及所述主控芯片4分别与所述微光算法fpga处理器2的另一端连接。

38.所述可见光传感器1用于采集原始图像,并将所述原始图像输入到所述微光算法fpga处理器2;所述微光算法fpga处理器2用于将所述原始图像进行去噪处理,并将去噪后的图像输入到所述图像信号处理芯片3;所述图像信号处理芯片3用于对所述去噪后的图像进行处理得到srgb图像;所述主控芯片4用于对所述微光算法fpga处理器2进行参数配置,以及用于生成缓存地址。

39.在一个具体实施方式中,所述微光算法fpga处理器2还用于对所述去噪后的图像进行去马赛克处理,得到srgb图像。

40.可见光传感器模块将可见光传感器1实时产生的原始图像(raw图像),通过mipi接口输出给微光算法fpga处理器2。微光算法fpga处理器2通过与可见光传感器1的mipi接口,接收raw图像。估计raw图像的噪声水平,并根据不同的噪声水平,在微光算法fpga处理器2内部完成raw图像的去噪处理。去噪处理完成后,可以通过mipi接口输出给所述图像信号处理芯片3(isp芯片),也可以在微光算法fpga处理器2内完成去噪后的raw图像的去马赛克处理,直接通过hdmi接口输出srgb图像。主控芯片4通过pcie接口对微光算法fpga处理器2进行各种参数的配置。isp芯片通过mipi接口接收去噪后的raw图像,并对raw图像进行处理,

具体包括aec(自动曝光控制)、agc(自动增益控制)、awb(自动白平衡)、色彩校正、lens shading(镜头明暗处理)、gamma校正以及祛除坏点,恢复出对应的srgb图像。

41.在一个具体实施方式中,单光源全彩摄像机还包括双倍速率同步动态随机存储器7;所述双倍速率同步动态随机存储器7与所述微光算法fpga处理器2连接;所述双倍速率同步动态随机存储器7用于存储所述原始图像、所述去噪后的图像以及所述srgb图像。

42.图2为本发明提供的微光算法fpga处理器内部逻辑框图,如图2所示,在一个具体实施方式中,所述微光算法fpga处理器2具体包括:图像接口模块5、算法处理模块6以及内部总线8;所述图像接口模块5与所述可见光传感器1连接,用于接收所述原始图像,并将所述原始图像传输至所述双倍速率同步动态随机存储器7中;所述算法处理模块6与所述双倍速率同步动态随机存储器7连接,用于对所述原始图像进行噪声估计、去噪处理以及去马赛克处理,并将去噪后的图像以及srgb图像传输至所述双倍速率同步动态随机存储器7中。

43.在一个具体实施方式中,所述图像接口模块5、所述算法处理模块6以及所述双倍速率同步动态随机存储器7之间通过所述内部总线8进行通信。

44.在一个具体实施方式中,所述图像接口模块5具体包括:mipi

‑

csi接口、mipi

‑

isp接口和hdmi接口,所述图像接口模块5完成可见光传感器1raw图像的输入、去噪后的raw图像的输出和srgb图像的输出。

45.所述mipi

‑

csi接口的一端与所述可见光传感器1连接,所述mipi

‑

csi接口的另一端通过所述内部总线8与所述双倍速率同步动态随机存储器7连接;所述mipi

‑

csi接口用于接收raw图像,并将raw图像输入到所述双倍速率同步动态随机存储器7。

46.fpga通过mipi csi接口与可见光传感器1相连,包括mipi d

‑

phy模块,mipi receive逻辑和原始图像缓存逻辑,其工作流程如下:

47.步骤1:mipi d

‑

phy模块采用1对源同步的差分时钟和4对差分数据线来进行数据传输,完成可见光传感器1输入raw图像的差分信号到串行数字信号的转换。

48.步骤2:mipi receive逻辑完成串行数字信号的帧同步,提取完整的图像帧数据。首先在串行数字信号中搜索到一帧数据的起始位置,然后根据起始位置,完成串行数字信号的对齐处理,并转换成完整的一帧原始图像。

49.步骤3:原始图像缓存逻辑按照主控芯片4分配的缓存地址,将提取出的raw图像通过内部总线8写入到双倍速率同步动态随机存储器7(double data rate,ddr)中进行缓存,并通过中断信号通知算法处理模块6进行后续的处理。

50.所述mipi

‑

isp接口的一端与所述图像信号处理芯片3连接;所述mipi

‑

isp接口的另一端通过所述内部总线8与所述双倍速率同步动态随机存储器7连接;所述mipi

‑

isp接口用于根据所述缓存地址提取所述去噪后的图像,将所述去噪后的图像数据输入到所述图像信号处理芯片3。

51.fpga通过mipi csi接口与isp芯片相连,包括mipi d

‑

phy模块,mipi transmit逻辑和去噪原始图像读取逻辑,其工作流程如下:

52.步骤1:去噪原始图像读取逻辑,算法处理模块6完成一帧raw图像的去噪处理后,通过中断信号通知mipi

‑

isp接口的去噪原始图像读取逻辑。去噪原始图像读取逻辑根据中断信号中携带的帧缓存地址,通过内部总线8将去噪后的原始图像从ddr读取到fpga中。

53.步骤2:mipi transmit逻辑完成去噪后的原始图像的串行化处理。首先在去噪后

的原始图像的首部插入帧同步信息,然后再将去噪后的原始图像串行化。

54.步骤3:mipi d

‑

phy模块采用1对源同步的差分时钟和4对差分数据线来进行数据传输,完成去噪后的原始图像的串行数字信号到差分信号的转换。

55.所述hdmi接口的一端通过所述内部总线8分别与所述算法处理模块6和所述双倍速率同步动态随机存储器7连接;所述hdmi接口的另一端与显示设备连接;所述hdmi接口用于输出所述srgb图像。

56.fpga通过hdmi接口与显示设备相连,包括hdmi tx phy模块,hdmi tx控制逻辑和srgb图像读取逻辑,其工作流程如下:

57.步骤1:srgb图像读取逻辑,算法处理模块6完成一帧raw图像的去马赛克(demosic)处理后,通过中断信号通知hdmi接口的srgb图像读取逻辑。srgb图像读取逻辑根据中断信号中携带的缓存地址,通过内部总线8将srgb图像从ddr读取到fpga中。

58.步骤2:hdmi tx控制逻辑完成srgb图像的串行化处理。首先在srgb图像的首部插入帧同步信息,然后再将srgb图像串行化。

59.步骤3:hdmi tx phy模块采用1对源同步的差分时钟和3对差分数据线来进行数据传输,完成srgb图像的串行数字信号到差分信号的转换,并输出到显示设备中。

60.在一个具体实施方式中,所述图像信号处理芯片3用于对所述去噪后的图像进行处理具体包括:自动曝光控制、自动增益控制、自动白平衡、色彩校正、镜头明暗处理、gamma校正和祛除坏点。

61.在一个具体实施方式中,所述算法处理模块6具体包括:noisees子模块、denoise子模块和demosic子模块;所述noisees子模块、所述denoise子模块和所述demosic子模块依次连接。所述算法处理模块6完成raw图像的噪声估计、raw图像去噪处理和去噪raw图像的去马赛克处理。

62.所述noisees子模块与所述双倍速率同步动态随机存储器7连接;所述noisees子模块用于根据所述缓存地址提取所述原始图像,对所述原始图像进行噪声估计,确定所述原始图像的噪声程度。

63.noisees模块包括原始图像读取逻辑与原始图像噪声估计逻辑,完成原始raw图像的噪声估计,并根据噪声程度把raw图像分为3类,如下所示:

64.noiseweak,噪声程度轻微。

65.noisenormal,噪声程度中等。

66.noisestrong,噪声程度严重。

67.noisees模块的处理流程如下:

68.步骤1:原始图像读取逻辑,图像接口模块5接收到一帧raw图像后,通过中断信号通知noisees模块。原始图像读取逻辑根据中断信号中携带的缓存地址,通过内部总线8将raw图像从ddr读取到fpga中。

69.步骤2:原始图像噪声估计逻辑,本发明采用基于滤波器的方法。首先用中值滤波器对raw图像做平滑处理,然后计算raw图像与平滑后图像的像素差平均值,最后根据像素差平均值来判断图像噪声的严重程度,设置2种噪声阈值,如下:

70.weak噪声阈值,表示噪声程度轻微;

71.若raw图像估计噪声小于weak噪声阈值,则判断raw图像的噪声属于noiseweak。

72.normal噪声阈值,表示噪声程度中等。

73.若raw图像估计噪声大于或者等于weak噪声阈值,并且小于normal噪声阈值,则判断raw图像的噪声属于noisenormal程度。

74.若raw图像估计噪声大于或者等于normal噪声阈值,则判断raw图像的噪声属于noisestrong程度。

75.步骤3:raw图像的噪声估计完成后,由中断信号通知denoise模块进行后续处理。

76.所述denoise子模块用于根据所述噪声程度对所述原始图像进行去噪处理。

77.denoise模块根据raw图像的噪声等级,采用不同等级的去噪模型完成raw图像去噪处理。本发明支持3种等级的不同去噪模型,各个去噪模型首先采用深度学习的方法进行训练,然后将训练完成的模型分别进行int8量化处理,最后得到去噪量化模型。去噪量化模型的前向推导功能由fpga中的denoise模块实现。

78.三种去噪模型如下所示:

79.denoiseweak模型:

80.denoiseweak模型处理noiseweak噪声等级的raw图像。denoiseweak模型每次只输入一帧raw图像,输入图像时,首先进行归一化处理,经过模型处理后,输出一帧去噪后的raw图像。

81.denoisenormal模型:

82.denoisenormal模型处理noisenormal噪声等级的raw图像。denoisenormal模型每次输入二帧raw图像,包括当前帧和时间序列上的前一帧raw图像,输入图像时,首先进行归一化处理,经过模型处理后,输出当前帧所对应的去噪raw图像。

83.denoisestrong模型:

84.denoisestrong模型处理noisestrong噪声等级的raw图像。denoisestrong模型每次输入四帧raw图像,包括当前帧和时间序列上的前三帧raw图像。输入图像时,首先进行归一化处理,经过模型处理后,输出当前帧所对应的去噪raw图像。

85.denoise模块的处理流程如下(以denoiseweak模块为例):

86.步骤1:原始图像读取逻辑,noisees模块完成一帧数据的噪声估计后,通过中断信号通知denoise模块的原始图像读取逻辑。原始图像读取逻辑根据中断信号中携带的缓存地址,通过内部总线8将raw图像从ddr读取到fpga中。

87.步骤2:根据中断信号中携带的噪声类型,选择对应的噪声处理模型。若raw图像的噪声属于noiseweak等级,则将denoiseweak模型的参数由ddr中加载到fpga内部的denoise模块中。

88.步骤3:将当前raw图像做归一化处理后,输入到denoiseweak模型进行去噪处理,等一帧数据处理完成后,根据主控芯片4分配的缓存地址,将去噪后的raw图像通过内部总线8写入ddr中进行缓存。

89.步骤4:同时产生denoise处理的完成中断,通知demosic模块和图像接口模块5进行后续处理。

90.所述demosic子模块用于对所述去噪后的图像进行去马赛克处理,输出srgb图像。

91.demosic模块将去噪后的raw图像转变为srgb图像,并可以通过hdmi接口进行输出展示。demosic模块中的raw2srgb模型采用深度学习的方法进行训练,并将训练完成的模型

进行int8量化处理,得到demosic量化模型,demosic量化模型的前向推导功能由fpga实现。

92.步骤1:去噪原始图像读取逻辑,denoise模块完成一帧数据的去噪声后,通过中断信号通知demosic模块的去噪原始图像读取逻辑。去噪原始图像读取逻辑根据中断信号中携带的缓存地址,通过内部总线8将去噪raw图像从ddr读取到fpga中demosic模块。

93.步骤2:将demosic模型的参数由ddr中加载到fpga内部的demosic模块中。

94.步骤3:将去噪raw图像做归一化处理后,输入到demosic模型进行去马赛克处理,当一帧raw图像处理完成后,根据主控芯片4分配的缓存地址,将得到的srgb图像通过内部总线8写入ddr中进行缓存。

95.步骤4:同时产生demosic处理的完成中断,并通知图像接口模块5。

96.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。

97.本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本发明的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。