1.本发明属于半导体技术领域,具体涉及一种芯片隔离环设计及筛片方法的设计。

背景技术:

2.半导体电路的生产过程通常为:晶圆先经过适当的清洗(cleaning)之后,接着进行氧化(oxidation)及沉积,最后进行微影、蚀刻及离子植入等反复步骤,在完成晶圆上电路的加工与制作过程中,难免对晶圆造成机械损伤,产生裂纹。

3.隐裂纹最初发生在晶圆阶段,由于隐裂纹不明显,或隐藏在中间层,无法轻易通过高倍显微镜全部检测出来。后续在对晶圆进行切割时,会将机械应力施加于所述晶圆上。这样,一方面原就存在的隐裂纹会在机械应力的作用下,裂纹强度加深,面积扩大从而增加了晶圆的不良率。另一方面在靠近隐裂纹区域,容易造成已经切割而成的芯片内部产生裂纹,这些裂纹芯片流入下道工序,不仅增加了后续工序芯片筛选的任务,同时还有可能影响封装的良品率。芯片裂纹是半导体集成电路封装过程中最严重的缺陷之一,也是集成电路封装最致命的失效模式。无论从半导体制造的任何环节,避免芯片裂纹的产生,以及对裂纹芯片的及时检测都是非常重要的。

4.晶圆制造过程完成后,每颗芯片都必须经过测试,这种测试通常被称为cp测试(circuit probing)。隔离环是介于芯片和划片槽之间的保护环。隔离环最根本也是最主要的作用就是防止芯片在切割的时候受到机械损伤。

技术实现要素:

5.本发明的目的是为了解决半导体芯片在完成晶圆上电路的加工与制作过程中容易产生隐裂纹的问题,提出了一种芯片隔离环设计及筛片方法。

6.本发明的技术方案为:一种芯片隔离环设计及筛片方法,包括以下步骤:s1、在芯片版图设计阶段,为每个芯片设计隔离环。

7.s2、在晶圆的cp测试阶段,针对晶圆中的每个芯片,对芯片上的隔离环进行iv测试。

8.s3、根据隔离环的iv测试结果计算得到电压差值。

9.s4、针对晶圆中的每个芯片,判断其电压差值是否在预设范围内,若是则判定该芯片为正常芯片,否则判定该芯片具有隐裂纹缺陷。

10.s5、将判定具有隐裂纹缺陷的芯片在晶圆上做隔离标记,划定晶圆的隔离区域,完成筛片。

11.进一步地,步骤s1中为每个芯片设计隔离环的具体方法为:在芯片上用隔离线设置一个能够将芯片内部电路包裹完全的开口环,在隔离线的一端设置pad,将隔离线的另一端避开该pad,并延长走线后在端点设置pad,将两个端点均设置有pad的开口环作为隔离环。

12.进一步地,步骤s2包括以下分步骤:

s21、在晶圆的cp测试阶段,针对晶圆中的每个芯片,将隔离环上的一个pad作为port1端口,另一个pad作为port2端口。

13.s22、在port2端口连接50ω的接地电阻。

14.s23、在port1端口依次输入电流i1和i2,测量得到port1端口对应的电压v1和v2。

15.进一步地,步骤s2中针对晶圆中的每个芯片,其iv测试条件均相同,即在每个芯片port1端口输入的电流i1均相同,在每个芯片port1端口输入的电流i2均相同,且i1≠i2。

16.进一步地,步骤s3具体为:根据port1端口的电压v1和v2计算得到电压差值

∆

v= v

1 ‑ꢀ

v2。

17.进一步地,步骤s4中电压差值的预设范围为:v

low

≤δv≤v

high

,其中v

low

表示预设的卡控门限最小值,v

high

表示预设的卡控门限最大值。

18.进一步地,卡控门限最小值v

low

和卡控门限最大值v

high

均通过n个芯片的电压差值δv得到,n为晶圆中的芯片总数。

19.本发明的有益效果是:(1)本发明在保留现有隔离环设计初衷的同时,通过隔离环上设置两个pad,进行隔离环的iv测试,通过对iv测试值进行计算和比较,判断芯片是否具有隐裂纹风险,进一步的隔离晶圆上具有隐裂纹风险的芯片,避免其流入下道工序,造成更大的损失。

20.(2)本发明在测试过程中,在port2端口连接50ω的接地电阻,利用输入电流测试电压的方法,可以规避采用高阻(大于500ω)的电压测试波动,以及低阻(小于5ω)的电流噪声造成的波动,从而实现测试精度的良好折中,保证隐裂纹探测的准确性;同时高精度标准50ω的接地电阻具有较强的系统兼容性,成本较低。

附图说明

21.图1所示为本发明实施例提供的一种芯片隔离环设计及筛片方法流程图。

22.图2所示为本发明实施例提供的隔离环设计示意图。

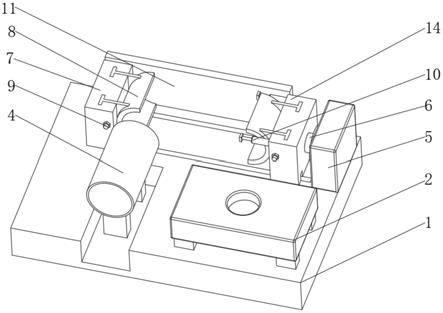

23.图3所示为本发明实施例提供的芯片隔离环端口设置以及测试示意图。

具体实施方式

24.现在将参考附图来详细描述本发明的示例性实施方式。应当理解,附图中示出和描述的实施方式仅仅是示例性的,意在阐释本发明的原理和精神,而并非限制本发明的范围。

25.本发明实施例提供了一种芯片隔离环设计及筛片方法,如图1所示,包括以下步骤s1~s5:s1、在芯片版图设计阶段,为每个芯片设计隔离环。

26.本发明实施例中,如图2所示,在芯片上用隔离线设置一个能够将芯片内部电路包裹完全的开口环,在隔离线的一端设置pad(芯片打线管脚),将隔离线的另一端避开该pad,并延长走线后在端点设置pad,将两个端点均设置有pad的开口环作为隔离环。这样隔离环的两端各有1个pad,同时隔离环仍能将芯片内部电路包裹完全。

27.s2、在晶圆的cp测试阶段,针对晶圆中的每个芯片,对芯片上的隔离环进行iv测试。

28.步骤s2包括以下分步骤s21~s23:s21、在晶圆的cp测试阶段,针对晶圆中的每个芯片,将隔离环上的一个pad作为port1端口,另一个pad作为port2端口。

29.本发明实施例中,如图3所示,将隔离环上位于左侧的pad作为port1端口,位于右侧的pad为port2端口。

30.s22、在port2端口连接50ω的接地电阻,如图3所示。

31.s23、在port1端口依次输入电流i1和i2,测量得到port1端口对应的电压v1和v2,如图3所示。

32.本发明实施例中,针对晶圆中的每个芯片,其iv测试条件均相同,即在每个芯片port1端口输入的电流i1均相同,在每个芯片port1端口输入的电流i2均相同,且i1≠i2。

33.s3、根据隔离环的iv测试结果计算得到电压差值,即根据port1端口的电压v1和v2计算得到电压差值

∆

v= v

1 ‑ꢀ

v2。

34.s4、针对晶圆中的每个芯片,判断其电压差值是否在预设范围内,若是则判定该芯片为正常芯片,否则判定该芯片具有隐裂纹缺陷。

35.本发明实施例中,电压差值的预设范围为:v

low

≤δv≤v

high

,其中v

low

表示预设的卡控门限最小值,v

high

表示预设的卡控门限最大值。

36.本发明实施例中,卡控门限最小值v

low

和卡控门限最大值v

high

均通过n个芯片的电压差值δv得到,n为晶圆中的芯片总数。具体而言,本发明实施例中卡控门限最小值v

low

和卡控门限最大值v

high

均通过针对n个芯片的电压差值δv进行大量数据测试后,按照数据分布的三个西格玛区间确定得到。

37.s5、将判定具有隐裂纹缺陷的芯片在晶圆上做隔离标记,划定晶圆的隔离区域,完成筛片。

38.本领域的普通技术人员将会意识到,这里所述的实施例是为了帮助读者理解本发明的原理,应被理解为本发明的保护范围并不局限于这样的特别陈述和实施例。本领域的普通技术人员可以根据本发明公开的这些技术启示做出各种不脱离本发明实质的其它各种具体变形和组合,这些变形和组合仍然在本发明的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。