1.本发明涉及静电防护技术领域,特别涉及一种低触发、低容值片式静电抑制器的制备方法。

背景技术:

2.静电抑制器的制备方法是一种进行片式静电抑制器加工制作的方法,静电保护器适用于对抗esd及其他电压突变脉冲,该器件最多可以保护18个数据通道,最大可抵抗30kv的尖峰脉冲. 其引脚容抗仅为10pf,非常适合保护高速或高频(可达200mhz以上)数据线,由于他们的小体积及非常小的漏电流,他们非常适用于一些对空间及功耗要求严格的场合,随着科技的不断发展,人们对于静电抑制器的制备方法的制造工艺要求也越来越高。

3.现有技术中,授权公告号为cn202011438369.2的专利公开了一种静电抑制器及其制作方法,带有一对底部电极和一对内电极的下基层,由一双面覆铜板按预设电极图案进行刻蚀而得到;其中,所述一对内电极分别通过盲孔连接层与所述一对底部电极对应连接导通;上基层;以及,中间粘合层,位于下基层和上基层之间,用于粘合下基层和上基层;其中:所述上基层的内侧开设有一开口朝向所述中间粘合层的凹槽,同时所述中间粘合层上开设一通孔,且所述通孔与所述凹槽连通形成一位于所述静电抑制器内部的空腔;所述一对内电极的两电极之间具有采用静电防护浆料印刷并固化而成的静电防护部,且所述静电防护部位于所述空腔内,现有的静电抑制器的制备方法在使用时存在一定的弊端,首先,在esd保护器件中,由于直接印刷电极会造成放电电极之间的间隔偏差,esd响应性容易变动。此外,虽然需要通过放电电极相对的区域的面积来调整esd响应性,但由于该调整被产品尺寸等所限制,因此,有时会难以实现所希望的esd响应性,不利于人们的使用,还有,在esd保护器件中,由于厚膜印刷,各层界面存在一定的缺陷,影响器件的稳定性和可靠性,因此在材料的选择上要求较高,较低的触发电压目前通过较窄的缝隙实现,会增大漏电的风险,目前高速的数据传输,对容值要求越来越低,缝隙式电极产生的容值已经不能满足低容值的要求,给人们的使用过程带来了一定的不利影响,为此,我们提出一种低触发、低容值片式静电抑制器的制备方法。

技术实现要素:

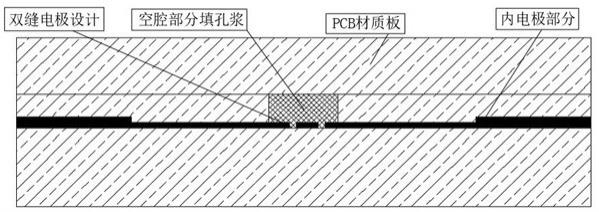

4.(一)解决的技术问题针对现有技术的不足,本发明提供了一种低触发、低容值片式静电抑制器的制备方法,通过激光精度切割制备的电极缝隙,相对于厚膜印刷工艺制备的电极,缝隙宽度一致性好,采用双缝隙电极设计,实现低容值,解决了超小容值的问题,采用3层压合板设计,实现了内部结构较高的致密度,具有较高的防渗透和耐湿气的性能,可以有效解决背景技术中的问题。

5.(二)技术方案为实现上述目的,本发明采取的技术方案为:一种低触发、低容值片式静电抑制器

的制备方法,包括以下操作步骤:s1:浆料选择:采取纳米材料制备技术、半导体材料、高分子材料和pcb板技术相结合,在电极切槽部位印刷具有疏松骨架结构以及半导体特性的功能材料层,切槽部位电极存在尖端和功能浆料为疏松的骨架结构形成的缝隙,实现低电压特性;s2:激光切割:通过激光精度切割制备的电极缝隙,控制缝隙宽度,通过覆铜板制备电极与基材结合,保证器件的触发性能,为电子传输提供便利的通道;s3:双缝设计:采用双缝隙切割电极,切割的缝隙为12~15um,取代原有产品的单缝隙工艺,电极的有效距离不变,双缝隙宽度之和为原来的单缝隙宽度,采用并联电容设计,电容降低;s4:压合工艺:采用三层pcb板压合工艺,底部留有双峰切割电极,在切割部位上方的压合板,中间层部位预留边长100~200um的通孔,采用压合工艺使电极缝隙的上方形成空腔后,通过厚膜印刷工艺印刷浆料,真空条件下对空腔进行填充,与底部电极完全结合,通过150℃烘干,蒸发溶剂后在顶部形成空间,预留的空间部分为静电浆料受到冲击提供缓冲作用,然后再压合一层pcb板,采用200℃高温压合增加结合力,排出里面的湿气提高器件的可靠性,实现内部结构较高的致密度,具有较高的防渗透和耐湿气的性能,同时中间层空腔的设计为防静电浆料提供能量释放的空间;s5:电极金属化:压合完成后,通过机械切割或激光切割的方式,将器件本身的预定的单元格进行切割,形成小颗粒,通过端涂低温固化浆料实现端测电极金属化,然后再镀锡镀镍形成电极,通过电镀工艺增加器件本身的重量,降低抛料的风险,端电极突出后焊接时在器件本体与基板接触的缝隙加大,减少漏电风险,制备完成。

6.作为一种优选的技术方案,所述s1步骤中在材料准备的过程中采取纳米材料制备技术、半导体材料、高分子材料和pcb板技术相结合的方法。

7.作为一种优选的技术方案,所述s2步骤中缝隙的宽度控制为12~15um,双缝隙的缝隙宽度总和小于30um。

8.作为一种优选的技术方案,所述s3步骤中采用双缝隙的设计对电极进行切割,且切割的缝隙为12~15um。

9.作为一种优选的技术方案,所述s2步骤中器件在保证不漏电的基础上,最大限度的降低触发电压,使触发电压降至300v以下,动作电压降至2kv,实现较好的esd响应性。

10.作为一种优选的技术方案,所述s3步骤中采用双缝隙电极设计实现低容值,解决超小容值的问题,电容值由现有的0.15pf降低为0.065~0.075pf。

11.作为一种优选的技术方案,所述s5步骤中采用端涂工艺进行加工,端电极采用低温固化银浆金属化,金属化后采用电镀工艺实现端头电极化。

12.作为一种优选的技术方案,所述s5步骤中采用电镀工艺实现端头电极化,改善抛料率,所述抛料率由原有抛料率的7

‰

降低至3

‰

以下。

13.(三)有益效果与现有技术相比,本发明提供了一种低触发、低容值片式静电抑制器的制备方法,具备以下有益效果:该一种低触发、低容值片式静电抑制器的制备方法,通过激光精度切割制备的电极缝隙,相对于厚膜印刷工艺制备的电极,缝隙宽度一致性好,采用双缝隙电极设计,实现低容值,解决了超小容值的问题,采用3层压合板设计,实现了内部结构较高的致密

度,具有较高的防渗透和耐湿气的性能,采取纳米材料制备技术、半导体材料、高分子材料和pcb板技术相结合,在电极切槽部位印刷具有疏松骨架结构以及半导体特性的功能材料层,切槽部位电极存在尖端和功能浆料为疏松的骨架结构形成的缝隙,实现低电压特性,通过激光精度切割制备的电极缝隙,控制缝隙宽度,通过覆铜板制备电极与基材结合,保证器件的触发性能,为电子传输提供便利的通道,采用双缝隙切割电极,切割的缝隙为12~15um,取代原有产品的单缝隙工艺,电极的有效距离不变,双缝隙宽度之和为原来的单缝隙宽度,采用并联电容设计,电容降低,采用三层pcb板压合工艺,底部留有双峰切割电极,在切割部位上方的压合板,中间层部位预留边长100~200um的通孔,采用压合工艺使电极缝隙的上方形成空腔后,通过厚膜印刷工艺印刷浆料,真空条件下对空腔进行填充,与底部电极完全结合,通过150℃烘干,蒸发溶剂后在顶部形成空间,预留的空间部分为静电浆料受到冲击提供缓冲作用,然后再压合一层pcb板,采用200℃高温压合增加结合力,排出里面的湿气提高器件的可靠性,实现内部结构较高的致密度,具有较高的防渗透和耐湿气的性能,同时中间层空腔的设计为防静电浆料提供能量释放的空间,压合完成后,通过机械切割或激光切割的方式,将器件本身的预定的单元格进行切割,形成小颗粒,通过端涂低温固化浆料实现端测电极金属化,然后再镀锡镀镍形成电极,通过电镀工艺增加器件本身的重量,降低抛料的风险,端电极突出后焊接时在器件本体与基板接触的缝隙加大,减少漏电风险,制备完成,整个静电抑制器的制备方法结构简单,操作方便,使用的效果相对于传统方式更好。

附图说明

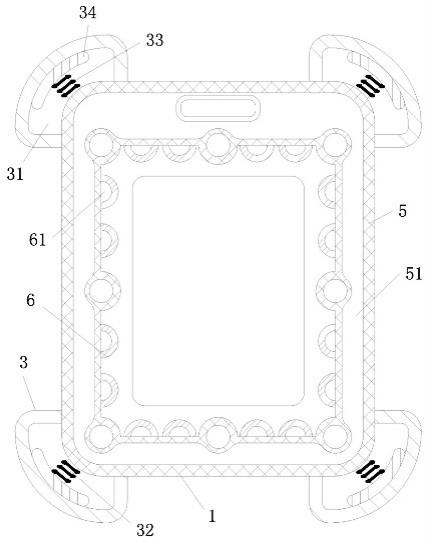

14.图1为本发明一种低触发、低容值片式静电抑制器的制备方法的整体结构示意图。

具体实施方式

15.下面将结合附图和具体实施方式对本发明的技术方案进行清楚、完整地描述,但是本领域技术人员将会理解,下列所描述的实施例是本发明一部分实施例,而不是全部的实施例,仅用于说明本发明,而不应视为限制本发明的范围。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。实施例中未注明具体条件者,按照常规条件或制造商建议的条件进行。所用试剂或仪器未注明生产厂商者,均为可以通过市售购买获得的常规产品。

16.在本发明的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

17.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

18.如图1所示,一种低触发、低容值片式静电抑制器的制备方法,包括以下操作步骤:

s1:浆料选择:采取纳米材料制备技术、半导体材料、高分子材料和pcb板技术相结合,在电极切槽部位印刷具有疏松骨架结构以及半导体特性的功能材料层,切槽部位电极存在尖端和功能浆料为疏松的骨架结构形成的缝隙,实现低电压特性;s2:激光切割:通过激光精度切割制备的电极缝隙,控制缝隙宽度,通过覆铜板制备电极与基材结合,保证器件的触发性能,为电子传输提供便利的通道;s3:双缝设计:采用双缝隙切割电极,切割的缝隙为12~15um,取代原有产品的单缝隙工艺,电极的有效距离不变,双缝隙宽度之和为原来的单缝隙宽度,采用并联电容设计,电容降低;s4:压合工艺:采用三层pcb板压合工艺,底部留有双峰切割电极,在切割部位上方的压合板,中间层部位预留边长100~200um的通孔,采用压合工艺使电极缝隙的上方形成空腔后,通过厚膜印刷工艺印刷浆料,真空条件下对空腔进行填充,与底部电极完全结合,通过150℃烘干,蒸发溶剂后在顶部形成空间,预留的空间部分为静电浆料受到冲击提供缓冲作用,然后再压合一层pcb板,采用200℃高温压合增加结合力,排出里面的湿气提高器件的可靠性,实现内部结构较高的致密度,具有较高的防渗透和耐湿气的性能,同时中间层空腔的设计为防静电浆料提供能量释放的空间;s5:电极金属化:压合完成后,通过机械切割或激光切割的方式,将器件本身的预定的单元格进行切割,形成小颗粒,通过端涂低温固化浆料实现端测电极金属化,然后再镀锡镀镍形成电极,通过电镀工艺增加器件本身的重量,降低抛料的风险,端电极突出后焊接时在器件本体与基板接触的缝隙加大,减少漏电风险,制备完成。

19.进一步的,s1步骤中在材料准备的过程中采取纳米材料制备技术、半导体材料、高分子材料和pcb板技术相结合的方法。

20.进一步的,s2步骤中缝隙的宽度控制为12~15um,双缝隙的缝隙宽度总和小于30um。

21.进一步的,s3步骤中采用双缝隙的设计对电极进行切割,且切割的缝隙为12~15um。

22.进一步的,s2步骤中器件在保证不漏电的基础上,最大限度的降低触发电压,使触发电压降至300v以下,动作电压降至2kv,实现较好的esd响应性。

23.进一步的,s3步骤中采用双缝隙电极设计实现低容值,解决超小容值的问题,电容值由现有的0.15pf降低为0.065~0.075pf。

24.进一步的,s5步骤中采用端涂工艺进行加工,端电极采用低温固化银浆金属化,金属化后采用电镀工艺实现端头电极化。

25.进一步的,s5步骤中采用电镀工艺实现端头电极化,改善抛料率,抛料率由原有抛料率的7

‰

降低至3

‰

以下。

26.实施例一:s2步骤中缝隙的宽度控制为13um,双缝隙的缝隙宽度总和为28um。

27.s3步骤中采用双缝隙的设计对电极进行切割,且切割的缝隙为13um。

28.s2步骤中器件在保证不漏电的基础上,最大限度的降低触发电压,使触发电压降至280v,动作电压降至2kv,实现较好的esd响应性。

29.s3步骤中采用双缝隙电极设计实现低容值,解决超小容值的问题,电容值由现有

的0.15pf降低为0.07pf。

30.实施例二:s2步骤中缝隙的宽度控制为14um,双缝隙的缝隙宽度总和为29um。

31.s3步骤中采用双缝隙的设计对电极进行切割,且切割的缝隙为14um。

32.s2步骤中器件在保证不漏电的基础上,最大限度的降低触发电压,使触发电压降至290v,动作电压降至2kv,实现较好的esd响应性。

33.s3步骤中采用双缝隙电极设计实现低容值,解决超小容值的问题,电容值由现有的0.15pf降低为0.071pf。

34.工作原理:采取纳米材料制备技术、半导体材料、高分子材料和pcb板技术相结合,在电极切槽部位印刷具有疏松骨架结构以及半导体特性的功能材料层,切槽部位电极存在尖端和功能浆料为疏松的骨架结构形成的缝隙,实现低电压特性,通过激光精度切割制备的电极缝隙,控制缝隙宽度,通过覆铜板制备电极与基材结合,保证器件的触发性能,为电子传输提供便利的通道,采用双缝隙切割电极,切割的缝隙为12~15um,取代原有产品的单缝隙工艺,电极的有效距离不变,双缝隙宽度之和为原来的单缝隙宽度,采用并联电容设计,电容降低,采用三层pcb板压合工艺,底部留有双峰切割电极,在切割部位上方的压合板,中间层部位预留边长100~200um的通孔,采用压合工艺使电极缝隙的上方形成空腔后,通过厚膜印刷工艺印刷浆料,真空条件下对空腔进行填充,与底部电极完全结合,通过150℃烘干,蒸发溶剂后在顶部形成空间,预留的空间部分为静电浆料受到冲击提供缓冲作用,然后再压合一层pcb板,采用200℃高温压合增加结合力,排出里面的湿气提高器件的可靠性,实现内部结构较高的致密度,具有较高的防渗透和耐湿气的性能,同时中间层空腔的设计为防静电浆料提供能量释放的空间,压合完成后,通过机械切割或激光切割的方式,将器件本身的预定的单元格进行切割,形成小颗粒,通过端涂低温固化浆料实现端测电极金属化,然后再镀锡镀镍形成电极,通过电镀工艺增加器件本身的重量,降低抛料的风险,端电极突出后焊接时在器件本体与基板接触的缝隙加大,减少漏电风险,制备完成。

35.需要说明的是,在本文中,诸如第一和第二(一号、二号)等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

36.以上显示和描述了本发明的基本原理和主要特征和本发明的优点。本行业的技术人员应该了解,本发明不受上述实施例的限制,上述实施例和说明书中描述的只是说明本发明的原理,在不脱离本发明精神和范围的前提下,本发明还会有各种变化和改进,这些变化和改进都落入要求保护的本发明范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。