1.本公开涉及具有沟槽结构的二极管、晶体管等半导体装置以及半导体装置的制造方法。

背景技术:

2.过去,如特表2016

‑

502270号公报中也记载的那样,已知具有沟槽结构的半导体装置,关于该沟槽结构,在位于从形成肖特基势垒的第1导电型的半导体层的表面形成的沟槽的底部的该半导体层内区域形成有第2导电型低浓度区域。

技术实现要素:

3.发明要解决的课题

4.在上述现有的半导体装置中,在俯视观察半导体基板时,沟槽底部的第2导电型低浓度区域伸出到沟槽外。

5.在这样的第2导电型低浓度区域从沟槽底部伸出到外方的结构中,该第2导电型低浓度区域伸出到正向电流的导通区域,会招致导通电阻的上升,因此有时正向特性劣化。

6.若要提升耐压而形成上述第2导电型低浓度区域,进而将该区域形成得大,就能得到耐压的提升,但会伴随导通电阻的上升。为此,有时难以抑制导通电阻的上升且提升耐压。

7.另外,在下一代器件材料(gan、sic等)等特定的半导体材料中,今后也有可能出现未充分建立离子注入技术的阶段。可能存在如下问题:在选择这样的材料时,难以使用离子注入技术将第2导电型低浓度区域精度良好地形成在所期望的范围。

8.用于解决课题的手段

9.本公开的1个方式的半导体装置具备:半导体基板;层叠于所述半导体基板的表面的第1导电型的第1半导体层;层叠于所述第1半导体层的凹部的底的通过外延生长而结晶生长的第2导电型的第2半导体层;侧面由所述第1半导体层构成且底面的至少一部分由所述第2半导体层构成的沟槽;将所述沟槽的底面以及侧面覆膜的绝缘膜;将被所述绝缘膜覆膜的所述沟槽的内部填埋的导电体;和与所述导电体电连接且与所述第1半导体层的表面形成肖特基势垒的金属膜,所述第2半导体层构成所述沟槽的底面的全部或中央部,在俯视观察所述半导体基板时收在所述沟槽的区域内。

10.本公开的1个方式的半导体装置的制造方法制造半导体装置,所述半导体装置具备:半导体基板;层叠于所述半导体基板的表面的第1导电型的第1半导体层;层叠于所述第1半导体层的凹部的底的第2导电型的第2半导体层;侧面由所述第1半导体层构成且底面的至少一部分由所述第2半导体层构成的沟槽;将所述沟槽的底面以及侧面覆膜的绝缘膜;将被所述绝缘膜覆膜的所述沟槽的内部填埋的导电体;和与所述导电体电连接且与所述第1半导体层的表面形成肖特基势垒的金属膜,所述半导体装置的制造方法具备:第2半导体层层叠工序,在所述第1半导体层上通过外延生长层叠包含第2导电型的杂质的所述第2半导

体层。

附图说明

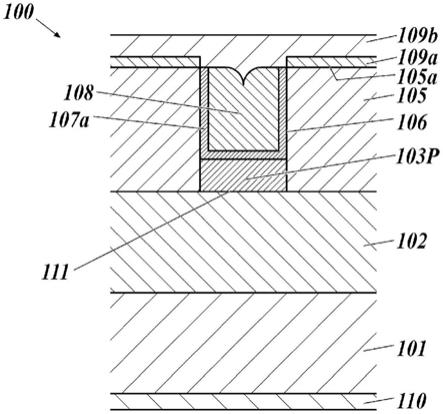

11.图1是用于说明本公开的第1实施方式的截面示意图。

12.图2是用于说明本公开的第1实施方式的截面示意图。

13.图3是用于说明本公开的第1实施方式的截面示意图。

14.图4是用于说明本公开的第1实施方式的截面示意图。

15.图5是用于说明本公开的第1实施方式的截面示意图。

16.图6是用于说明本公开的第1实施方式的截面示意图。

17.图7是用于说明本公开的第1实施方式的截面示意图。

18.图8是用于说明本公开的第1实施方式的截面示意图。

19.图9是用于说明本公开的第2实施方式的截面示意图。

20.图10是用于说明本公开的第2实施方式的截面示意图。

21.图11是用于说明本公开的第2实施方式的截面示意图。

22.图12是用于说明本公开的第2实施方式的截面示意图。

23.图13是用于说明本公开的第2实施方式的截面示意图。

24.图14是用于说明本公开的第2实施方式的截面示意图。

25.图15是用于说明本公开的第2实施方式的截面示意图。

26.图16是用于说明本公开的第3实施方式的截面示意图。

27.图17是用于说明本公开的第3实施方式的截面示意图。

28.图18是用于说明本公开的第3实施方式的截面示意图。

29.图19是用于说明本公开的第3实施方式的截面示意图。

30.图20是用于说明本公开的第3实施方式的截面示意图。

31.图21是用于说明本公开的第3实施方式的截面示意图。

32.图22是用于说明本公开的第3实施方式的截面示意图。

33.图23是用于说明本公开的第3实施方式的截面示意图。

34.图24是用于说明本公开的第3实施方式的截面示意图。

35.图25是用于说明本公开的第4实施方式的截面示意图。

36.图26是用于说明本公开的第4实施方式的截面示意图。

37.图27是用于说明本公开的第4实施方式的截面示意图。

38.图28是用于说明本公开的第4实施方式的截面示意图。

39.图29是用于说明本公开的第4实施方式的截面示意图。

40.图30是用于说明本公开的第4实施方式的截面示意图。

41.图31是用于说明本公开的第5实施方式的截面示意图。

42.图32是用于说明本公开的第5实施方式的截面示意图。

43.图33是用于说明本公开的第5实施方式的截面示意图。

44.图34是用于说明本公开的第5实施方式的截面示意图。

45.图35是用于说明本公开的第5实施方式的截面示意图。

46.图36是用于说明本公开的第5实施方式的截面示意图。

47.图37是用于说明本公开的第5实施方式的截面示意图。

48.图38是用于说明本公开的第5实施方式的截面示意图。

49.图39是用于说明本公开的第5实施方式的截面示意图。

50.图40是用于说明本公开的第5实施方式的截面示意图。

51.图41是用于说明本公开的第6实施方式的截面示意图。

52.图42是关于正向电压以及耐压而比较本发明例和比较例的图表。

具体实施方式

53.以下参考附图来说明本公开的一个实施方式。

54.〔第1实施方式〕

55.首先说明第1实施方式的半导体装置的制造方法以及半导体装置。

56.(制造方法)

57.如下那样制造半导体装置。

58.对图1所示的在半导体基板101上层叠第1半导体层的下层部102的结构如图2所示那样,实施第2半导体层层叠工序,通过外延生长层叠包含第2导电型(p型)的杂质的第2半导体层103。

59.半导体基板101是n型高浓度硅基板。半导体层102是通过外延生长法层叠于半导体基板101的表面的n型低浓度的半导体层。

60.接下来,如图3所示那样在第2半导体层103上形成蚀刻掩模图案104。

61.接下来如图4所示那样,通过将蚀刻掩模图案104作为掩模进行蚀刻,来除去从蚀刻掩模图案104露出的第2半导体层103,留下蚀刻掩模图案104下的第2半导体层103p。如以上那样,在第2半导体层层叠工序之后,将选择性地蚀刻通过该第2半导体层层叠工序层叠的半导体层而留下的部分作为产品部分的第2半导体层103p。

62.接下来如图5所示那样,与第2半导体层103p的周围相邻地将n型的第1半导体层的上层部105层叠得比第2半导体层103p更高,由此构成沟槽106。

63.接下来如图6所示那样除去蚀刻掩模图案104。于是出现沟槽106。另外,沟槽106的数量是任意的。

64.接下来如图7所示那样,将绝缘膜(热氧化膜)107a、107b形成于包括沟槽106内在内的上层部105的表面、在沟槽106的底面露出的第2半导体层103p的上表面后,在沟槽106内埋设导电体108。作为导电体108的材料,运用多晶硅或金属材料等。

65.进而,在将沟槽106的周围的绝缘膜107b除去后,如图8所示那样,使肖特基金属膜109a与上层部105的上表面105a接合来形成肖特基势垒,进而形成表面电极金属膜109b来将肖特基金属膜109a和导电体108连接。进而形成背面电极金属膜110。

66.(半导体装置)

67.能通过例如以上的制造方法制造的半导体装置100,如图8所示那样具备:第1导电型且比较高浓度的半导体基板101;层叠于半导体基板101的表面的第1导电型且比较低浓度的第1半导体层102、105;层叠于第1半导体层102、105的凹部111的底的通过外延生长而结晶生长的第2导电型的第2半导体层103p;侧面由第1半导体层的上层部105构成且底面的全部由第2半导体层103p构成的沟槽106;将沟槽106的底面以及侧面覆膜的绝缘膜107a;将

被绝缘膜107a覆膜的沟槽106的内部填埋的导电体108;和与导电体108电连接且与第1半导体层的上层部105的上表面105a形成肖特基势垒的肖特基金属膜109a。

68.第2半导体层103p配置于沟槽106下,在俯视观察半导体基板101时收在沟槽106的区域内。

69.层叠于半导体基板101上的半导体层内的区域、即俯视观察半导体基板101时沟槽106的区域外的区域,被第1导电型(n型)的区域占据。因此,能在肖特基结下将正向电流的导通区域确保得大。

70.半导体装置100除了能应用于sbd(schottky diode,肖特基二极管)以外,还能应用于mosfet(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,金属氧化物半导体场效应晶体管)、igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)等。

71.在构成mosfet的情况下,将pbody(p体)、栅极等形成于中心部,表面电极金属膜109b成为源极电极,背面电极金属膜110成为漏极电极。在igbt的情况下,进一步运用p型高浓度基板作为半导体基板101,表面电极金属膜109b成为发射极电极,背面电极金属膜110成为集电极电极。

72.〔第2实施方式〕

73.接下来说明第2实施方式的半导体装置的制造方法以及半导体装置。

74.(制造方法)

75.如下那样制造半导体装置。

76.对图9所示的在半导体基板201上层叠第1半导体层202的结构,如图10所示那样,在第1半导体层202上形成蚀刻掩模图案203。半导体基板201是n型高浓度硅基板。半导体层202是通过外延生长法层叠于半导体基板201的表面的n型低浓度的半导体层。

77.接下来,如图11所示那样,通过将蚀刻掩模图案203作为掩模进行蚀刻,来在第1半导体层202形成凹部204。

78.接下来,如图12所示那样,实施第2半导体层层叠工序,将包含第2导电型(p型)的杂质的第2半导体层205p通过外延生长层叠于凹部204的底。由此形成以第2半导体层205p的上表面为底面的沟槽206。

79.接下来,如图13所示那样除去蚀刻掩模图案203。

80.接下来,如图14所示那样,在将绝缘膜(热氧化膜)207a、207b形成于包括沟槽206内在内的第1半导体层202的表面、在沟槽206的底面露出的第2半导体层205p的上表面后,在沟槽206内埋设导电体208。作为导电体208的材料,运用多晶硅或金属材料等。

81.进而,在除去沟槽206的周围的绝缘膜207b后,如图15所示那样,使肖特基金属膜209a与第1半导体层202的表面202a接合来形成肖特基势垒,进而形成表面电极金属膜209b来将肖特基金属膜209a和导电体208连接。进而形成背面电极金属膜210。

82.(半导体装置)

83.能通过例如以上的制造方法制造的半导体装置200,如图15所示那样具备:第1导电型且比较高浓度的半导体基板201;层叠于半导体基板201的表面的第1导电型且比较低浓度的第1半导体层202;层叠于第1半导体层202的凹部204的底的通过外延生长而结晶生长的第2导电型的第2半导体层205p;侧面由第1半导体层202构成且底面的全部由第2半导体层205p构成的沟槽206;将沟槽206的底面以及侧面覆膜的绝缘膜207a;将被绝缘膜207a

覆膜的沟槽206的内部填埋的导电体208;和与导电体208电连接且与第1半导体层202的表面202a形成肖特基势垒的肖特基金属膜209a。

84.第2导电型区域205p配置于沟槽206下,在俯视观察半导体基板201时收在沟槽206的区域内。

85.层叠于半导体基板201上的半导体层内的区域、即俯视观察半导体基板201时沟槽206的区域外的区域被第1导电型(n型)的区域占据。因此,能在肖特基结下将正向电流的导通区域确保得大。

86.半导体装置200除了能应用于sbd(schottky diode,肖特基二极管)以外,还能应用于mosfet(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,金属氧化物半导体场效应晶体管)、igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)等。

87.在构成mosfet的情况下将,pbody、栅极等形成于中心部,表面电极金属膜209b成为源极电极,背面电极金属膜210成为漏极电极。在igbt的情况下,进一步运用p型高浓度基板作为半导体基板201,表面电极金属膜209b成为发射极电极,背面电极金属膜210成为集电极电极。

88.〔第3实施方式〕

89.接下来,说明第3实施方式的半导体装置的制造方法以及半导体装置。

90.(制造方法)

91.如下那样制造半导体装置。

92.如图16所示那样,与上述第2实施方式同样,在半导体基板301上的第1半导体层302上形成在沟槽的形成预定的区域开口的绝缘体掩模图案303,将其作为掩模进行蚀刻,由此在第1半导体层302形成凹部304(凹部形成工序)。

93.接下来,作为凹部形成工序后的掩模形成工序,首先如图17所示那样形成绝缘体层305。将绝缘体层305层叠于上述的沟槽形成工序中的绝缘体掩模图案303上。与此同时用绝缘体层305覆盖凹部304的底面以及侧面。作为构成绝缘体掩模图案303以及绝缘体层305的绝缘材料,能举出氧化硅、氮化硅、teos(四乙氧基硅烷)等。作为绝缘体层205的层叠方法,例如运用化学蒸镀(cvd)。

94.接下来,如图18所示那样蚀刻表面整体。作为蚀刻,运用各向异性蚀刻。作为各向异性蚀刻,运用与表面垂直的纵向的蚀刻速度比与表面平行的横向的蚀刻速度快的反应性的各向异性蚀刻。

95.因此,如图18所示那样,能将附着在绝缘体层305的一部分当中凹部304的底面的外缘部304a以及侧面304b的部分的侧壁绝缘体305s留下,并使凹部304的底面的中央部304c露出。这是因为,在将凹部304的底面的中央部304c上的绝缘体通过纵向蚀刻除去时,侧壁绝缘体305s残存。

96.侧壁绝缘体305s由于是越靠近凹部304的开口的部位,蚀刻越是进展,因此随着从凹部304的开口靠近底面而变厚。

97.另外,在凹部304的周围的第1半导体层302的表面302a中,绝缘体掩模图案303在图17所示的蚀刻前的阶段被绝缘体层305覆盖。为此,在将凹部304的底面的中央部304c上的绝缘体通过纵向蚀刻除去时,绝缘体掩模图案303也残存。

98.将通过以上的各向异性蚀刻而残存的绝缘体掩模图案303和侧壁绝缘体305s合起

来作为绝缘体掩模图案306。

99.绝缘体掩模图案306,如图18所示那样成为覆盖凹部304的周围的第1半导体层302的表面302a、和凹部304的底面的外缘部304a以及侧面304b、并使该底面的中央部304c露出的图案。将该绝缘体掩模图案306作为用于接下来的第2半导体层层叠工序的掩模。

100.接下来实施第2半导体层层叠工序。在第2半导体层层叠工序中,在第1半导体层302上通过外延生长层叠包含第2导电型的杂质的第2半导体层308。

101.在本实施方式中,将绝缘体掩模图案306作为掩模,在凹部304的底面的中央部304c所露出的第1半导体层302上层叠第2半导体层。其中,在这之前实施小凹部形成工序。

102.作为小凹部形成工序,如图19所示那样,将绝缘体掩模图案306作为掩模来蚀刻在凹部304的底面的中央部304c露出的第1半导体层302,在凹部304的底面的中央部304c形成第1半导体层302的小凹部307。

103.接下来,如图20所示那样,将绝缘体掩模图案306作为掩模,来在在凹部304的底面的中央部露出的第1半导体层302上层叠第2半导体层308。在此,由于先形成小凹部307,因此,将绝缘体掩模图案306作为掩模来在小凹部内307层叠第2半导体层308。

104.接下来,通过热处理使第2半导体层308的杂质扩散,如图21所示那样形成第2导电型区域309p。

105.除去绝缘体掩模图案306,形成将第2导电型区域309p的上表面作为底面中央部的沟槽310。

106.接下来如图23所示那样,在将绝缘膜(热氧化膜)311a、311b形成于包含沟槽310内在内的第1半导体层302的表面、在沟槽306的底面露出的第2半导体层308的上表面后,在沟槽310内埋设导电体312。作为导电体312的材料,运用多晶硅或金属材料等。

107.进而,在除去沟槽310的周围的绝缘膜311b后,如图24所示那样使肖特基金属膜313a与第1半导体层302的表面302a接合来形成肖特基势垒,进而形成表面电极金属膜313b来将肖特基金属膜313a和导电体312连接。进而形成背面电极金属膜314。

108.(半导体装置)

109.能通过例如以上的制造方法制造的半导体装置300,如图24所示那样具备:第1导电型且比较高浓度的半导体基板301;层叠于半导体基板301的表面的第1导电型且比较低浓度的第1半导体层302;层叠于第1半导体层302的凹部304 307的底的通过外延生长而结晶生长的第2导电型的第2半导体层308;侧面由第1半导体层302构成且底面的中央部由第2半导体层308构成的沟槽310;将沟槽310的底面以及侧面覆膜的绝缘膜311a;将被绝缘膜311a覆膜的沟槽310的内部填埋的导电体312;和与导电体312电连接且与第1半导体层302的表面302a形成肖特基势垒的肖特基金属膜313a。

110.第2半导体层308以及将其作为第2导电型杂质的扩散源的第2导电型区域309p配置于沟槽310下,在俯视观察半导体基板201时收在沟槽206的区域内。

111.第2半导体层308以及第2导电型区域309p构成沟槽310的底面的中央部,在俯视观察半导体基板301时,不与沟槽310的区域的外缘相接,收在该区域内。第1半导体层302构成除了中央部以外的沟槽310的底面的外缘部。

112.层叠于半导体基板301上的半导体层内的区域、即俯视观察半导体基板301时沟槽310的区域外的区域被第1导电型(n型)的区域占据。因此,能在肖特基结下将正向电流的导

通区域确保得大。

113.在本实施方式中,沟槽310的底面平坦地形成,即,第1半导体层302所构成的外缘部和第2半导体层308所构成的中央部配置在相同深度。

114.半导体装置300除了能应用于sbd(schottky diode,肖特基二极管)以外,还能应用于mosfet(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,金属氧化物半导体场效应晶体管)、igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)等。

115.在构成mosfet的情况下,将pbody、栅极等在中心部形成,表面电极金属膜313b成为源极电极,背面电极金属膜314成为漏极电极。在igbt的情况下,进一步运用p型高浓度基板作为半导体基板301,表面电极金属膜313b成为发射极电极,背面电极金属膜314成为集电极电极。

116.〔第4实施方式〕

117.接下来说明第4实施方式的半导体装置的制造方法以及半导体装置。

118.(制造方法)

119.如下那样制造半导体装置。

120.与上述第3实施方式的到图18为止的工序同样地,如图25所示那样在第1半导体层402形成凹部404,在凹部404内设置侧壁绝缘体405s。

121.将通过上述第3实施方式的同样的各向异性蚀刻而残存的绝缘体掩模图案403和侧壁绝缘体405s合起来作为绝缘体掩模图案406。

122.绝缘体掩模图案406如图25所示那样成为覆盖凹部404的周围的第1半导体层402的表面402a、和凹部404的底面的外缘部404a以及侧面404b、并使该底面的中央部404c露出的图案。将该送绝缘体掩模图案406作为用于接下来的第2半导体层层叠工序的掩模。

123.接下来实施第2半导体层层叠工序。在第2半导体层层叠工序中,在第1半导体层402上通过外延生长层叠包含第2导电型的杂质的第2半导体层407p。

124.在本实施方式中,将绝缘体掩模图案406作为掩模,在凹部404的底面的中央部404c所露出的第1半导体层402上层叠第2半导体层407p,得到图26所示的结构。

125.接下来,如图27所示那样除去绝缘体掩模图案406,形成将第2半导体层407p的上表面作为凸状的底面中央部的沟槽408。

126.接下来,如图28所示那样,在将绝缘膜(热氧化膜)409a、409b形成于包括沟槽408内在内的第1半导体层402的表面、在沟槽408的底面露出的第2半导体层407p的上表面后,如图29所示那样,在沟槽408内埋设导电体410。作为导电体410的材料,运用多晶硅或金属材料等。

127.进而,在除去沟槽408的周围的绝缘膜409b后,如图30所示那样使肖特基金属膜411a与第1半导体层402的表面402a接合来形成肖特基势垒,进而形成表面电极金属膜411b来将肖特基金属膜411a和导电体410连接。进而形成背面电极金属膜412。

128.(半导体装置)

129.能通过例如以上的制造方法制造的半导体装置400,如图30所示那样具备:第1导电型且比较高浓度的半导体基板401;层叠于半导体基板401的表面的第1导电型且比较低浓度的第1半导体层402;层叠于第1半导体层402的凹部404的底的通过外延生长而结晶生长的第2导电型的第2半导体层407p;侧面由第1半导体层402构成且底面的中央部由第2半

导体层407p构成的沟槽408;将沟槽408的底面以及侧面覆膜的绝缘膜409a;将被绝缘膜409a覆膜的沟槽408的内部填埋的导电体410;和与导电体410电连接且与第1半导体层402的表面402a形成肖特基势垒的肖特基金属膜411a。

130.第2半导体层407p配置于沟槽408下,在俯视观察半导体基板401时手咋沟槽408的区域内。

131.第2半导体层407p构成沟槽408的底面的中央部,在俯视观察半导体基板401时,不与沟槽408的区域的外缘相接,收在该区域内。第1半导体层402构成除了中央部以外的沟槽408的底面的外缘部。

132.层叠于半导体基板401上的半导体层内的区域、即俯视观察半导体基板401时沟槽408的区域外的区域被第1导电型(n型)的区域占据。因此,能在肖特基结下将正向电流的导通区域确保得大。

133.在本实施方式中,沟槽408的底面具有基于第2半导体层407p的凸部,即,相对于第1半导体层402所构成的外缘部,第2半导体层407p所构成的中央部形成为凸状。

134.半导体装置400除了能应用于sbd(schottky diode,肖特基二极管)以外,还能应用于mosfet(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,金属氧化物半导体场效应晶体管)、igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)等。

135.在构成mosfet的情况下,将pbody、栅极等形成于中心部,表面电极金属膜411b成为源极电极,背面电极金属膜412成为漏极电极。在igbt的情况下,进一步运用p型高浓度基板作为半导体基板401,表面电极金属膜411b成为发射极电极,背面电极金属膜412成为集电极电极。

136.〔第5实施方式〕

137.接下来说明第5实施方式的半导体装置的制造方法以及半导体装置。

138.(制造方法)

139.如下那样制造半导体装置。

140.在层叠于图31所示的半导体基板501上的第1半导体层的下层部502的表面如图32所示那样形成在沟槽的形成预定的区域开口的掩模图案503。半导体基板501是n型高浓度硅基板。第1半导体层的下层部502是通过外延生长法层叠于半导体基板501的表面的n型低浓度的半导体层。

141.接下来,实施通过外延生长层叠包含第2导电型(p型)的杂质的第2半导体层504p的第2半导体层层叠工序。

142.在本实施方式中,作为第2半导体层层叠工序,将掩模图案503作为掩模,在沟槽的形成预定区域的下层部502上将第2半导体层504p层叠得比掩模图案503低,将剩下的缝隙、即第2半导体层504p与掩模图案503的缝隙用氮化膜505填埋,得到图33所示的结构。

143.接下来,如图34所示那样蚀刻氮化膜505,来使掩模图案503露出,在掩模图案503的开口部的第2半导体层504p上留下氮化膜506。

144.接下来,如图35所示那样除去掩模图案503,在该掩模图案503所存在过的下层部502上,如图3所示那样,将第1半导体层的上层部507层叠得比第2半导体层504p高。上层部507与下层部502同样地是n型低浓度的半导体层。将氮化膜506作为掩模,通过外延生长法来在下层部502的表面层叠上层部507。

145.接下来,通过如图37所示那样除去氮化膜506,来构成沟槽508。

146.接下来,如图38所示那样,将绝缘膜(热氧化膜)509a、509b形成于包括沟槽508内在内的上层部507的表面、在沟槽508的底面露出的第2半导体层504p的上表面。

147.之后,如图39所示那样在沟槽508内埋设导电体510。作为导电体510的材料,运用多晶硅或金属材料等。

148.进而,在除去沟槽508的周围的绝缘膜509b后,如图40所示那样使肖特基金属膜511a与上层部507的上表面507a接合来形成肖特基势垒,进而形成表面电极金属膜511b来将肖特基金属膜511a和导电体510连接。进而形成背面电极金属膜512。

149.(半导体装置)

150.能通过例如以上的制造方法制造的半导体装置500,如图40所示那样具备:第1导电型且比较高浓度的半导体基板501;层叠于半导体基板501的表面的第1导电型且比较低浓度的第1半导体层502、507;层叠于第1半导体层502、507的凹部513的底的通过外延生长而结晶生长的第2导电型的第2半导体层504p;侧面由第1半导体层的上层部507构成且底面的全部由第2半导体层504p构成的沟槽508;将沟槽508的底面以及侧面覆膜的绝缘膜509a;将被绝缘膜509a覆膜的沟槽508的内部填埋的导电体510;和对导电体510电连接且与第1半导体层的上层部507的上表面507a形成肖特基势垒的肖特基金属膜511a。

151.第2半导体层504p配置于沟槽508下,在俯视观察半导体基板501时收在沟槽508的区域内。

152.层叠于半导体基板501上的半导体层内的区域、即俯视观察半导体基板501时沟槽508的区域外的区域,被第1导电型(n型)的区域占据。因此,能在肖特基结下将正向电流的导通区域确保得大。

153.半导体装置500除了能应用于sbd(schottky diode,肖特基二极管)以外,还能应用于mosfet(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,金属氧化物半导体场效应晶体管)、igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)等。

154.在构成mosfet的情况下,将pbody、栅极等形成于中心部,表面电极金属膜511b成为源极电极,背面电极金属膜512成为漏极电极。在igbt的情况下,进一步运用p型高浓度基板作为半导体基板501,表面电极金属膜511b成为发射极电极,背面电极金属膜512成为集电极电极。

155.〔第6实施方式〕

156.接下来说明第6实施方式的半导体装置的制造方法以及半导体装置。

157.本实施方式说明为以上述第1实施方式的半导体装置100或第5实施方式的半导体装置500为基本的半导体装置。

158.如图41所示那样,第1半导体层的上层部105、507的上表面105a、507a形成为凸状,其他如上述第1实施方式或第5实施方式说明的那样。

159.该上表面105a、507a突出成将从两侧的导电体108、510远离的中央部作为顶部。根据相关的结构,上表面105a、507a的面积变大,因此,与肖特基金属膜109a、511a的接合面即肖特基结面变大,能流过更大的正向电流。因此,能实现低的导通电阻的正向特性。

160.这样的凸状的上表面105a、507a能通过上述第1实施方式或第5实施方式中说明的制造方法构成。

161.将蚀刻掩模图案104作为掩模通过外延生长法来层叠上述第1实施方式的上层部105。为此,在从蚀刻掩模图案104的边缘远离的中央部,沉积量成为最大,形成上述的凸状的上表面105a。

162.将氮化膜506作为掩模,通过外延生长法来层叠上述第5实施方式的上层部507。为此,在从氮化膜506的边缘远离的中央部,沉积量成为最大,形成上述的凸状的上表面507a。

163.之后,不将凸状的上表面105a、507a平滑化,蒸镀肖特基金属膜109a、511a。

164.能得到以上那样形成为凸状的上表面105a、507a的肖特基结。

165.〔作用效果〕

166.根据以上说明的实施方式,通过配置于沟槽下的第2导电型的第2半导体层缓和反向电压施加时的电场,从而提升耐压。另外,能确保肖特基结下的正向电流的导通区域,能抑制导通电阻的上升。

167.另外,能够不使用离子注入法而使用外延技术来在沟槽底部将第2导电型的第2半导体层精度良好地形成在所期望的范围。对于半导体基板301、第1半导体层102、105以及第2半导体层103,还能选择gan(氮化镓)等未充分建立离子注入技术的半导体材料。另外半导体基板301、第1半导体层102、105以及第2半导体层103也可以是sic(碳化硅)、金刚石、ga2o3(氧化镓)、aln(氮化铝)。

168.若使用外延技术,则由于能比离子注入更陡峭地形成杂质分布,因此第2导电型区域难以扩展到肖特基结下的导通区域,能抑制导通电阻的上升。

169.根据第1或第5实施方式,不使用蚀刻法就能构成沟槽形状。为此,不再需要受到损伤的蚀刻面的后处理。

170.根据第1或第5实施方式,由于第1半导体层的下层部和上层部在不同工序中层叠,因此能在第1半导体层的下层部和上层部中改变掺杂浓度。由此能期待性能改善(例如,与上层部比较提高下层部的掺杂浓度,降低导通电阻)。

171.〔特性比较〕

172.在图42示出关于比较例和本发明例的vf

‑

vrm特性。vf是正向电流if=10〔a〕时的正向电压。vrm表示耐压,是反向漏电流irm=0.1〔ma〕时的反向电压。

173.在图42的图表中,出现表示遵循上述第1实施方式的本发明例的sbd的特性的点11。

174.在图42的图表中,点14表示p型区域103p伸出到沟槽106的外方的比较例的sbd的特性。其他条件与本发明例的sbd(点11)共通。

175.在图42的图表中,直线16表示没有p型区域103p的比较例的sbd的特性。其他条件与本发明例的sbd(点11)共通。直线16表示越使半导体层102、105的n型杂质浓度降低、vf以及vrm就越是直线上升的倾向。

176.在p型区域103p伸出到沟槽106的外方的比较例的sbd当中点14的sbd,相对于没有p型区域103p的比较例的sbd,能提升耐压vrm。但代价是正向电压vf上升。

177.在p型区域103p伸出到沟槽106的外方的比较例的sbd中,耐压vrm提升,并且正向电压vf上升。这是因为,虽然能得到耐压的提升,但伴随导通电阻的上升。

178.与此相对,在本发明例的sbd(点11)中,抑制了导通电阻的上升且提升了耐压,与比较例比较,能达成低的vf和高的耐压vrm。

179.以上说明了本公开的实施方式,但本实施方式在作为示例而示出的,能以其他种种形态实施,能在不脱离发明的要旨的范围内,进行构成要素的省略、置换、变更。

180.产业上的可利用性

181.本公开能利用在半导体装置以及半导体装置的制造方法中。

182.附图标记的说明

183.100 半导体装置

184.101 半导体基板

185.102、105 半导体层(n型)

186.103p 第2半导体层(p型)

187.106 沟槽

188.107a 绝缘膜(热氧化膜)

189.108 导电体

190.109a 肖特基金属膜

191.109b 表面电极金属膜

192.110 背面电极金属膜

193.111 凹部

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。