一种计算任意数据的crc值方法及装置

技术领域

1.本技术涉及crc计算方法领域,尤其涉及一种计算任意数据的crc值方法及装置。

背景技术:

2.crc校验是通信过程中检查数据序列是否发生错误的重要方法。其原理是按照crc计算规则计算被传送的x宽度据序列的y位校验码序列(crc码),将x宽度据序列和y位校验码序列合并发送。传输数据后校验x宽度据序列和y位校验码来判断数据序列是否发生错误。

3.现有技术中,计算crc校验码的方法包括串行计算和并行计算。其中,串行计算利用循环逐位计算数据序列的crc校验码,串行计算每个时钟周期处理1bit数据序列,当数据序列较长时,计算crc校验码消耗时间长、效率低。其中,并行计算需要将数据序列分成长度为nbit的若干组,每个时钟周期处理nbit的数据序列,再通过多组nbit串联的crc计算公式得到整个发送序列的crc。现有的并行计算方法计算的数据序列需要是n的整数倍。

技术实现要素:

4.为了解决上述技术问题或者至少部分地解决上述技术问题,本技术提供的计算任意数据的crc值方法及装置。

5.一方面,本技术提供的计算任意数据的crc值方法包括:

6.在数据序列的高位进行补零获取目标数据序列,目标数据序列的长度为并行运算模组宽度的整数倍;

7.以并行运算模组的宽度为步进长度,将目标数据序列分为若干有序的子目标数据序列;

8.定义crc值并初始化;

9.子目标数据序列依次输入并行运算模组计算crc值,直至最后一个子目标数据序列处理完毕,并行运算模组实现crc并行迭代公式,crc并行迭代公式公式为:

10.当前的crc值=crck(上一crc值,输入的子目标数据序列)^校正数值,其中,第一个子目标数据序列代入时,上一crc值等于初始化crc值。

11.更进一步地,在数据序列的高位进行补零获取目标数据序列包括:

12.获取数据序列的长度;

13.数据序列的长度除以所述并行运算模组的宽度取余获取余数;

14.计算余数的宽度;

15.并行运算模组宽度减去余数的宽度获取补零数量;

16.在数据序列高位按补零数量进行补零。

17.更进一步地,将目标数据序列分为若干子目标数据序列时,从目标数据序列的最高位或最低位开始,以并行运算模组的宽度为步进长度,将目标数据序列分为若干有序的子目标数据序列,以使有序的子目标数据序列保留目标数据序列中数据的排列顺序信息。

18.更进一步地,定义crc值并将crc值初始化为全1,crc值初始位数为k。

19.更进一步地,子目标数据序列依次输入crc并行迭代公式计算crc值,直至最后一个子目标数据序列处理完毕包括:

20.获取目标数据所分的子目标数据序列的数量;

21.构建统计子目标数据序列输入操作的计数变量,计数变量在子目标数据序列被输入计算后自动加一;

22.判断计数变量是否小于子目标数据序列的数量,是则将下一子目标数据序列依次输入crc并行迭代公式计算crc值。

23.更进一步地,在子目标数据序列输入crc并行迭代公式前,确定子目标数据序列中有效数据的宽度,根据有效数据的宽度选择对应的校正数值;

24.将相应的子目标数据序列和校正数值代入如下crc并行迭代公式计算crc值:当前的crc值=crck(上一crc值,输入的子目标数据序列)^校正数值,其中,crck(上一crc值,输入的子目标数据序列)套用crck(a,b),crck表示不同的crc算法,k表示crc算法的位宽,a为crck算法执行时参与运算的crc寄存器中的初始值,b为crck算法执行时的输入数据。

25.更进一步地,确定子目标数据序列中有效数据的宽度,根据有效数据的宽度选择对应的校正数值包括:

26.根据子目标数据序列的输入次序确定子目标数据序列的有效数据宽度值:

27.从高位输入时,对第一个输入子目标数据序列进行有效数据宽度计算,或从低位输入时,对最后一个输入子目标数据序列进行有效数据宽度计算;其余的子目标数据序列有效数据宽度等于并行运算模组的宽度;

28.判断子目标数据序列的有效数据的宽度是否等于并行运算模组的宽度,

29.是则校正数值赋值为零,且校正数值位数为k;

30.否则根据有效数据宽度和预先设置的校正数值计算规则获取对应的校正数值。

31.更进一步地,子目标数据序列进行有效数据宽度计算过程如下:获取数据序列的长度,数据序列的长度除以所述并行运算模组的宽度取余获取余数,计算余数的宽度,根据余数的宽度确定子目标数据序列中有效数据的宽度。

32.另一方面,本技术提供一种计算任意数据的crc值装置,所述计算任意数据的crc值装置包括数据序列参数处理模块,所述数据序列参数处理模块用于获取数据序列的长度,并用数据序列的长度除以并行运算模组的宽度获取并保存商和余数;

33.补零模块,所述补零模块用于从所述数据序列参数处理模块获取余数并利用余数计算补零数量,根据补零数量在数据序列高位进行补零,生成目标数据序列保存;

34.分组模块,所述分组模块用于根据并行运算模组的宽度对补零模块生成的目标数据序列进行分组为若干子目标数据序列;

35.校正数值计算模块,所述校正数值计算模块配置实现校正数值计算规则,根据子目标数据序列的有效数据宽度选择相应的校正数值计算规则来计算校正数值;

36.crc计算模块,所述crc计算模块包含并行运算模组,所述并行运算模组用于实现crc并行迭代公式;

37.crc计算模块用于从所述数据序列参数处理模块获取商和余数,根据商和余数确定目标数据所分的子目标数据序列的数量,利用子目标数据序列的数量控制所述crc并行

迭代公式的迭代过程;crc计算模块根据子目标数据序列的有效数据宽度确定crc并行迭代公式的校正数值;crc计算模块从分组模块获取子目标数据序列;将校正数值、子目标数据序列和crc并行迭代公式计算的crc值代入crc并行迭代公式迭代计算出最终的crc值。

38.更进一步地,所述计算任意数据的crc值装置还包括数据帧解析模块,所述数据帧解析模块用于解析数据包获取数据包中的数据序列,数据包中的校验序列以及数据序列的长度;

39.判断模块,所述判断模块比较所述校验序列和所述crc计算模块计算的crc值是否相同,是则认为数据传输过程中数据序列未发生错误,否则认为数据序列发生错误。

40.本技术实施例提供的上述技术方案与现有技术相比具有如下优点:

41.本技术采用并行的crc计算方法,crc计算速度快;本技术采用一个固定位数的并行运算模块计算实现任意位宽的crc算法,使得crc计算过程中,数据序列的长度不在受限于是crc算法位宽的整数倍。从而能够实现任意长度数据序列的crc值计算。与实现任意长度数据序列crc值计算的现有技术,本技术仅仅采用一个固定位数的并行运算模块即可实现,相比采用若干并行计算模块的现有技术能够节约硬件资源。由于本技术硬件资源占用少,因此能够应用在逻辑电路相对简单的处理器中,实现高速并行计算任意长度数据序列的crc值,可以有效的降低处理器成本。

附图说明

42.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本发明的实施例,并与说明书一起用于解释本发明的原理。

43.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

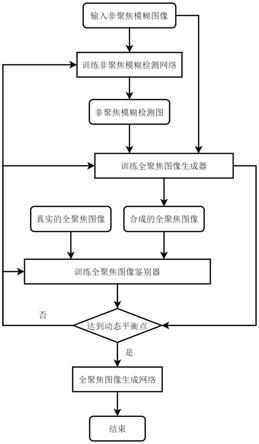

44.图1为本技术实施例提供的计算任意数据的crc值方法的流程图;

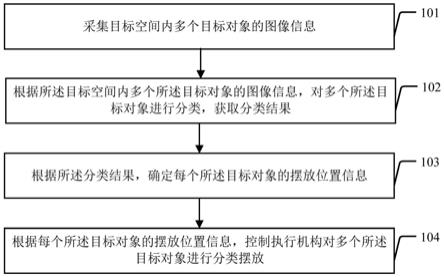

45.图2为本实施例提供的在数据序列的高位进行补零获取目标数据序列的流程图;

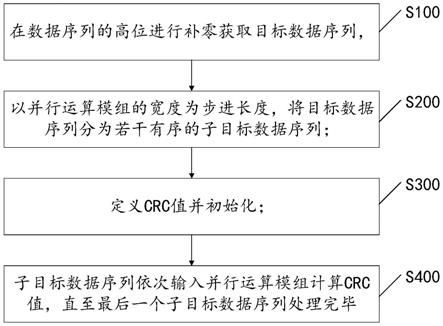

46.图3为本实施例提供的本技术迭代计算crc值的流程图;

47.图4为本实施例提供的获取校正数值的流程图;

48.图5为本技术实施例提供的计算任意数据的crc值装置的示意图。

具体实施方式

49.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术的一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本技术保护的范围。

50.需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

51.crc即循环冗余校验码(cyclic redundancy check):是数据通信领域中最常用的一种查错校验码。crc对数据进行多项式计算,并将得到的crc校验序列附在数据帧的后面,接收设备也执行类似的算法,对数据帧进行crc计算,并将crc计算结果与crc校验序列比较以判断数据帧是否出错,以保证接收数据的正确性和完整性。

52.常见的crc算法如下表所示:

53.crc

‑

4/itux4 x 14crc

‑

5/epcx5 x3 15crc

‑

5/itux5 x4 x2 15crc

‑

5/usbx5 x2 15crc

‑

6/itux6 x 16crc

‑

7/mmcx7 x3 17crc

‑

8x8 x2 x 18crc

‑

8/itux8 x2 x 18crc

‑

8/rohcx8 x2 x 18crc

‑

8/maximx8 x5 x4 18crc

‑

16/ibmx

16

x

15

x2 116crc

‑

16/maximx

16

x

15

x2 116crc

‑

16/usbx

16

x

15

x2 116crc

‑

16/modbusx

16

x

15

x2 116crc

‑

16/ccittx

16

x

12

x5 116crc

‑

16/ccitt

‑

falsex

16

x

12

x5 116crc

‑

16/x25x

16

x

12

x5 116crc

‑

16/xmodemx

16

x

12

x5 116crc

‑

16/dnpx

16

x

13

x

12

x

11

x

10

x8 x6 x5 x2 116crc

‑

32x

32

x

26

x

23

x

22

x

16

x

12

x

11

x

10

x8 x7 x5 x4 x2 x 132crc

‑

32/mpeg

‑

2x

32

x

26

x

23

x

22

x

16

x

12

x

11

x

10

x8 x7 x5 x4 x2 x 132

54.表中第一列为crc算法名称,第二列为采用的多项式,第三列为算法位宽(此算法位宽不等同于并行处理模组的宽度),现有的crc算法只能计算长度为并行处理模组输入数据位宽整数倍的数据序列的crc值。

55.实施例1

56.参阅图1所示,本实施例提供一种计算任意数据的crc值方法,包括:

57.s100,在数据序列的高位进行补零获取目标数据序列,目标数据序列的长度为并行运算模组宽度的整数倍;

58.具体实施过程中,参阅图2所示,在数据序列的高位进行补零获取目标数据序列的过程包括:

59.s101,获取数据序列的长度n;现有很多通信协议在进行数据封装传输时,会将数据序列的长度信息保存在封装数据的设定比特位中,如以太帧中保存数据长度信息,通过读取设定比特位中的数据获取数据序列的长度。

60.s102,数据序列的长度n除以所述并行运算模组的宽度m取余获取余数;具体方法

为n%m求得余数;

61.假定输入数据序列为0xaabbccdd1234567890(长度为9字节),并行运算模组的宽度为4字节,9%4得到余数为1字节

62.s103,计算余数的宽度;具体实例中9%4余数是1单位是字节,余数的宽度即为1字节或者8比特;

63.s104,并行运算模组宽度减去余数的宽度获取补零数量;具体实例中并行运算模组宽度为4字节,余数的宽度为1字节因此需要补零3字节;

64.s105,在数据序列高位按补零数量进行补零。具体实例中,在0xaabbccdd1234567890的高位补零3字节即可获得目标数据序列:0x000000aabbccdd1234567890(长度为12字节)。

65.s200,以并行运算模组的宽度为步进长度,将目标数据序列分为若干有序的子目标数据序列;将目标数据序列分为若干子目标数据序列时,从目标数据序列的最高位或最低位开始,以并行运算模组的宽度为步进长度,将目标数据序列分为若干有序的子目标数据序列,以使有序的子目标数据序列保留目标数据序列中数据的排列顺序信息。目标数据序列:0x000000aabbccdd1234567890(长度为12字节)被分为三个子目标数据序列0x000000aa、0xbbccdd12以及0x34567890。

66.s300,定义crc值并初始化;定义crc值并将crc值初始化为全1,初始化的crc值位数等于k,k为crc算法位宽。具体实例中将crc初始值定义为0xffff。

67.s400,子目标数据序列依次输入并行运算模组计算crc值,直至最后一个子目标数据序列处理完毕,并行运算模组实现crc并行迭代公式,crc并行迭代公式公式为:

68.当前的crc值=crck(上一crc值,输入的子目标数据序列)^校正数值,其中,第一个子目标数据序列代入时,上一crc值等于初始化crc值。

69.参阅图3所示,子目标数据序列依次输入crc并行迭代公式计算crc值,直至最后一个子目标数据序列处理完毕的过程包括:

70.s401,预先构建统计子目标数据序列输入操作的计数变量,

71.s402,获取目标数据所分的子目标数据序列的数量;具体实施过程中,一种可行的获取子目标数据序列的数量的方法包括:

72.获取数据序列的长度,数据序列的长度除以并行运算模组的宽度并保存商和余数,

73.如果余数等于零,则子目标数据序列的数量等于商的值;

74.如果余数不等于零,则子目标数据序列的数量等于商加一。

75.s403,循环判断计数变量是否小于子目标数据序列的数量,是则s404将下一子目标数据序列依次输入crc并行迭代公式计算crc值,执行s405,否则执行s406输出最终crc值。

76.s405,计数变量在子目标数据序列被输入计算后自动加一;继续执行s403。

77.具体实施过程中,crc并行迭代公式如下:

78.当前的crc值=crck(上一crc值,输入的子目标数据序列)^校正数值,该crc并行迭代公式包含三个输入参数:上一crc值、输入的子目标数据序列和校正数值。

79.其中,crck(上一crc值,输入的子目标数据序列)套用crck(a,b),crck表示不同的

crc算法,k表示crc算法的位宽,a为crck算法执行时参与运算的crc寄存器中的初始值,b为crck算法执行时的输入数据。本技术以可变的上一crc值取代crck算法执行时参与运算的crc寄存器中的初始值。

80.该crc并行迭代公式需要提供步骤s300中初始的crc值、子目标数据序列和校正数值才能够迭代运行。本技术在子目标数据序列输入crc并行迭代公式前,确定子目标数据序列中有效数据的宽度,根据有效数据的宽度选择对应的校正数值。

81.参阅图4所示,确定子目标数据序列中有效数据的宽度,根据有效数据的宽度选择对应的校正数值的过程包括:

82.在进行crc值计算过程中,如果目标数据序列的高位开始将子目标数据序列输入到并行运算模组中,那么输入的第一个子目标数据序列经历过补零,其有效数据的宽度不等于并行运算模组的宽度,剩余的子目标数据序列的有效数据宽度等于并行运算模组的宽度。因此,只需对第一个输入子目标数据序列进行有效数据宽度计算。

83.或如果目标数据序列的低位开始将子目标数据序列输入到并行运算模组中,那么输入的最后一个子目标数据序列经历过补零,其有效数据的宽度不等于并行运算模组的宽度,剩余的子目标数据序列的有效数据宽度等于并行运算模组的宽度。因此,只需对最后一个输入子目标数据序列进行有效数据宽度计算。

84.s4031,对子目标数据序列进行有效数据宽度计算,其过程包括:

85.a对于第一个输入或最后一个输入的子目标数据序列,获取数据序列的长度,数据序列的长度除以所述并行运算模组的宽度取余获取余数,计算余数的宽度,根据余数的宽度确定第一个输入或最后一个输入子目标数据序列中有效数据的宽度。

86.b对于除第一个输入子目标数据序列外的子目标数据序列或除最后一个输入子目标数据序列外的子目标数据序列,有效数据宽度等于并行运算模组位宽。

87.s4032,判断子目标数据序列的有效数据的宽度是否等于并行运算模组的宽度,

88.s4033,是则校正数值赋值为零,校正数值位数为k,

89.s4034,否则根据有效数据宽度和预先设置的校正数值计算规则获取对应的校正数值。

90.校正数值的计算方式:

91.下述过程采用的crc算法为crc

‑

ccitt(x^16 x^12 x^5 1),并行运算模组宽度为4字节,初始化的crc值为0xffff(位数对应k值16),以lfsr_q[p]表示上一crc值的某一位,p为数值;以lfsr_cu[q],表示当前crc值的某一位,u表示位数,q为数值;以data_in[w]表示输入子目标数据序列的某一位,w为数值。

[0092]

a:有效数据宽度为1字节时crc

‑

ccitt算法过程:

[0093]

lfsr_c8[0]=lfsr_q[8]^lfsr_q[12]^data_in[0]^data_in[4];

[0094]

lfsr_c8[1]=lfsr_q[9]^lfsr_q[13]^data_in[1]^data_in[5];

[0095]

lfsr_c8[2]=lfsr_q[10]^lfsr_q[14]^data_in[2]^data_in[6];

[0096]

lfsr_c8[3]=lfsr_q[11]^lfsr_q[15]^data_in[3]^data_in[7];

[0097]

lfsr_c8[4]=lfsr_q[12]^data_in[4];

[0098]

lfsr_c8[5]=lfsr_q[8]^lfsr_q[12]^lfsr_q[13]^data_in[0]^data_in[4]^data_in[5];

[0099]

lfsr_c8[6]=lfsr_q[9]^lfsr_q[13]^lfsr_q[14]^data_in[1]^data_in[5]^data_in[6];

[0100]

lfsr_c8[7]=lfsr_q[10]^lfsr_q[14]^lfsr_q[15]^data_in[2]^data_in[6]^data_in[7];

[0101]

lfsr_c8[8]=lfsr_q[0]^lfsr_q[11]^lfsr_q[15]^data_in[3]^data_in[7];

[0102]

lfsr_c8[9]=lfsr_q[1]^lfsr_q[12]^data_in[4];

[0103]

lfsr_c8[10]=lfsr_q[2]^lfsr_q[13]^data_in[5];

[0104]

lfsr_c8[11]=lfsr_q[3]^lfsr_q[14]^data_in[6];

[0105]

lfsr_c8[12]=lfsr_q[4]^lfsr_q[8]^lfsr_q[12]^lfsr_q[15]^data_in[0]^data_in[4]^data_in[7];

[0106]

lfsr_c8[13]=lfsr_q[5]^lfsr_q[9]^lfsr_q[13]^data_in[1]^data_in[5];

[0107]

lfsr_c8[14]=lfsr_q[6]^lfsr_q[10]^lfsr_q[14]^data_in[2]^data_in[6];

[0108]

lfsr_c8[15]=lfsr_q[7]^lfsr_q[11]^lfsr_q[15]^data_in[3]^data_in[7];

[0109]

有效数据宽度为4字节时crc

‑

ccitt算法过程:

[0110]

lfsr_c32[0]=lfsr_q[3]^lfsr_q[4]^lfsr_q[6]^lfsr_q[10]^lfsr_q[11]^lfsr_q[12]^data_in[0]^data_in[4]^data_in[8]^data_in[11]^data_in[12]^data_in[19]^data_in[20]^data_in[22]^data_in[26]^data_in[27]^data_in[28];

[0111]

lfsr_c32[1]=lfsr_q[4]^lfsr_q[5]^lfsr_q[7]^lfsr_q[11]^lfsr_q[12]^lfsr_q[13]^data_in[1]^data_in[5]^data_in[9]^data_in[12]^data_in[13]^data_in[20]^data_in[21]^data_in[23]^data_in[27]^data_in[28]^data_in[29];

[0112]

lfsr_c32[2]=lfsr_q[5]^lfsr_q[6]^lfsr_q[8]^lfsr_q[12]^lfsr_q[13]^lfsr_q[14]^data_in[2]^data_in[6]^data_in[10]^data_in[13]^data_in[14]^data_in[21]^data_in[22]^data_in[24]^data_in[28]^data_in[29]^data_in[30];

[0113]

lfsr_c32[3]=lfsr_q[6]^lfsr_q[7]^lfsr_q[9]^lfsr_q[13]^lfsr_q[14]^lfsr_q[15]^data_in[3]^data_in[7]^data_in[11]^data_in[14]^data_in[15]^data_in[22]^data_in[23]^data_in[25]^data_in[29]^data_in[30]^data_in[31];

[0114]

lfsr_c32[4]=lfsr_q[0]^lfsr_q[7]^lfsr_q[8]^lfsr_q[10]^lfsr_q[14]^lfsr_q[15]^data_in[4]^data_in[8]^data_in[12]^data_in[15]^data_in[16]^data_in[23]^data_in[24]^data_in[26]^data_in[30]^data_in[31];

[0115]

lfsr_c32[5]=lfsr_q[0]^lfsr_q[1]^lfsr_q[3]^lfsr_q[4]^lfsr_q[6]^lfsr_q[8]^lfsr_q[9]^lfsr_q[10]^lfsr_q[12]^lfsr_q[15]^data_in[0]^data_in[4]^data_in[5]^data_in[8]^data_in[9]^data_in[11]^data_in[12]^data_in[13]^data_in[16]^data_in[17]^data_in[19]^data_in[20]^data_in[22]^data_in[24]^data_in[25]^data_in[26]^data_in[28]^data_in[31];

[0116]

lfsr_c32[6]=lfsr_q[1]^lfsr_q[2]^lfsr_q[4]^lfsr_q[5]^lfsr_q[7]^lfsr_q[9]^lfsr_q[10]^lfsr_q[11]^lfsr_q[13]^data_in[1]^data_in[5]^data_in[6]^data_in[9]^data_in[10]^data_in[12]^data_in[13]^data_in[14]^data_in[17]^data_in[18]^data_in[20]^data_in[21]^data_in[23]^data_in[25]^data_in[26]^data_in[27]^data_in[29];

[0117]

lfsr_c32[7]=lfsr_q[2]^lfsr_q[3]^lfsr_q[5]^lfsr_q[6]^lfsr_q[8]^lfsr_q[10]^lfsr_q[11]^lfsr_q[12]^lfsr_q[14]^data_in[2]^data_in[6]^data_in[7]^data_in[10]^data_in[11]^data_in[13]^data_in[14]^data_in[15]^data_in[18]^data_in[19]^data_in[21]^data_in[22]^data_in[24]^data_in[26]^data_in[27]^data_in[28]^data_in[30];

[0118]

lfsr_c32[8]=lfsr_q[0]^lfsr_q[3]^lfsr_q[4]^lfsr_q[6]^lfsr_q[7]^lfsr_q[9]^lfsr_q[11]^lfsr_q[12]^lfsr_q[13]^lfsr_q[15]^data_in[3]^data_in[7]^data_in[8]^data_in[11]^data_in[12]^data_in[14]^data_in[15]^data_in[16]^data_in[19]^data_in[20]^data_in[22]^data_in[23]^data_in[25]^data_in[27]^data_in[28]^data_in[29]^data_in[31];

[0119]

lfsr_c32[9]=lfsr_q[0]^lfsr_q[1]^lfsr_q[4]^lfsr_q[5]^lfsr_q[7]^lfsr_q[8]^lfsr_q[10]^lfsr_q[12]^lfsr_q[13]^lfsr_q[14]^data_in[4]^data_in[8]^data_in[9]^data_in[12]^data_in[13]^data_in[15]^data_in[16]^data_in[17]^data_in[20]^data_in[21]^data_in[23]^data_in[24]^data_in[26]^data_in[28]^data_in[29]^data_in[30];

[0120]

lfsr_c32[10]=lfsr_q[0]^lfsr_q[1]^lfsr_q[2]^lfsr_q[5]^lfsr_q[6]^lfsr_q[8]^lfsr_q[9]^lfsr_q[11]^lfsr_q[13]^lfsr_q[14]^lfsr_q[15]^data_in[5]^data_in[9]^data_in[10]^data_in[13]^data_in[14]^data_in[16]^data_in[17]^data_in[18]^data_in[21]^data_in[22]^data_in[24]^data_in[25]^data_in[27]^data_in[29]^data_in[30]^data_in[31];

[0121]

lfsr_c32[11]=lfsr_q[1]^lfsr_q[2]^lfsr_q[3]^lfsr_q[6]^lfsr_q[7]^lfsr_q[9]^lfsr_q[10]^lfsr_q[12]^lfsr_q[14]^lfsr_q[15]^data_in[6]^data_in[10]^data_in[11]^data_in[14]^data_in[15]^data_in[17]^data_in[18]^data_in[19]^data_in[22]^data_in[23]^data_in[25]^data_in[26]^data_in[28]^data_in[30]^data_in[31];

[0122]

lfsr_c32[12]=lfsr_q[0]^lfsr_q[2]^lfsr_q[6]^lfsr_q[7]^lfsr_q[8]^lfsr_q[12]^lfsr_q[13]^lfsr_q[15]^data_in[0]^data_in[4]^data_in[7]^data_in[8]^data_in[15]^data_in[16]^data_in[18]^data_in[22]^data_in[23]^data_in[24]^data_in[28]^data_in[29]^data_in[31];

[0123]

lfsr_c32[13]=lfsr_q[0]^lfsr_q[1]^lfsr_q[3]^lfsr_q[7]^lfsr_q[8]^lfsr_q[9]^lfsr_q[13]^lfsr_q[14]^data_in[1]^data_in[5]^data_in[8]^data_in[9]^data_in[16]^data_in[17]^data_in[19]^data_in[23]^data_in[24]^data_in[25]^data_in[29]^data_in[30];

[0124]

lfsr_c32[14]=lfsr_q[1]^lfsr_q[2]^lfsr_q[4]^lfsr_q[8]^lfsr_q[9]^lfsr_q[10]^lfsr_q[14]^lfsr_q[15]^data_in[2]^data_in[6]^data_in[9]^data_in[10]^data_in[17]^data_in[18]^data_in[20]^data_in[24]^data_in[25]^data_in[26]^data_in[30]^data_in[31];

[0125]

lfsr_c32[15]=lfsr_q[2]^lfsr_q[3]^lfsr_q[5]^lfsr_q[9]^lfsr_q[10]^lfsr_q[11]^lfsr_q[15]^data_in[3]^data_in[7]^data_in[10]^data_in[11]^data_in[18]^data_in[19]^data_in[21]^data_in[25]^data_in[26]^data_in[27]^data_in[31]。

[0126]

b:crc值初始为0xffff,代入1字节0比特位和4比特位可得:

[0127]

lfsr_c8[0]=0^data_in[0]^data_in[4];

[0128]

lfsr_c8[4]=1^data_in[4]。

[0129]

crc值初始为0xffff,代入4字节0比特位和4比特位可得:

[0130]

lfsr_c32[0]=0^data_in[0]^data_in[4]^data_in[8]^data_in[11]^data_in[12]^data_in[19]^data_in[20]^data_in[22]^data_in[26]^data_in[27]^data_in[28];

[0131]

lfsr_c32[4]=0^data_in[4]^data_in[8]^data_in[12]^data_in[15]^data_in[16]^data_in[23]^data_in[24]^data_in[26]^data_in[30]^data_in[31]。

[0132]

c:子目标数据序列0x000000aa的代入0比特位和4比特位可得:

[0133]

lfsr_c8[0]=0^data_in[0]^data_in[4];

[0134]

lfsr_c8[4]=1^data_in[4];

[0135]

lfsr_c32[0]=0^data_in[0]^data_in[4];

[0136]

lfsr_c32[4]=0^data_in[4];

[0137]

d:依据c的结果可得到:

[0138]

lfsr_c8[0]=lfsr_c32[0];

[0139]

lfsr_c8[4]=lfsr_c32[4]^1;

[0140]

整理可得到,若子目标数据序列的有效数据为1字节,lfsr_c8=lfsr_c32^0x6530。0x6530即为1字节有效数据的校正数值。

[0141]

同理可得:lfsr_c16=lfsr_c32^0x99cf。0x99cf是子目标数据序列的有效数据为2字节时的校正数值。

[0142]

lfsr_c24=lfsr_c32^0x485c。0x485c是子目标数据序列的有效数据为3字节时的校正数值。

[0143]

同理对于固定位宽为其他字节的并行运算模组,可以计算少于并行运算模组位宽的有效数据的crc值与并行运算模组位宽的有效数据的crc值之间的异或转换数值作为相应的校正数值。

[0144]

具体实施过程中,配置的校正数值计算规则确定了不同crc算法下,有效数据宽度与校正数值之间的映射关系。

[0145]

实施例2

[0146]

参阅图5所示,本实施例提供一种计算任意数据的crc值装置,包括数据序列参数处理模块,所述数据序列参数处理模块用于获取数据序列的长度,并用数据序列的长度除以并行运算模组的宽度获取并保存商和余数;

[0147]

补零模块,所述补零模块用于从所述数据序列参数处理模块获取余数并利用余数计算补零数量,根据补零数量在数据序列高位进行补零,生成目标数据序列保存;

[0148]

分组模块,所述分组模块用于根据并行运算模组的宽度对补零模块生成的目标数据序列进行分组为若干子目标数据序列;

[0149]

校正数值计算模块,所述校正数值计算模块配置实现校正数值计算规则,根据子目标数据序列的有效数据宽度选择相应的校正数值计算规则来计算校正数值;

[0150]

crc计算模块,所述crc计算模块包含并行运算模组,所述并行运算模组用于实现crc并行迭代公式;

[0151]

crc计算模块用于从所述数据序列参数处理模块获取商和余数,根据商和余数确定目标数据所分的子目标数据序列的数量,利用子目标数据序列的数量控制所述crc并行迭代公式的迭代过程;crc计算模块根据子目标数据序列的有效数据宽度确定crc并行迭代公式的校正数值;crc计算模块从分组模块获取子目标数据序列;将校正数值、子目标数据序列和crc并行迭代公式计算的crc值代入crc并行迭代公式迭代计算出最终的crc值。

[0152]

具体实施过程中,计算任意数据的crc值装置还包括数据帧解析模块,所述数据帧解析模块用于解析数据包获取数据包中的数据序列,数据包中的校验序列以及数据序列的长度;

[0153]

判断模块,所述判断模块比较所述校验序列和所述crc计算模块计算的crc值是否相同,否则生成提示数据序列发生错误的信息。

[0154]

本技术采用并行的crc计算方法,crc计算速度快;本技术采用一个固定位数的并行运算模块计算实现任意位宽的crc算法,使得crc计算过程中,数据序列的长度不在受限于是crc算法位宽的整数倍。从而能够实现任意长度数据序列的crc值计算。与实现任意长度数据序列crc值计算的现有技术,本技术仅仅采用一个固定位数的并行运算模块即可实现,相比采用若干并行计算模块的现有技术能够节约硬件资源。由于本技术硬件资源占用少,因此能够应用在逻辑电路相对简单的处理器中,实现高速并行计算任意长度数据序列的crc值,可以有效的降低处理器成本。

[0155]

在本发明所提供的实施例中,应该理解到,所揭露的装置和方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

[0156]

所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

[0157]

另外,在本发明各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

[0158]

以上所述仅是本发明的具体实施方式,使本领域技术人员能够理解或实现本发明。对这些实施例的多种修改对本领域的技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所申请的原理和新颖特点相一致的最宽的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。