1.本发明涉及高频模拟集成电路设计技术,尤其涉及一种应用于高频锁相环中的频率检测。

背景技术:

2.鉴频器电路(frequency detector)通常与鉴相器电路(phase detector pd)一起构成模拟及数字锁相环电路的核心器件,是高速通信收发系统中重要的组成部分。通过在锁相环(pll)反馈系统中感知振荡电路输出信号的边沿,通过检测振荡电路输出信号边沿与基准时钟信号边沿间的时间差值,产生脉冲信号,通过脉冲信号的宽度调节振荡电路的起振频率,使振荡电路的起振频率与基准时钟频率的某一个倍数相同。从而实现锁相环电路的频率及相位锁定。其整体电路框图如图1所示,鉴频器的输入信号为输入数据或基准时钟信号din及压控振荡电路的输出信号do,通过鉴频器将din,do信号间的上升沿时间差转换为脉冲信号,该信号控制电荷泵实现电荷的输出与流入,实现电压/电流转换,再通过低通滤波器进行滤波及降噪后作为压控振荡电路的控制信号调节do的频率及相位。在高速(20gbps)时钟与数据恢复电路中,当输入数据din含有较大抖动时,造成鉴频器的检测错误,从而无法实现频率锁定。

技术实现要素:

3.本发明所要解决的主要技术问题是提供一种抗抖动的高速鉴频器电路,解决了输入数据din含有较大抖动导鉴频器检测错误,无法进行频率锁定的问题。

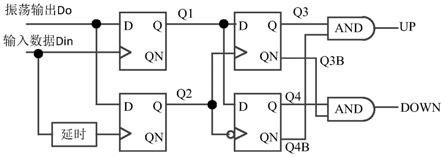

4.为了解决上述的技术问题,本发明提供了一种抗抖动的高速鉴频器电路,由四个d触发器、一个延时电路、2个与门构成;

5.q1、q2、q3、q4分别为四个d触发器1、2、3、4的正相输出,q3b、q4b为第三d触发器和第四d触发器的反相输出;q3和q3b连接至第一与门的两个输入端,q4和q4b连接至第二与门的两个输入端;第一与门输出up信号,第二与门输出down信号;第一d触发器两个输入端分别连接输入数据din和振荡输出do,第二d触发器第一输入端连接振荡输出do,第二输入端通过延时模块连接输入数据din;第三d触发器、第四d触发器的第一输入端分别连接至q1;第三d触发器、第四d触发器的第二输入端分别连接至q2;

6.当输入数据din的频率高于振荡输出do频率时,up信号为高电平,电荷泵向滤波器提供电流,滤波器输出电压升高,提高振荡电路输出频率;当输入数据din频率低于振荡输出do频率时,down信号为高电平,滤波器向电荷泵提供电流,滤波器输出电压降低,降低振荡电路输出频率。

7.在一较佳实施例中:所述up信号和down信号不总是处于相反状态。

8.在一较佳实施例中:当输入数据din含有较大抖动时,up信号及down信号同时处于低电平状态。

附图说明

9.图1为现有技术中包含鉴相器与鉴频器的pll电路框图;

10.图2为本发明优选实施例中抗抖动高速鉴频器的电路图;

11.图3为本发明优选实施例的信号时序图,其中a为输入数据din含有较大抖动的时序图;b为输入数据没有含有较大抖动的时序图;

12.图4为本发明优选实施例的仿真结果图。

具体实施方式

13.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述;显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例,基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

14.在本发明的描述中,需要说明的是,术语“上”、“下”、“内”、“外”、“顶/底端”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性。

15.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“设置有”、“套设/接”、“连接”等,应做广义理解,例如“连接”,可以是壁挂连接,也可以是可拆卸连接,或一体地连接,可以是机械连接,也可以是电连接,可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通,对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

16.参考图2,本实施例提供了一种抗抖动的高速鉴频器电路,由四个d触发器、一个延时电路、2个与门构成;

17.q1、q2、q3、q4分别为四个d触发器1、2、3、4的正相输出,q3b、q4b为第三d触发器和第四d触发器的反相输出;q3和q3b连接至第一与门的两个输入端,q4和q4b连接至第二与门的两个输入端;第一与门输出up信号,第二与门输出down信号;第一d触发器两个输入端分别连接输入数据din和振荡输出do,第二d触发器第一输入端连接振荡输出do,第二输入端通过延时模块连接输入数据din;第三d触发器、第四d触发器的第一输入端分别连接至q1;第三d触发器、第四d触发器的第二输入端分别连接至q2;

18.当输入数据din的频率高于振荡输出do频率时,up信号为高电平,电荷泵向滤波器提供电流,滤波器输出电压升高,提高振荡电路输出频率;当输入数据din频率低于振荡输出do频率时,down信号为高电平,滤波器向电荷泵提供电流,滤波器输出电压降低,降低振荡电路输出频率。

19.经过上述设计后,以输入数据din的频率高于振荡输出do频率为例,如图3所示,当输入数据din的上升沿和下降沿都含有较大抖动的场合,q3及q4b产生相反的信号使up,down信号均保持低电平,不进行充放电,避免了由于抖动造成的误判。当输入数据din的上升沿和下降沿都含有较小抖动的场合,q3及q4b能够进行较为明确的频率判别,up,down信号正常工作。图4为发明电路的仿真结果。

20.以上所述,仅为本发明较佳的具体实施方式,但本发明的设计构思并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,利用此构思对本发明进行非实质性的改动,均属于侵犯本发明保护范围的行为。

技术特征:

1.一种抗抖动的高速鉴频器电路,其特征在于:由四个d触发器、一个延时电路、2个与门构成;q1、q2、q3、q4分别为四个d触发器1、2、3、4的正相输出,q3b、q4b为第三d触发器和第四d触发器的反相输出;q3和q3b连接至第一与门的两个输入端,q4和q4b连接至第二与门的两个输入端;第一与门输出up信号,第二与门输出down信号;第一d触发器两个输入端分别连接输入数据din和振荡输出do,第二d触发器第一输入端连接振荡输出do,第二输入端通过延时模块连接输入数据din;第三d触发器、第四d触发器的第一输入端分别连接至q1;第三d触发器、第四d触发器的第二输入端分别连接至q2;当输入数据din的频率高于振荡输出do频率时,up信号为高电平,电荷泵向滤波器提供电流,滤波器输出电压升高,提高振荡电路输出频率;当输入数据din频率低于振荡输出do频率时,down信号为高电平,滤波器向电荷泵提供电流,滤波器输出电压降低,降低振荡电路输出频率。2.根据权利要求1所述的一种抗抖动的高速鉴频器电路,其特征在于:所述up信号和down信号不总是处于相反状态。3.根据权利要求1所述的一种抗抖动的高速鉴频器电路,其特征在于:当输入数据din含有较大抖动时,up信号及down信号同时处于低电平状态。

技术总结

本发明提供了一种抗抖动的高速鉴频器电路,Q1、Q2、Q3、Q4分别为四个D触发器1、2、3、4的正相输出,Q3B、Q4B为第三D触发器和第四D触发器的反相输出;Q3和Q3B连接至第一与门的两个输入端,Q4和Q4B连接至第二与门的两个输入端;第一与门输出UP信号,第二与门输出DOWN信号;第一D触发器两个输入端分别连接输入数据D i n和振荡输出Do,第二D触发器第一输入端连接振荡输出Do,第二输入端通过延时模块连接输入数据D i n;第三D触发器、第四D触发器的第一输入端分别连接至Q1;第三D触发器、第四D触发器的第二输入端分别连接至Q2。第二输入端分别连接至Q2。第二输入端分别连接至Q2。

技术研发人员:林海军 杨骁

受保护的技术使用者:厦门市迅芯电子科技有限公司

技术研发日:2021.07.23

技术公布日:2021/11/4

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。