1.本发明涉及一种发光元件,且特别是涉及一种包含反射镜结构的倒装式发光元件。

背景技术:

2.发光二极管(light

‑

emitting diode,led)为固态半导体发光元件,其优点为功耗低,产生的热能低,工作寿命长,防震,体积小,反应速度快和具有良好的光电特性,例如稳定的发光波长。因此发光二极管被广泛应用于家用电器,设备指示灯,及光电产品等。

技术实现要素:

3.本发明的一目的为提供一发光元件以提高发光元件的光取出效率。

4.本发明的一目的为提供一发光元件以提高发光元件的结构的可靠性。

5.本发明的一目的为提供一发光元件以降低绝缘层破损而使元件失效的机率,提高电绝缘的可靠性。

6.为达成上述至少一目的,根据本发明的一实施例揭露一发光元件,包含一基板,包含一上表面及一侧边;一半导体叠层,位于基板的上表面上,包含一第一半导体层、一活性层及一第二半导体层;一切割道,环绕半导体叠层并露出基板的上表面;一保护层,覆盖半导体叠层及切割道;一反射层,包含一分布式布拉格反射镜结构,覆盖保护层;以及一包覆层,覆盖反射层,其中,反射层包含一不均匀部邻近基板的侧边,且不均匀部包含一不均匀的厚度。

附图说明

7.图1为本发明一实施例所揭示的一发光元件1的上视图;

8.图2为沿着图1的切线a

‑

a’的发光元件1的剖视图;

9.图3为图1的发光元件1的位置c的部分剖视图;

10.图4为图1的发光元件1的位置c的sem照片图;

11.图5a~图5f为本发明一实施例所揭示的发光元件1的制造方法的示意图;

12.图6为图1的位置d的sem照片图;

13.图7为本发明一实施例所揭示的一发光元件1g的上视图;

14.图8为沿着图7的切线y

‑

y’的发光元件1g的剖视图;

15.图9a为本发明的一实施例所揭示的自图7的x轴观之的发光元件1g的侧视图;

16.图9b为本发明的一实施例所揭示的自图7的y轴观之的发光元件1g的侧视图;

17.图9c为本发明的另一实施例所揭示的自图7的x轴观之的发光元件1g的侧视图;

18.图9d为本发明的另一实施例所揭示的自图7的y轴观之的发光元件1g的侧视图;

19.图10为图8的发光元件1g的位置ⅰ的部分剖视图;

20.图11为图8的发光元件1g的位置ⅰ的sem照片图;

21.图12为图8的发光元件1g的位置ⅱ的部分剖视图;

22.图13为图8的发光元件1g的位置ⅱ的sem照片图;

23.图14为本发明一实施例的发光装置2的示意图;

24.图15为本发明一实施例的发光装置3的示意图。

25.符号说明

26.1,1g 发光元件

27.10 基板

28.10d 切割道

29.10s 侧边

30.100 上表面

31.101 倾斜面

32.103 第一粗化部

33.104 第二粗化部

34.105 下表面

35.1000 孔隙

36.1000s 阻断面

37.1000v 凹部

38.1001 切割区域

39.11 凸部

40.20 半导体叠层

41.20s 侧边

42.20ts表面

43.211 第一半导体层

44.211a 台面

45.211b 第一电性接触区

46.212 活性层

47.213 第二半导体层

48.30 导电层

49.41 第一接触电极

50.41b 底部

51.41t 顶部

52.410 第一凹部

53.410s 侧壁

54.411 第一接合层

55.412 第一导电层

56.42 第二接触电极

57.42b 底部

58.42t 顶部

59.420 第二接触部

60.420s 侧壁

61.421 第二连接部

62.422 第二延伸部

63.423 第二接合层

64.424 第二导电层

65.425 第二凹部

66.50 保护层

67.500 绝缘反射结构

68.501 第一绝缘反射结构开口

69.501d 间距

70.501s 侧壁

71.502 第二绝缘反射结构开口

72.502d 间距

73.502s 侧壁

74.51 反射层

75.510 第一垫片

76.511 不均匀部

77.512 第二垫片

78.513 封装基板

79.515 断裂面

80.53 绝缘部

81.54 致密层

82.58 反射结构

83.61 第一电极垫

84.62 第二电极垫

85.602 灯罩

86.604 反射镜

87.606 承载部

88.608 发光体

89.610 发光模块

90.612 灯座

91.614 散热片

92.616 连接部

93.618 电连接元件

94.d1,d2,d3,d4 露出的基板宽度

95.e 长度

96.e1 第一侧

97.e2 第二侧

98.e3 第三侧

99.e4 第四侧

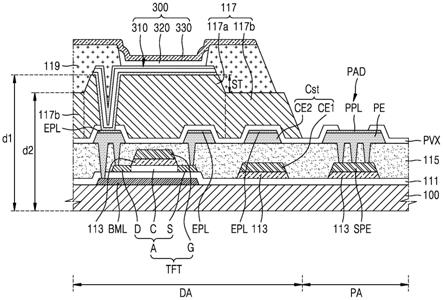

100.h1,h2 阶差

101.l1,l2 距离

102.p 连接部

103.p1,p3 侧面

104.s 距离

105.s1,s2,s3,s4 侧边

106.w1,w2 宽度

具体实施方式

107.为了使本发明的叙述更加详尽与完备,请参照下列实施例的描述并配合相关图示。但是,以下所示的实施例是用于例示本发明的发光元件,并非将本发明限定于以下的实施例。又,本说明书记载于实施例中的构成零件的尺寸、材质、形状、相对配置等在没有限定的记载下,本发明的范围并非限定于此,而仅是单纯的说明而已。且各图示所示构件的大小或位置关系等,会由于为了明确说明有加以夸大的情形。更且,在以下的描述中,为了适切省略详细说明,对于同一或同性质的构件用同一名称、符号显示。

108.图1是本发明一实施例所揭示的包含多个发光元件1的一晶片的上视图。图2是沿着图1的切线a

‑

a’的发光元件1的剖视图。

109.如图2所示,一发光元件1,包含一基板10,包含一上表面100及一侧边10s;一半导体叠层20位于基板10的上表面100上,包含一第一半导体层211、一活性层212及一第二半导体层213;一切割道10d,环绕半导体叠层20并露出基板10的上表面100;一保护层50覆盖半导体叠层20及切割道10d;一反射层51,包含一分布式布拉格反射镜结构,位于保护层50之上;以及一包覆层52覆盖反射层51,其中,反射层51包含一不均匀部511邻近基板10的侧边10s,且不均匀部511包含一不均匀的厚度。

110.基板10可以为一成长基板以外延成长半导体叠层20。基板10包括用以外延成长磷化铝镓铟(algainp)的砷化镓(gaas)晶片,或用以成长氮化镓(gan)、氮化铟镓(ingan)或氮化铝镓(algan)的蓝宝石(al2o3)晶片、氮化镓(gan)晶片、碳化硅(sic)晶片、或氮化铝(aln)晶片。

111.基板10与半导体叠层20相接的一面可以为粗糙化的表面。粗糙化的表面可以为具有不规则形态的表面或具有规则形态的表面。例如,相对于上表面100,基板10包含一或多个凸部11凸出于上表面100,或是包含一或多个凹部(图未示)凹陷于上表面100。在一剖视图下,凸部11或凹部(图未示)可以为半球形状或者多边锥形状。为了增加发光元件的出光效率,基板10的凸部11包含一第一层及一第二层(图未示)。第一层包含与构成基板10相同的材料,例如砷化镓(gaas)、蓝宝石(al2o3)、氮化镓(gan)、碳化硅(sic)、或氮化铝(aln)。第二层包含与构成第一层、基板10不同的材料。第二层的材料包含绝缘材料,例如氧化硅、氮化硅或氮氧化硅。在一实施例中,第二层选择的材料折射率介于基板10和半导体叠层20的折射率之间。在一实施例中,切割道10d不包含凸部11或凹部。在一实施例中,在形成切割道10d时,基板10表面的凸部11或凹部可经由蚀刻去除,使得后续形成于切割道10d上的保护层50、反射层51、以及包覆层52覆盖反射层51能有较佳的披覆。蚀刻方式包含当凸部11材料

为和基板10相同为外延成长基板的材料时,可以干蚀刻或湿蚀刻方式去除凸部11。当凸部11材料为绝缘材料时,可以干蚀刻或湿蚀刻方式去除凸部11。干蚀刻包含例如等离子体蚀刻、激发态离子蚀刻、电感耦合等离子蚀刻或是增强型电容耦合等离子蚀刻。

112.在本发明的一实施例中,通过金属有机化学气相沉积法(mocvd)、分子束外延(mbe)、氢化物气相沉积法(hvpe)、物理气相沉积法(pvd)或离子电镀方法以于基板10上形成具有光电特性的半导体叠层20,例如发光(light

‑

emitting)叠层,其中物理气象沉积法包含溅镀(sputtering)或蒸镀(evaporation)法。

113.半导体叠层20包含第一半导体层211、第二半导体层213以及形成在第一半导体层211和第二半导体层213之间的活性层212。通过改变半导体叠层20中一层或多层的物理及化学组成以调整发光元件1发出光线的波长。半导体叠层20的材料包含ⅲ料包族半导体材料,例如al

x

in

y

ga

(1

‑

x

‑

y)

n或al

x

in

y

ga

(1

‑

x

‑

y)

p,其中0≤x,y≤1;(x y)≤1。当半导体叠层20的材料为alingap系列材料时,可发出波长介于610nm及650nm之间的红光,或波长介于530nm及570nm之间的绿光。当半导体叠层20的材料为ingan系列材料时,可发出波长介于400nm及490nm之间的蓝光,或波长介于530nm及570nm之间的绿光。当半导体叠层20的材料为algan系列或alingan系列材料时,可发出波长介于250nm及400nm之间的紫外光。

114.第一半导体层211和第二半导体层213可为包覆层(cladding layer),两者具有不同的导电型态、电性、极性,或依掺杂的元素以提供电子或空穴,例如第一半导体层211为n型电性的半导体,第二半导体层213为p型电性的半导体。活性层212形成在第一半导体层211和第二半导体层213之间,电子与空穴于一电流驱动下在活性层212复合,将电能转换成光能,以发出一光线。活性层212可为单异质结构(single heterostructure,sh),双异质结构(double heterostructure,dh),双侧双异质结构(double

‑

side double heterostructure,ddh),或是多层量子阱结构(multi

‑

quantum well,mqw)。活性层212的材料可为中性、p型或n型电性的半导体。第一半导体层211、第二半导体层213、或活性层212可为一单层或包含多个子层的结构。

115.在本发明的一实施例中,半导体叠层20还可包含一缓冲层(图未示)位于第一半导体层211和基板10之间,用以释放基板10和半导体叠层20之间因材料晶格不匹配而产生的应力,以减少差排及晶格缺陷,进而提升外延品质。缓冲层可为一单层或包含多个子层的结构。在一实施例中,可选用pvd氮化铝(aln)作为缓冲层,形成于半导体叠层20及基板10之间,用以改善半导体叠层20的外延品质。在一实施例中,用以形成pvd氮化铝(aln)的靶材由氮化铝所组成。在另一实施例中,可使用由铝组成的靶材,在氮源的环境下与铝靶材反应性地形成氮化铝。

116.在本发明的一实施例中,发光元件1包含一第一接触电极41及一第二接触电极42形成于半导体叠层20的同一侧。发光元件1可以为倒装芯片(flip chip)结构或是正装的水平芯片(lateral chip)结构。

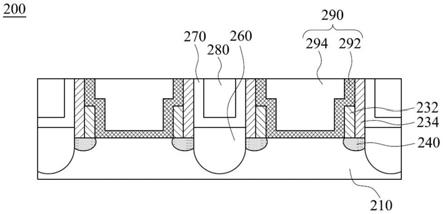

117.在本实施例中,通过移除部分的第二半导体层213及活性层212以露出第一半导体层211,形成一台面211a以及一或多个第一电性接触区211b。被蚀刻而露出的第二半导体层213及活性层212的侧面相对于露出的第一半导体层211是倾斜面。第一接触电极41形成于第一电性接触区211b上以接触第一半导体层211,并和第一半导体层211形成电连接。第二接触电极42形成于第二半导体层213上,并和第二半导体层213形成电连接。

118.在本发明的一实施例中,为了减少接触电阻并提高电流扩散的效率,发光元件1包含一导电层30位于第二半导体层213和第二接触电极42之间。导电层30的材料包含对于活性层212所发出的光线为透明的材料,例如具有小于500埃厚度的金属材料或透明导电氧化物。透明导电氧化物包含氧化铟锡(ito)或氧化铟锌(izo)。

119.在本发明的一实施例中,发光元件1包含一或多个电流局限层(图未示)位于第二半导体层213与导电层30之间,并位于第二接触电极42的下方。电流局限层为非导电材料所形成,包含氧化铝(al2o3)、氮化硅(sin

x

)、氧化硅(sio

x

)、氧化钛(tio

x

),或氟化镁(mgf

x

)。在一变化例中,电流局限层可以包括分布式布拉格反射器(dbr),其中分布式布拉格反射器由不同折射率的绝缘材料堆叠而成。为了增加发光元件的光取出效率,电流局限层对于活性层212所发出的光线具有80%以上的光反射率。

120.一绝缘反射结构500覆盖半导体叠层20、第一接触电极41及第二接触电极42,以将来自活性层212的光反射至基板10的一侧,例如基板10的下表面105。在本实施例中,为了减少金属反射膜对光线的吸收,绝缘反射结构500包含绝缘性材料。绝缘反射结构500可形成为单层或是多层,但优选为多层结构。具体而言,绝缘反射结构500的结构由保护层50,反射层51及/或包覆层52依序堆叠而成,其中反射层51包含分布式布拉格反射镜(distributed bragg reflector,dbr)结构。

121.在发明的一变化例中,保护层50,反射层51及包覆层52中的一个以上可以被省略。换言之,绝缘反射结构500的结构可包含保护层50,反射层51及包覆层52中的任一层或是任二层。

122.在发明的一变化例中,保护层50及包覆层52中的一个以上可以包含多层膜。优选的,包覆层52包含一氧化硅膜与反射层51相接,以及一氮化硅膜位于氧化硅膜之上。

123.绝缘反射结构500包含一第一绝缘反射结构开口501以露出第一接触电极41,以及一第二绝缘反射结构开口502以露出第二接触电极42。一第一电极垫61覆盖第一绝缘反射结构开口501以接触第一接触电极41,并与第一半导体层211形成电性连接。一第二电极垫62覆盖第二绝缘反射结构开口502以接触第二接触电极42,并与第二半导体层213形成电性连接。

124.在发明的一变化例中,第一接触电极41及第二接触电极42中的一个以上可以被省略。第一绝缘反射结构开口501露出第一半导体层211及/或第二绝缘反射结构开口502露出导电层30。第一电极垫61覆盖第一绝缘反射结构开口501以接触第一半导体层211,及/或第二电极垫62覆盖第二绝缘反射结构开口502以接触导电层30。

125.第一接触电极41,第二接触电极42,第一电极垫61及第二电极垫62包含金属材料,例如铬(cr)、钛(ti)、钨(w)、金(au)、铝(al)、铟(in)、锡(sn)、镍(ni)、铂(pt)、银(ag)等金属或上述材料的合金。第一电极垫61及第二电极垫62可由单个层或是多个层所组成。例如,第一电极垫61或第二电极垫62可包括al/pt层、ti/au层、ti/pt/au层、cr/au层、cr/pt/au层、ni/au层、ni/pt/au层、cr/al/ti/pt层、ti/al/ti/pt/ni/pt层、cr/al/ti/al/ni/pt/au层、cr/al/cr/ni/au层或ag/niti/tiw/pt层。第一电极垫61及第二电极垫62可作为外部电源供电至第一半导体层211及第二半导体层213的电流路径。在第一电极垫61及第二电极垫62包含多个层的实施例中,第一电极垫61及第二电极垫62与外部电源相接的金属结构可以由金(au)和锡(sn)或锡(sn)和银(ag)多层交叠而成,或是由金(au)作为第一电极垫61及第

二电极垫62的最外层金属层,其中金(au)或银(ag)的厚度或组成比是锡(sn)的0.25%~2.25%。第一接触电极41,第二接触电极42,第一电极垫61及/或第二电极垫62包含一厚度介于1~100μm之间,较佳为1.2~60μm之间,更佳为1.5~6μm之间。在一实施例中,第一电极垫61及/或第二电极垫62包含锡(sn)的金属层具有一厚度介于3.5~8.5μm之间。在一实施例中,第一电极垫61及/或第二电极垫62包含锡银(snag)的金属层具有一厚度介于8~10μm之间。

126.如上所述,因绝缘反射结构500覆盖于半导体叠层20、第一接触电极41及第二接触电极42等凹凸结构上,半导体叠层20、第一接触电极41及第二接触电极42之间的高度差会影响绝缘反射结构500的镀膜品质。例如,当绝缘反射结构500覆盖于半导体叠层20上时,在半导体叠层20的侧表面与基板10的上表面100的相接处,一断裂面(图未示)容易形成于绝缘反射结构500中,外部水气易沿着断裂面侵入半导体叠层20而降低元件的可靠性。

127.为了改善上述断裂面的问题,在本实施例中,利用化学气相沉积(cvd)具有较佳披覆性的镀膜特性,优选地,通过化学气相沉积(chemical vapor deposition,cvd),更佳地,通过等离子体辅助化学气相沉积(plasma enhanced chemical vapor deposition,pecvd)来形成保护层50及包覆层52。

128.在发明的一变化例中,保护层50及包覆层52的其中一个以上可通过原子气相沉积形成。

129.保护层50的材料包含氧化硅,优选的具有0.2μm~2μm的厚度。如果保护层50的厚度小于0.2μm,保护层50无法完全包覆第一接触电极41及第二接触电极42。如果保护层50的厚度大于2μm,在形成第一绝缘反射结构开口501及第二绝缘反射结构开口502时,会增加制作工艺的时间与成本。

130.包覆层52的材料包含金属氧化物,例如al2o3,或是氮化物、氧化物、氮氧化物,例如sin,sio

x

或sio

x

n

y

。在发明的一变化例中,包覆层52可通过上述材料形成单层结构或通过上述材料的组合而形成多层结构。包覆层52优选的具有0.5μm~2.5μm的厚度。

131.反射层51形成在保护层50及包覆层52之间。反射层51包含不同折射率的两种以上的材料交替堆叠以形成一分布式布拉格反射镜(dbr)结构,选择性地反射特定波长的光。例如,可通过层叠sio2/tio2或sio2/nb2o5等层来形成高反射率的绝缘反射结构。当sio2/tio2或sio2/nb2o5形成分布式布拉格反射镜(dbr)结构时,分布式布拉格反射镜(dbr)结构的每一个层被设计成活性层212发出的光的波长的四分之一的光学厚度的一或整数倍。分布式布拉格反射镜(dbr)结构的每一个层的厚度在λ/4的一或整数倍的基础上可具有

±

30%的偏差。由于分布式布拉格反射镜(dbr)结构的每一个层的厚度会影响到反射率,因此优选地利用电子束蒸镀(e

‑

beam evaporation)来形成反射层51以稳定的控制分布式布拉格反射镜(dbr)结构的每一个层的厚度。

132.图1为形成有多个发光元件1的晶片的示意图。通过激光及/或刀具划割切割区域1001,将形成有多个发光元件1的晶片分离成单独的发光元件1时,激光及/或刀具划割的物理性冲击力容易在发光元件1边缘的绝缘反射结构500中产生裂痕,特别是反射层51。并且,一旦裂痕扩散到半导体叠层20,外部水气易沿着裂痕侵入半导体叠层20内部而降低元件的可靠性。

133.为了解决上述的问题,发光元件1包含切割道10d,切割道10d是晶片切割时的切割

区域1001的一部分。切割道10d是切割区域1001在晶片切割制作工艺后,在发光元件1上保留下来的区域。切割道10d位于基板10的侧边10s与半导体叠层20的一侧边20s之间,且切割道10d包含一宽度介于0.1μm~50μm之间,较佳小于30μm,更佳小于15μm。切割道10d露出基板10的上表面100,并位于发光元件1的周围以环绕半导体叠层20。在本实施例中,位于切割道10d的基板10还包含一倾斜面101连接至基板10的上表面100。相较于倾斜面101,上表面100大致为一水平面。自发光元件1的一上视图观之,切割道10d包含一第一表面积,半导体叠层20包含一第二表面积,且第一表面积与第二表面积的一比值介于10~50%之间。自发光元件1的侧视图观之,如图2所示,位于切割道10d上的绝缘反射结构500直接接触基板10的上表面100。

134.在一变化例中,为了使台面211a保留较多的面积,用以放置第一电极垫61及第二电极垫62,半导体叠层20的侧边20s与基板10的上表面100之间包含一角度介于70度~110度之间,较佳介于80度~100度之间,更佳介于85度~95度之间。

135.在一变化例中,为了改善反射层51披覆于半导体叠层20的侧边20s的膜质,避免反射层51产生龟裂的缺陷,半导体叠层20的侧边20s与基板10的上表面100之间包含一角度介于10度~50度之间,较佳介于20度~40度之间,更佳介于25度~35度之间。在另一变化例中,侧边20s可由具有不同斜率的斜面所构成。靠近基板10的上表面100的斜面比远离基板10的上表面100的斜面陡峭。例如,直接接触基板10的上表面100的斜面与基板10的上表面100之间包含一角度介于50度~70度之间。较远离于基板10的上表面100的斜面与平行于上表面100的一水平面之间包含一角度介于30度~50度。

136.在本实施例中,如图2所示,保护层50覆盖基板10的倾斜面101。反射层51包含不均匀部511。不均匀部511是全部或部分覆盖基板10的倾斜面101。不均匀部511包含多个膜层,且多个膜层之一的末端包含一楔形。多个膜层之一的末端包含一厚度于朝向基板10的一方向上渐减。保护层50及/或包覆层52的一末端包含一楔形,保护层50及/或包覆层52的一末端的一厚度于朝向基板10的一方向上渐减。

137.图3是图1的发光元件1的位置c的部分剖视图。图4是图1的发光元件1的位置c及图3的sem照片图。如图2、图3及图4所示,基板包含一第一粗化部103位于基板10的多个侧边10s上。基板可选择性包含一第二粗化部104位于基板10的倾斜面101上,并远离第一粗化部103。

138.在发明的一实施例中,如图2及图3所示,在形成绝缘反射结构500之前,通过原子气相沉积法于基板10的上表面100及半导体叠层20的一表面20ts上形成一致密层54以直接披覆基板10的上表面100及半导体叠层20的表面20ts。致密层54的材料包含氧化硅、氧化铝、氧化铪、氧化锆、氧化钇、氧化镧、氧化钽、氮化硅、氮化铝或氮氧化硅。在本实施例中,致密层54与半导体叠层20相接的介面包含金属元素及氧,其中金属元素包含铝、铪、锆、钇、镧或钽。致密层54包含一厚度介于之间,较佳介于之间,更佳介于之间。

139.原子气相沉积法(atomic layer deposition)形成的膜具有良好的阶梯覆盖性和厚度均匀性,并且具有较高的致密度。利用此特性于基板10及半导体叠层20上共形的形成一无针孔的致密层54。利用原子气相沉积法(atomic layer deposition)形成的致密层54可以防止水气沿着基板10及半导体叠层20之间的间隙,或是半导体叠层20表面上的孔隙而

侵入半导体叠层20。

140.在发明的一变化例中(图未示),致密层54及保护层50可成对地叠层多次之后,再通过保护层50与反射层51相接。

141.图5a~图5f是本发明一实施例所揭示的发光元件1的制造方法。以下为方便说明,图5a~图5f是以沿着图1的切线a

‑

a’上的结构及位置d来说明,部分视图会适当省略。如图5a所示,提供一基板10,其包含一上表面100、一下表面105及多个凸部11凸出于上表面100。在基板10上形成缓冲层(图未示)以及半导体叠层20,其中半导体叠层20包含第一半导体层211、第二半导体层213、以及形成在第一半导体层211和第二半导体层213之间的活性层212。

142.如图5b所示,蚀刻移除半导体叠层20周边的部分第一半导体层211、第二半导体层213以及活性层212,形成一台面211a与一第一电性接触区211b以露出第一半导体层211,以及形成一切割区域1001以露出基板10。在本实施例中,在一上视图观之,如图1所示,切割区域1001将半导体叠层20划分成多个发光区域。台面211a连续地环绕各多个发光区域的半导体叠层20的周边,且大致为一四边形。为了将多个发光区域分离而形成单独的发光元件,切割区域1001需要一定的宽度以确保不会损伤到发光元件,同时保留足够的发光面积,较佳为介于1μm~150μm之间,更佳为介于5μm~50μm之间。

143.如图5c所示,在第一电性接触区211b上形成第一接触电极41。在第二半导体层213上形成导电层30及/或第二接触电极42。

144.如图5d所示,通过激光划切及/或蚀刻制作工艺在切割区域1001的基板10上形成具有一倾斜面101的凹部1000v。在一侧视图中,凹部1000v包含三角形、多边形或是不规则的形状。在一实施例中,通过激光划切及/或蚀刻制作工艺在切割区域1001的基板10上形成具有倾斜面101的凹部1000v的步骤,可提前至第一接触电极41及第二接触电极42形成步骤之前。

145.在发明的一实施例中,在形成凹部1000v的步骤前,先形成绝缘反射结构500。当基板10为蓝宝石基板时,可通过包含uv波长范围内的激光,例如,266纳米、343纳米、或355纳米,在切割区域1001上切割熔融绝缘反射结构500及基板10,形成具有倾斜面101的凹部1000v。经熔融后的基板10可能产生有残留物,残留物可能包含铝(al)、氧(o)、硅(si)、钛(ti)及/或碳(c)。在一实施例中,残留物附着于倾斜面101上。在本实施例中,经过激光熔融的倾斜面101包含一粗化表面。在通过激光划切形成凹部1000v的一例中,第二粗化部104形成于基板10的倾斜面101上。在一实施例中,残留物附着于具有第二粗化部104的倾斜面101上。

146.在发明的一实施例中,蚀刻制作工艺可以通过湿蚀刻来实施,蚀刻液包含盐酸(hcl)、硝酸(hno3)、氢氧化钾(koh)、硫酸(h2so4)、磷酸(h3po4)或上述溶液的组合。蚀刻制作工艺的温度约为200~300℃。在发明的另一实施例中,蚀刻制作工艺可以通过干蚀刻来实施,例如等离子体蚀刻、激发态离子蚀刻、电感耦合等离子蚀刻或是增强型电容耦合等离子蚀刻。在通过蚀刻形成凹部1000v的一例中,第二粗化部104形成于基板10的倾斜面101上。

147.接着在半导体叠层20、切割区域1001及凹部1000v上形成保护层50。保护层50的材料包含氧化铝(al2o3)、氮化硅(sin

x

)、氧化硅(sio

x

)或氮氧化硅(sio

x

n

y

)。保护层50优选地具有0.2μm~2μm之间的厚度。如果保护层50的厚度小于0.2μm,则其不足以完全覆盖半导体

叠层20及凹部1000v上具有高度差的结构。如果保护层50的厚度大于2μm,则可能增加后续图案化蚀刻制作工艺的时间。化学气相沉积(cvd)比电子束蒸镀(e

‑

beam evaporation)或物理气相沉积(physical vapor deposition)更容易覆盖具有高度差的结构。为了完全覆盖半导体叠层20及凹部1000v上具有高度差的结构,保护层50优选地通过化学气相沉积(chemical vapor deposition)来形成,更佳地通过等离子体辅助化学气相沉积(pecvd)来形成。

148.如图5e所示,在保护层50上形成反射层51。在本实施例中,反射层51包含不同折射率的两种以上的材料交替堆叠以形成一分布式布拉格反射镜(dbr)结构,选择性地反射特定波长的光。例如,可通过层叠sio2/tio2或sio2/nb2o5等层来形成高反射率的绝缘反射结构。当sio2/tio2或sio2/nb2o5形成分布式布拉格反射镜(dbr)结构时,分布式布拉格反射镜(dbr)结构的至少一个层被设计成具有特定波长的四分之一的一或整数倍的光学厚度、大于特定波长的四分之一的一或整数倍、或小于特定波长的四分之一的一或整数倍的光学厚度,并且sio2/tio2或sio2/nb2o5的对数优选地在4~30对之间。如果sio2/tio2或sio2/nb2o5的对数小于此范围,则分布式布拉格反射镜(dbr)结构的反射率会不佳;如果sio2/tio2或sio2/nb2o5的对数大于此范围,则分布式布拉格反射镜(dbr)结构的厚度会变得过厚。为了准确地控制分布式布拉格反射镜(dbr)结构的每一层的厚度,优选地,通过电子束蒸镀(e

‑

beam evaporation)来形成反射层51。在发明的一实施例中,反射层51优选地具有1μm~6μm之间的厚度,更佳具有2μm~4μm之间的厚度,例如3.5μm。

149.如图5e所示,由于电子束蒸镀(e

‑

beam evaporation)对于具有高度差的结构的覆盖性不佳,当反射层51通过电子束蒸镀(e

‑

beam evaporation)形成于切割区域1001上时,反射层51无法完全覆盖凹部1000v,因而在凹部1000v中形成一孔隙1000,以及沿线段x

‑

x’剖面的一阻断面1000s形成于孔隙1000上方的反射层51中。

150.为了保护反射层51的分布式布拉格反射镜(dbr)结构,并增加分布式布拉格反射镜(dbr)结构的反射率,在反射层51上形成包覆层52。为了实现增加反射率的效果,包覆层52的厚度优选地大于0.5μm,更佳地,包覆层52的厚度介于0.1~2.5μm之间,较佳介于0.2~2μm之间,更佳介于0.5~1.5μm之间。为了完全覆盖反射层51的表面,包覆层52优选地通过化学气相沉积(chemical vapor deposition)来形成,更佳地通过等离子体辅助化学气相沉积(pecvd)来形成。

151.将形成有多个发光元件的晶片分离成单独的各个发光元件时,可以使用激光及/或刀具划割,也可以单独以化学蚀刻制作工艺来完成或同时辅助激光及/或刀具划割。当使用激光来划割晶片时,可以使用隐形激光切割,从基板10内部来划割晶片,从而避免碎屑、半导体材料损失的问题。例如,在入射基板10的下表面105的一方向上,将激光的焦点聚焦于基板10的上表面100与下表面105之间,在基板10内沿着多个切割区域1001形成多个损伤区域,但是不损坏基板10的上表面100与下表面105。接着利用一物理冲击力,沿着多个损伤区域,向基板上、下表面的一延伸方向形成劈裂面。通过延伸的劈裂面以及反射层51的阻断面,将形成有多个发光元件1的晶片分离成单独的各个发光元件1。在分离后的发光元件侧边10s上,多个损伤区域处构成第一粗化部103。相较于直接用刀具划割,隐形激光切割减少切割道所需的宽度。

152.如图5e所示,通过微影、蚀刻制作工艺在保护层50、反射层51及包覆层52上形成第

一绝缘反射结构开口501以露出第一接触电极41,及第二绝缘反射结构开口502以露出一第二接触电极42。接续地,在第一绝缘反射结构开口501上形成第一电极垫61,以及在第二绝缘反射结构开口502上形成第二电极垫62。

153.图6是图1的位置d及第5e图的位置d所示结构的sem照片图。如图6所示,基板包含一或多个凸部11突出于基板10的上表面100。绝缘反射结构500,包含保护层50,反射层51及包覆层52。保护层50,反射层51及/或包覆层52包含一表面轮廓对应于基板10的多个凸部11。由于凸部11与基板10的上表面100之间的高度差,保护层50,反射层51及/或包覆层52,包含一断裂面515对应于基板10的凸部11的一与基板10的上表面100之间的一连接部p。

154.如图5e所示,沿着基板10的损伤区域,例如第一粗化部103,及沿线段x

‑

x’的反射层51的阻断面1000s,利用物理冲击力以划分基板10及绝缘反射结构500,形成图5f所示的多个发光元件1。如图5f所示,保护层50覆盖基板10的倾斜面101。反射层51包含不均匀部511。不均匀部511是全部或部分覆盖基板10的倾斜面101。不均匀部511包含多个膜层,且多个膜层之一的末端包含一楔形。多个膜层之一的末端包含一厚度于朝向基板10的一方向上渐减。保护层50及/或包覆层52的一末端包含一楔形,保护层50及/或包覆层52的一末端的一厚度于朝向基板10的一方向上渐减。

155.图7是本发明一实施例所揭示的一发光元件1g的上视图。图8是沿着图7的切线y

‑

y’的发光元件1g的剖视图。在本实施例中,发光元件1g与图1~图6的发光元件1具有相同名称、标号的构造,表示为相同的结构、具有相同的材料、或具有相同的功能,在此会适当省略说明或是不再赘述。

156.一发光元件1g,包含基板10,包含上表面100及侧边10s;半导体叠层20位于基板10的上表面100上,包含第一半导体层211、活性层212及第二半导体层213;切割道10d,环绕半导体叠层20并露出基板10的上表面100;导电层30位于第二半导体层213上;一电流阻挡层31位于导电层30及第二半导体层213之间;一绝缘反射结构500覆盖半导体叠层20及切割道10d,包含第一绝缘反射结构开口501以及第二绝缘反射结构开口502;第一电极垫61覆盖第一绝缘反射结构开口501以电连接至第一半导体层211;以及第二电极垫62覆盖第二绝缘反射结构开口502以电连接至第二半导体层213。

157.发光元件1g可以是如图7所示正方形或是具有一长边及一短边的长方形。发光元件1g的任一边至少大于50μm,但不超过260μm。于发光元件1g的最长边小于200μm的一例中,第一电极垫61及第二电极垫62之间的间距至少大于10μm,但不超过45μm。在发光元件1g的最长边大于200μm的一例中,第一电极垫61及第二电极垫62之间的间距至少大于50μm,但不超过150μm。

158.在发光元件1g的最长边大于200μm的一例中,发光元件1g还包含第一接触电极41位于第一半导体层211上,以及第二接触电极42位于导电层30上。在发光元件1g的最长边小于200μm的一例中,发光元件1g可以不包含第一接触电极41以及第二接触电极42。

159.第二接触电极42包含一第二接触部420,一第二连接部421,以及一或多个第二延伸部422自第二连接部421朝远离于第二接触部420的方向延伸。第二连接部421的一宽度w1大于或等于第二延伸部422的一宽度w2。多个第二延伸部422的尾端相隔一最短距离s。

160.第二连接部421的一长度e与最短距离s的比值为0.05~0.12。自发光元件1g的上视观之,第二连接部421与第二电极垫62的一最短距离l1可以小于或等于与第二连接部421

与第一电极垫61的一最短距离l2。

161.发光元件1g的厚度可介于50μm~110μm之间,较佳为70μm~90μm之间。如图7所示,在横向方向(x轴)上露出的基板宽度d3或d4与在纵向方向(y轴)上露出的基板宽度d1或d2可以相同或不同。露出的基板宽度d1,d2,d3或d4至少大于4μm,但不超过10μm。

162.图9a是本发明的一实施例所揭示的自图7的x轴观之的发光元件1g的侧视图。图9b是本发明的一实施例所揭示的自图7的y轴观之的发光元件1g的侧视图。在一实施例中,如图7及图9a所示,第一电极垫61及第二电极垫62分别靠近发光元件1g的第一侧e1及第二侧e2。自发光元件1g的第三侧e3或第四侧e4观之,基板10的侧面p3的两侧边s1,s2相对于基板10的下表面105是倾斜的。如图7及图9b所示,自发光元件1g的第一侧e1或第二侧e2观之,基板10的侧面p1的两侧s3,s4大致垂直于基板10的下表面105。侧面p1的晶格面可以是r面,侧面p3的晶格面可以是m面或a面。露出的基板宽度d1或d2大于露出的基板宽度d3或d4。由于r面是比较容易裂开的面,所以侧面p1可以仅包含一个第一粗化部103。由于m面或a面是比较不容易裂开的面,所以侧面p3可以包含多个第一粗化部103。亦即通过多次不同深度的隐形激光切割改善切割良率,对应多次不同深度的隐形激光切割形成多个第一粗化部103。

163.图9c是本发明的另一实施例所揭示的自图7的x轴观之的发光元件1g的侧视图。图9d是本发明的另一实施例所揭示的自图7的y轴观之的发光元件1g的侧视图。在另一实施例中,如图7及图9c所示,自发光元件1g的第三侧e3或第四侧e4观之,基板10的侧面p3的两侧边s1,s2大致垂直于基板10的下表面105。如图7及图9d所示,自发光元件1g的第一侧e1或第二侧e2观之,基板10的侧面p1的两侧边s3,s4相对于基板10的下表面105是倾斜的。侧面p1的晶格面可以是m面或a面,侧面p3的晶格面可以是r面。露出的基板宽度d1或d2小于露出的基板宽度d3或d4。由于r面是比较容易裂开的面,所以侧面p3可以仅包含一个第一粗化部103。由于m面或a面是比较不容易裂开的面,所以侧面p1可以包含多个第一粗化部103。

164.在发明的一实施例中,发光元件1g的任一长边与任一短边的长度比值超过2时,例如,第三侧e3为长边,第一侧e1为短边,第三侧e3与第一侧e1的e3/e1长度比值大于2时,基板10的第三侧e3所露出来的晶格面是r面,基板10的第一侧e1所露出来的晶格面是m面或a面。

165.图10是图8的发光元件1g的位置ⅰ的部分剖视图。图11是图8的发光元件1g的位置ⅰ的sem照片图。为了提高绝缘反射结构500,例如sio2膜与第一接触电极41的黏合性,第一接触电极41包含一第一接合层411以及一第一导电层412。在蚀刻形成第一绝缘反射结构开口501时,部分的第一接触电极41会被移除而形成一第一凹部410。在一实施例中,第一凹部410形成于第一接合层411中。第一凹部410的一底部41b与第一接触电极41的一顶部41t之间具有一阶差h1。阶差h1介于20nm~200nm之间,优选的介于50nm~150nm之间,更佳为介于80nm~100nm之间。绝缘反射结构500的一侧壁501s与第一凹部410的一侧壁410s之间可以是连续性地相连接或是具有一最小间距501d。最小间距501d介于5nm~100nm之间,优选的介于10nm~50nm之间,更佳为介于20nm~30nm之间。

166.图12是图8的发光元件1g的位置ⅱ的部分剖视图。图13是图8的发光元件1g的位置ⅱ的sem照片图。为了提高绝缘反射结构500,例如sio2膜与第二接触电极42的黏着合性,第二接触电极42包含一第二接合层423以及一第二导电层424。于蚀刻形成第二绝缘反射结构开口502时,部分的第二接触电极42会被移除而形成一第二凹部425。在一实施例中,第二凹

部425形成于第二接合层423中。第二凹部425的一底部42b与第二接触电极42的一顶部42t之间具有一阶差h2。阶差h2介于20nm~200nm之间,优选的介于50nm~150nm之间,更佳为介于80nm~100nm之间。绝缘反射结构500的一侧壁502s与第二凹部425的一侧壁420s之间可以是连续性地相连接或是具有一最小间距502d。最小间距502d介于5nm~100nm之间,优选的介于10nm~50nm之间,更佳为介于20nm~30nm之间。

167.第一接合层411及第二接合层423包含钛(ti)、金(au)、镍(ni)、铂(pt)等金属或上述材料的合金。第一导电层412及第二导电层424包含铬(cr)、钛(ti)、钨(w)、金(au)、铝(al)、铟(in)、锡(sn)、铂(pt)、镍(ni)、银(ag)等金属或上述材料的合金。

168.图14为依本发明一实施例的发光装置2的示意图。将前述实施例中的发光元件1或1g以倒装芯片的形式安装于封装基板513的第一垫片511、第二垫片512上。第一垫片511、第二垫片512之间通过一包含绝缘材料的绝缘部53做电性绝缘。倒装芯片安装是将与电极垫形成面相对的成长基板侧向上设为主要的光取出面。为了增加发光装置2的光取出效率,可于发光元件1或1g的周围设置一反射结构58。

169.图15为依本发明一实施例的发光装置3的示意图。发光装置3为一球泡灯包括一灯罩602、一反射镜604、一发光模块610、一灯座612、一散热片614、一连接部616以及一电连接元件618。发光模块610包含一承载部606,以及多个发光单元608位于承载部606上,其中多个发光体608可为前述实施例中的发光元件1、1g或发光装置2。

170.本发明所列举的各实施例仅用以说明本发明,并非用以限制本发明的范围。任何人对本发明所作的任何显而易知的修饰或变更都不脱离本发明的精神与范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。